5

4

3

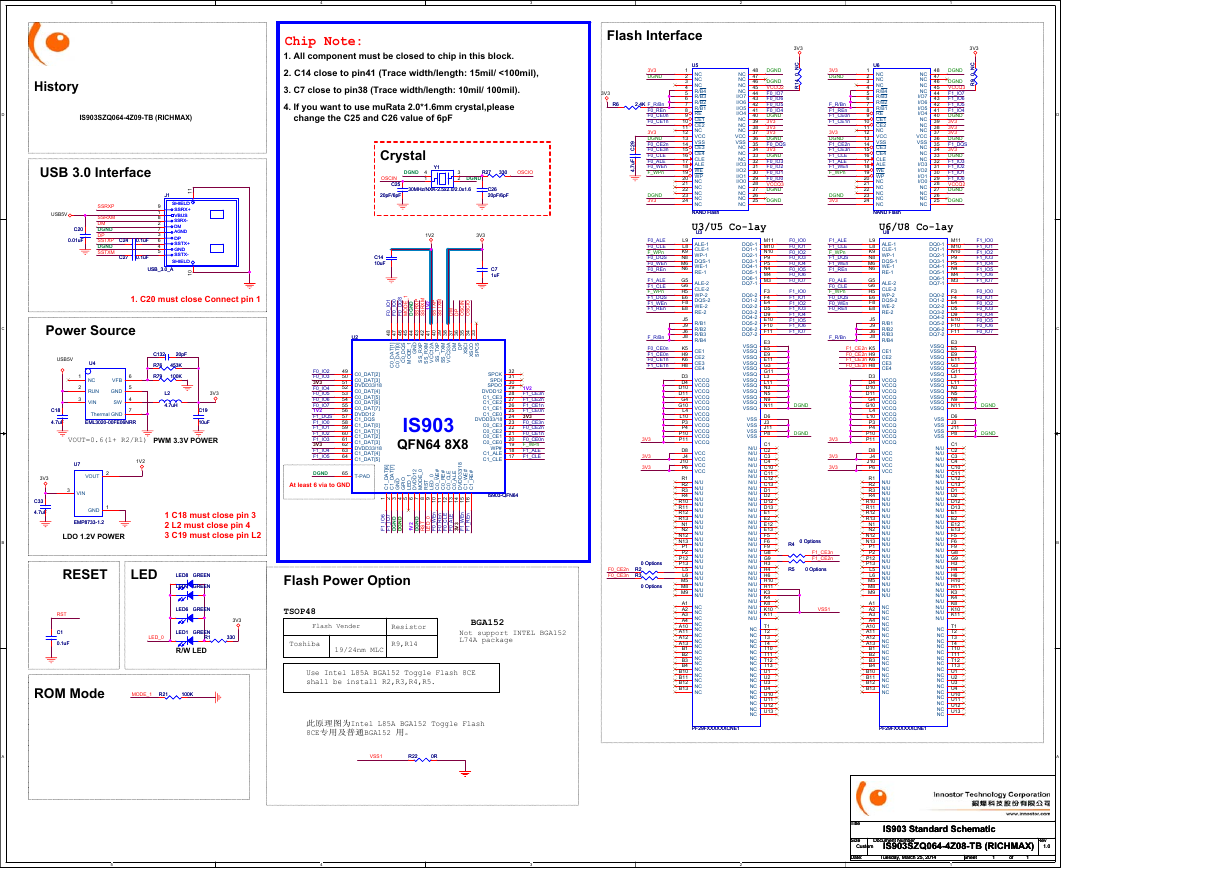

History

IS903SZQ064-4Z09-TB (RICHMAX)

USB 3.0 Interface

USB5V

C20

C20

0.01uF

0.01uF

SSRXP

SSRXM

DM

DGND

DP

SSTXP

DGND

SSTXM

C24

C24

0.1uF

0.1uF

C27

C27

0.1uF

0.1uF

J1

J1

1

1

SHIELD

SHIELD

SSRX+

SSRX+

VBUS

VBUS

SSRX-

SSRX-

DM

DM

AGND

AGND

DP

DP

SSTX+

SSTX+

GND

GND

SSTX-

SSTX-

SHIELD

SHIELD

9

1

8

2

7

3

6

4

5

USB_3.0_A

USB_3.0_A

0

1

1. C20 must close Connect pin 1

Power Source

USB5V

C18

C18

4.7uF

4.7uF

U4

U4

NC

RUN

VIN

1

2

3

VFB

GND

SW

Thermal GND

6

5

4

7

EML3020-00FE06NRR

EML3020-00FE06NRR

C132

C132

20pF

20pF

R76

R76

R79

R79

453K

453K

100K

100K

L2

L2

4.7uH

4.7uH

3V3

C19

C19

10uF

10uF

VOUT=0.6(1+ R2/R1) PWM 3.3V POWER

1V2

3V3

C33

C33

4.7uF

4.7uF

U7

U7

VOUT

3

VIN

GND

EMP8733-1.2

EMP8733-1.2

2

1

LDO 1.2V POWER

1 C18 must close pin 3

2 L2 must close pin 4

3 C19 must close pin L2

Chip Note:

1. All component must be closed to chip in this block.

2. C14 close to pin41 (Trace width/length: 15mil/ <100mil),

3. C7 close to pin38 (Trace width/length: 10mil/ 100mil).

4. If you want to use muRata 2.0*1.6mm crystal,please

change the C25 and C26 value of 6pF

Crystal

Y1

Y1

DGND

4

1

3

2

DGND

R27

R27

330

330

OSCIO

30MHz/NXK-2.5x2.0/2.0x1.6

30MHz/NXK-2.5x2.0/2.0x1.6

C26

C26

20pF/6pF

20pF/6pF

OSCIN

C25

C25

20pF/6pF

20pF/6pF

1V2

3V3

C14

C14

10uF

10uF

C7

C7

1uF

1uF

U2

U2

F0_IO2

F0_IO3

3V3

F0_IO4

F0_IO5

F0_IO6

F0_IO7

1V2

F1_DQS

F1_IO0

F1_IO1

F1_IO2

F1_IO3

3V3

F1_IO4

F1_IO5

49

C0_DAT[2]

50

51 C0_DAT[3]

DVDD33/18

52

C0_DAT[4]

53

C0_DAT[5]

54

C0_DAT[6]

55

C0_DAT[7]

56

DVDD12

57

C1_DQS

58

C1_DAT[0]

59

C1_DAT[1]

60

C1_DAT[2]

61

C1_DAT[3]

62

DVDD33/18

63

C1_DAT[4]

64

C1_DAT[5]

DGND

65

At least 6 via to GND

T-PAD

I

I

1

O

_

0

F

0

O

_

0

F

S

Q

D

_

0

F

1

_

E

D

O

M

P

X

R

S

S

M

X

R

S

S

D

N

G

D

2

V

1

P

X

T

S

S

M

X

T

S

S

I

I

N

C

S

O

O

C

S

O

M

D

P

D

8

4

7

4

6

4

5

4

4

4

3

4

2

4

1

4

0

4

9

3

8

3

7

3

6

3

5

3

4

3

3

3

S

Q

D

_

0

C

1

_

E

D

O

M

]

1

[

T

A

D

_

0

C

]

0

[

T

A

D

_

0

C

D

N

G

P

X

R

_

S

S

M

X

R

_

S

S

A

2

1

C

C

V

P

X

T

_

S

S

M

X

T

_

S

S

A

3

3

C

C

V

M

D

P

D

I

C

S

X

O

C

S

X

S

C

P

S

IS903

QFN64 8X8

]

6

[

T

A

D

_

1

C

]

7

[

T

A

D

_

1

C

2

1

D

D

V

D

0

_

E

D

O

M

1

_

D

E

L

#

E

W

_

0

C

#

E

R

_

0

C

E

L

C

_

0

C

E

L

A

_

0

C

0

_

D

E

L

T

S

R

D

N

G

I

O

P

G

8

1

/

3

3

D

D

V

D

#

E

W

_

1

C

#

E

R

_

1

C

1

2

3

4

5

6

7

8

9

0

1

1

1

2

1

3

1

4

1

5

1

6

1

I

I

6

O

_

1

F

7

O

_

1

F

D

N

G

D

D

N

G

D

D

N

G

D

T

S

R

2

V

1

n

E

W

_

0

F

n

E

R

_

0

F

E

L

C

_

0

F

E

L

A

_

0

F

0

_

D

E

L

3

V

3

n

E

W

_

1

F

n

E

R

_

1

F

SPCK

SPDI

SPDO

DVDD12

C1_CE3

C1_CE2

C1_CE1

C1_CE0

DVDD33/18

C0_CE3

C0_CE2

C0_CE1

C0_CE0

WP#

C1_ALE

C1_CLE

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

1V2

F1_CE3n

F1_CE2n

F1_CE1n

F1_CE0n

3V3

F0_CE3n

F0_CE2n

F0_CE1n

F0_CE0n

F_WPn

F1_ALE

F1_CLE

IS903-QFN64

IS903-QFN64

RESET

LED

RST

C1

C1

0.1uF

0.1uF

LED_0

LED8 GREEN

LED8 GREEN

LED7 GREEN

LED7 GREEN

LED6 GREEN

LED6 GREEN

LED1 GREEN

LED1 GREEN

R1

R1

R/W LED

3V3

330

330

Flash Power Option

TSOP48

Flash Vender

Toshiba

19/24nm MLC

Resistor

R9,R14

BGA152

Not support INTEL BGA152

L74A package

ROM Mode

MODE_1

R21

R21

100K

100K

Use Intel L85A BGA152 Toggle Flash 8CE

shall be install R2,R3,R4,R5.

此原理图为Intel L85A BGA152 Toggle Flash

8CE专用及普通BGA152 用。

VSS1

R22

R22

0R

0R

D

C

B

A

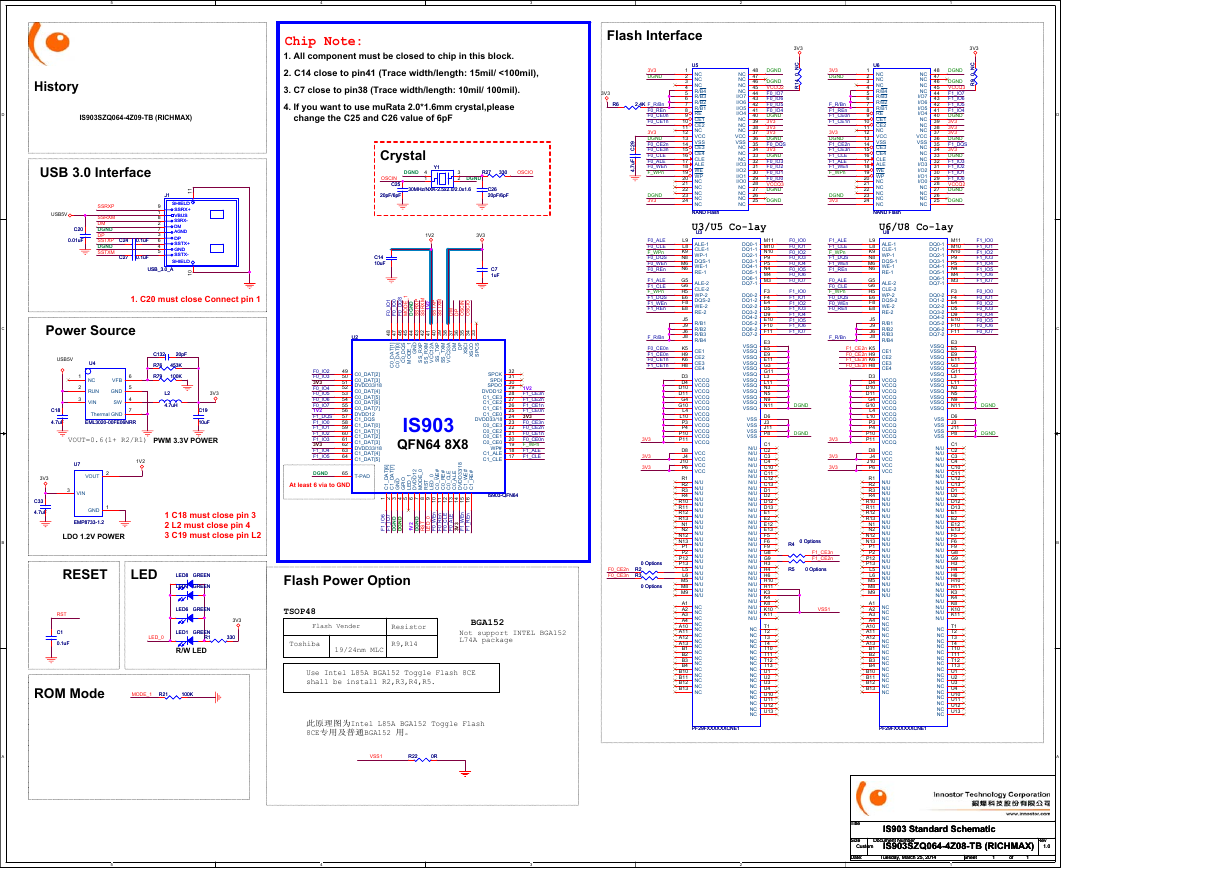

Flash Interface

3V3

R6

R6

2.4K

2.4K

9

9

2

2

C

C

F

F

u

u

7

7

.

.

4

4

3V3

DGND

F_R/Bn

F0_REn

F0_CE0n

F0_CE1n

3V3

DGND

F0_CE2n

F0_CE3n

F0_CLE

F0_ALE

F0_WEn

F_WPn

DGND

3V3

F0_ALE

F0_CLE

F_WPn

F0_DQS

F0_WEn

F0_REn

F1_ALE

F1_CLE

F_WPn

F1_DQS

F1_WEn

F1_REn

F_R/Bn

F0_CE0n

F1_CE0n

F0_CE1n

F1_CE1n

3V3

3V3

3V3

F0_CE2n

F0_CE3n

0 Options

0 Options

R2

R2

R3

R3

0 Options

0 Options

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

L9

L8

K9

N8

M6

N6

G5

G6

H5

E6

F8

E8

J5

J9

J6

J8

K5

H9

K6

H8

D3

D4

D10

D11

G4

G10

L4

L10

P3

P4

P10

P11

D8

J4

J10

P6

R1

R2

R3

R4

R10

R11

R12

R13

N1

N2

N12

N13

P1

P2

P12

P13

L5

L6

M5

M8

M9

A1

A2

A3

A4

A10

A11

A12

A13

B1

B2

B3

B4

B10

B11

B12

B13

U3/U5 Co-lay

U3

U3

ALE-1

CLE-1

WP-1

DQS-1

WE-1

RE-1

ALE-2

CLE-2

WP-2

DQS-2

WE-2

RE-2

R/B1

R/B2

R/B3

R/B4

CE1

CE2

CE3

CE4

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCC

VCC

VCC

VCC

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

DQ0-1

DQ1-1

DQ2-1

DQ3-1

DQ4-1

DQ5-1

DQ6-1

DQ7-1

DQ0-2

DQ1-2

DQ2-2

DQ3-2

DQ4-2

DQ5-2

DQ6-2

DQ7-2

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

M11

M10

N10

P9

P5

N4

M4

M3

F3

F4

E4

D5

D9

E10

F10

F11

E3

E5

E9

E11

G3

G11

L3

L11

N3

N5

N9

N11

D6

J3

J11

P8

C1

C2

C3

C4

C10

C11

C12

C13

D1

D2

D12

D13

E1

E2

E12

E13

F5

F6

F9

G8

G9

H3

H4

H6

H10

H11

K3

K4

K8

K10

K11

T1

T2

T3

T4

T10

T11

T12

T13

U1

U2

U3

U4

U10

U11

U12

U13

2

NC

NC

NC

NC

I/O7

I/O6

I/O5

I/O4

NC

NC

NC

VCC

VSS

NC

NC

NC

I/O3

I/O2

I/O1

I/O0

NC

NC

NC

NC

3V3

C

C

N

N

_

_

0

0

4

4

1

1

R

R

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

DGND

DGND

VCCQ2

F0_IO7

F0_IO6

F0_IO5

F0_IO4

DGND

3V3

3V3

3V3

DGND

F0_DQS

3V3

DGND

F0_IO3

F0_IO2

F0_IO1

F0_IO0

VCCQ3

DGND

DGND

U5

U5

NC

NC

NC

R/B4

R/B3

R/B2

R/B1

RE

CE1

CE2

NC

VCC

VSS

CE3

CE4

CLE

ALE

WE

WP

NC

NC

NC

NC

NC

NAND Flash

NAND Flash

3V3

DGND

F_R/Bn

F1_REn

F1_CE0n

F1_CE1n

3V3

DGND

F1_CE2n

F1_CE3n

F1_CLE

F1_ALE

F1_WEn

F_WPn

DGND

3V3

F1_ALE

F1_CLE

F_WPn

F1_DQS

F1_WEn

F1_REn

F0_ALE

F0_CLE

F_WPn

F0_DQS

F0_WEn

F0_REn

F_R/Bn

3V3

3V3

3V3

F0_IO0

F0_IO1

F0_IO2

F0_IO3

F0_IO4

F0_IO5

F0_IO6

F0_IO7

F1_IO0

F1_IO1

F1_IO2

F1_IO3

F1_IO4

F1_IO5

F1_IO6

F1_IO7

DGND

DGND

R4 0 Options

R4 0 Options

F1_CE3n

F1_CE2n

R5

R5

0 Options

0 Options

VSS1

1

3V3

C

C

N

N

_

_

0

0

9

9

R

R

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

NC

NC

NC

NC

I/O7

I/O6

I/O5

I/O4

NC

NC

NC

VCC

VSS

NC

NC

NC

I/O3

I/O2

I/O1

I/O0

NC

NC

NC

NC

DGND

DGND

VCCQ3

F1_IO7

F1_IO6

F1_IO5

F1_IO4

DGND

3V3

3V3

3V3

DGND

F1_DQS

3V3

DGND

F1_IO3

F1_IO2

F1_IO1

F1_IO0

VCCQ2

DGND

DGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

U6

U6

NC

NC

NC

R/B4

R/B3

R/B2

R/B1

RE

CE1

CE2

NC

VCC

VSS

CE3

CE4

CLE

ALE

WE

WP

NC

NC

NC

NC

NC

NAND Flash

NAND Flash

L9

L8

K9

N8

M6

N6

G5

G6

H5

E6

F8

E8

J5

J9

J6

J8

F1_CE2n

F0_CE2n

F1_CE3n

F0_CE3n

K5

H9

K6

H8

D3

D4

D10

D11

G4

G10

L4

L10

P3

P4

P10

P11

D8

J4

J10

P6

R1

R2

R3

R4

R10

R11

R12

R13

N1

N2

N12

N13

P1

P2

P12

P13

L5

L6

M5

M8

M9

A1

A2

A3

A4

A10

A11

A12

A13

B1

B2

B3

B4

B10

B11

B12

B13

U6/U8 Co-lay

U8

U8

ALE-1

CLE-1

WP-1

DQS-1

WE-1

RE-1

ALE-2

CLE-2

WP-2

DQS-2

WE-2

RE-2

R/B1

R/B2

R/B3

R/B4

CE1

CE2

CE3

CE4

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

VCC

VCC

VCC

VCC

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

F1_IO0

F1_IO1

F1_IO2

F1_IO3

F1_IO4

F1_IO5

F1_IO6

F1_IO7

F0_IO0

F0_IO1

F0_IO2

F0_IO3

F0_IO4

F0_IO5

F0_IO6

F0_IO7

DGND

DGND

DQ0-1

DQ1-1

DQ2-1

DQ3-1

DQ4-1

DQ5-1

DQ6-1

DQ7-1

DQ0-2

DQ1-2

DQ2-2

DQ3-2

DQ4-2

DQ5-2

DQ6-2

DQ7-2

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

N/U

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

M11

M10

N10

P9

P5

N4

M4

M3

F3

F4

E4

D5

D9

E10

F10

F11

E3

E5

E9

E11

G3

G11

L3

L11

N3

N5

N9

N11

D6

J3

J11

P8

C1

C2

C3

C4

C10

C11

C12

C13

D1

D2

D12

D13

E1

E2

E12

E13

F5

F6

F9

G8

G9

H3

H4

H6

H10

H11

K3

K4

K8

K10

K11

T1

T2

T3

T4

T10

T11

T12

T13

U1

U2

U3

U4

U10

U11

U12

U13

PF29FXXXXXXCNE1

PF29FXXXXXXCNE1

PF29FXXXXXXCNE1

PF29FXXXXXXCNE1

5

4

3

2

1

Title

Title

Title

Size

Size

Size

Custom

Custom

Custom

Date:

Date:

Date:

Document Number

Document Number

Document Number

IS903 Standard Schematic

IS903 Standard Schematic

IS903 Standard Schematic

IS903SZQ064-4Z08-TB (RICHMAX)

IS903SZQ064-4Z08-TB (RICHMAX)

IS903SZQ064-4Z08-TB (RICHMAX)

Tuesday, March 25, 2014

1

Tuesday, March 25, 2014

Tuesday, March 25, 2014

1

1

Sheet

Sheet

Sheet

of

of

of

1

1

1

D

C

B

A

Rev

Rev

Rev

1.0

1.0

1.0

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc