RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

RTC6705 CMOS 5.8GHz Band FM Transmitter

Product Description

The RTC6705 is a wide-band FM transmitter intended for the application on 5.8GHz bands FM

transmission. This chip includes a 5.8GHz band RF modulator, two channels of audio modulator

and internal power amplifier with +13dBm power output referred to external matching network.

The 5.8GHz band RF modulator block, which is frequency-synthesizer based with an integrated

VCO, generates the 5.8GHz band FM signal modulated with video signal and two modulated

audio subcarriers at 6MHz and 6.5MHz respectively. Both Stereo and Mono application are

available on the chip.

Transmission frequency can be set by internal register via SPI programming, or by selecting six

dedicated pins. Two stages output power of +2dBm or +13dBm can be configured via pins 34

and 35. Both CE and FCC regulations are easy to pass by using RTC6705 with application

circuit and single room shielding case.

Features

� 3.3V power supply

� Built-in PA with +13dBm output power

� 5.8GHz band FM modulator and transmitter

� Simple digital pins setting 24 fixed channels to eliminate external micro-controller

� Two audio subcarrier modulators at 6MHz/6.5MHz

� Single chip CMOS technology with integrated VCO and PLL

� Transmitter frequency programmability by SPI

� 40-pin leadless QFN package pass RoHS

Application

� AV Sender

� Baby Monitor

� Wireless Camera

� Wireless Audio

� Wireless Earphone

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

1

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

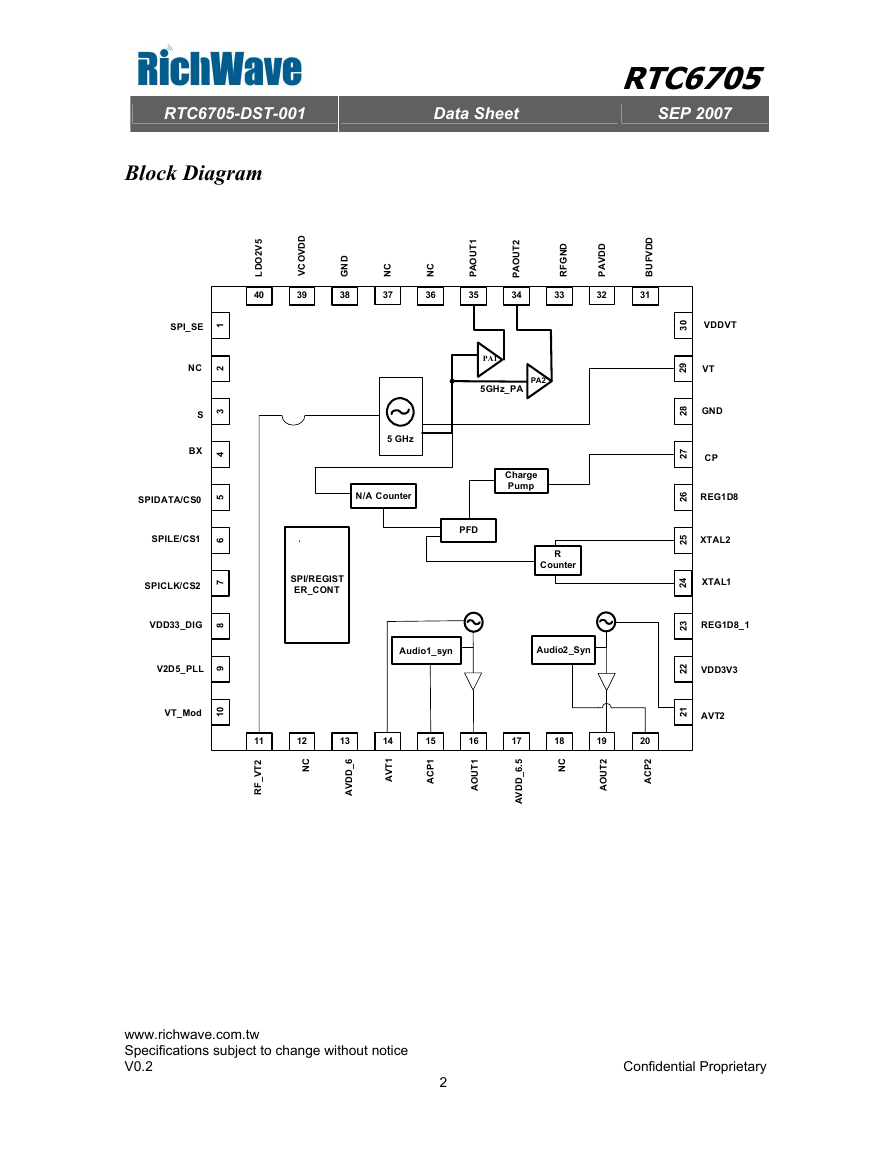

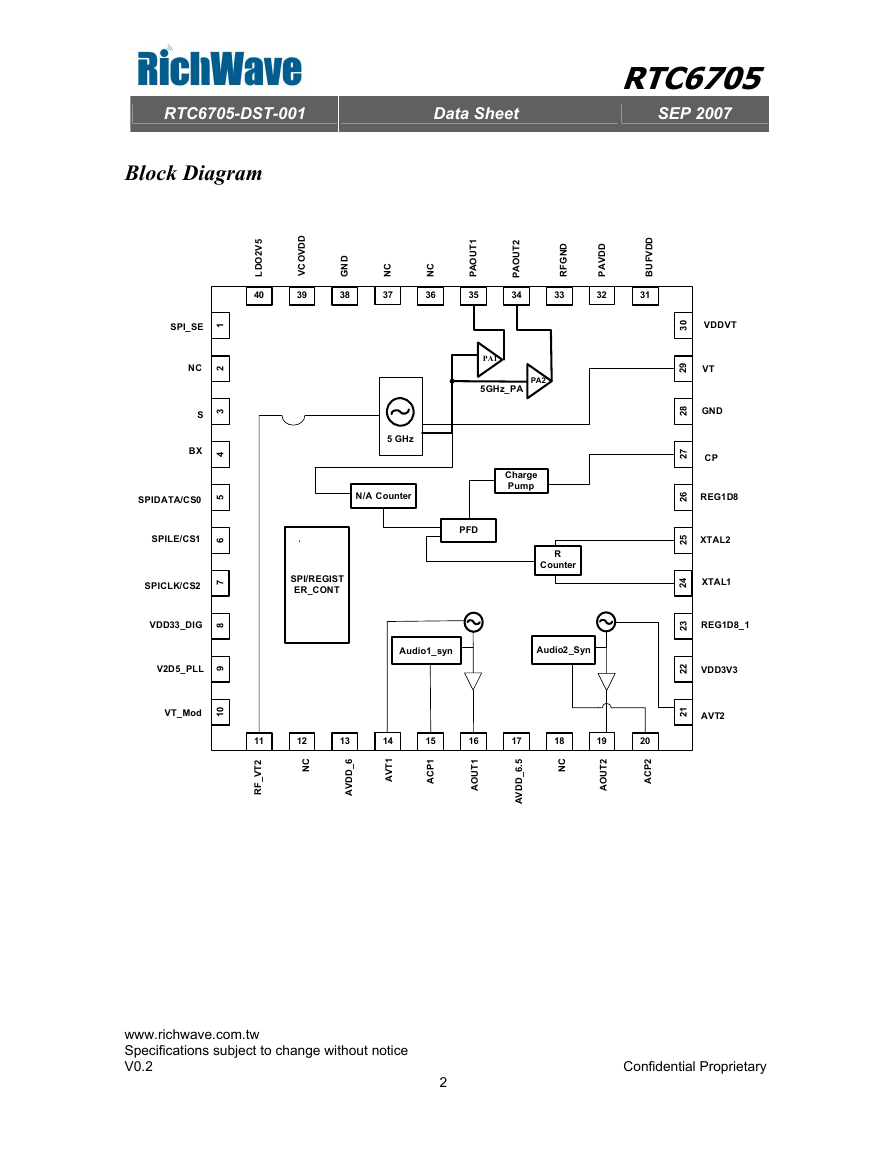

Block Diagram

5

V

2

O

D

L

40

D

D

V

O

C

V

39

D

N

G

38

C

N

37

C

N

36

1

T

U

O

A

P

35

2

T

U

O

A

P

34

D

N

G

F

R

33

D

D

V

A

P

32

D

D

V

F

U

B

31

SPI_SE

1

NC

2

3

S

BX

4

5 GHz

SPIDATA/CS0

5

N/A Counter

SPILE/CS1

6

SPICLK/CS2

7

SPI/REGIST

ER_CONT

PA1

PA2

5GHz_PA

Charge

Pump

PFD

R

Counter

VDD33_DIG

8

V2D5_PLL

9

VT_Mod

0

1

Audio1_syn

Audio2_Syn

11

2

T

V

_

F

R

12

C

N

13

6

_

D

D

V

A

14

1

T

V

A

15

1

P

C

A

16

1

T

U

O

A

17

5

.

6

_

D

D

V

A

18

C

N

19

2

T

U

O

A

20

2

P

C

A

0

3

VDDVT

9

2

VT

8

2

GND

7

2

CP

6

2

REG1D8

5

2

XTAL2

4

2

XTAL1

3

2

REG1D8_1

2

2

VDD3V3

1

2

AVT2

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

2

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

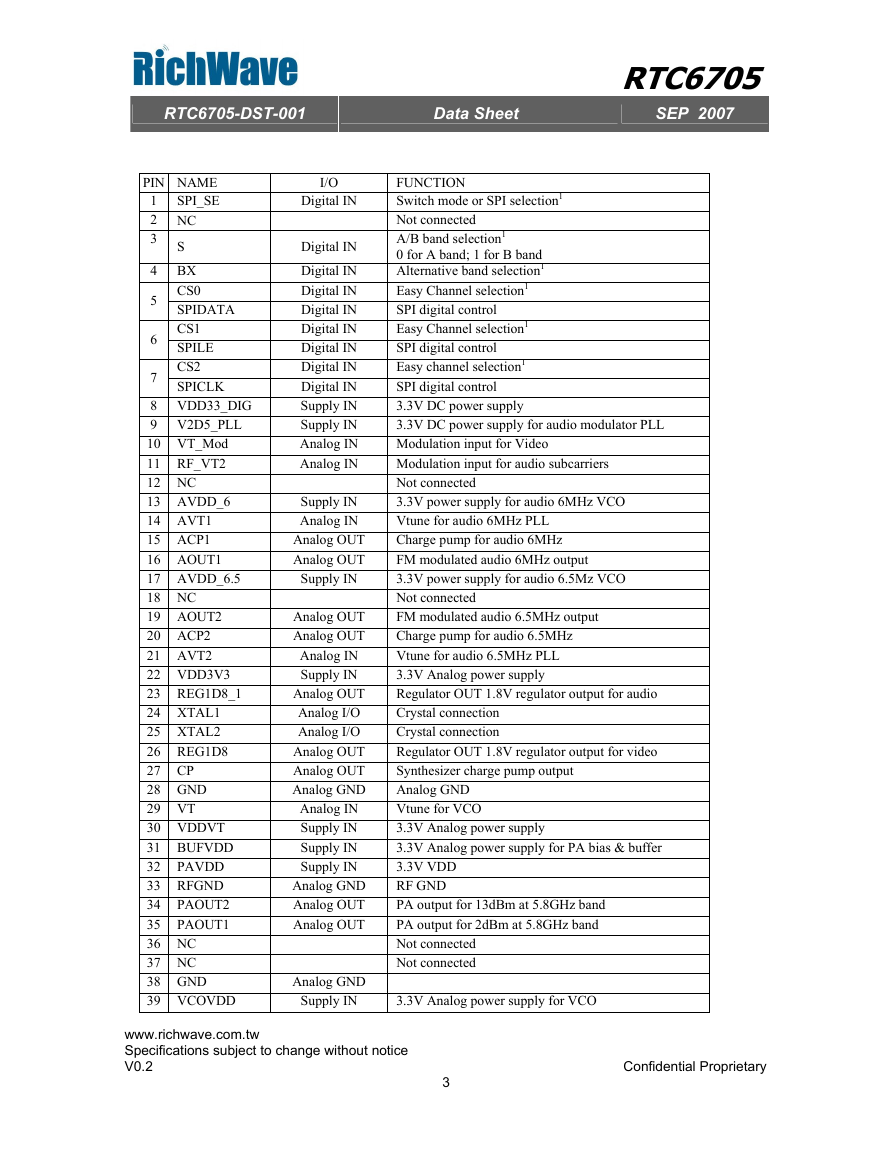

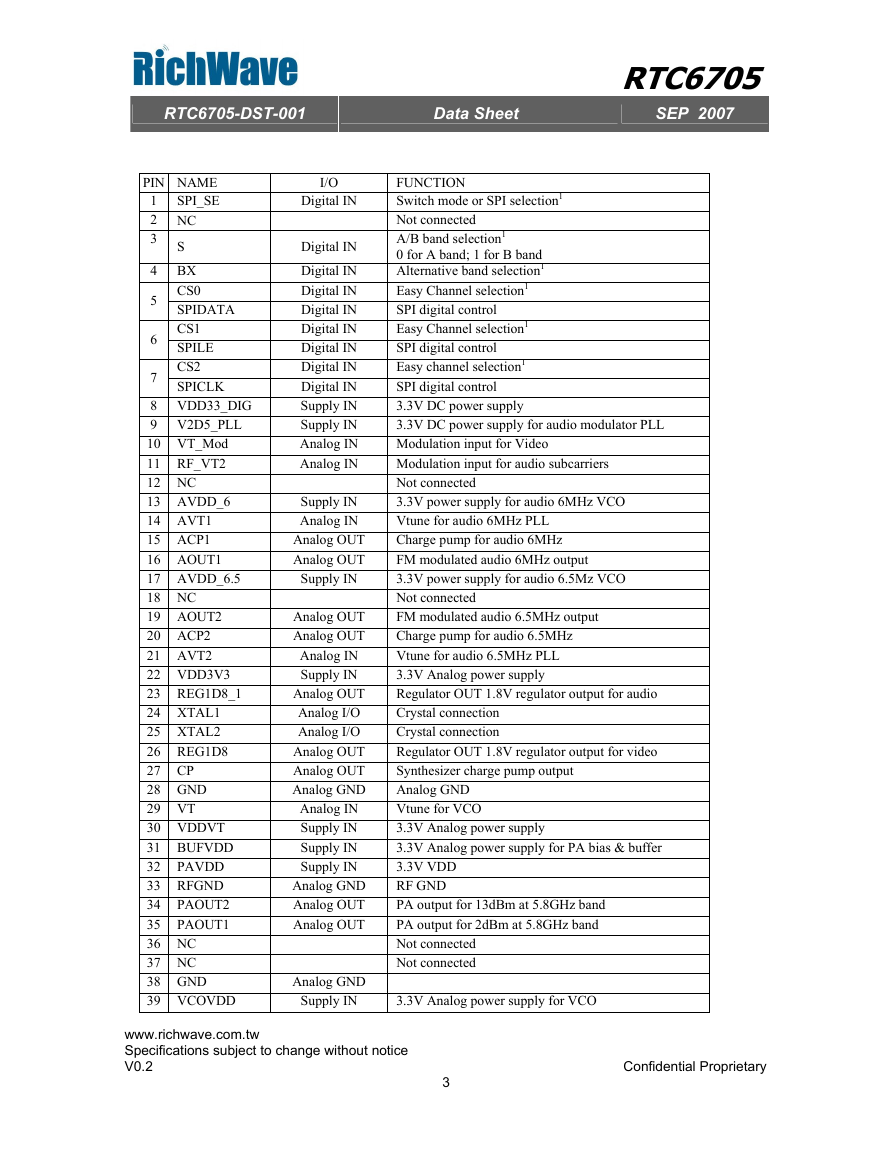

PIN NAME

SPI_SE

1

2 NC

3

S

4 BX

5

6

7

CS0

SPIDATA

CS1

SPILE

CS2

SPICLK

8 VDD33_DIG

9 V2D5_PLL

10 VT_Mod

11 RF_VT2

12 NC

I/O

Digital IN

Digital IN

Digital IN

Digital IN

Digital IN

Digital IN

Digital IN

Digital IN

Digital IN

Supply IN

Supply IN

Analog IN

Analog IN

FUNCTION

Switch mode or SPI selection1

Not connected

A/B band selection1

0 for A band; 1 for B band

Alternative band selection1

Easy Channel selection1

SPI digital control

Easy Channel selection1

SPI digital control

Easy channel selection1

SPI digital control

3.3V DC power supply

3.3V DC power supply for audio modulator PLL

Modulation input for Video

Modulation input for audio subcarriers

Not connected

13 AVDD_6

Supply IN

3.3V power supply for audio 6MHz VCO

14 AVT1

15 ACP1

16 AOUT1

Analog IN

Vtune for audio 6MHz PLL

Analog OUT

Charge pump for audio 6MHz

Analog OUT

FM modulated audio 6MHz output

17 AVDD_6.5

Supply IN

3.3V power supply for audio 6.5Mz VCO

18 NC

Not connected

19 AOUT2

Analog OUT

FM modulated audio 6.5MHz output

20 ACP2

21 AVT2

Analog OUT

Charge pump for audio 6.5MHz

Analog IN

Vtune for audio 6.5MHz PLL

22 VDD3V3

Supply IN

3.3V Analog power supply

23 REG1D8_1

Analog OUT

Regulator OUT 1.8V regulator output for audio

24 XTAL1

25 XTAL2

Analog I/O

Crystal connection

Analog I/O

Crystal connection

26 REG1D8

Analog OUT

Regulator OUT 1.8V regulator output for video

27 CP

28 GND

29 VT

30 VDDVT

31 BUFVDD

32 PAVDD

33 RFGND

34 PAOUT2

35 PAOUT1

36 NC

37 NC

38 GND

Analog OUT

Synthesizer charge pump output

Analog GND

Analog GND

Analog IN

Vtune for VCO

Supply IN

Supply IN

Supply IN

3.3V Analog power supply

3.3V Analog power supply for PA bias & buffer

3.3V VDD

Analog GND

RF GND

Analog OUT

PA output for 13dBm at 5.8GHz band

Analog OUT

PA output for 2dBm at 5.8GHz band

Not connected

Not connected

Analog GND

39 VCOVDD

Supply IN

3.3V Analog power supply for VCO

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

3

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

40 LDD2V5

Supply IN

Analog power supply for VCO

Note 1. Internal pull-high circuit can be left floating for logical high.

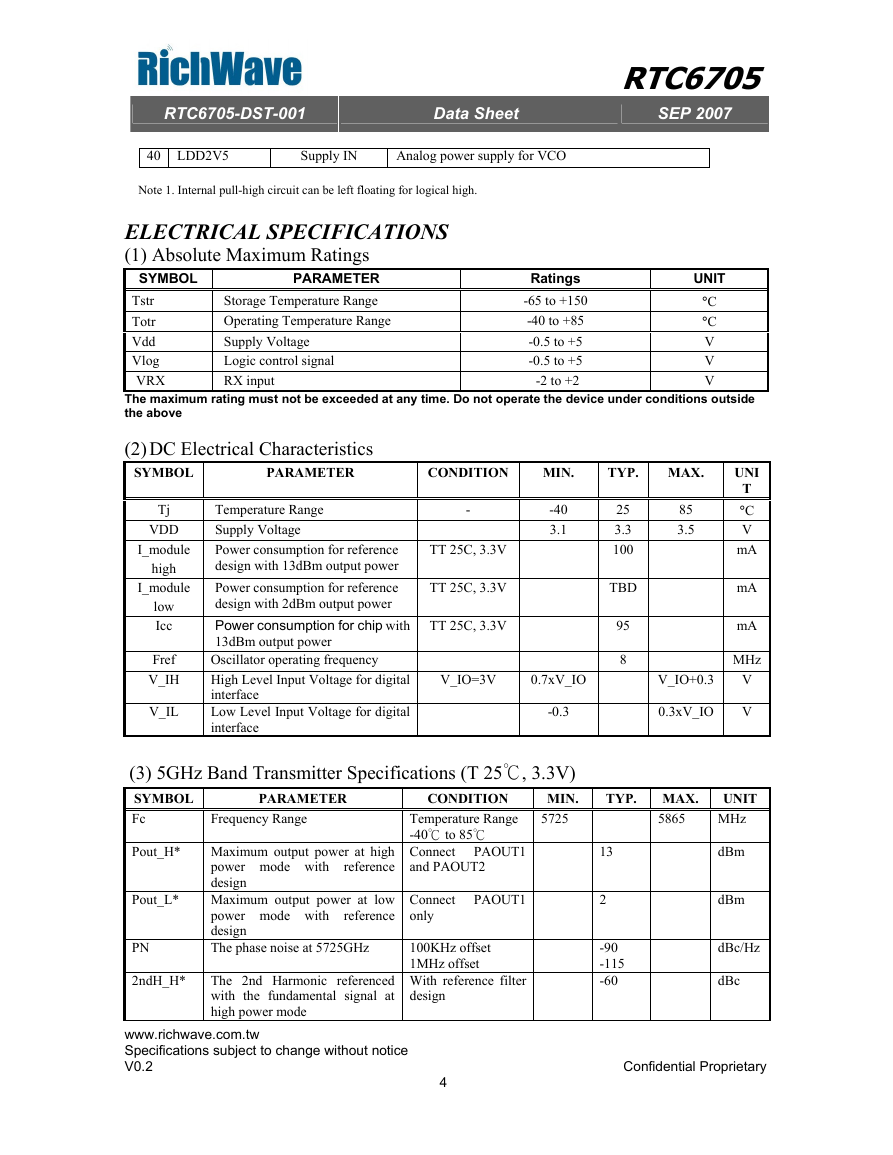

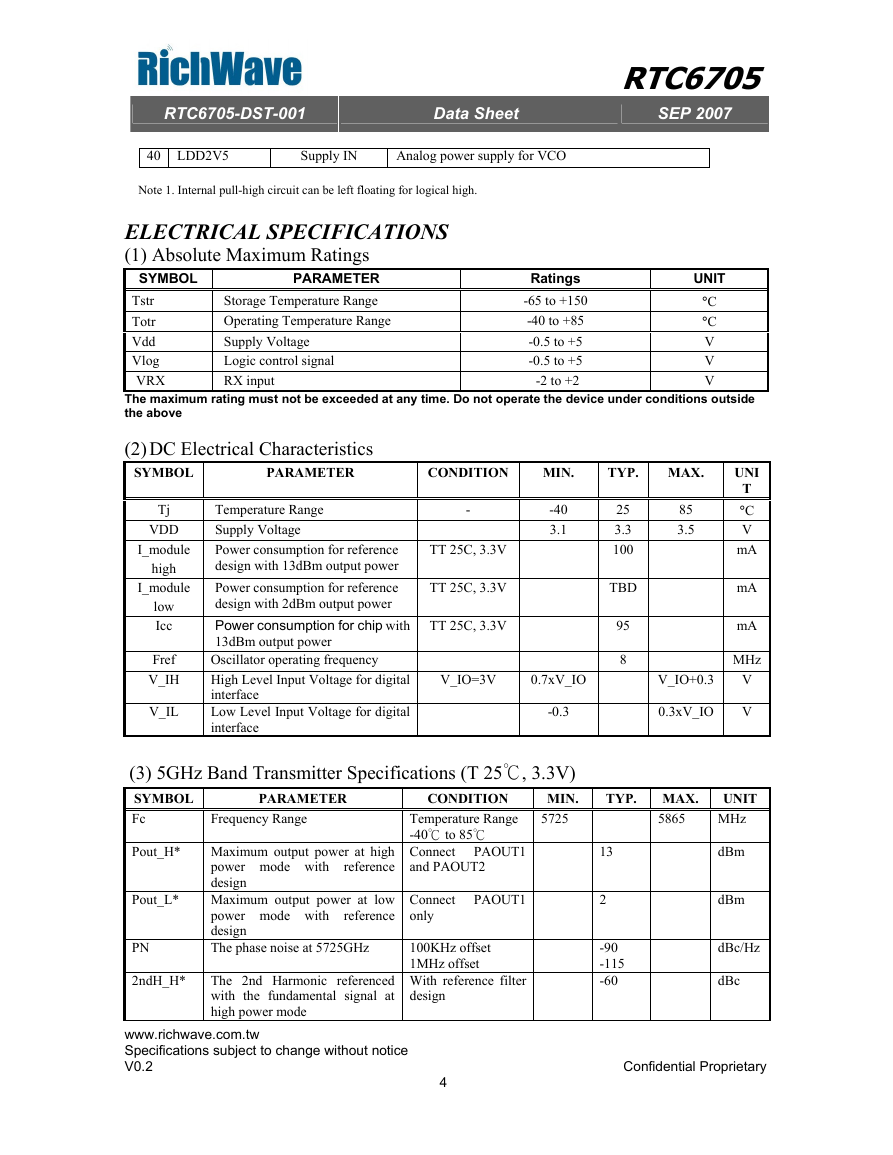

ELECTRICAL SPECIFICATIONS

(1) Absolute Maximum Ratings

SYMBOL

PARAMETER

Tstr

Totr

Vdd

Vlog

VRX

Storage Temperature Range

Operating Temperature Range

Supply Voltage

Logic control signal

RX input

Ratings

-65 to +150

-40 to +85

-0.5 to +5

-0.5 to +5

-2 to +2

UNIT

°C

°C

V

V

V

The maximum rating must not be exceeded at any time. Do not operate the device under conditions outside

the above

(2) DC Electrical Characteristics

SYMBOL

PARAMETER

CONDITION

MIN.

TYP. MAX.

Tj

Temperature Range

VDD

Supply Voltage

I_module

high

I_module

low

Icc

Fref

V_IH

V_IL

Power consumption for reference

design with 13dBm output power

Power consumption for reference

design with 2dBm output power

Power consumption for chip with

13dBm output power

Oscillator operating frequency

High Level Input Voltage for digital

interface

Low Level Input Voltage for digital

interface

-

TT 25C, 3.3V

TT 25C, 3.3V

TT 25C, 3.3V

-40

3.1

V_IO=3V

0.7xV_IO

-0.3

25

3.3

100

TBD

95

8

85

3.5

V_IO+0.3

0.3xV_IO

(3) 5GHz Band Transmitter Specifications (T 25℃, 3.3V)

UNI

T

°C

V

mA

mA

mA

MHz

V

V

SYMBOL

PARAMETER

CONDITION

MIN.

TYP. MAX.

UNIT

Fc

Frequency Range

Pout_H*

Pout_L*

PN

2ndH_H*

Maximum output power at high

power mode with

reference

design

Maximum output power at low

power mode with

reference

design

The phase noise at 5725GHz

The 2nd Harmonic referenced

with the fundamental signal at

high power mode

to 85℃

Temperature Range

-40

Connect PAOUT1

and PAOUT2

℃

Connect PAOUT1

only

100KHz offset

1MHz offset

With reference filter

design

www.richwave.com.tw

Specifications subject to change without notice

V0.2

4

5725

5865

MHz

13

2

-90

-115

-60

dBm

dBm

dBc/Hz

dBc

Confidential Proprietary

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

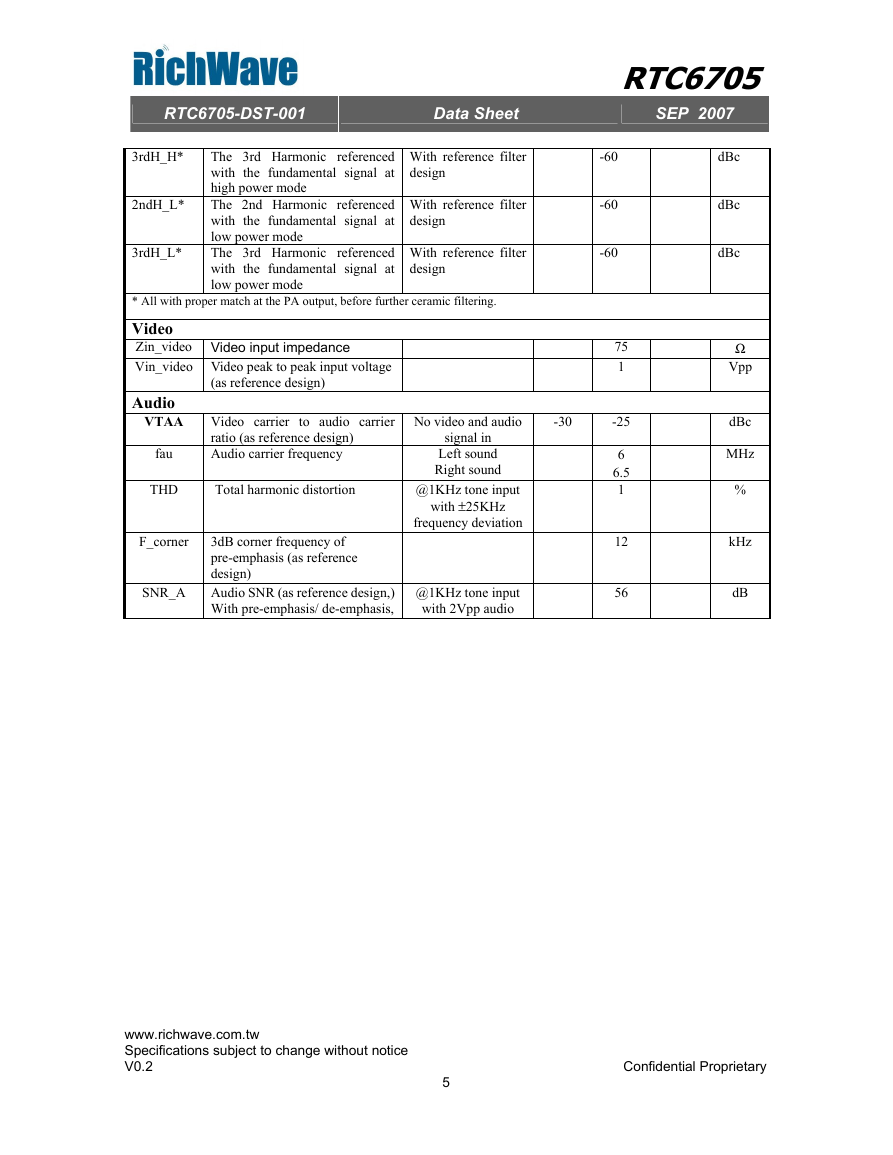

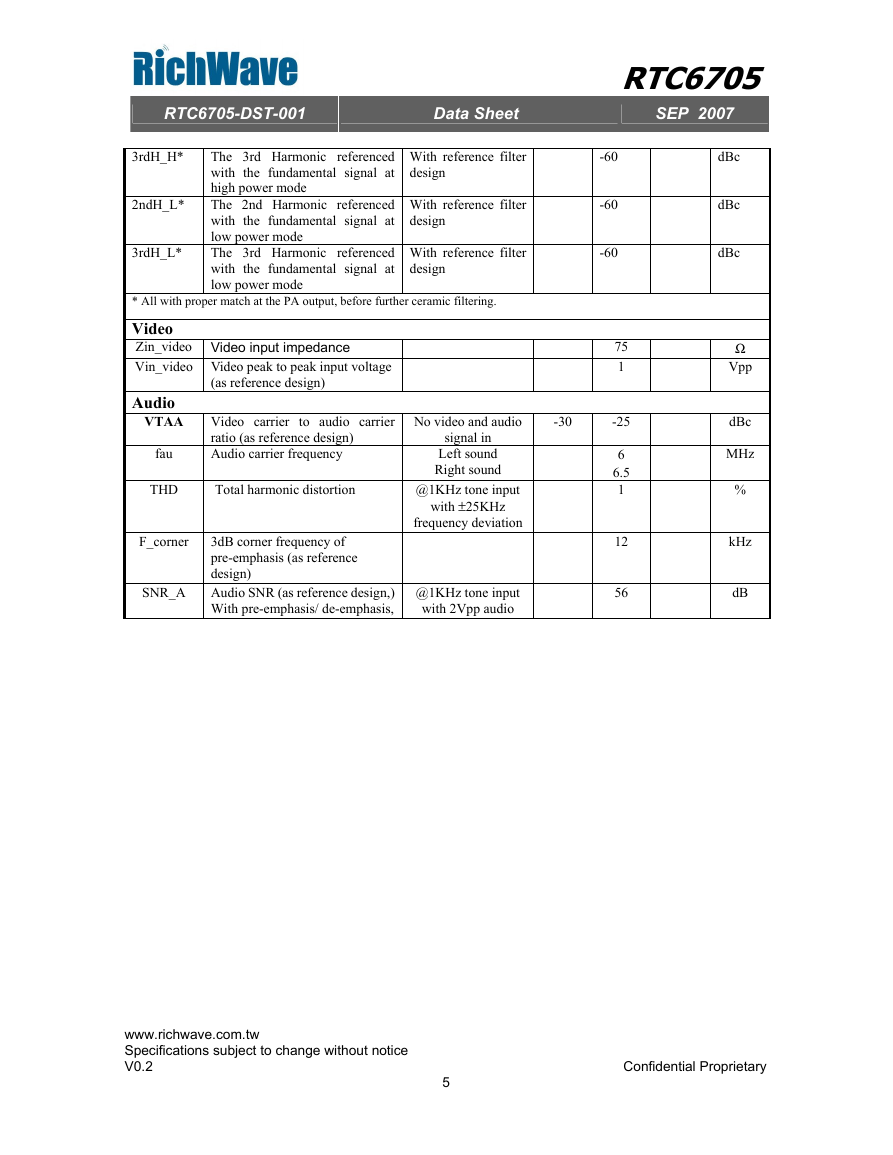

3rdH_H*

2ndH_L*

3rdH_L*

The 3rd Harmonic referenced

with the fundamental signal at

high power mode

The 2nd Harmonic referenced

with the fundamental signal at

low power mode

The 3rd Harmonic referenced

with the fundamental signal at

low power mode

With reference filter

design

With reference filter

design

With reference filter

design

* All with proper match at the PA output, before further ceramic filtering.

-60

-60

-60

75

1

-25

6

6.5

1

12

56

dBc

dBc

dBc

Ω

Vpp

dBc

MHz

%

kHz

dB

Video

Zin_video Video input impedance

Vin_video Video peak to peak input voltage

Audio

VTAA

fau

(as reference design)

Video carrier to audio carrier

ratio (as reference design)

Audio carrier frequency

No video and audio

-30

signal in

Left sound

Right sound

THD

Total harmonic distortion

@1KHz tone input

F_corner

3dB corner frequency of

pre-emphasis (as reference

design)

with ±25KHz

frequency deviation

SNR_A

Audio SNR (as reference design,)

With pre-emphasis/ de-emphasis,

@1KHz tone input

with 2Vpp audio

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

5

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

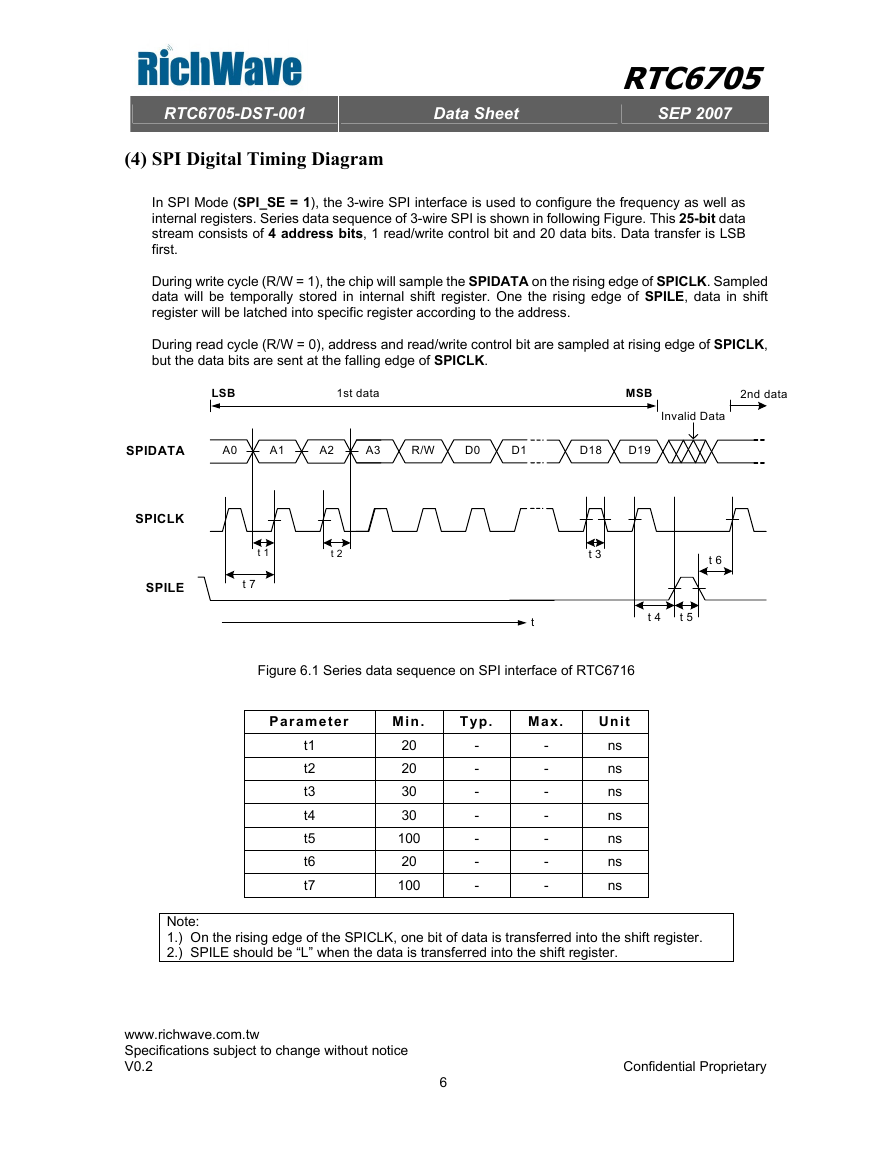

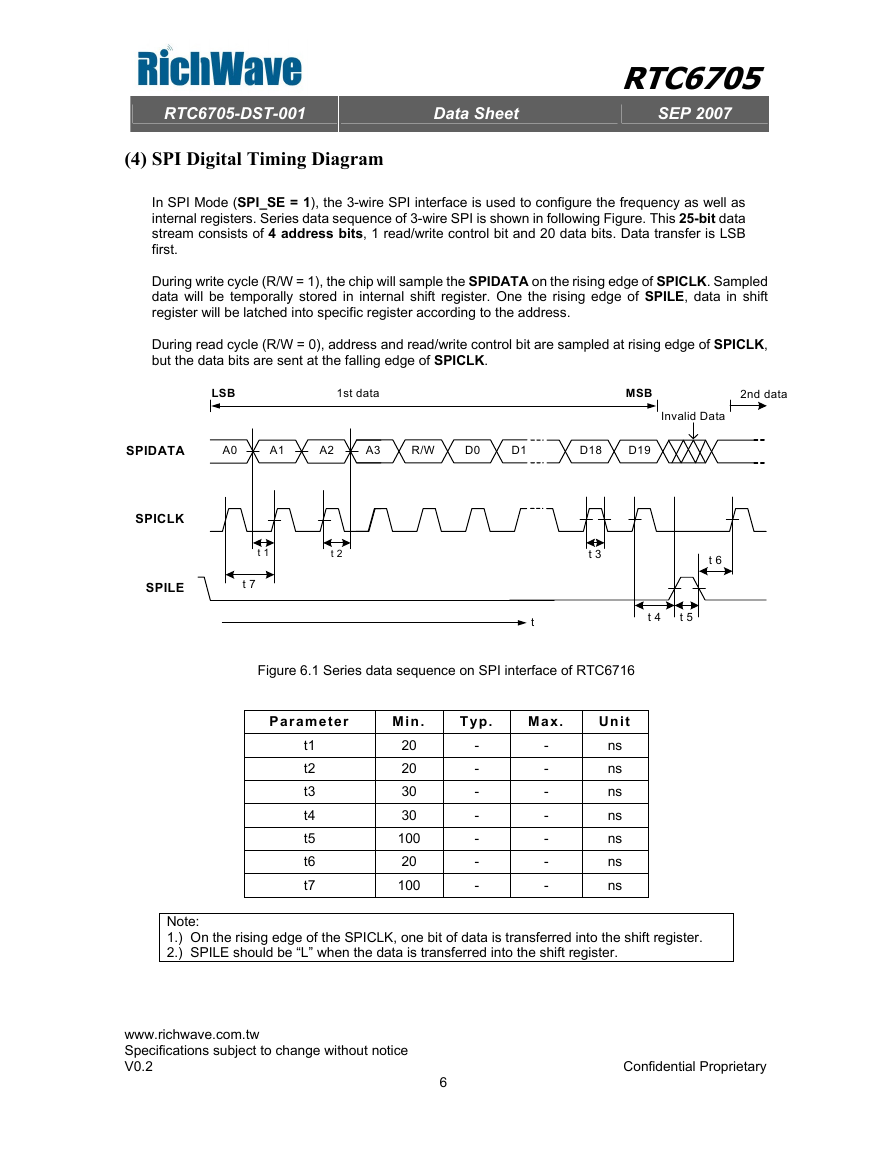

(4) SPI Digital Timing Diagram

In SPI Mode (SPI_SE = 1), the 3-wire SPI interface is used to configure the frequency as well as

internal registers. Series data sequence of 3-wire SPI is shown in following Figure. This 25-bit data

stream consists of 4 address bits, 1 read/write control bit and 20 data bits. Data transfer is LSB

first.

During write cycle (R/W = 1), the chip will sample the SPIDATA on the rising edge of SPICLK. Sampled

data will be temporally stored in internal shift register. One the rising edge of SPILE, data in shift

register will be latched into specific register according to the address.

During read cycle (R/W = 0), address and read/write control bit are sampled at rising edge of SPICLK,

but the data bits are sent at the falling edge of SPICLK.

LSB

1st data

MSB

2nd data

Invalid Data

SPIDATA

A0

A1

A2

A3

R/W

D0

D1

D18

D19

SPICLK

SPILE

t 7

t 1

t 2

t 3

t 6

Figure 6.1 Series data sequence on SPI interface of RTC6716

t

t 4

t 5

P a r a m e t e r

M i n .

T yp .

M a x .

U n i t

t1

t2

t3

t4

t5

t6

t7

20

20

30

30

100

20

100

-

-

-

-

-

-

-

-

-

-

-

-

-

-

ns

ns

ns

ns

ns

ns

ns

Note:

1.) On the rising edge of the SPICLK, one bit of data is transferred into the shift register.

2.) SPILE should be “L” when the data is transferred into the shift register.

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

6

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

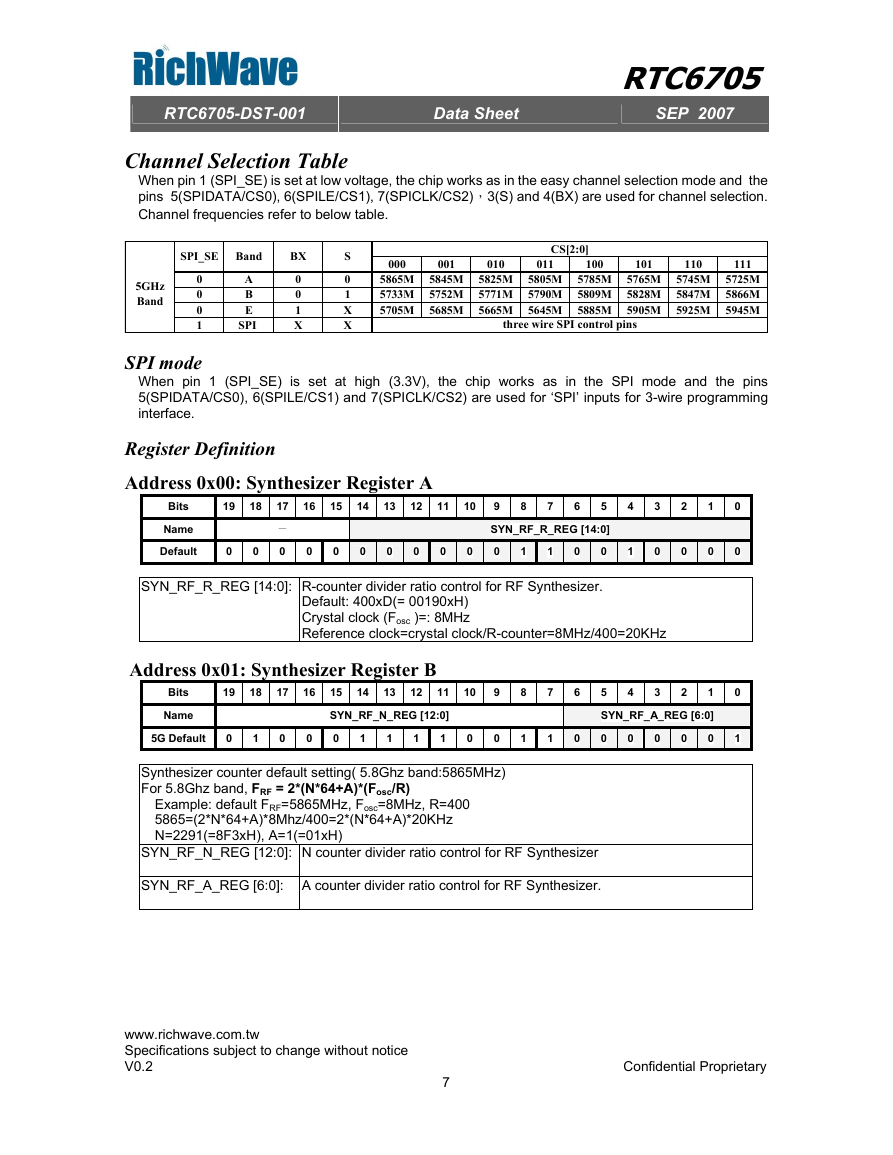

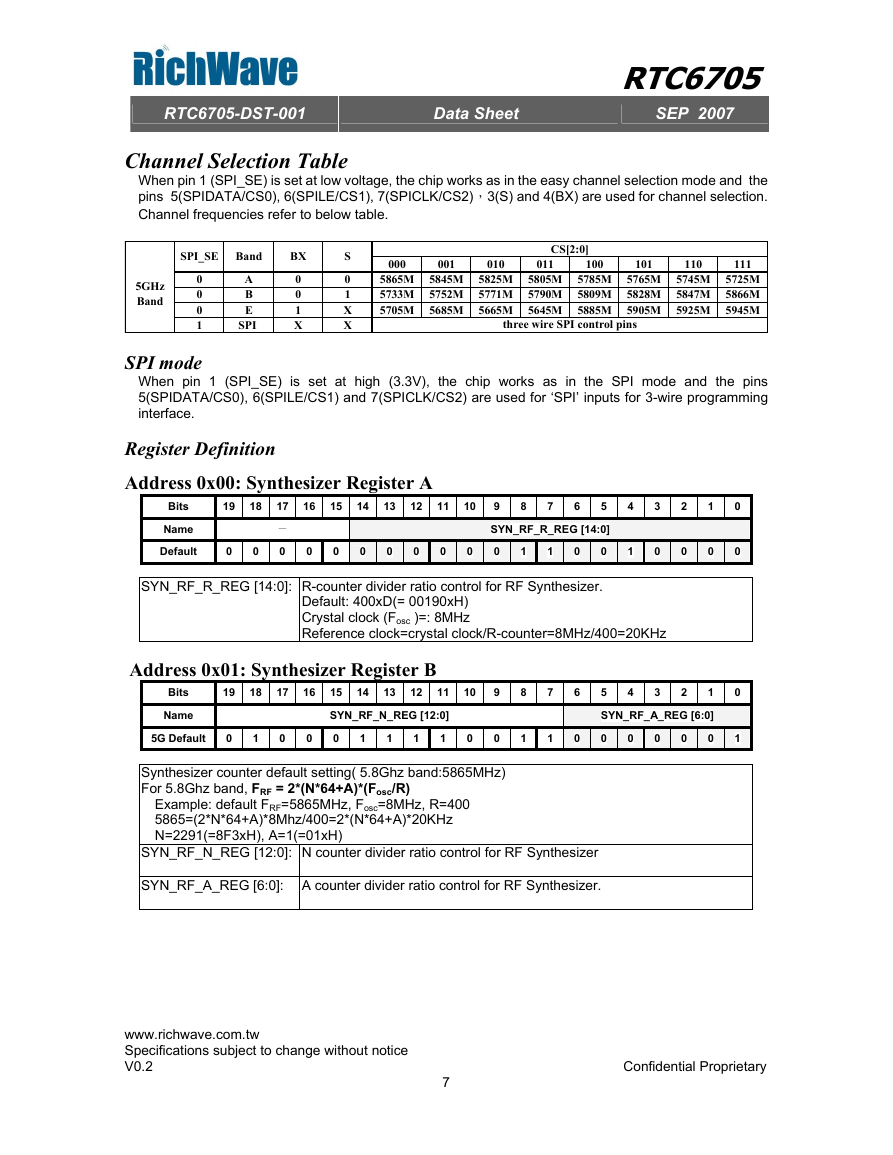

Channel Selection Table

When pin 1 (SPI_SE) is set at low voltage, the chip works as in the easy channel selection mode and the

pins 5(SPIDATA/CS0), 6(SPILE/CS1), 7(SPICLK/CS2),3(S) and 4(BX) are used for channel selection.

Channel frequencies refer to below table.

SPI_SE

Band

BX

5GHz

Band

0

0

0

1

A

B

E

SPI

0

0

1

X

S

0

1

X

X

SPI mode

CS[2:0]

000

001

010

011

100

101

110

111

5865M 5845M 5825M 5805M 5785M 5765M 5745M 5725M

5733M 5752M 5771M 5790M 5809M 5828M 5847M 5866M

5705M 5685M 5665M 5645M 5885M 5905M 5925M 5945M

three wire SPI control pins

When pin 1 (SPI_SE) is set at high (3.3V), the chip works as in the SPI mode and the pins

5(SPIDATA/CS0), 6(SPILE/CS1) and 7(SPICLK/CS2) are used for ‘SPI’ inputs for 3-wire programming

interface.

Register Definition

Address 0x00: Synthesizer Register A

Bits

19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Name

-

SYN_RF_R_REG [14:0]

Default

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

1

0

0

0

0

SYN_RF_R_REG [14:0]: R-counter divider ratio control for RF Synthesizer.

Default: 400xD(= 00190xH)

Crystal clock (Fosc )=: 8MHz

Reference clock=crystal clock/R-counter=8MHz/400=20KHz

Address 0x01: Synthesizer Register B

Bits

19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Name

SYN_RF_N_REG [12:0]

SYN_RF_A_REG [6:0]

5G Default

0

1

0

0

0

1

1

1

1

0

0

1

1

0

0

0

0

0

0

1

Synthesizer counter default setting( 5.8Ghz band:5865MHz)

For 5.8Ghz band, FRF = 2*(N*64+A)*(Fosc/R)

Example: default FRF=5865MHz, Fosc=8MHz, R=400

5865=(2*N*64+A)*8Mhz/400=2*(N*64+A)*20KHz

N=2291(=8F3xH), A=1(=01xH)

SYN_RF_N_REG [12:0]: N counter divider ratio control for RF Synthesizer

SYN_RF_A_REG [6:0]: A counter divider ratio control for RF Synthesizer.

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

7

�

RTC6705

RTC6705-DST-001

Data Sheet

SEP 2007

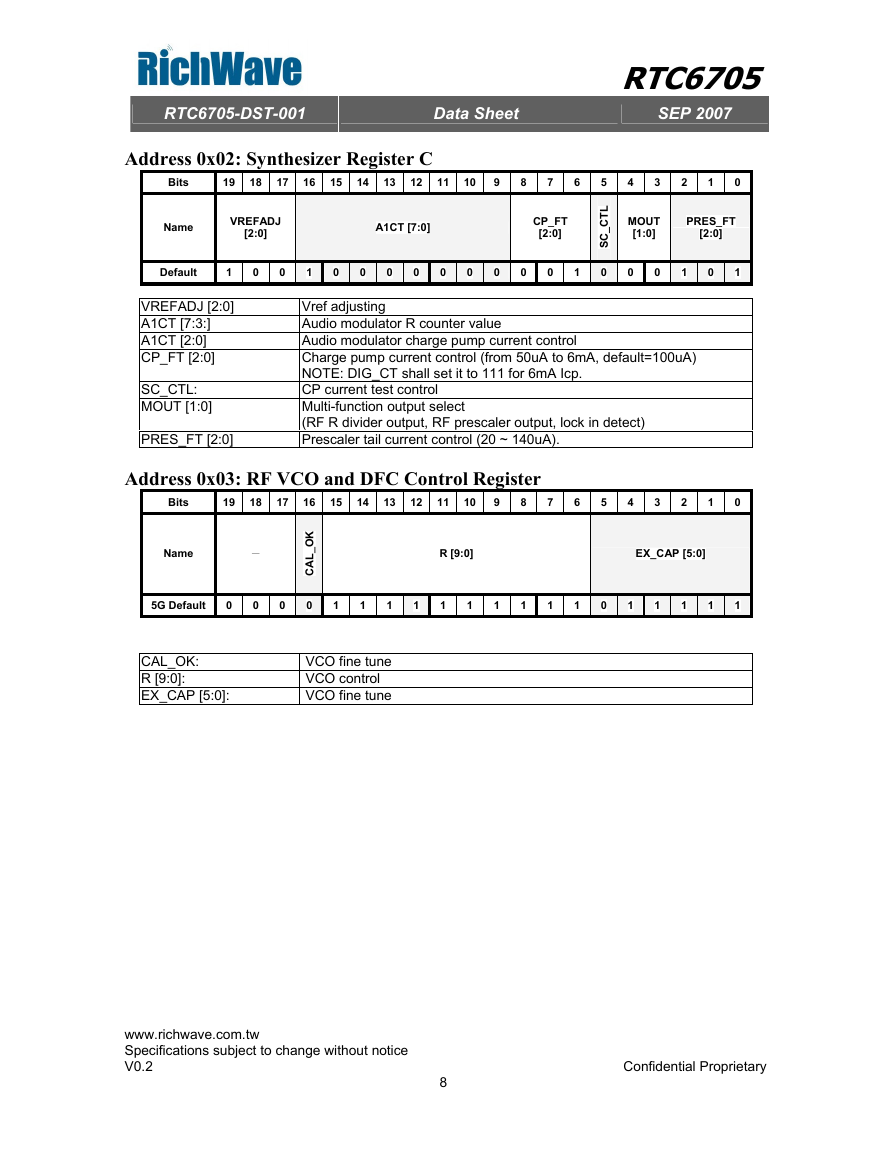

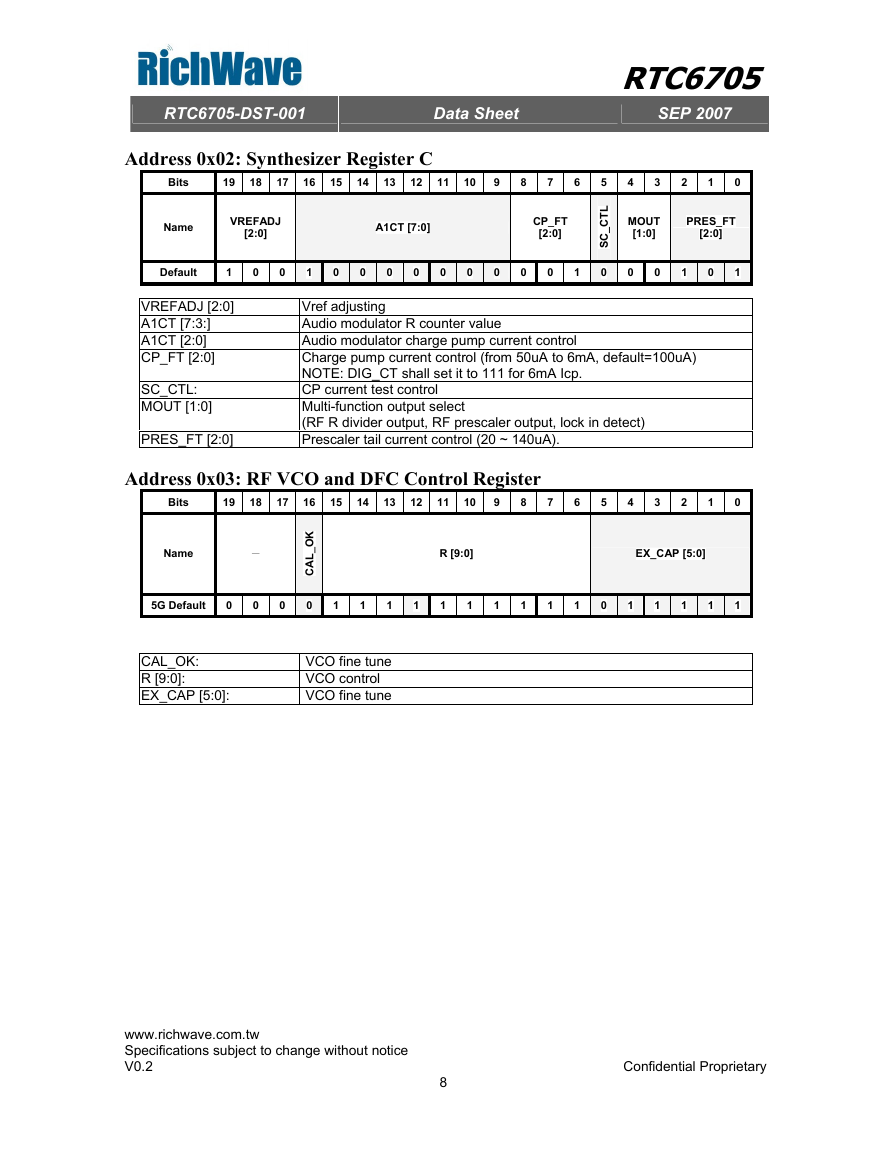

Address 0x02: Synthesizer Register C

Bits

19 18 17 16 15 14 13 12 11 10

9

8

7

6

Name

VREFADJ

[2:0]

A1CT [7:0]

CP_FT

[2:0]

5

L

T

C

_

C

S

4

3

2

1

0

MOUT

[1:0]

PRES_FT

[2:0]

Default

1

0

0

1

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

1

VREFADJ [2:0]

A1CT [7:3:]

A1CT [2:0]

CP_FT [2:0]

SC_CTL:

MOUT [1:0]

PRES_FT [2:0]

Vref adjusting

Audio modulator R counter value

Audio modulator charge pump current control

Charge pump current control (from 50uA to 6mA, default=100uA)

NOTE: DIG_CT shall set it to 111 for 6mA Icp.

CP current test control

Multi-function output select

(RF R divider output, RF prescaler output, lock in detect)

Prescaler tail current control (20 ~ 140uA).

Address 0x03: RF VCO and DFC Control Register

Bits

19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Name

-

K

O

_

L

A

C

R [9:0]

EX_CAP [5:0]

5G Default

0

0

0

0

1

1

1

1

1

1

1

1

1

1

0

1

1

1

1

1

CAL_OK:

R [9:0]:

EX_CAP [5:0]:

VCO fine tune

VCO control

VCO fine tune

www.richwave.com.tw

Specifications subject to change without notice

V0.2

Confidential Proprietary

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc