Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

Features

1/2.3-Inch 10Mp CMOS Digital Image Sensor

MT9J003 Data Sheet

For the latest data sheet, refer to Aptina’s Web site: www.aptina.com

Features

• 1080p digital video mode

Simple two-wire serial interface

Auto black level calibration

Support for external mechanical shutter

Support for external LED or xenon flash

High frame rate preview mode with arbitrary down-

size scaling from maximum resolution

Programmable controls: gain, horizontal and vertical

blanking, auto black level offset correction, frame

size/rate, exposure, left–right and top–bottom image

reversal, window size, and panning

Data interfaces: parallel or four-lane serial high-speed

pixel interface (HiSPi™) differential signaling (sub-

LVDS)

On-die phase-locked loop (PLL) oscillator

Bayer pattern downsize scaler

Integrated position-based color and lens shading

correction

One-time programmable memory (OTPM) for storing

module information

Applications

Digital video cameras

Digital still cameras

General Description

The Aptina MT9J003 is a 1/2.3-inch CMOS active-pixel

digital imaging sensor with an active pixel array of

3856H x 2764V including border pixels. It can support 10

megapixel (3664H x 2748V) digital still images and a

1080p (3840H x 2160V) digital video mode. It incorpo-

rates sophisticated on-chip camera functions such as

windowing, mirroring, column and row skip modes, and

snapshot mode. It is programmable through a simple

two-wire serial interface and has very low power con-

sumption.

Ordering Information

Table 1:

Part Number

MT9J003I12STCV2

MT9J003T12STCV

MT9J003D00STCV C2CBC1 HiSPi Bare Die, 0° CRA

MT9J003I12STCU

MT9J003D00STCU C2CBC1

Available Part Numbers

Description

HiSPi 48-pin iLCC, 0° CRA

HiSPi 48-pin tPLCC, 13.4° CRA

Parallel 48-pin iLCC, 0° CRA

Parallel Bare die, 0° CRA

Table 2:

Key Performance Parameters

Parameter

Optical format

Active imager size

Active pixels

Pixel size

Chief ray angle

Color filter array

Shutter type

Input clock frequency

Maxi-

mum

data

rate

Parallel

HiSPi (4-lane)

Frame

rate

Still mode, 4:3

(3664H x 2748V)

Preview mode

VGA

1080p mode

(1920H x 1080V)

ADC resolution

Responsivity

Dynamic range

SNRMAX

I/O Digital

Supply

voltage

Power

Con-

sump-

tion

Package

Digital

Analog

SLVS I/O

Still mode at 15fps

w/ serial I/F

Still mode at 7.5fps

w/ parallel I/F

Preview

Standby

Operating temperature

Value

1/2.3-inch (4:3)

6.440mm(H) x 4.616mm (V),

7.923mm diagonal (Entire sensor)

6.119mm(H) x 4.589mm (V),

7.649mm diagonal (Still mode)

6.413mm(H) x 3.607mm (V),

7.358mm diagonal (Video mode)

3856H x 2764V (Entire sensor)

3664H x 2748V (4:3, Still mode)

3840H x 2160V (16:9, Video mode)

1.67 x 1.67μm

0°, 13.4°

RGB Bayer pattern

Electronic rolling shutter (ERS)

with global reset release (GRR)

6–48 MHz

80 Mp/s at 80 MHz PIXCLK

2.8Gbps

Programmable up to 15 fps serial

I/F, 7.5 fps parallel I/F

30 fps with binning

60 fps with skip2bin2

60 fps using HiSPi I/F

30 fps using parallel I/F

12-bit, on-die

0.31 V/lux-sec (550nm)

65.2dB

34dB

1.7–1.9V (1.8V nominal)

or 2.4–3.1V (2.8V nominal)

1.7–1.9V (1.8V nominal)

2.4–3.1V (2.8V nominal)

0.4 - 0.8V (0.4 or 0.8V nominal)

638mW

388mW

250mW low power VGA

500μW (typical, EXTCLK disabled)

48-pin iLCC (10mm x 10mm)

Bare die,

48pin Tiny PLCC (12mm x 12mm)

–30°C to +70°C (at junction)

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

1

.

©2009 Aptina Imaging Corporation All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

Table of Contents

Table of Contents

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Functional Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Pixel Array . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Output Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Serial Pixel Data Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

High Speed Serial Pixel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

HiSPi Physical Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

DLL Timing Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

HiSPi Streaming Mode Protocol Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Protocol Fundamentals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Parallel Pixel Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Output Data Timing (Parallel Pixel Data Interface) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Frame Rates at Common Resolutions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Two-Wire Serial Register Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Start Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Stop Condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Slave Address/Data Direction Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Message Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Acknowledge Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

No-Acknowledge Bit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Typical Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Single READ From Random Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Single READ From Current Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Sequential READ, Start From Random Location. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Sequential READ, Start From Current Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Single WRITE to Random Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Sequential WRITE, Start at Random Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Programming Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

X Address Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Effect of Scaler on Legal Range of Output Sizes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Output Data Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Changing Registers While Streaming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Programming Restrictions When Using Global Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Control of the Signal Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Serial Register Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Parallel Pixel Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Output Enable Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Configuration of the Pixel Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

System States. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Power-On Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Soft Reset Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Signal State During Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

General Purpose Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

2

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

Table of Contents

Streaming/Standby Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Trigger Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Programming the PLL Divisors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Scaler. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Shading Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

The Correction Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

One-Time Programmable Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Sensor Readout Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Image Acquisition Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Window Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Pixel Border . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Readout Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Horizontal Mirror . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Vertical Flip. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Subsampling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Frame Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Absolute Minimum Array Line Length Pck . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Array Readout Line Length Pck . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Interface Line Length Pck . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Minimum Row Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Minimum Frame Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Fine Integration Time Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Fine Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Low Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Integration Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Aptina Gain Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Flash Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Global Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Overview of Global Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Entering and Leaving the Global Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Programmable Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Control of the Electromechanical Shutter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Using FLASH with Global Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

External Control of Integration Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Retriggering the Global Reset Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Global Reset and Soft Standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Sensor Core Digital Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Test Patterns . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

HiSPi Test Patterns . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Test Cursors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Timing Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Power-Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Power-Down Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Hard Standby and Hard Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Soft Standby and Soft Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Soft Standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Soft Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Spectral Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

3

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

Table of Contents

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

4

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

List of Figures

List of Figures

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

Figure 1:

Pixel Color Pattern Detail (Top Right Corner) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Figure 2:

Typical Configuration: Serial Four-Lane HiSPi Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Figure 3:

Typical Configuration: Parallel Pixel Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Figure 4:

HiSPi Package Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 5:

48-Pin iLCC Parallel Package Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 6:

HiSPi Transmitter and Receiver Interface Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 7:

Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Figure 8:

Block Diagram of DLL Timing Adjustment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Figure 9:

Delaying the clock_lane with Respect to data_lane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Figure 10:

Delaying data_lane with Respect to the clock_lane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Figure 11:

Steaming vs. Packetized Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 12:

Spatial Illustration of Image Readout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 13:

Pixel Data Timing Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 14:

Row Timing and FV/LV Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 15:

Single READ From Random Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Figure 16:

Single READ From Current Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Figure 17:

Sequential READ, Start From Random Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Figure 18:

Sequential READ, Start From Current Location. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Figure 19:

Single WRITE to Random Location. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Figure 20:

Sequential WRITE, Start at Random Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Figure 21:

Effect of Limiter on the Data Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Figure 22:

Figure 23:

Timing of Data Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Figure 24: MT9J003 System States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Figure 25:

Clocking Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Sequence for Programming the MT9J003 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Figure 26:

Effect of Horizontal Mirror on Readout Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Figure 27:

Effect of Vertical Flip on Readout Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Figure 28:

Figure 29:

Pixel Array Readout Without Subsampling and With 2x2 Skipping. . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Combinations of Pixel Skipping in the MT9J003 Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Figure 30:

Pixel Binning and Summing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Figure 31:

Pixel Skipping Combined with Summing or Binning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Figure 32:

Xenon Flash Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Figure 33:

Figure 34:

LED Flash Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

LED Flash Enabled Following Forced Restart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Figure 35:

Overview of Global Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Figure 36:

Entering and Leaving a Global Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Figure 37:

Figure 38:

Controlling the Reset and Integration Phases of the Global Reset Sequence . . . . . . . . . . . . . . . . . . . .53

Control of the Electromechanical Shutter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Figure 39:

Figure 40:

Controlling the SHUTTER Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Figure 41: Using FLASH With Global Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Global Reset Bulb . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Figure 42:

Figure 43:

Entering Soft Standby During a Global Reset Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Test Cursor Behavior With Image Orientation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Figure 44:

Power-Up Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Figure 45:

Figure 46:

Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Figure 47: Hard Standby and Hard Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Figure 48:

Soft Standby and Soft Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Quantum Efficiency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Figure 49:

Two-WIre Serial Bus Timing Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Figure 50:

Figure 51:

I/O Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

Figure 52: HiSPi Eye Diagram for Both Clock and Data Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Figure 53: HiSPi Skew Between Data Signals Within the PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

48-Pin iLCC Package Outline Drawing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Figure 54:

Figure 55:

48-Pin tPLCC Package Outline Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

5

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

List of Tables

List of Tables

Table 1:

Table 2:

Table 3:

Table 4:

Table 5:

Table 6:

Table 7:

Table 8:

Table 9:

Table 10:

Table 11:

Table 12:

Table 13:

Table 14:

Table 15:

Table 16:

Table 17:

Table 18:

Table 19:

Table 20:

Table 21:

Table 22:

Table 23:

Table 24:

Table 25:

Table 26:

Table 27:

Table 28:

Table 29:

Table 30:

Table 31:

Table 32:

Table 33:

Table 34:

Table 35:

Table 36:

Table 37:

Table 38:

Available Part Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Key Performance Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Row Timing with HiSPi Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Row Timing with Parallel Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Row Timing with Parallel Interface Using Low Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Register Settings for Common Resolutions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Definitions for Programming Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Output Enable Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Configuration of the Pixel Data Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

RESET_BAR and PLL in System States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Signal State During Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Streaming/STANDBY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Trigger Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Subsampling Combinations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Minimum Row Time and Blanking Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Minimum Frame Time and Blanking Numbers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Fine_Integration_Time Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

Fine_Correction Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Recommended Gain Stages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Test Patterns . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

HiSPi Test Patterns . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Power-Up Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

CRA (13.4°) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

DC Electrical Definitions and Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Parallel Interface Configured to Use Low Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Two-Wire Serial Register Interface Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Two-Wire Serial Register Interface Timing Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

I/O Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

I/O Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

HiSPi Rise and Fall Times at 480 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

HiSPi Rise and Fall Times at 360 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

Channel, PHY and intra-PHY Skew. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Clock DLL Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

Data DLL Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

48-Pin tPLCC Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

6

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

General Description

General Description

Functional Overview

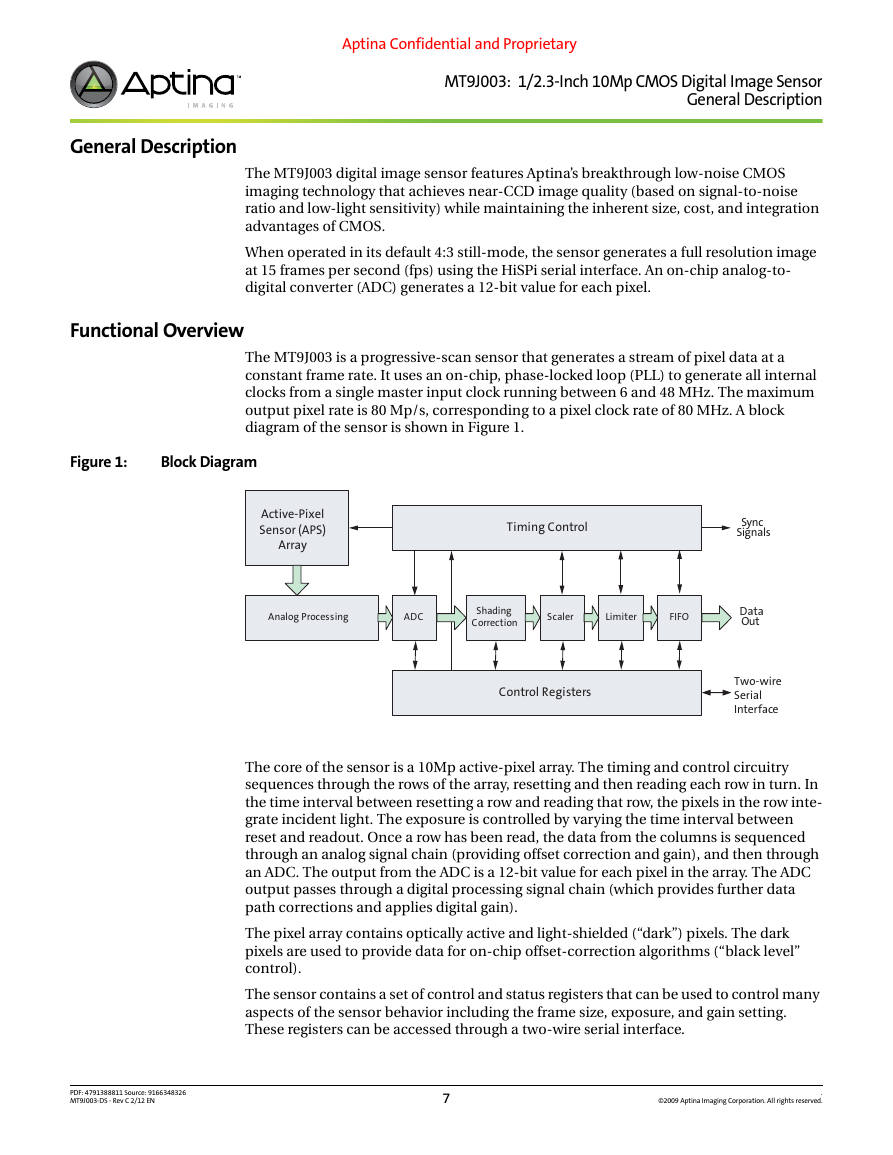

The MT9J003 digital image sensor features Aptina’s breakthrough low-noise CMOS

imaging technology that achieves near-CCD image quality (based on signal-to-noise

ratio and low-light sensitivity) while maintaining the inherent size, cost, and integration

advantages of CMOS.

When operated in its default 4:3 still-mode, the sensor generates a full resolution image

at 15 frames per second (fps) using the HiSPi serial interface. An on-chip analog-to-

digital converter (ADC) generates a 12-bit value for each pixel.

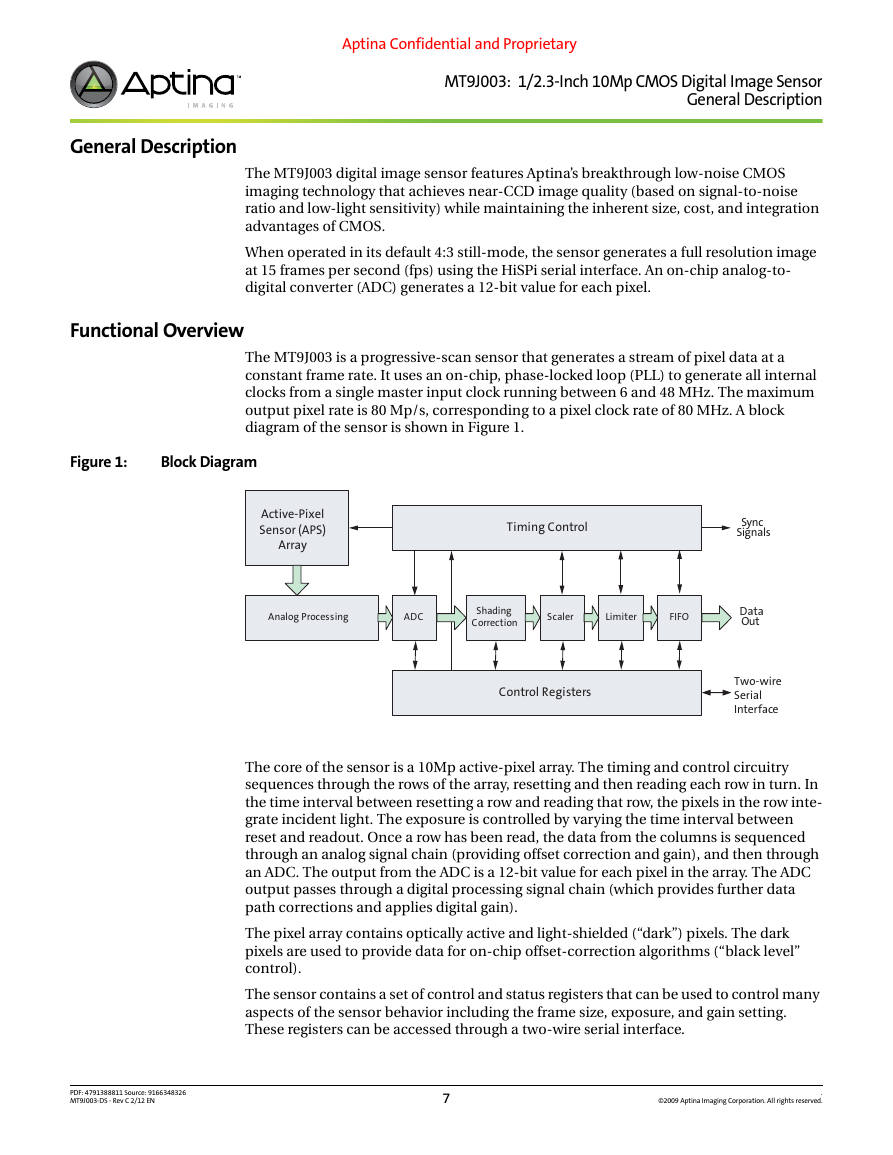

The MT9J003 is a progressive-scan sensor that generates a stream of pixel data at a

constant frame rate. It uses an on-chip, phase-locked loop (PLL) to generate all internal

clocks from a single master input clock running between 6 and 48 MHz. The maximum

output pixel rate is 80 Mp/s, corresponding to a pixel clock rate of 80 MHz. A block

diagram of the sensor is shown in Figure 1.

Figure 1:

Block Diagram

Active-Pixel

Sensor (APS)

Array

Timing Control

Analog Processing

ADC

Shading

Correction

Scaler

Limiter

FIFO

Control Registers

Sync

Signals

Data

Out

Two-wire

Serial

Interface

The core of the sensor is a 10Mp active-pixel array. The timing and control circuitry

sequences through the rows of the array, resetting and then reading each row in turn. In

the time interval between resetting a row and reading that row, the pixels in the row inte-

grate incident light. The exposure is controlled by varying the time interval between

reset and readout. Once a row has been read, the data from the columns is sequenced

through an analog signal chain (providing offset correction and gain), and then through

an ADC. The output from the ADC is a 12-bit value for each pixel in the array. The ADC

output passes through a digital processing signal chain (which provides further data

path corrections and applies digital gain).

The pixel array contains optically active and light-shielded (“dark”) pixels. The dark

pixels are used to provide data for on-chip offset-correction algorithms (“black level”

control).

The sensor contains a set of control and status registers that can be used to control many

aspects of the sensor behavior including the frame size, exposure, and gain setting.

These registers can be accessed through a two-wire serial interface.

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

7

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

Aptina Confidential and Proprietary

MT9J003: 1/2.3-Inch 10Mp CMOS Digital Image Sensor

Functional Overview

The output from the sensor is a Bayer pattern; alternate rows are a sequence of either

green and red pixels or blue and green pixels. The offset and gain stages of the analog

signal chain provide per-color control of the pixel data.

The control registers, timing and control, and digital processing functions shown in

Figure 1 on page 7 are partitioned into three logical parts:

A sensor core that provides array control and data path corrections. The output of the

sensor core is a 12-bit parallel pixel data stream qualified by an output data clock

(PIXCLK), together with LINE_VALID (LV) and FRAME_VALID (FV) signals or a 4-lane

serial high-speed pixel interface (HiSPi).

A digital shading correction block to compensate for color/brightness shading intro-

duced by the lens or chief ray angle (CRA) curve mismatch.

Additional functionality is provided. This includes a horizontal and vertical image

scaler, a limiter, a data compressor, an output FIFO, and a serializer.

The output FIFO is present to prevent data bursts by keeping the data rate continuous.

Programmable slew rates are also available to reduce the effect of electromagnetic inter-

ference from the output interface.

A flash output signal is provided to allow an external xenon or LED light source to

synchronize with the sensor exposure time. Additional I/O signals support the provision

of an external mechanical shutter.

The sensor core uses a Bayer color pattern, as shown in Figure 2. The even-numbered

rows contain green and red pixels; odd-numbered rows contain blue and green pixels.

Even-numbered columns contain green and blue pixels; odd-numbered columns

contain red and green pixels.

Pixel Array

Figure 2:

Pixel Color Pattern Detail (Top Right Corner)

Column Readout Direction

...

Black Pixels

First clear

active pixel

(110, 52)

Row

Readout

Direction

...

Gr

R

Gr

R

Gr

B

Gb

B

Gb

B

Gr

R

Gr

R

Gr

PDF: 4791388811 Source: 9166348326

MT9J003-DS - Rev C 2/12 EN

8

.

©2009 Aptina Imaging Corporation. All rights reserved.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc