D

C

B

A

5

4

3

2

1

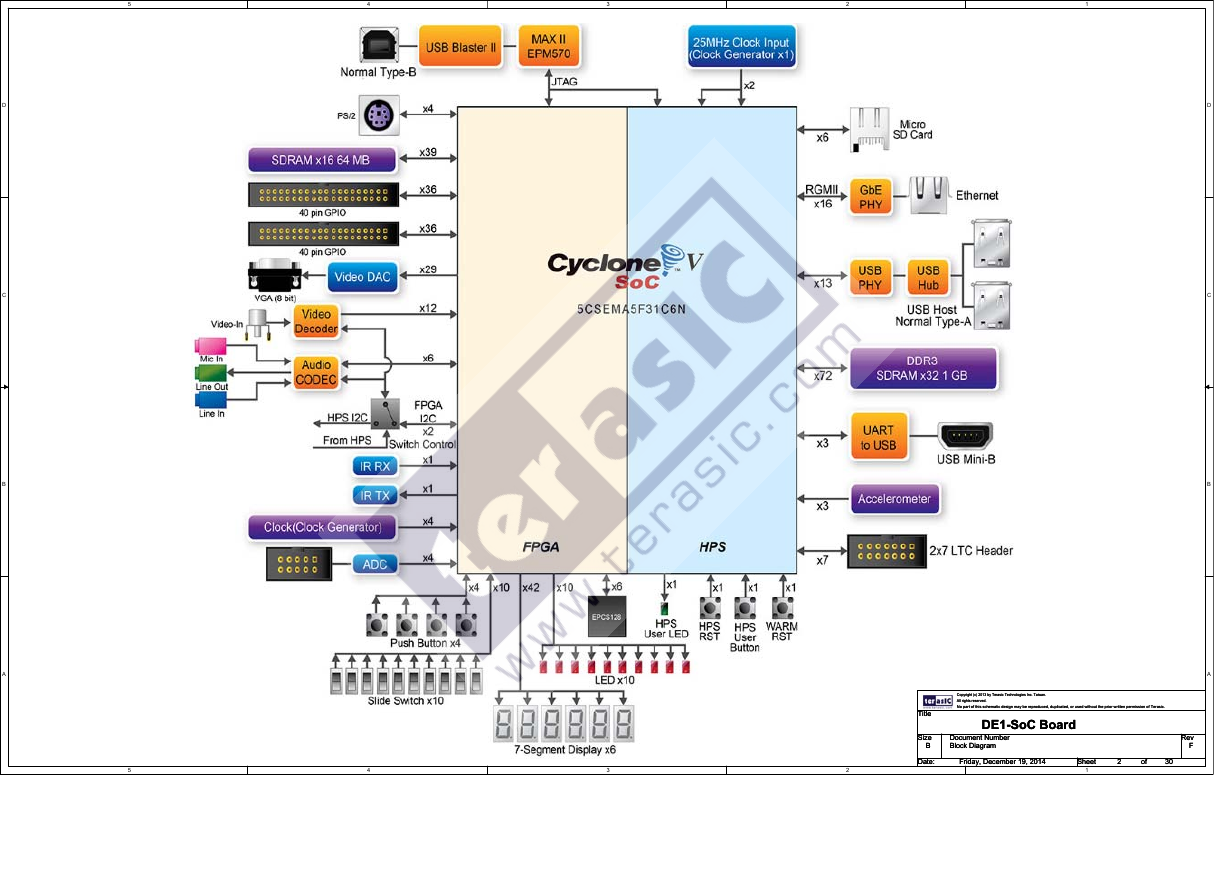

ALTERA Cyclone V SoC Development & Education Board (DE1-SoC)

PAGE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

CONTENT

Cover Page

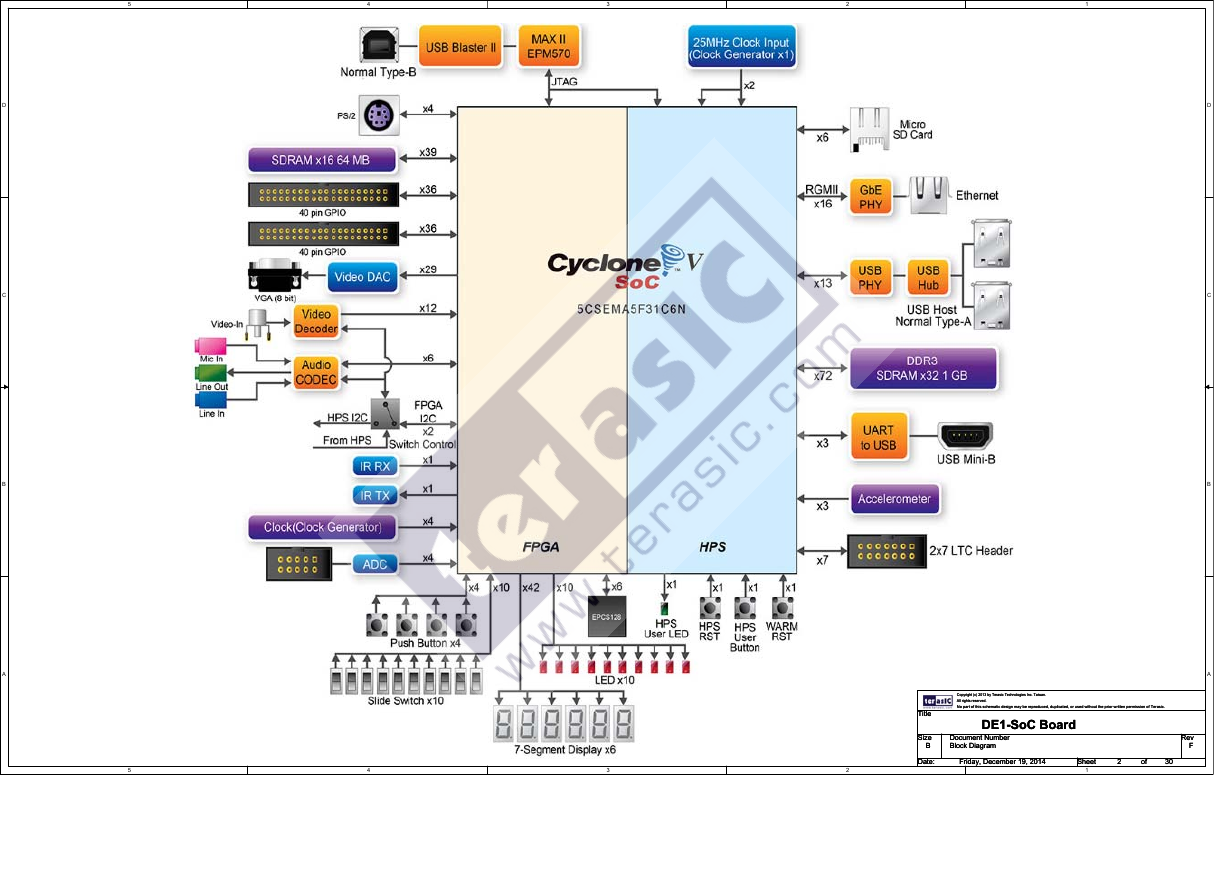

Block Diagram

FPGA BANK 3, BANK 4

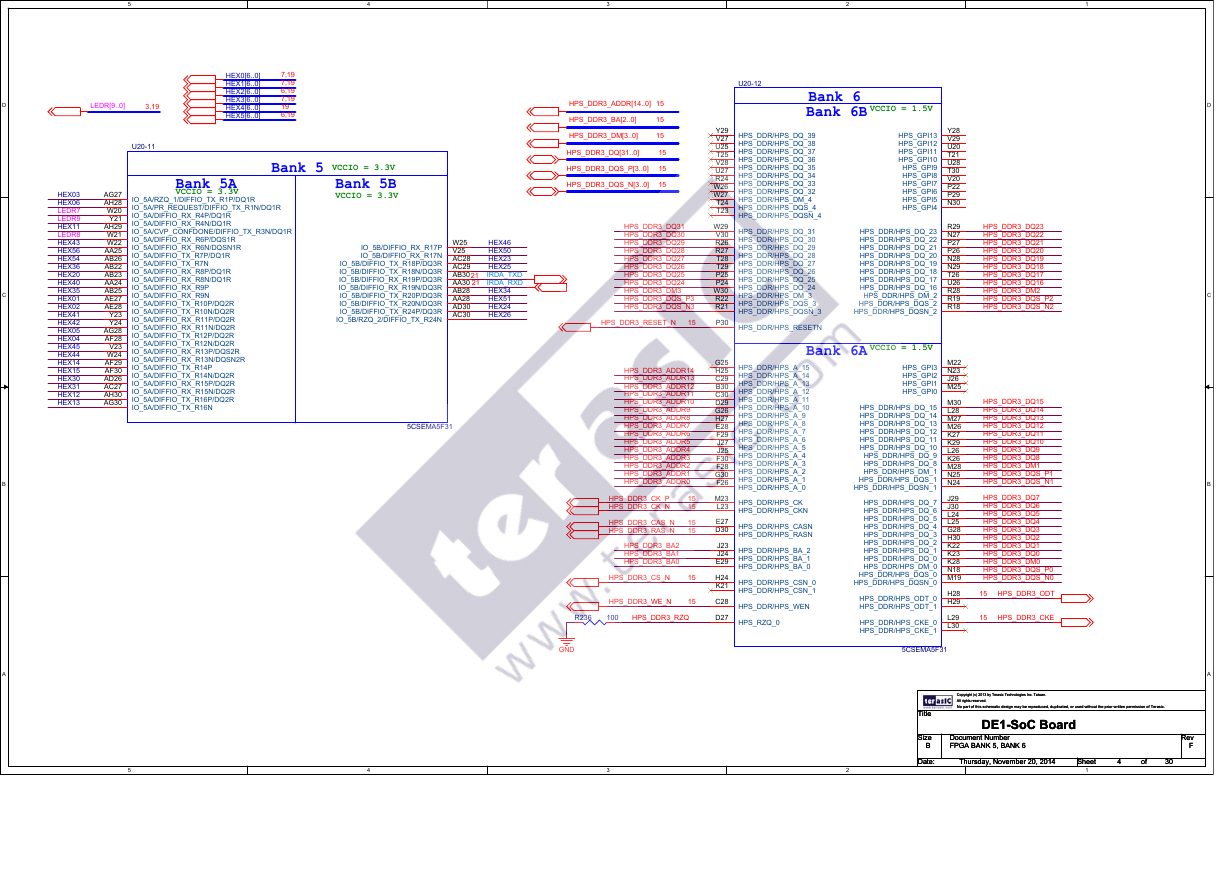

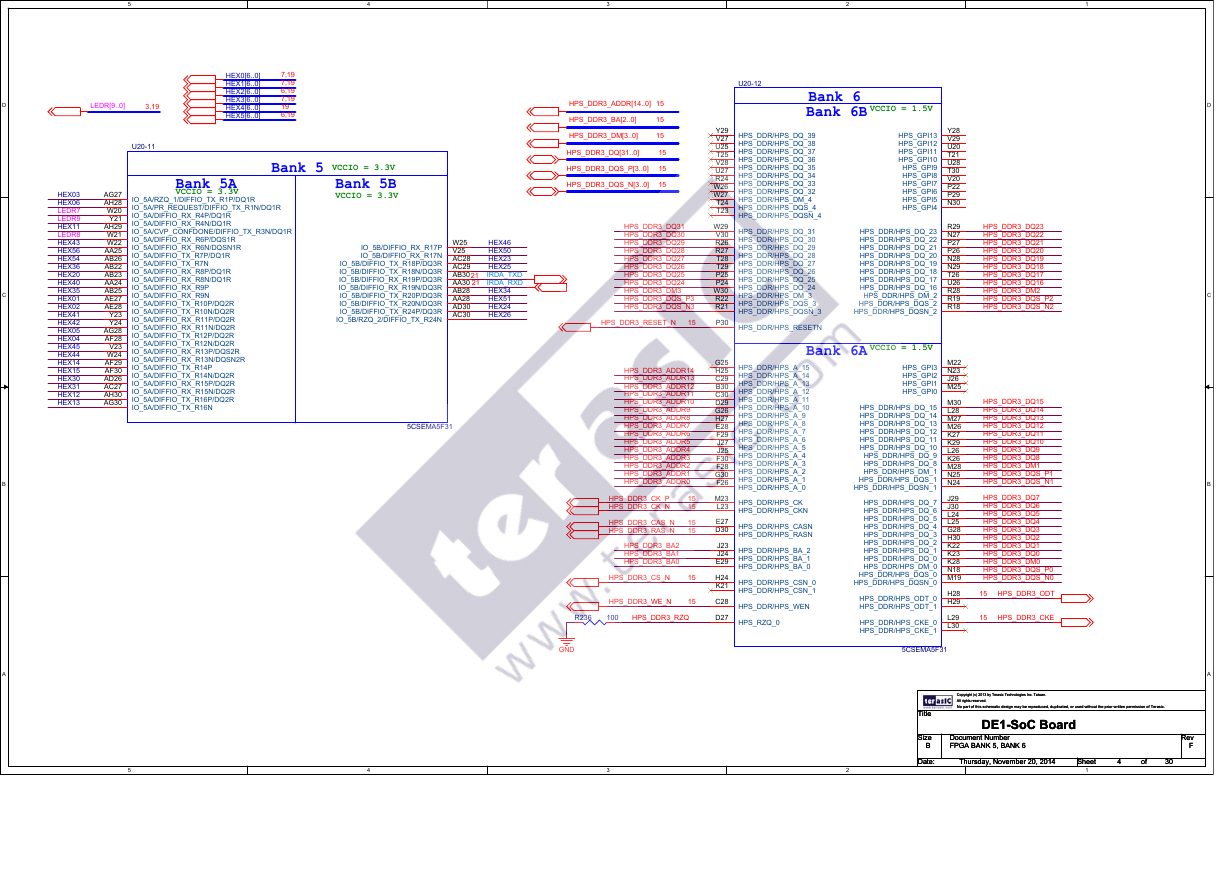

FPGA BANK 5, BANK 6

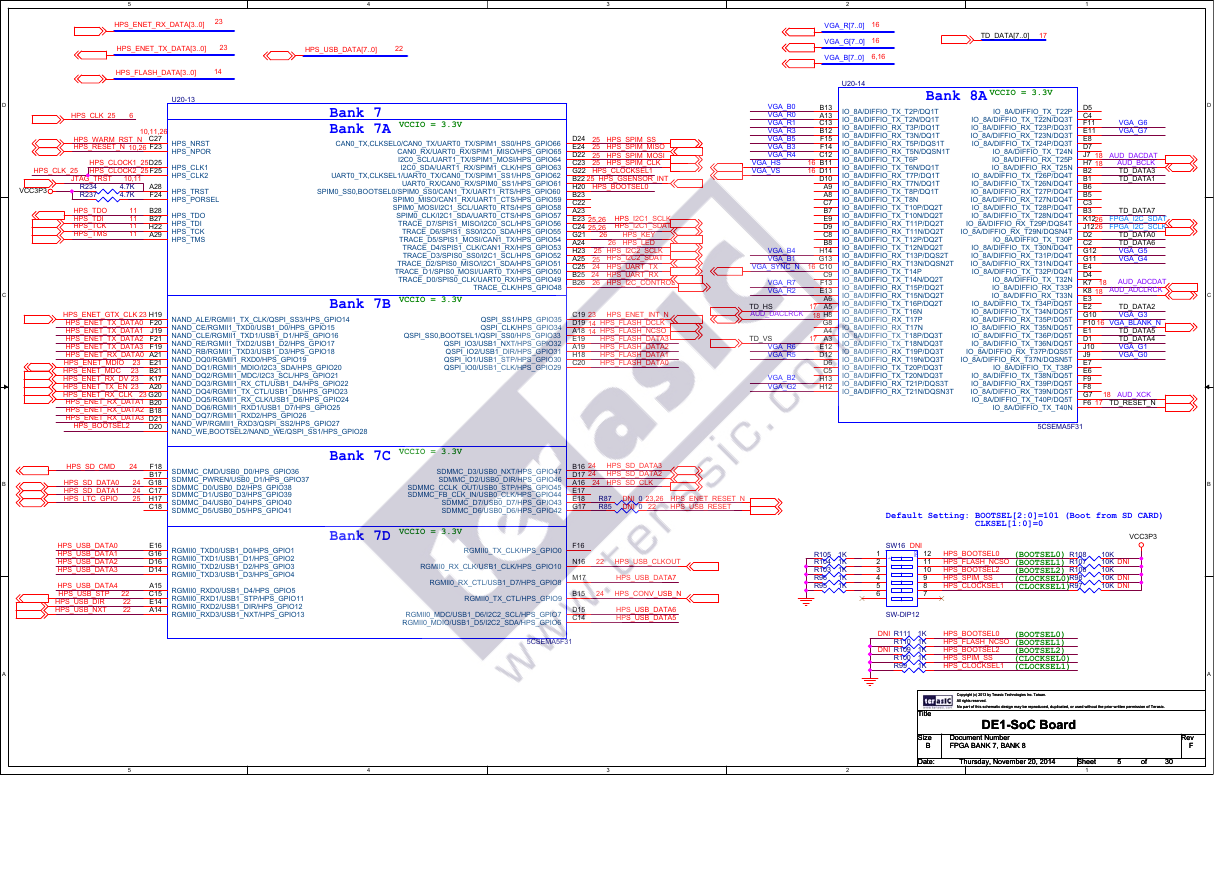

FPGA BANK 7, BANK 8

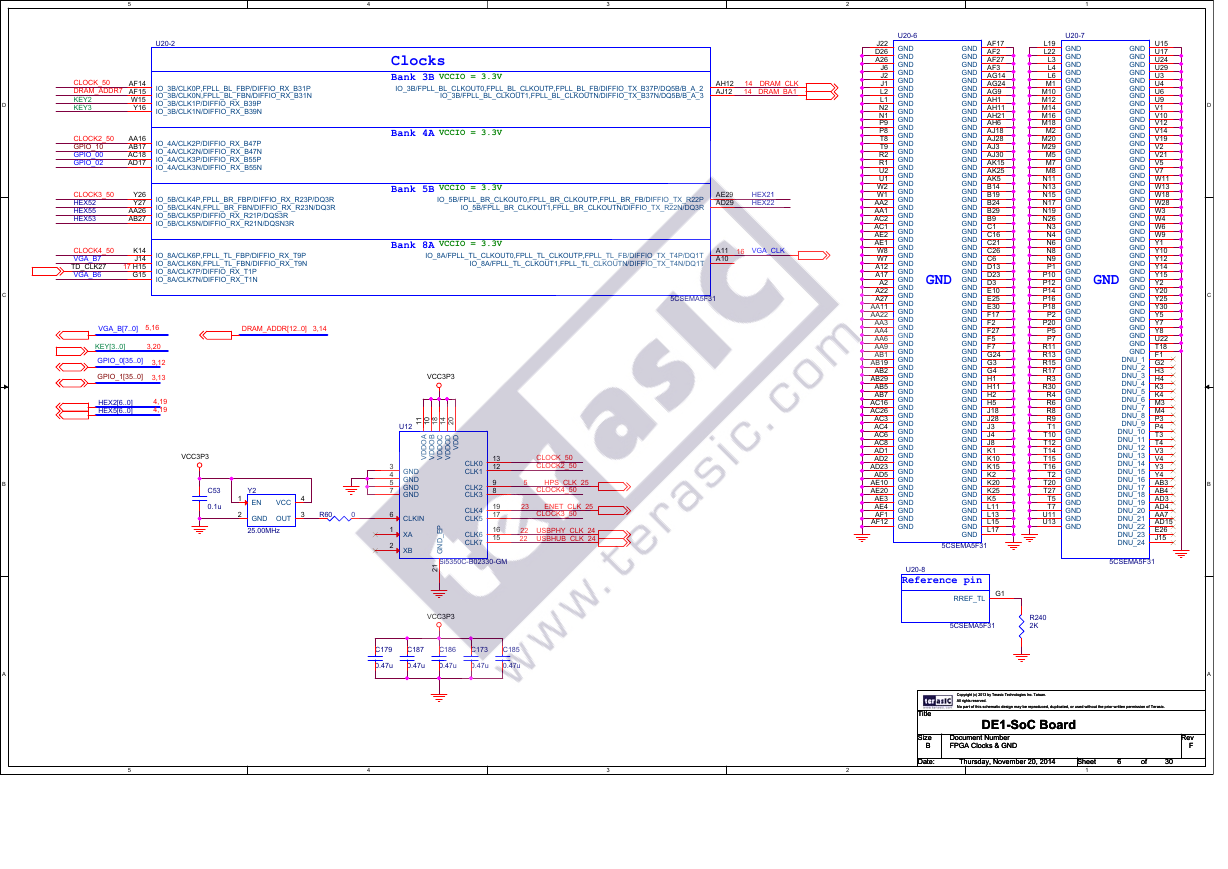

FPGA Clocks, GND

FPGA Configuration

FPGA Decoupling

FPGA Power

USB Blaster II

JTAG Chain

GPIO 0

GPIO 1

SDRAM, HPS QSPI Flash

HPS DDR3 SDRAM

PAGE

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

CONTENT

ADV7123 VGA

ADV7180 Video Decoder

Audio CODEC

7-Segment Display, LED

FPGA BUTTON, Switch

ADC, PS2, IR Tx, IR Rx

2-port USB Host

1 Gagabit Ethernet

UART to USB, SD CARD

Accelerometer, LTC Connector

I2C Multiplexer, HPS BUTTON, HPS LED

Power - 1.1V

Power - 5V, 3.3V

Power - 9V, 2.5V, 1.5V

Power - 1.2V, 1.8V, DDR3 VREF, DDR3 VTT

D

C

B

A

5

4

3

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

Cover Page

Cover Page

Cover Page

Rev

Rev

Rev

F

F

F

Thursday, November 20, 2014

Thursday, November 20, 2014

Thursday, November 20, 2014

Sheet

Sheet

Sheet

1

1

1

1

of

of

of

30

30

30

�

5

4

3

2

1

D

C

B

A

D

C

B

A

5

4

3

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

Block Diagram

Block Diagram

Block Diagram

Rev

Rev

Rev

F

F

F

Friday, December 19, 2014

Friday, December 19, 2014

Friday, December 19, 2014

Sheet

Sheet

Sheet

1

2

2

2

of

of

of

30

30

30

�

D

C

B

A

5

4

3

2

1

SW[9..0]

7,20

USB_B2_DATA[7..0]

7,10

U20-9

Bank 3A

Bank 3

VCCIO = 3.3V

Bank 3B

10

10

10

10

10

7

10

10

10

10

USB_B2_CLK

USB_EMPTY

SW2

USB_SCL

USB_SDA

USB_RESET_n

USB_B2_DATA7

USB_B2_DATA4

FAN_CTRL

SW0

USB_OE_n

USB_RD_n

USB_FULL

USB_WR_n

USB_B2_DATA3

USB_B2_DATA2

SW1

SW5

USB_B2_DATA6

USB_B2_DATA1

AF4

AF5

AF9

AG8

AF8

AG7

AG1

AH2

AA12

AB12

AF6

AG6

AG5

AH5

AJ1

AJ2

AC12

AD12

AG2

AH3

IO_3A/PR_ERROR/DIFFIO_RX_B7P

IO_3A/PR_DONE/DIFFIO_RX_B7N

IO_3A/DIFFIO_TX_B8P/DQ1B

IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1B

IO_3A/DIFFIO_TX_B9P/DQ2B

IO_3A/DIFFIO_TX_B9N

IO_3A/DIFFIO_RX_B10P/DQ2B

IO_3A/DIFFIO_RX_B10N/DQ2B

IO_3A/DIFFIO_RX_B11P/DQS2B

IO_3A/DIFFIO_RX_B11N/DQSN2B

IO_3A/DIFFIO_TX_B12P

IO_3A/DIFFIO_TX_B12N/DQ2B

IO_3A/DIFFIO_TX_B13P/DQ2B

IO_3A/DIFFIO_TX_B13N/DQ2B

IO_3A/DIFFIO_RX_B14P/DQ2B

IO_3A/DIFFIO_RX_B14N/DQ2B

IO_3A/DIFFIO_RX_B15P

IO_3A/DIFFIO_RX_B15N

IO_3A/DIFFIO_TX_B16P/DQ2B

IO_3A/DIFFIO_TX_B16N/DQ2B

IO_3B/DIFFIO_TX_B17P/DQ3B

IO_3B/DIFFIO_TX_B17N

IO_3B/DIFFIO_RX_B18P/DQ3B

IO_3B/DIFFIO_RX_B18N/DQ3B

IO_3B/DIFFIO_RX_B19P/DQS3B

IO_3B/DIFFIO_RX_B19N/DQSN3B

IO_3B/DIFFIO_TX_B20P

IO_3B/DIFFIO_TX_B20N/DQ3B

IO_3B/DIFFIO_TX_B21P/DQ3B

IO_3B/DIFFIO_TX_B21N/DQ3B

IO_3B/DIFFIO_RX_B22P/DQ3B

IO_3B/DIFFIO_RX_B22N/DQ3B

IO_3B/DIFFIO_RX_B23P

IO_3B/DIFFIO_RX_B23N

IO_3B/DIFFIO_TX_B24P/DQ3B

IO_3B/DIFFIO_TX_B24N/DQ3B

IO_3B/DIFFIO_TX_B25P/DQ4B/B_WEN

IO_3B/DIFFIO_TX_B25N/GND

IO_3B/DIFFIO_RX_B26P/DQ4B/B_A_14

IO_3B/DIFFIO_RX_B26N/DQ4B/B_A_15

IO_3B/DIFFIO_RX_B27P/DQS4B/B_CSN_0

IO_3B/DIFFIO_RX_B27N/DQSN4B/B_CSN_1

IO_3B/DIFFIO_TX_B28P/B_A_12

IO_3B/DIFFIO_TX_B28N/DQ4B/B_A_13

IO_3B/DIFFIO_TX_B29P/DQ4B/B_A_10

IO_3B/DIFFIO_TX_B29N/DQ4B/B_A_11

IO_3B/DIFFIO_RX_B30P/DQ4B/B_A_8

IO_3B/DIFFIO_RX_B30N/DQ4B/B_A_9

IO_3B/DIFFIO_TX_B32P/DQ4B/B_CASN

IO_3B/DIFFIO_TX_B32N/DQ4B/B_RASN

IO_3B/DIFFIO_TX_B33P/DQ5B/B_BA_0

IO_3B/DIFFIO_TX_B33N/GND

IO_3B/DIFFIO_RX_B34P/DQ5B/B_BA_1

IO_3B/DIFFIO_RX_B34N/DQ5B/B_BA_2

IO_3B/DIFFIO_RX_B35P/DQS5B/B_CK

IO_3B/DIFFIO_RX_B35N/DQSN5B/B_CKN

IO_3B/DIFFIO_TX_B36P/B_A_6

IO_3B/DIFFIO_TX_B36N/DQ5B/B_A_7

IO_3B/DIFFIO_RX_B38P/DQ5B/B_A_4

IO_3B/DIFFIO_RX_B38N/DQ5B/B_A_5

IO_3B/DIFFIO_TX_B40P/DQ5B/B_A_0

IO_3B/DIFFIO_TX_B40N/DQ5B/B_A_1

DRAM_ADDR[12..0] 6,14

DRAM_DQ[15..0]

14

KEY[3..0]

6,20

14

14

14

14

21

21

21

21

14

14

14

14

AG10

AH9

AF11

AG11

AA13

AB13

AK2

AK3

AJ4

AK4

AE13

AF13

AD14

AE14

AJ5

AK6

AJ6

AJ7

AG12

AG13

AB15

AC14

AK7

AK8

AJ9

AK9

AH13

AH14

AH7

AH8

AH10

AJ10

AJ11

AK11

AA14

AA15

AK12

AK13

AG15

AH15

AJ14

AK14

DRAM_DQ5

DRAM_DQ11

DRAM_CAS_N

DRAM_CS_N

DRAM_WE_N

DRAM_LDQM

ADC_SCLK

ADC_DOUT

ADC_CONVST

ADC_DIN

DRAM_RAS_N

DRAM_BA0

DRAM_ADDR6

DRAM_ADDR3

DRAM_DQ15

DRAM_DQ0

DRAM_DQ14

DRAM_DQ1

DRAM_ADDR10

DRAM_ADDR9

DRAM_ADDR4

DRAM_ADDR5

DRAM_DQ2

DRAM_DQ3

DRAM_DQ10

DRAM_DQ4

DRAM_ADDR11

DRAM_ADDR1

DRAM_DQ13

DRAM_DQ12

DRAM_DQ8

DRAM_DQ9

DRAM_DQ7

DRAM_DQ6

KEY0

KEY1

DRAM_UDQM

DRAM_CKE

DRAM_ADDR2

DRAM_ADDR8

DRAM_ADDR12

DRAM_ADDR0

5CSEMA5F31

GPIO_0[35..0]

GPIO_1[35..0]

6,12

6,13

LEDR[9..0]

4,19

U20-10

Bank 4A

VCCIO = 3.3V

IO_4A/DIFFIO_TX_B41P/DQ6B/B_DQ_2

IO_4A/RZQ_0/DIFFIO_TX_B41N

IO_4A/DIFFIO_RX_B42P/DQ6B/B_DQ_1

IO_4A/DIFFIO_RX_B42N/DQ6B/B_DQ_0

IO_4A/DIFFIO_RX_B43P/DQS6B/B_DQS_0

IO_4A/DIFFIO_RX_B43N/DQSN6B/B_DQSN_0

IO_4A/DIFFIO_TX_B44P/B_ODT_0

IO_4A/DIFFIO_TX_B44N/DQ6B/B_DQ_3

IO_4A/DIFFIO_TX_B45P/DQ6B/B_DQ_6

IO_4A/DIFFIO_TX_B45N/DQ6B/B_ODT_1

IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_5

IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_4

IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_0

IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_7

IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_10

IO_4A/DIFFIO_TX_B49N/GND

IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_9

IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_8

IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_1

IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_1

IO_4A/DIFFIO_TX_B52P/B_CKE_1

IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_11

IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_14

IO_4A/DIFFIO_TX_B53N/DQ7B/B_CKE_0

IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_13

IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_12

IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_1

IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_15

IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_18

IO_4A/DIFFIO_TX_B57N/GND

IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_17

IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_16

IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_2

IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_2

IO_4A/DIFFIO_TX_B60P/B_RESETN

IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_19

IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_22

IO_4A/DIFFIO_TX_B61N/DQ8B/GND

IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_21

IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_20

IO_4A/DIFFIO_RX_B63P/GND

IO_4A/DIFFIO_RX_B63N/GND

IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_2

IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_23

IO_4A/DIFFIO_TX_B65P/DQ9B/B_DQ_26

IO_4A/DIFFIO_TX_B65N/GND

IO_4A/DIFFIO_RX_B66P/DQ9B/B_DQ_25

IO_4A/DIFFIO_RX_B66N/DQ9B/B_DQ_24

IO_4A/DIFFIO_RX_B67P/DQS9B/B_DQS_3

IO_4A/DIFFIO_RX_B67N/DQSN9B/B_DQSN_3

IO_4A/DIFFIO_TX_B68P/GND

IO_4A/DIFFIO_TX_B68N/DQ9B/B_DQ_27

IO_4A/DIFFIO_TX_B69P/DQ9B/B_DQ_30

IO_4A/DIFFIO_TX_B69N/DQ9B/GND

IO_4A/DIFFIO_RX_B70P/DQ9B/B_DQ_29

IO_4A/DIFFIO_RX_B70N/DQ9B/B_DQ_28

IO_4A/DIFFIO_RX_B71P/GND

IO_4A/DIFFIO_RX_B71N/GND

IO_4A/DIFFIO_TX_B72P/DQ9B/B_DM_3

IO_4A/DIFFIO_TX_B72N/DQ9B/B_DQ_31

IO_4A/DIFFIO_TX_B73P/DQ10B/B_DQ_34

IO_4A/DIFFIO_TX_B73N/GND

IO_4A/DIFFIO_RX_B74P/DQ10B/B_DQ_33

IO_4A/DIFFIO_RX_B74N/DQ10B/B_DQ_32

IO_4A/DIFFIO_RX_B75P/DQS10B/B_DQS_4

IO_4A/DIFFIO_RX_B75N/DQSN10B/B_DQSN_4

IO_4A/DIFFIO_TX_B76P/GND

IO_4A/DIFFIO_TX_B76N/DQ10B/B_DQ_35

IO_4A/DIFFIO_TX_B77P/DQ10B/B_DQ_38

IO_4A/DIFFIO_TX_B77N/DQ10B/GND

IO_4A/DIFFIO_RX_B78P/DQ10B/B_DQ_37

IO_4A/DIFFIO_RX_B78N/DQ10B/B_DQ_36

IO_4A/DIFFIO_RX_B79P/GND

IO_4A/DIFFIO_RX_B79N/GND

IO_4A/DIFFIO_TX_B80P/DQ10B/B_DM_4

IO_4A/DIFFIO_TX_B80N/DQ10B/B_DQ_39

AF20

AF21

Y18

AA19

AK23

AK24

AJ24

AJ25

AF23

AF24

AC20

AD19

AJ26

AK26

AG25

AH25

AE22

AE23

V18

W19

AJ27

AK27

AK28

AK29

AD20

AD21

Y19

AA20

AG26

AH27

AF25

AF26

AC22

AC23

AA21

AB21

AD24

AE24

GPIO_012

GPIO_015

GPIO_018

GPIO_032

LEDR0

LEDR1

GPIO_013

GPIO_014

GPIO_09

GPIO_04

GPIO_031

GPIO_022

GPIO_011

GPIO_010

GPIO_034

GPIO_020

GPIO_08

GPIO_05

LEDR2

LEDR4

GPIO_07

GPIO_06

GPIO_021

GPIO_035

GPIO_030

GPIO_033

GPIO_123

GPIO_111

GPIO_129

GPIO_128

GPIO_026

GPIO_027

GPIO_01

GPIO_016

GPIO_023

GPIO_126

GPIO_125

GPIO_127

AG16

AG17

AE17

AF18

V16

W16

AE16

AF16

AJ16

AK16

AG21

AH20

AH17

AH18

AG18

AH19

AJ17

AK18

V17

W17

AJ19

AK19

AJ20

AJ21

AF19

AG20

AG23

AH24

AG22

AH22

AE18

AE19

Y17

AA18

AK21

AK22

AH23

AJ22

GPIO_028

GPIO_029

GPIO_03

GPIO_017

GPIO_124

GPIO_122

GPIO_121

GPIO_120

GPIO_131

GPIO_130

GPIO_019

GPIO_024

GPIO_117

GPIO_118

GPIO_19

GPIO_119

GPIO_132

GPIO_15

LEDR3

LEDR5

GPIO_113

GPIO_116

GPIO_115

GPIO_114

GPIO_025

GPIO_133

LEDR6

GPIO_134

GPIO_110

GPIO_112

GPIO_17

GPIO_18

GPIO_135

GPIO_13

GPIO_11

GPIO_12

GPIO_14

GPIO_16

5CSEMA5F31

D

C

B

A

5

4

3

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

FPGA BANK 3, BANK 4

FPGA BANK 3, BANK 4

FPGA BANK 3, BANK 4

Rev

Rev

Rev

F

F

F

Thursday, November 20, 2014

Thursday, November 20, 2014

Thursday, November 20, 2014

Sheet

Sheet

Sheet

1

3

3

3

of

of

of

30

30

30

�

D

C

B

A

5

4

3

2

1

LEDR[9..0]

3,19

U20-11

HEX0[6..0]

HEX1[6..0]

HEX2[6..0]

HEX3[6..0]

HEX4[6..0]

HEX5[6..0]

7,19

7,19

6,19

7,19

19

6,19

Bank 5

HEX03

HEX06

LEDR7

LEDR9

HEX11

LEDR8

HEX43

HEX56

HEX54

HEX36

HEX20

HEX40

HEX35

HEX01

HEX02

HEX41

HEX42

HEX05

HEX04

HEX45

HEX44

HEX14

HEX15

HEX30

HEX31

HEX12

HEX13

AG27

AH28

W20

Y21

AH29

W21

W22

AA25

AB26

AB22

AB23

AA24

AB25

AE27

AE28

Y23

Y24

AG28

AF28

V23

W24

AF29

AF30

AD26

AC27

AH30

AG30

Bank 5A

VCCIO = 3.3V

IO_5A/RZQ_1/DIFFIO_TX_R1P/DQ1R

IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1R

IO_5A/DIFFIO_RX_R4P/DQ1R

IO_5A/DIFFIO_RX_R4N/DQ1R

IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1R

IO_5A/DIFFIO_RX_R6P/DQS1R

IO_5A/DIFFIO_RX_R6N/DQSN1R

IO_5A/DIFFIO_TX_R7P/DQ1R

IO_5A/DIFFIO_TX_R7N

IO_5A/DIFFIO_RX_R8P/DQ1R

IO_5A/DIFFIO_RX_R8N/DQ1R

IO_5A/DIFFIO_RX_R9P

IO_5A/DIFFIO_RX_R9N

IO_5A/DIFFIO_TX_R10P/DQ2R

IO_5A/DIFFIO_TX_R10N/DQ2R

IO_5A/DIFFIO_RX_R11P/DQ2R

IO_5A/DIFFIO_RX_R11N/DQ2R

IO_5A/DIFFIO_TX_R12P/DQ2R

IO_5A/DIFFIO_TX_R12N/DQ2R

IO_5A/DIFFIO_RX_R13P/DQS2R

IO_5A/DIFFIO_RX_R13N/DQSN2R

IO_5A/DIFFIO_TX_R14P

IO_5A/DIFFIO_TX_R14N/DQ2R

IO_5A/DIFFIO_RX_R15P/DQ2R

IO_5A/DIFFIO_RX_R15N/DQ2R

IO_5A/DIFFIO_TX_R16P/DQ2R

IO_5A/DIFFIO_TX_R16N

VCCIO = 3.3V

Bank 5B

VCCIO = 3.3V

IO_5B/DIFFIO_RX_R17P

IO_5B/DIFFIO_RX_R17N

IO_5B/DIFFIO_TX_R18P/DQ3R

IO_5B/DIFFIO_TX_R18N/DQ3R

IO_5B/DIFFIO_RX_R19P/DQ3R

IO_5B/DIFFIO_RX_R19N/DQ3R

IO_5B/DIFFIO_TX_R20P/DQ3R

IO_5B/DIFFIO_TX_R20N/DQ3R

IO_5B/DIFFIO_TX_R24P/DQ3R

IO_5B/RZQ_2/DIFFIO_TX_R24N

W25

V25

AC28

AC29

AB30

AA30

AB28

AA28

AD30

AC30

21

21

HEX46

HEX50

HEX23

HEX25

IRDA_TXD

IRDA_RXD

HEX34

HEX51

HEX24

HEX26

5CSEMA5F31

HPS_DDR3_ADDR[14..0] 15

HPS_DDR3_BA[2..0]

HPS_DDR3_DM[3..0]

HPS_DDR3_DQ[31..0]

HPS_DDR3_DQS_P[3..0]

HPS_DDR3_DQS_N[3..0]

15

15

15

15

15

HPS_DDR3_DQ31

HPS_DDR3_DQ30

HPS_DDR3_DQ29

HPS_DDR3_DQ28

HPS_DDR3_DQ27

HPS_DDR3_DQ26

HPS_DDR3_DQ25

HPS_DDR3_DQ24

HPS_DDR3_DM3

HPS_DDR3_DQS_P3

HPS_DDR3_DQS_N3

U20-12

Bank 6

Bank 6B

VCCIO = 1.5V

Y29

HPS_DDR/HPS_DQ_39

V27

U25 HPS_DDR/HPS_DQ_38

HPS_DDR/HPS_DQ_37

T25

HPS_DDR/HPS_DQ_36

V28

HPS_DDR/HPS_DQ_35

U27

R24 HPS_DDR/HPS_DQ_34

HPS_DDR/HPS_DQ_33

W26

HPS_DDR/HPS_DQ_32

W27

HPS_DDR/HPS_DM_4

T24

HPS_DDR/HPS_DQS_4

T23

HPS_DDR/HPS_DQSN_4

W29

HPS_DDR/HPS_DQ_31

V30

R26 HPS_DDR/HPS_DQ_30

HPS_DDR/HPS_DQ_29

R27

HPS_DDR/HPS_DQ_28

T28

HPS_DDR/HPS_DQ_27

T29

P25 HPS_DDR/HPS_DQ_26

HPS_DDR/HPS_DQ_25

P24

HPS_DDR/HPS_DQ_24

W30

HPS_DDR/HPS_DM_3

R22

HPS_DDR/HPS_DQS_3

R21

HPS_DDR/HPS_DQSN_3

HPS_GPI13

HPS_GPI12

HPS_GPI11

HPS_GPI10

HPS_GPI9

HPS_GPI8

HPS_GPI7

HPS_GPI6

HPS_GPI5

HPS_GPI4

HPS_DDR/HPS_DQ_23

HPS_DDR/HPS_DQ_22

HPS_DDR/HPS_DQ_21

HPS_DDR/HPS_DQ_20

HPS_DDR/HPS_DQ_19

HPS_DDR/HPS_DQ_18

HPS_DDR/HPS_DQ_17

HPS_DDR/HPS_DQ_16

HPS_DDR/HPS_DM_2

HPS_DDR/HPS_DQS_2

HPS_DDR/HPS_DQSN_2

HPS_DDR3_RESET_N

15

P30

HPS_DDR/HPS_RESETN

Bank 6A

HPS_DDR3_ADDR14

HPS_DDR3_ADDR13

HPS_DDR3_ADDR12

HPS_DDR3_ADDR11

HPS_DDR3_ADDR10

HPS_DDR3_ADDR9

HPS_DDR3_ADDR8

HPS_DDR3_ADDR7

HPS_DDR3_ADDR6

HPS_DDR3_ADDR5

HPS_DDR3_ADDR4

HPS_DDR3_ADDR3

HPS_DDR3_ADDR2

HPS_DDR3_ADDR1

HPS_DDR3_ADDR0

HPS_DDR3_CK_P

HPS_DDR3_CK_N

HPS_DDR3_CAS_N

HPS_DDR3_RAS_N

HPS_DDR3_BA2

HPS_DDR3_BA1

HPS_DDR3_BA0

HPS_DDR3_CS_N

HPS_DDR3_WE_N

15

15

15

15

15

15

R236

100

HPS_DDR3_RZQ

G25

HPS_DDR/HPS_A_15

H25

C29 HPS_DDR/HPS_A_14

HPS_DDR/HPS_A_13

B30

HPS_DDR/HPS_A_12

C30

HPS_DDR/HPS_A_11

D29

HPS_DDR/HPS_A_10

G26

HPS_DDR/HPS_A_9

H27

HPS_DDR/HPS_A_8

E28

HPS_DDR/HPS_A_7

F29

HPS_DDR/HPS_A_6

J27

HPS_DDR/HPS_A_5

J25

HPS_DDR/HPS_A_4

F30

HPS_DDR/HPS_A_3

F28

HPS_DDR/HPS_A_2

G30

F26 HPS_DDR/HPS_A_1

HPS_DDR/HPS_A_0

M23

L23

E27

D30

J23

J24

E29

H24

K21

C28

D27

HPS_DDR/HPS_CK

HPS_DDR/HPS_CKN

HPS_DDR/HPS_CASN

HPS_DDR/HPS_RASN

HPS_DDR/HPS_BA_2

HPS_DDR/HPS_BA_1

HPS_DDR/HPS_BA_0

HPS_DDR/HPS_CSN_0

HPS_DDR/HPS_CSN_1

HPS_DDR/HPS_WEN

HPS_RZQ_0

VCCIO = 1.5V

HPS_GPI3

HPS_GPI2

HPS_GPI1

HPS_GPI0

HPS_DDR/HPS_DQ_15

HPS_DDR/HPS_DQ_14

HPS_DDR/HPS_DQ_13

HPS_DDR/HPS_DQ_12

HPS_DDR/HPS_DQ_11

HPS_DDR/HPS_DQ_10

HPS_DDR/HPS_DQ_9

HPS_DDR/HPS_DQ_8

HPS_DDR/HPS_DM_1

HPS_DDR/HPS_DQS_1

HPS_DDR/HPS_DQSN_1

HPS_DDR/HPS_DQ_7

HPS_DDR/HPS_DQ_6

HPS_DDR/HPS_DQ_5

HPS_DDR/HPS_DQ_4

HPS_DDR/HPS_DQ_3

HPS_DDR/HPS_DQ_2

HPS_DDR/HPS_DQ_1

HPS_DDR/HPS_DQ_0

HPS_DDR/HPS_DM_0

HPS_DDR/HPS_DQS_0

HPS_DDR/HPS_DQSN_0

HPS_DDR/HPS_ODT_0

HPS_DDR/HPS_ODT_1

HPS_DDR/HPS_CKE_0

HPS_DDR/HPS_CKE_1

Y28

V29

U20

T21

U28

T30

V20

P22

P29

N30

R29

N27

P27

P26

N28

N29

T26

U26

R28

R19

R18

M22

N23

J26

M25

M30

L28

M27

M26

K27

K29

L26

K26

M28

N25

N24

J29

J30

L24

L25

G28

H30

K22

K23

K28

N18

M19

H28

H29

L29

L30

HPS_DDR3_DQ23

HPS_DDR3_DQ22

HPS_DDR3_DQ21

HPS_DDR3_DQ20

HPS_DDR3_DQ19

HPS_DDR3_DQ18

HPS_DDR3_DQ17

HPS_DDR3_DQ16

HPS_DDR3_DM2

HPS_DDR3_DQS_P2

HPS_DDR3_DQS_N2

HPS_DDR3_DQ15

HPS_DDR3_DQ14

HPS_DDR3_DQ13

HPS_DDR3_DQ12

HPS_DDR3_DQ11

HPS_DDR3_DQ10

HPS_DDR3_DQ9

HPS_DDR3_DQ8

HPS_DDR3_DM1

HPS_DDR3_DQS_P1

HPS_DDR3_DQS_N1

HPS_DDR3_DQ7

HPS_DDR3_DQ6

HPS_DDR3_DQ5

HPS_DDR3_DQ4

HPS_DDR3_DQ3

HPS_DDR3_DQ2

HPS_DDR3_DQ1

HPS_DDR3_DQ0

HPS_DDR3_DM0

HPS_DDR3_DQS_P0

HPS_DDR3_DQS_N0

15

HPS_DDR3_ODT

15

HPS_DDR3_CKE

GND

5CSEMA5F31

5

4

3

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

FPGA BANK 5, BANK 6

FPGA BANK 5, BANK 6

FPGA BANK 5, BANK 6

Rev

Rev

Rev

F

F

F

Thursday, November 20, 2014

Thursday, November 20, 2014

Thursday, November 20, 2014

Sheet

Sheet

Sheet

1

4

4

4

of

of

of

30

30

30

D

C

B

A

�

5

4

3

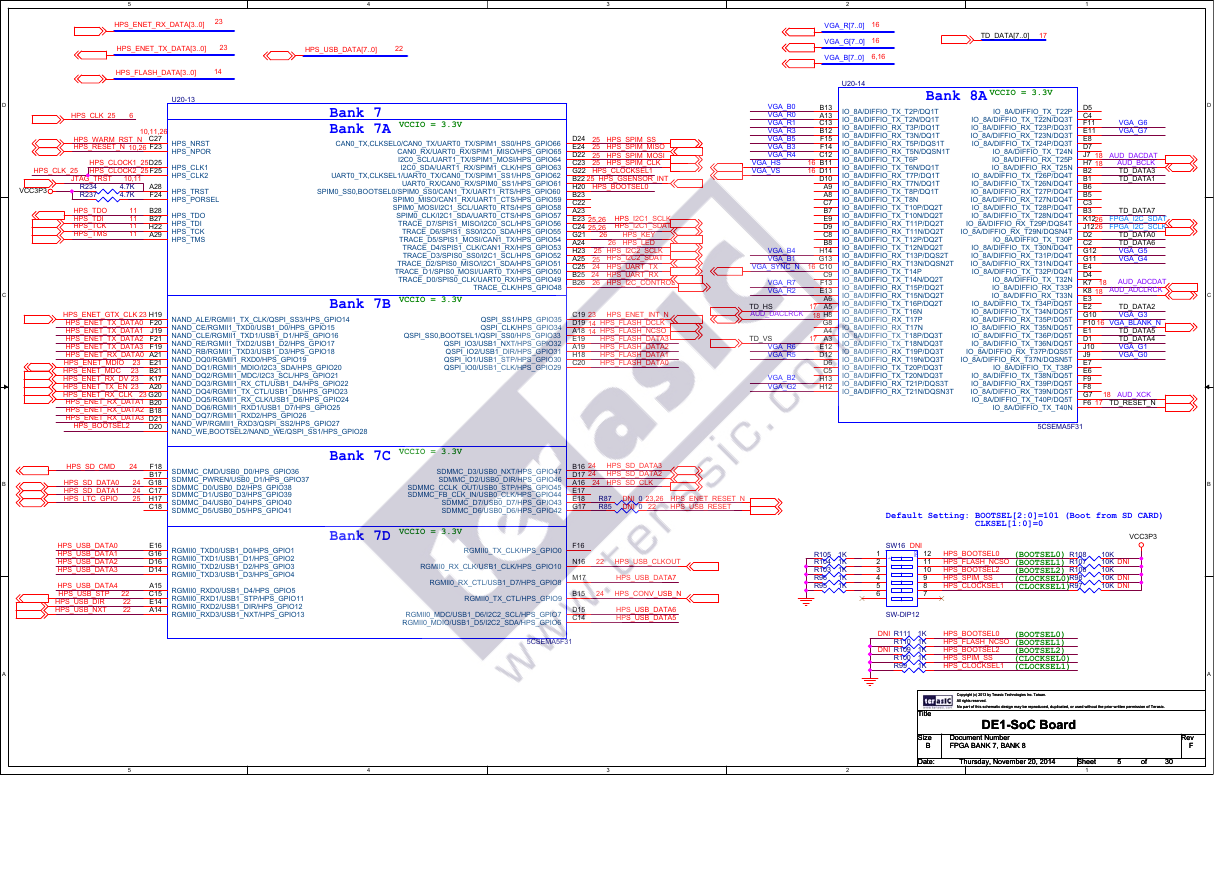

HPS_ENET_RX_DATA[3..0]

HPS_ENET_TX_DATA[3..0]

23

23

HPS_FLASH_DATA[3..0]

14

HPS_USB_DATA[7..0]

22

2

VGA_R[7..0] 16

VGA_G[7..0] 16

VGA_B[7..0] 6,16

U20-14

1

TD_DATA[7..0]

17

D24

E24

D22

C23

G22

B22

H20

B23

C22

A23

E23

C24

G21

A24

H23

A25

C25

B25

B26

C19

D19

A18

E19

A19

H18

C20

B16

D17

A16

E17

E18

G17

F16

N16

M17

B15

D15

C14

HPS_SPIM_SS

HPS_SPIM_MISO

HPS_SPIM_MOSI

HPS_SPIM_CLK

25

25

25

25

HPS_CLOCKSEL1

25

HPS_GSENSOR_INT

HPS_BOOTSEL0

25,26

25,26

26

25

25

24

24

26

HPS_I2C1_SCLK

HPS_I2C1_SDAT

HPS_KEY

HPS_LED

26

HPS_I2C2_SCLK

HPS_I2C2_SDAT

HPS_UART_TX

HPS_UART_RX

HPS_I2C_CONTROL

23

14

14

HPS_ENET_INT_N

HPS_FLASH_DCLK

HPS_FLASH_NCSO

HPS_FLASH_DATA3

HPS_FLASH_DATA2

HPS_FLASH_DATA1

HPS_FLASH_DATA0

24

24

24

HPS_SD_DATA3

HPS_SD_DATA2

HPS_SD_CLK

R87

R85

DNI

DNI

0

0

23,26

22

HPS_ENET_RESET_N

HPS_USB_RESET

22

HPS_USB_CLKOUT

HPS_USB_DATA7

24

HPS_CONV_USB_N

HPS_USB_DATA6

HPS_USB_DATA5

VGA_B0

VGA_R0

VGA_R1

VGA_R3

VGA_B5

VGA_B3

VGA_R4

VGA_HS

VGA_VS

16

16

VGA_B4

VGA_B1

VGA_SYNC_N 16

VGA_R7

VGA_R2

TD_HS

17

AUD_DACLRCK 18

TD_VS

VGA_R6

VGA_R5

17

VGA_B2

VGA_G2

B13

A13

C13

B12

F15

F14

C12

B11

D11

D10

A9

A8

C7

B7

E9

D9

C8

B8

H14

G13

C10

C9

F13

E13

A6

A5

H8

G8

A4

A3

E12

D12

D6

C5

H13

H12

Bank 8A

VCCIO = 3.3V

IO_8A/DIFFIO_TX_T2P/DQ1T

IO_8A/DIFFIO_TX_T2N/DQ1T

IO_8A/DIFFIO_RX_T3P/DQ1T

IO_8A/DIFFIO_RX_T3N/DQ1T

IO_8A/DIFFIO_RX_T5P/DQS1T

IO_8A/DIFFIO_RX_T5N/DQSN1T

IO_8A/DIFFIO_TX_T6P

IO_8A/DIFFIO_TX_T6N/DQ1T

IO_8A/DIFFIO_RX_T7P/DQ1T

IO_8A/DIFFIO_RX_T7N/DQ1T

IO_8A/DIFFIO_TX_T8P/DQ1T

IO_8A/DIFFIO_TX_T8N

IO_8A/DIFFIO_TX_T10P/DQ2T

IO_8A/DIFFIO_TX_T10N/DQ2T

IO_8A/DIFFIO_RX_T11P/DQ2T

IO_8A/DIFFIO_RX_T11N/DQ2T

IO_8A/DIFFIO_TX_T12P/DQ2T

IO_8A/DIFFIO_TX_T12N/DQ2T

IO_8A/DIFFIO_RX_T13P/DQS2T

IO_8A/DIFFIO_RX_T13N/DQSN2T

IO_8A/DIFFIO_TX_T14P

IO_8A/DIFFIO_TX_T14N/DQ2T

IO_8A/DIFFIO_RX_T15P/DQ2T

IO_8A/DIFFIO_RX_T15N/DQ2T

IO_8A/DIFFIO_TX_T16P/DQ2T

IO_8A/DIFFIO_TX_T16N

IO_8A/DIFFIO_RX_T17P

IO_8A/DIFFIO_RX_T17N

IO_8A/DIFFIO_TX_T18P/DQ3T

IO_8A/DIFFIO_TX_T18N/DQ3T

IO_8A/DIFFIO_RX_T19P/DQ3T

IO_8A/DIFFIO_RX_T19N/DQ3T

IO_8A/DIFFIO_TX_T20P/DQ3T

IO_8A/DIFFIO_TX_T20N/DQ3T

IO_8A/DIFFIO_RX_T21P/DQS3T

IO_8A/DIFFIO_RX_T21N/DQSN3T

IO_8A/DIFFIO_TX_T22P

IO_8A/DIFFIO_TX_T22N/DQ3T

IO_8A/DIFFIO_RX_T23P/DQ3T

IO_8A/DIFFIO_RX_T23N/DQ3T

IO_8A/DIFFIO_TX_T24P/DQ3T

IO_8A/DIFFIO_TX_T24N

IO_8A/DIFFIO_RX_T25P

IO_8A/DIFFIO_RX_T25N

IO_8A/DIFFIO_TX_T26P/DQ4T

IO_8A/DIFFIO_TX_T26N/DQ4T

IO_8A/DIFFIO_RX_T27P/DQ4T

IO_8A/DIFFIO_RX_T27N/DQ4T

IO_8A/DIFFIO_TX_T28P/DQ4T

IO_8A/DIFFIO_TX_T28N/DQ4T

IO_8A/DIFFIO_RX_T29P/DQS4T

IO_8A/DIFFIO_RX_T29N/DQSN4T

IO_8A/DIFFIO_TX_T30P

IO_8A/DIFFIO_TX_T30N/DQ4T

IO_8A/DIFFIO_RX_T31P/DQ4T

IO_8A/DIFFIO_RX_T31N/DQ4T

IO_8A/DIFFIO_TX_T32P/DQ4T

IO_8A/DIFFIO_TX_T32N

IO_8A/DIFFIO_RX_T33P

IO_8A/DIFFIO_RX_T33N

IO_8A/DIFFIO_TX_T34P/DQ5T

IO_8A/DIFFIO_TX_T34N/DQ5T

IO_8A/DIFFIO_RX_T35P/DQ5T

IO_8A/DIFFIO_RX_T35N/DQ5T

IO_8A/DIFFIO_TX_T36P/DQ5T

IO_8A/DIFFIO_TX_T36N/DQ5T

IO_8A/DIFFIO_RX_T37P/DQS5T

IO_8A/DIFFIO_RX_T37N/DQSN5T

IO_8A/DIFFIO_TX_T38P

IO_8A/DIFFIO_TX_T38N/DQ5T

IO_8A/DIFFIO_RX_T39P/DQ5T

IO_8A/DIFFIO_RX_T39N/DQ5T

IO_8A/DIFFIO_TX_T40P/DQ5T

IO_8A/DIFFIO_TX_T40N

D5

C4

F11

E11

E8

D7

J7

H7

B2

B1

B6

B5

C3

B3

K12

J12

D2

C2

G12

G11

E4

D4

K7

K8

E3

E2

G10

F10

E1

D1

J10

J9

E7

E6

F9

F8

G7

F6

VGA_G6

VGA_G7

AUD_DACDAT

AUD_BCLK

TD_DATA3

TD_DATA1

TD_DATA7

FPGA_I2C_SDAT

FPGA_I2C_SCLK

TD_DATA0

TD_DATA6

VGA_G5

VGA_G4

AUD_ADCDAT

AUD_ADCLRCK

18

18

26

26

18

18

16

VGA_BLANK_N

TD_DATA2

VGA_G3

TD_DATA5

TD_DATA4

VGA_G1

VGA_G0

18

AUD_XCK

TD_RESET_N

17

5CSEMA5F31

Default Setting: BOOTSEL[2:0]=101 (Boot from SD CARD)

CLKSEL[1:0]=0

R105 1K

R104 1K

R103 1K

R96

1K

1K

R95

SW16

DNI

O

N

1

12

11

10

9

8

7

1

2

3

4

5

6

SW-DIP12

DNI

DNI

R111 1K

R110 1K

R109 1K

R100 1K

R99

1K

VCC3P3

HPS_BOOTSEL0

HPS_FLASH_NCSO

HPS_BOOTSEL2

HPS_SPIM_SS

HPS_CLOCKSEL1

(BOOTSEL0)

(BOOTSEL1)

(BOOTSEL2)

(CLOCKSEL0)

(CLOCKSEL1)

R108

R107

R106

R98

R97

10K

10K DNI

10K

10K DNI

10K DNI

HPS_BOOTSEL0

HPS_FLASH_NCSO

HPS_BOOTSEL2

HPS_SPIM_SS

HPS_CLOCKSEL1

(BOOTSEL0)

(BOOTSEL1)

(BOOTSEL2)

(CLOCKSEL0)

(CLOCKSEL1)

D

C

B

A

HPS_CLK_25

6

10,11,26

HPS_WARM_RST_N

HPS_RESET_N 10,26

HPS_CLOCK1_25

HPS_CLOCK2_25

JTAG_TRST

R234

R237

10,11

4.7K

4.7K

C27

F23

D25

F25

A28

F24

HPS_CLK_25

VCC3P3

U20-13

HPS_NRST

HPS_NPOR

HPS_CLK1

HPS_CLK2

HPS_TRST

HPS_PORSEL

HPS_TDO

HPS_TDI

HPS_TCK

HPS_TMS

11

11

11

11

B28

HPS_TDO

B27

HPS_TDI

H22

A29 HPS_TCK

HPS_TMS

Bank 7

Bank 7A

VCCIO = 3.3V

CAN0_TX,CLKSEL0/CAN0_TX/UART0_TX/SPIM1_SS0/HPS_GPIO66

CAN0_RX/UART0_RX/SPIM1_MISO/HPS_GPIO65

I2C0_SCL/UART1_TX/SPIM1_MOSI/HPS_GPIO64

I2C0_SDA/UART1_RX/SPIM1_CLK/HPS_GPIO63

UART0_TX,CLKSEL1/UART0_TX/CAN0_TX/SPIM1_SS1/HPS_GPIO62

UART0_RX/CAN0_RX/SPIM0_SS1/HPS_GPIO61

SPIM0_SS0,BOOTSEL0/SPIM0_SS0/CAN1_TX/UART1_RTS/HPS_GPIO60

SPIM0_MISO/CAN1_RX/UART1_CTS/HPS_GPIO59

SPIM0_MOSI/I2C1_SCL/UART0_RTS/HPS_GPIO58

SPIM0_CLK/I2C1_SDA/UART0_CTS/HPS_GPIO57

TRACE_D7/SPIS1_MISO/I2C0_SCL/HPS_GPIO56

TRACE_D6/SPIS1_SS0/I2C0_SDA/HPS_GPIO55

TRACE_D5/SPIS1_MOSI/CAN1_TX/HPS_GPIO54

TRACE_D4/SPIS1_CLK/CAN1_RX/HPS_GPIO53

TRACE_D3/SPIS0_SS0/I2C1_SCL/HPS_GPIO52

TRACE_D2/SPIS0_MISO/I2C1_SDA/HPS_GPIO51

TRACE_D1/SPIS0_MOSI/UART0_TX/HPS_GPIO50

TRACE_D0/SPIS0_CLK/UART0_RX/HPS_GPIO49

TRACE_CLK/HPS_GPIO48

VCCIO = 3.3V

Bank 7B

HPS_ENET_GTX_CLK 23

HPS_ENET_TX_DATA0

HPS_ENET_TX_DATA1

HPS_ENET_TX_DATA2

HPS_ENET_TX_DATA3

HPS_ENET_RX_DATA0

HPS_ENET_MDIO 23

HPS_ENET_MDC 23

HPS_ENET_RX_DV 23

HPS_ENET_TX_EN 23

HPS_ENET_RX_CLK 23

HPS_ENET_RX_DATA1

HPS_ENET_RX_DATA2

HPS_ENET_RX_DATA3

HPS_BOOTSEL2

H19

F20

J19

F21

F19

A21

E21

B21

K17

A20

G20

B20

B18

D21

D20

HPS_SD_CMD

24

HPS_SD_DATA0

HPS_SD_DATA1

HPS_LTC_GPIO

24

24

25

HPS_USB_DATA0

HPS_USB_DATA1

HPS_USB_DATA2

HPS_USB_DATA3

HPS_USB_DATA4

HPS_USB_STP

HPS_USB_DIR

HPS_USB_NXT

22

22

22

F18

B17

G18

C17

H17

C18

E16

G16

D16

D14

A15

C15

E14

A14

NAND_ALE/RGMII1_TX_CLK/QSPI_SS3/HPS_GPIO14

NAND_CE/RGMII1_TXD0/USB1_D0/HPS_GPIO15

NAND_CLE/RGMII1_TXD1/USB1_D1/HPS_GPIO16

NAND_RE/RGMII1_TXD2/USB1_D2/HPS_GPIO17

NAND_RB/RGMII1_TXD3/USB1_D3/HPS_GPIO18

NAND_DQ0/RGMII1_RXD0/HPS_GPIO19

NAND_DQ1/RGMII1_MDIO/I2C3_SDA/HPS_GPIO20

NAND_DQ2/RGMII1_MDC/I2C3_SCL/HPS_GPIO21

NAND_DQ3/RGMII1_RX_CTL/USB1_D4/HPS_GPIO22

NAND_DQ4/RGMII1_TX_CTL/USB1_D5/HPS_GPIO23

NAND_DQ5/RGMII1_RX_CLK/USB1_D6/HPS_GPIO24

NAND_DQ6/RGMII1_RXD1/USB1_D7/HPS_GPIO25

NAND_DQ7/RGMII1_RXD2/HPS_GPIO26

NAND_WP/RGMII1_RXD3/QSPI_SS2/HPS_GPIO27

NAND_WE,BOOTSEL2/NAND_WE/QSPI_SS1/HPS_GPIO28

Bank 7C

SDMMC_CMD/USB0_D0/HPS_GPIO36

SDMMC_PWREN/USB0_D1/HPS_GPIO37

SDMMC_D0/USB0_D2/HPS_GPIO38

SDMMC_D1/USB0_D3/HPS_GPIO39

SDMMC_D4/USB0_D4/HPS_GPIO40

SDMMC_D5/USB0_D5/HPS_GPIO41

RGMII0_TXD0/USB1_D0/HPS_GPIO1

RGMII0_TXD1/USB1_D1/HPS_GPIO2

RGMII0_TXD2/USB1_D2/HPS_GPIO3

RGMII0_TXD3/USB1_D3/HPS_GPIO4

RGMII0_RXD0/USB1_D4/HPS_GPIO5

RGMII0_RXD1/USB1_STP/HPS_GPIO11

RGMII0_RXD2/USB1_DIR/HPS_GPIO12

RGMII0_RXD3/USB1_NXT/HPS_GPIO13

Bank 7D

QSPI_SS1/HPS_GPIO35

QSPI_CLK/HPS_GPIO34

QSPI_SS0,BOOTSEL1/QSPI_SS0/HPS_GPIO33

QSPI_IO3/USB1_NXT/HPS_GPIO32

QSPI_IO2/USB1_DIR/HPS_GPIO31

QSPI_IO1/USB1_STP/HPS_GPIO30

QSPI_IO0/USB1_CLK/HPS_GPIO29

VCCIO = 3.3V

SDMMC_D3/USB0_NXT/HPS_GPIO47

SDMMC_D2/USB0_DIR/HPS_GPIO46

SDMMC_CCLK_OUT/USB0_STP/HPS_GPIO45

SDMMC_FB_CLK_IN/USB0_CLK/HPS_GPIO44

SDMMC_D7/USB0_D7/HPS_GPIO43

SDMMC_D6/USB0_D6/HPS_GPIO42

VCCIO = 3.3V

RGMII0_TX_CLK/HPS_GPIO0

RGMII0_RX_CLK/USB1_CLK/HPS_GPIO10

RGMII0_RX_CTL/USB1_D7/HPS_GPIO8

RGMII0_TX_CTL/HPS_GPIO9

RGMII0_MDC/USB1_D6/I2C2_SCL/HPS_GPIO7

RGMII0_MDIO/USB1_D5/I2C2_SDA/HPS_GPIO6

5CSEMA5F31

D

C

B

A

5

4

3

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

FPGA BANK 7, BANK 8

FPGA BANK 7, BANK 8

FPGA BANK 7, BANK 8

Rev

Rev

Rev

F

F

F

Thursday, November 20, 2014

Thursday, November 20, 2014

Thursday, November 20, 2014

Sheet

Sheet

Sheet

1

5

5

5

of

of

of

30

30

30

�

D

C

B

A

5

4

3

2

1

U20-2

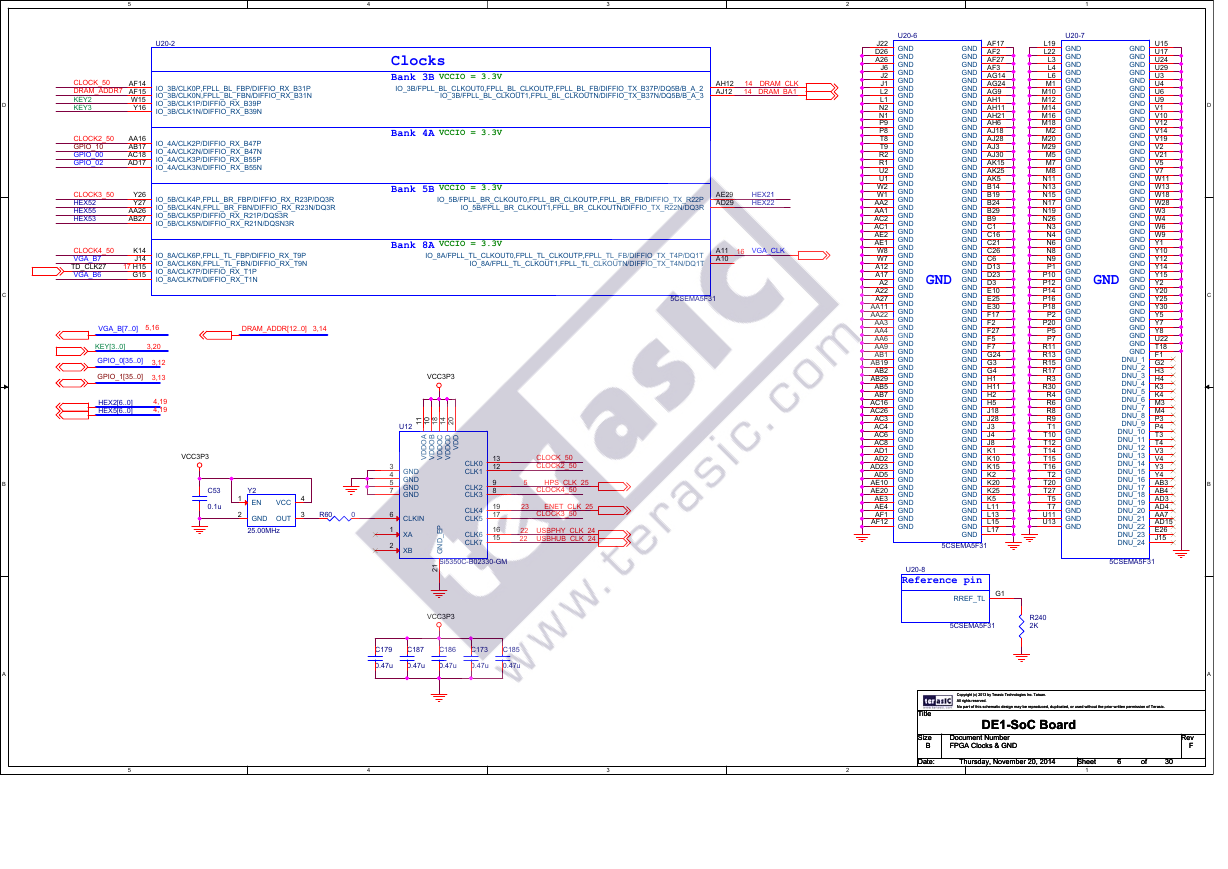

CLOCK_50

DRAM_ADDR7

KEY2

KEY3

AF14

AF15

W15

Y16

IO_3B/CLK0P,FPLL_BL_FBP/DIFFIO_RX_B31P

IO_3B/CLK0N,FPLL_BL_FBN/DIFFIO_RX_B31N

IO_3B/CLK1P/DIFFIO_RX_B39P

IO_3B/CLK1N/DIFFIO_RX_B39N

CLOCK2_50

GPIO_10

GPIO_00

GPIO_02

CLOCK3_50

HEX52

HEX55

HEX53

AA16

AB17

AC18

AD17

Y26

Y27

AA26

AB27

IO_4A/CLK2P/DIFFIO_RX_B47P

IO_4A/CLK2N/DIFFIO_RX_B47N

IO_4A/CLK3P/DIFFIO_RX_B55P

IO_4A/CLK3N/DIFFIO_RX_B55N

IO_5B/CLK4P,FPLL_BR_FBP/DIFFIO_RX_R23P/DQ3R

IO_5B/CLK4N,FPLL_BR_FBN/DIFFIO_RX_R23N/DQ3R

IO_5B/CLK5P/DIFFIO_RX_R21P/DQS3R

IO_5B/CLK5N/DIFFIO_RX_R21N/DQSN3R

CLOCK4_50

VGA_B7

TD_CLK27

VGA_B6

K14

J14

H15

G15

17

IO_8A/CLK6P,FPLL_TL_FBP/DIFFIO_RX_T9P

IO_8A/CLK6N,FPLL_TL_FBN/DIFFIO_RX_T9N

IO_8A/CLK7P/DIFFIO_RX_T1P

IO_8A/CLK7N/DIFFIO_RX_T1N

Clocks

Bank 3B

VCCIO = 3.3V

IO_3B/FPLL_BL_CLKOUT0,FPLL_BL_CLKOUTP,FPLL_BL_FB/DIFFIO_TX_B37P/DQ5B/B_A_2

IO_3B/FPLL_BL_CLKOUT1,FPLL_BL_CLKOUTN/DIFFIO_TX_B37N/DQ5B/B_A_3

AH12

AJ12

14

14

DRAM_CLK

DRAM_BA1

Bank 4A

VCCIO = 3.3V

Bank 5B

VCCIO = 3.3V

IO_5B/FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTP,FPLL_BR_FB/DIFFIO_TX_R22P

IO_5B/FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTN/DIFFIO_TX_R22N/DQ3R

AE29

AD29

HEX21

HEX22

Bank 8A

VCCIO = 3.3V

IO_8A/FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTP,FPLL_TL_FB/DIFFIO_TX_T4P/DQ1T

IO_8A/FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTN/DIFFIO_TX_T4N/DQ1T

16

VGA_CLK

A11

A10

VGA_B[7..0] 5,16

KEY[3..0]

3,20

GPIO_0[35..0]

GPIO_1[35..0]

HEX2[6..0]

HEX5[6..0]

3,12

3,13

4,19

4,19

DRAM_ADDR[12..0] 3,14

VCC3P3

5CSEMA5F31

VCC3P3

C53

0.1u

1

2

Y2

EN

VCC

OUT

GND

25.00MHz

4

3

R60

0

1

1

0

1

8

1

4

1

0

2

U12

A

O

D

D

V

B

O

D

D

V

C

O

D

D

V

D

O

D

D

V

D

D

V

3

4

5

7

6

1

2

GND

GND

GND

GND

CLKIN

XA

XB

13

12

9

8

19

17

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLOCK_50

CLOCK2_50

5

23

HPS_CLK_25

CLOCK4_50

ENET_CLK_25

CLOCK3_50

22

22

USBPHY_CLK_24

USBHUB_CLK_24

16

15

CLK6

CLK7

P

E

_

D

N

G

Si5350C-B02330-GM

1

2

VCC3P3

C179

0.47u

C187

0.47u

C186

0.47u

C173

0.47u

C185

0.47u

5

4

3

2

J22

D26

A26

J6

J2

J1

L2

L1

N2

N1

P9

P8

T8

T9

R2

R1

U2

U1

W2

W1

AA2

AA1

AC2

AC1

AE2

AE1

W8

W7

A12

A17

A2

A22

A27

AA11

AA22

AA3

AA4

AA6

AA9

AB1

AB19

AB2

AB29

AB5

AB7

AC16

AC26

AC3

AC4

AC6

AC8

AD1

AD2

AD23

AD5

AE10

AE20

AE3

AE4

AF1

AF12

U20-6

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AF17

AF2

AF27

AF3

AG14

AG24

AG9

AH1

AH11

AH21

AH6

AJ18

AJ28

AJ3

AJ30

AK15

AK25

AK5

B14

B19

B24

B29

B9

C1

C16

C21

C26

C6

D13

D23

D3

E10

E25

E30

F17

F2

F27

F5

F7

G24

G3

G4

H1

H11

H2

H5

J18

J28

J3

J4

J8

K1

K10

K15

K2

K20

K25

K5

L11

L13

L15

L17

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

L19

L22

L3

L4

L6

M1

M10

M12

M14

M16

M18

M2

M20

M29

M5

M7

M8

N11

N13

N15

N17

N19

N26

N3

N4

N6

N8

N9

P1

P10

P12

P14

P16

P18

P2

P20

P5

P7

R11

R13

R15

R17

R3

R30

R4

R6

R8

R9

T1

T10

T12

T14

T15

T16

T2

T20

T27

T5

T7

U11

U13

U20-7

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

5CSEMA5F31

U20-8

Reference pin

RREF_TL

G1

5CSEMA5F31

R240

2K

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DNU_1

DNU_2

DNU_3

DNU_4

DNU_5

DNU_6

DNU_7

DNU_8

DNU_9

DNU_10

DNU_11

DNU_12

DNU_13

DNU_14

DNU_15

DNU_16

DNU_17

DNU_18

DNU_19

DNU_20

DNU_21

DNU_22

DNU_23

DNU_24

U15

U17

U24

U29

U3

U4

U6

U9

V1

V10

V12

V14

V19

V2

V21

V5

V7

W11

W13

W18

W28

W3

W4

W6

W9

Y1

Y10

Y12

Y14

Y15

Y2

Y20

Y25

Y30

Y5

Y7

Y8

U22

T18

F1

G2

H3

H4

K3

K4

M3

M4

P3

P4

T3

T4

V3

V4

Y3

Y4

AB3

AB4

AD3

AD4

AA7

AD15

E26

J15

5CSEMA5F31

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

FPGA Clocks & GND

FPGA Clocks & GND

FPGA Clocks & GND

Rev

Rev

Rev

F

F

F

Thursday, November 20, 2014

Thursday, November 20, 2014

Thursday, November 20, 2014

Sheet

Sheet

Sheet

1

6

6

6

of

of

of

30

30

30

D

C

B

A

�

D

C

B

A

5

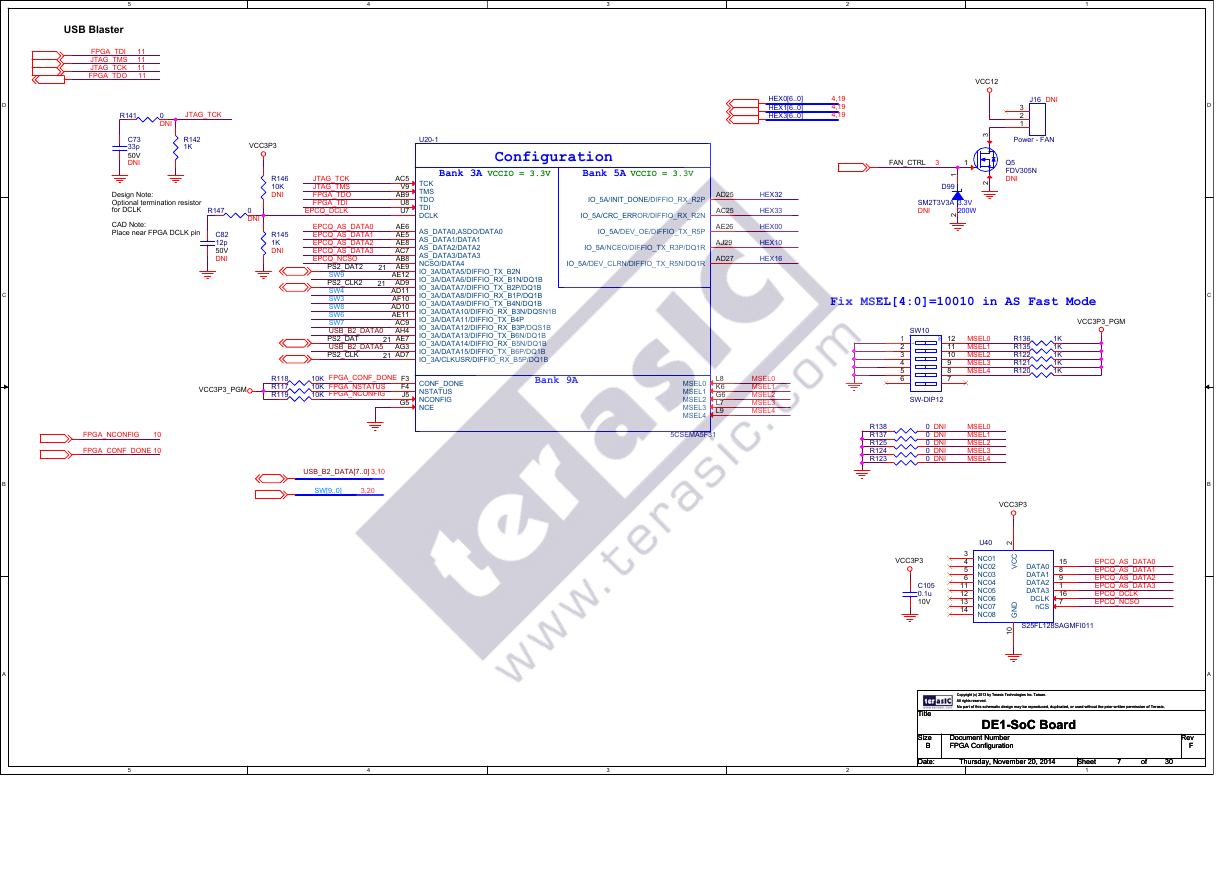

USB Blaster

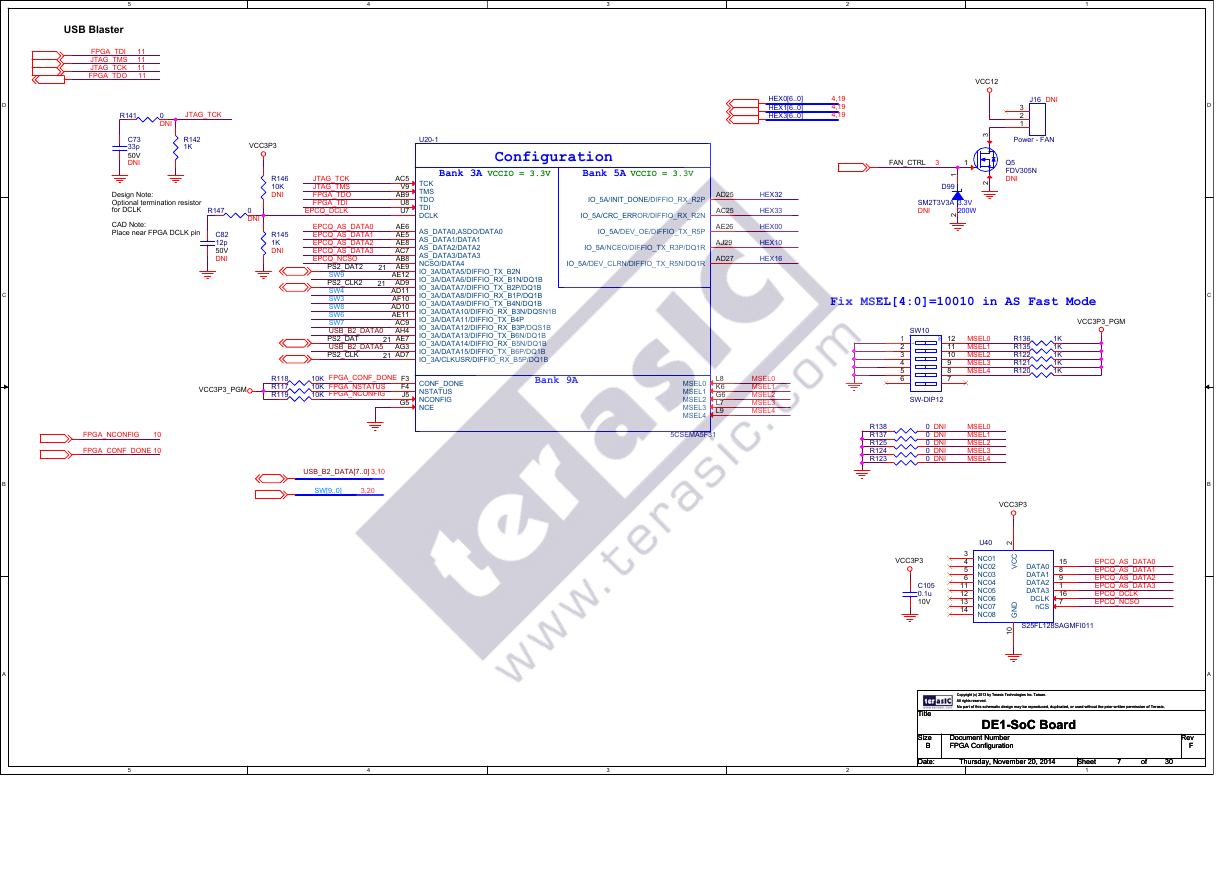

FPGA_TDI

11

JTAG_TMS

11

11

JTAG_TCK

FPGA_TDO 11

R141

0

DNI

JTAG_TCK

C73

33p

50V

DNI

R142

1K

VCC3P3

Design Note:

Optional termination resistor

for DCLK

CAD Note:

Place near FPGA DCLK pin

R146

10K

DNI

R145

1K

DNI

R147

0

DNI

C82

12p

50V

DNI

JTAG_TCK

JTAG_TMS

FPGA_TDO

FPGA_TDI

EPCQ_DCLK

EPCQ_AS_DATA0

EPCQ_AS_DATA1

EPCQ_AS_DATA2

EPCQ_AS_DATA3

EPCQ_NCSO

21

21

PS2_DAT2

SW9

PS2_CLK2

SW4

SW3

SW8

SW6

SW7

USB_B2_DATA0

PS2_DAT

USB_B2_DATA5

PS2_CLK

21

21

AC5

V9

AB9

U8

U7

AE6

AE5

AE8

AC7

AB8

AE9

AE12

AD9

AD11

AF10

AD10

AE11

AC9

AH4

AE7

AG3

AD7

U20-1

TCK

TMS

TDO

TDI

DCLK

AS_DATA0,ASDO/DATA0

AS_DATA1/DATA1

AS_DATA2/DATA2

AS_DATA3/DATA3

NCSO/DATA4

IO_3A/DATA5/DIFFIO_TX_B2N

IO_3A/DATA6/DIFFIO_RX_B1N/DQ1B

IO_3A/DATA7/DIFFIO_TX_B2P/DQ1B

IO_3A/DATA8/DIFFIO_RX_B1P/DQ1B

IO_3A/DATA9/DIFFIO_TX_B4N/DQ1B

IO_3A/DATA10/DIFFIO_RX_B3N/DQSN1B

IO_3A/DATA11/DIFFIO_TX_B4P

IO_3A/DATA12/DIFFIO_RX_B3P/DQS1B

IO_3A/DATA13/DIFFIO_TX_B6N/DQ1B

IO_3A/DATA14/DIFFIO_RX_B5N/DQ1B

IO_3A/DATA15/DIFFIO_TX_B6P/DQ1B

IO_3A/CLKUSR/DIFFIO_RX_B5P/DQ1B

4

3

2

1

Configuration

Bank 5A

VCCIO = 3.3V

Bank 3A

VCCIO = 3.3V

HEX0[6..0]

HEX1[6..0]

HEX3[6..0]

4,19

4,19

4,19

IO_5A/INIT_DONE/DIFFIO_RX_R2P

IO_5A/CRC_ERROR/DIFFIO_RX_R2N

IO_5A/DEV_OE/DIFFIO_TX_R5P

IO_5A/NCEO/DIFFIO_TX_R3P/DQ1R

IO_5A/DEV_CLRN/DIFFIO_TX_R5N/DQ1R

AD25

AC25

AE26

AJ29

AD27

HEX32

HEX33

HEX00

HEX10

HEX16

VCC12

J16

DNI

3

2

1

3

Power - FAN

FAN_CTRL

3

1

1

D99

2

SM2T3V3A

DNI

2

3.3V

200W

Q5

FDV305N

DNI

VCC3P3_PGM

R118

R117

R119

10K

10K

10K

FPGA_CONF_DONE

FPGA_NSTATUS

FPGA_NCONFIG

F3

F4

J5

G5

CONF_DONE

NSTATUS

NCONFIG

NCE

Bank 9A

FPGA_NCONFIG

10

FPGA_CONF_DONE 10

USB_B2_DATA[7..0] 3,10

SW[9..0]

3,20

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

L8

K6

G6

L7

L9

5CSEMA5F31

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

Fix MSEL[4:0]=10010 in AS Fast Mode

VCC3P3_PGM

SW10

1

O

N

1

2

3

4

5

6

SW-DIP12

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

12

11

10

9

8

7

R136

R135

R122

R121

R120

1K

1K

1K

1K

1K

R138

R137

R125

R124

R123

0 DNI

0 DNI

0 DNI

0 DNI

0 DNI

MSEL0

MSEL1

MSEL2

MSEL3

MSEL4

VCC3P3

5

4

3

2

VCC3P3

C105

0.1u

10V

U40

2

3

4

5

6

11

12

13

14

NC01

NC02

NC03

NC04

NC05

NC06

NC07

NC08

C

C

V

D

N

G

0

1

DATA0

DATA1

DATA2

DATA3

DCLK

nCS

15

8

9

1

16

7

EPCQ_AS_DATA0

EPCQ_AS_DATA1

EPCQ_AS_DATA2

EPCQ_AS_DATA3

EPCQ_DCLK

EPCQ_NCSO

S25FL128SAGMFI011

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

FPGA Configuration

FPGA Configuration

FPGA Configuration

Rev

Rev

Rev

F

F

F

Thursday, November 20, 2014

Thursday, November 20, 2014

Thursday, November 20, 2014

Sheet

Sheet

Sheet

1

7

7

7

of

of

of

30

30

30

D

C

B

A

�

5

4

3

2

1

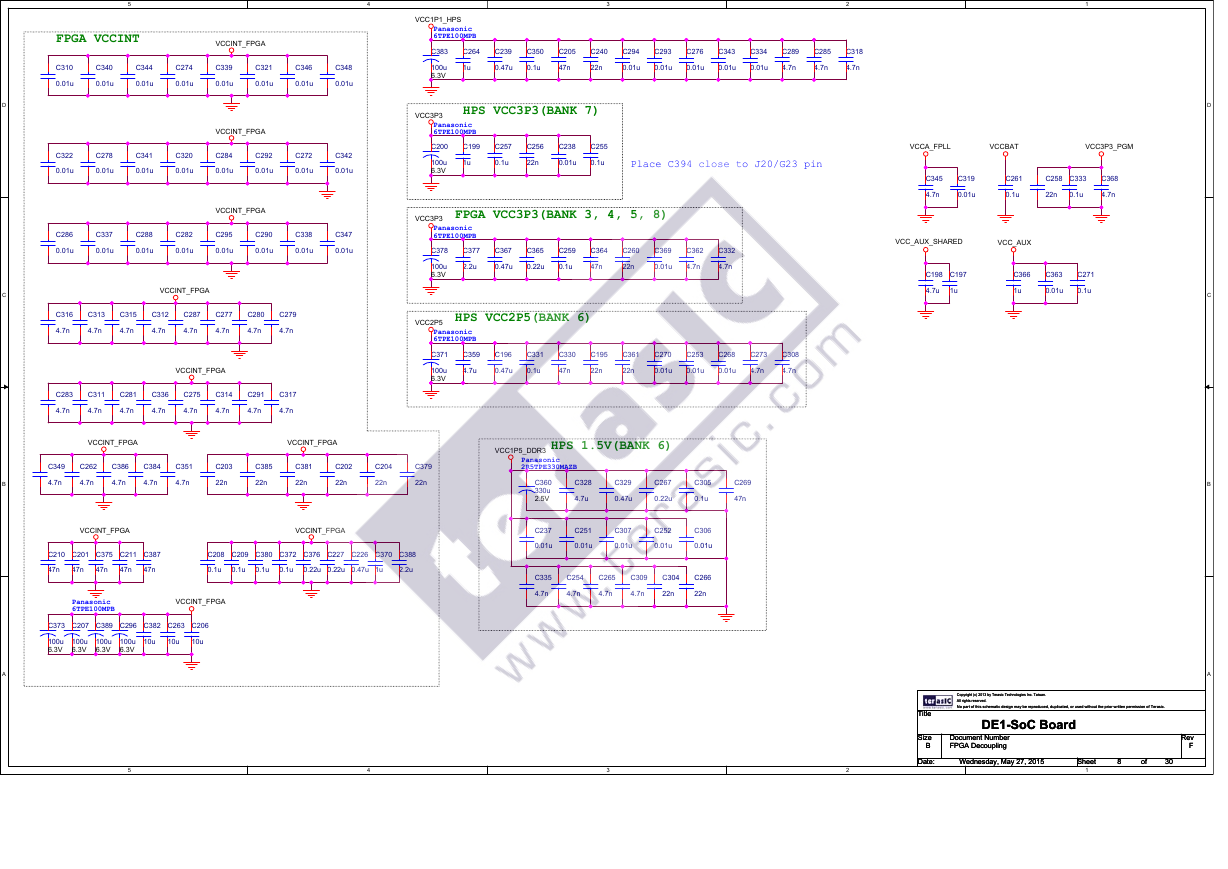

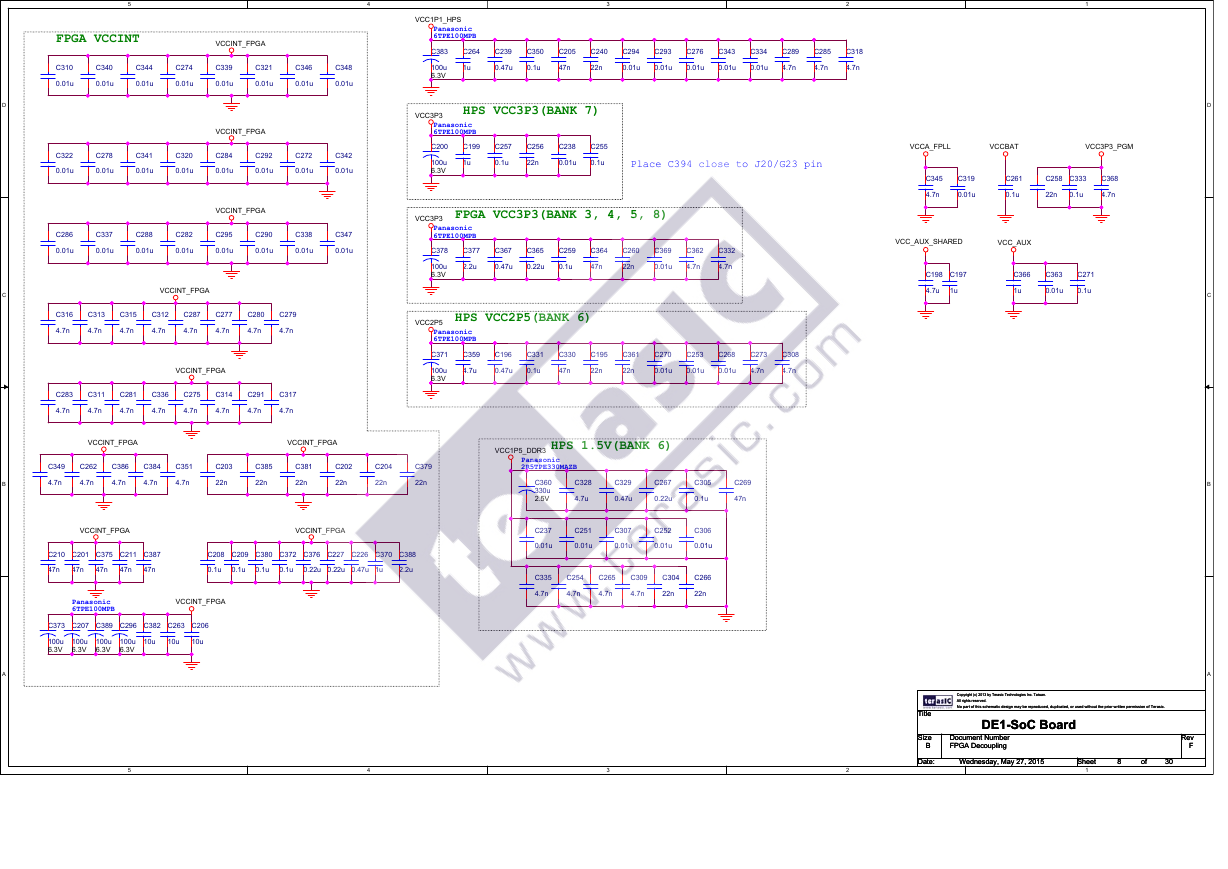

FPGA VCCINT

VCCINT_FPGA

C310

0.01u

C340

0.01u

C344

0.01u

C274

0.01u

C339

0.01u

C321

0.01u

C346

0.01u

C348

0.01u

VCC1P1_HPS

Panasonic

6TPE100MPB

C264

C383

100u

6.3V

1u

C239

0.47u

C350

0.1u

C205

C240

47n

22n

C294

0.01u

C293

0.01u

C276

0.01u

C343

0.01u

C334

0.01u

C289

4.7n

C285

4.7n

C318

4.7n

VCCINT_FPGA

C322

0.01u

C278

0.01u

C341

0.01u

C320

0.01u

C284

0.01u

C292

0.01u

C272

0.01u

C342

0.01u

VCCINT_FPGA

C286

0.01u

C337

0.01u

C288

0.01u

C282

0.01u

C295

0.01u

C290

0.01u

C338

0.01u

C347

0.01u

VCCINT_FPGA

C316

4.7n

C313

4.7n

C315

4.7n

C312

4.7n

C287

4.7n

C277

4.7n

C280

4.7n

C279

4.7n

VCC3P3

Panasonic

6TPE100MPB

C199

C200

100u

6.3V

1u

VCC3P3

Panasonic

6TPE100MPB

C377

C378

100u

6.3V

2.2u

VCCINT_FPGA

100u

6.3V

4.7u

C283

4.7n

C311

4.7n

C281

4.7n

C336

4.7n

C275

4.7n

C314

4.7n

C291

4.7n

C317

4.7n

VCCINT_FPGA

VCCINT_FPGA

C349

4.7n

C262

4.7n

C386

4.7n

C384

4.7n

C351

4.7n

C203

22n

C385

22n

C381

22n

C202

22n

C204

22n

C379

22n

VCCINT_FPGA

VCCINT_FPGA

C210

C201

C375

C211

C387

C208

C209

C380

C372

C376

C227

C226

C370

C388

47n

47n

47n

47n

47n

0.1u

0.1u

0.1u

0.1u

0.22u

0.22u

0.47u

1u

2.2u

Panasonic

6TPE100MPB

VCCINT_FPGA

C373

C207

C389

C296

C382

C263

C206

100u

6.3V

100u

6.3V

100u

6.3V

100u

6.3V

10u

10u

10u

HPS VCC3P3(BANK 7)

C257

0.1u

C256

22n

C238

0.01u

C255

0.1u

Place C394 close to J20/G23 pin

FPGA VCC3P3(BANK 3, 4, 5, 8)

C367

0.47u

C365

0.22u

C259

0.1u

C364

C260

47n

22n

C369

0.01u

C362

4.7n

C332

4.7n

HPS VCC2P5(BANK 6)

VCC2P5

Panasonic

6TPE100MPB

C359

C371

C196

0.47u

C331

0.1u

C330

C195

C361

47n

22n

22n

C270

0.01u

C253

0.01u

C268

0.01u

C273

4.7n

C308

4.7n

HPS 1.5V(BANK 6)

VCC1P5_DDR3

Panasonic

2R5TPE330MAZB

C360

330u

2.5V

C237

0.01u

C328

4.7u

C251

0.01u

C329

0.47u

C307

0.01u

C267

0.22u

C252

0.01u

C305

0.1u

C306

0.01u

C269

47n

C335

4.7n

C254

4.7n

C265

4.7n

C309

4.7n

C304

C266

22n

22n

D

C

B

A

VCCA_FPLL

VCCBAT

VCC3P3_PGM

C345

4.7n

C319

0.01u

C261

0.1u

C258

C333

22n

0.1u

C368

4.7n

VCC_AUX_SHARED

VCC_AUX

C198

C197

4.7u

1u

C366

1u

C363

0.01u

C271

0.1u

D

C

B

A

5

4

3

2

Title

Title

Title

Size

Size

Size

B

B

B

Date:

Date:

Date:

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

All rights reserved.

All rights reserved.

All rights reserved.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

DE1-SoC Board

DE1-SoC Board

DE1-SoC Board

Document Number

Document Number

Document Number

FPGA Decoupling

FPGA Decoupling

FPGA Decoupling

Rev

Rev

Rev

F

F

F

Wednesday, May 27, 2015

Wednesday, May 27, 2015

Wednesday, May 27, 2015

Sheet

Sheet

Sheet

1

8

8

8

of

of

of

30

30

30

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc