自动化技术与应用 201 2年第31卷第l z期

通 信 与 信 息 处 理

Com munication and Information P rocessing

扩 频 通 信 系统 中一种 基 于 F P G A 的

匹配 滤 波 同步 捕 获 方 法

杨 鹏 ,郭黎 利 ,晏 慧 强

(哈尔 滨工程 大学 信息与通信工程学 院 ,黑龙江 哈尔 滨 15001)

摘 要 :本 文 通 过对 匹 配 滤 波器 同 步捕 获原 理 的研 究 ,利 用 扩 频 通 信 系 统 中 PN 码 良好 的 自相 关性 ,提 出 了 基 于 FPGA 实 现 的 全 数 字

匹配滤波的改进 同步捕获方法 ,在低信噪比下可实现载波和码元 同时同步 ,且在不损失同步精度 的前提下降低 了采样率及片 内

资 源 消 耗 ,并 给 出 了 同步 精 度 对 误 码 性 能 的 影 响 及 片 内 资源 消耗 分 析 。

关 键 词 :同 步 ;匹配 滤 波 ;扩 频 通 信 ;FPGA

中 图分 类 号 :TN926+.1 文献 标 识 码 :A 文 章 编 号 :1003—7241(2012)12-0028—04

A Method of Synchronization Capture Using Match Filter Based

On FPGA in Spread Spectrum Communication System

YANG Peng,GU O Li-li,YAN H ui—qiang

(College ofInformation and Communication Engineering,Harbin Engineering University,Harbin,150001 China)

Abstract:Through researching the principle of synchronization capture to match filter and using good auto—correlation of PN code

in spread spectrum com munication system ,this paper provides an improved realizable m ethod of synchronization

capture using digital m atch filter based on FPGA.It can implement carrier and code synchrOnizatiOn sim ultaneously in

low signal to noise ratio.M oreover,it reduces the sam pling rate and resource consum ption in the chip without loss

synchronization accuracy,it also gives effect of synchrOnizatiOn accuracy to the BER performance and analysis of

resource consumption in the chip.

K ey words:synchr0nizatiOn;match filter;spread spectrum communication;FPGA

1 引 言

扩 频通 信 系统 具有 抗 噪声 和 干扰 能力 强 、功 率谱

现 。前 者主要基 于滑动 相关法 ,工作 在大信 噪 比情 况下

有较好 的性能 ,一般捕获 的时间较长 ;后者 可 以在低信 噪

密度 低 、抗截 获能力 强和多址 通信 能力强等 技术优 势 ,

比下实现 同步 ,且 捕获 时间较短 【2]。 由于 可编程 逻辑器

被广 泛应用 于军事和 民用通 信系统 中n】。扩频信号具有

件 的发展 ,使得 FPGA易于 实现全数字 匹配滤波器 完成

良好 的尖锐 的 自相关性 和低值 的互 相 关性 ,但这也对 接

收机 的同步性 能提 出了更高的要 求 ,尤其在 低信 噪比甚

同步 ,本 文在原 有方法 上加 以改 进 ,在 不损 失 同步精 度

的前提下 降低 采样 率并使 FPGA综 合资源 消耗 下降 ,提

至在负信 噪比下 ,载波和 PN码元 的同步显得尤为 困难 ,

高 了可 实 现性 。

因此 需对 低信 噪 比下 同步 问题做 重 点研 究 。

扩频通 信 系统 中同步 的方 法很 多[ ,以相 关检 测的

2 匹配 滤 波 器 同步 原 理

捕 获 、跟踪环 路为主 ,其 次就 是用 匹配 滤波器 方法来实

由最佳 接收理 论知 ,若 接 收信号 为 (f),则 匹配滤

收 稿 日期 :2 01 2—0 5—2 5

波器的冲激响应 h(t)为

h(t)=s(T— ),0 T

(1)

�

通 信 与 信 息 处 理

Comm unication and Information Processing

《自动 化 技 术 与 应 用 》201 2年第 31卷第 12期

式 中 为信 号 ( )的持续 时间 ,即 PN 码 的整个 码

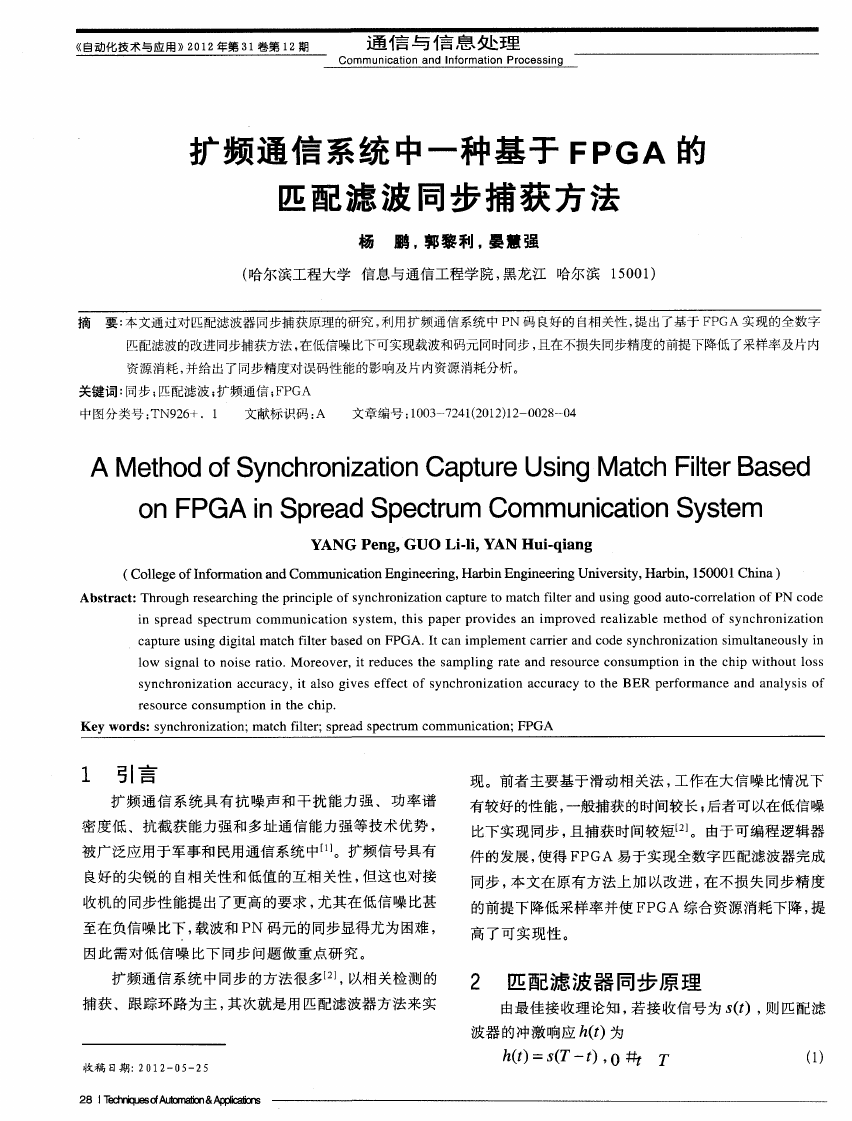

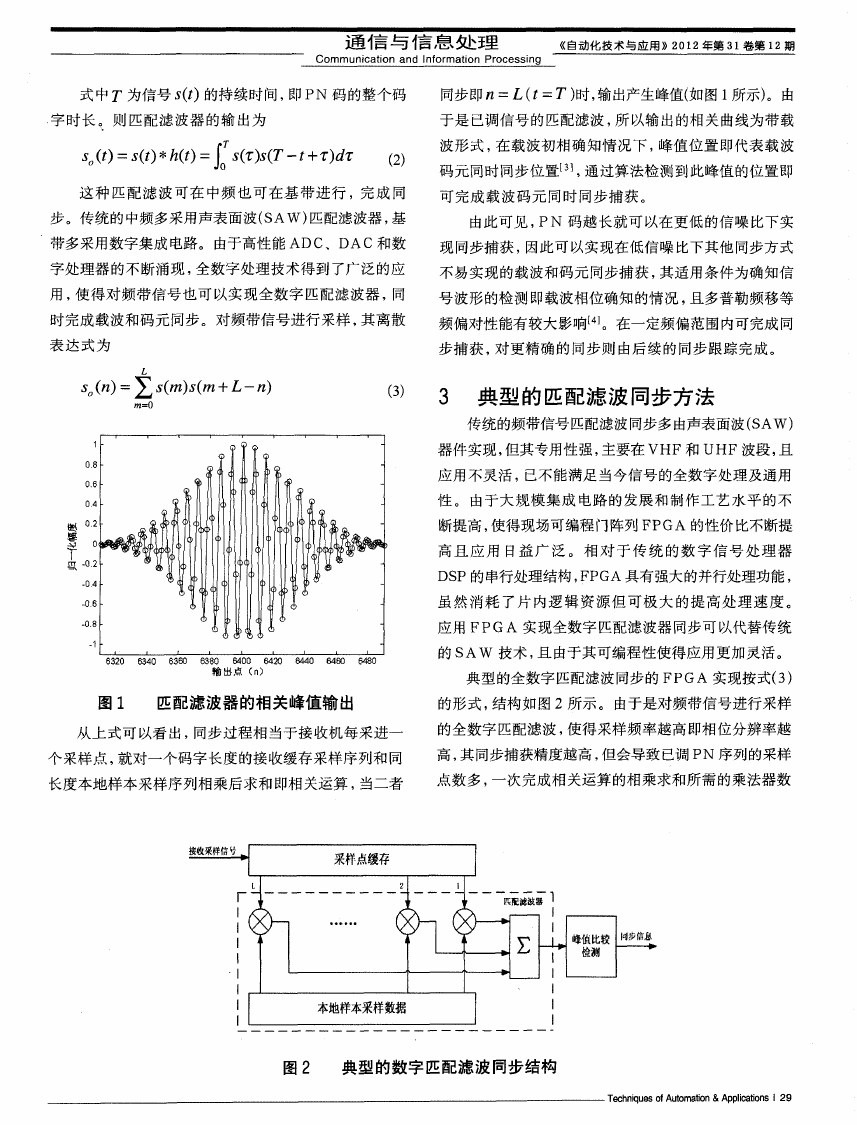

同步即 n=L(t=T)时 ,输出产生峰值(如图 1所示 )。由

字 时长 。则 匹配滤 波器 的输 出为

于 是 已调 信号 的匹配滤 波 ,所 以输出的相 关曲线为 带载

。 )= ( )冰 (f) Jo ( ) (丁一f+ ) (2)

· r

波 形 式 ,在 载波初 相确 知情 况下 ,峰值位 置 即代表载 波

码 元 同时同步位 置【3l,通过算 法检测 到此峰值 的位置 即

这 种 匹配 滤 波 可在 中频 也 可在 基 带 进 行 ,完 成 同

可完 成载 波码 元 同时 同步捕 获 。

步。传统 的中频多采用声表 面波(sAw )匹配滤波器 ,基

由此可见 ,PN 码越 长就 可 以在更 低的信 噪 比下实

带多采用数字集成 电路 。由于高性 能 ADC、DAC和 数

现 同步捕 获 ,因此可 以实现在 低信 噪 比下其他 同步方 式

字 处理器 的不 断涌现 ,全数 字处理 技术得 到 了广 泛的应

不 易实现 的载波和 码元 同步捕获 ,其 适用条件 为确知信

用 ,使得 对 频带信 号也 可 以实现 全数字 匹配 滤波 器 ,同

号 波形的检 测 即载 波相位确 知的情 况 ,且多普 勒频移 等

时完成 载波和码 元 同步 。对频 带信号进 行采样 ,其离散

频偏对性 能有较大 影响【4]。在 一定频偏 范围 内可完成 同

表 达 式为

步捕 获 ,对 更精 确 的同步 则 由后 续 的同步 跟踪完 成 。

(,z) (,,z) ( +L一,z)

(3) 3 典型 的 匹配 滤 波 同步 方 法

传统 的频带信号匹配滤波 同步多 由声表面波 (SAW )

器件 实现 ,但其 专用性 强 ,主要在 VHF和 UHF波段 ,且

应 用不灵 活 ,已不能 满足 当今信号 的全数字处 理及通 用

性 。 由于 大 规模 集成 电路的 发展 和 制作 工艺 水平 的 不

断提 高 ,使得现场 可编程 门阵列 FPGA 的性价 比不断提

高 且 应 用 日益 广 泛 。 相对 于 传 统 的 数 字 信 号 处 理 器

DSP的串行处理结构 ,FPGA具有 强大的并行处理功 能 ,

虽 然 消 耗 了 片 内逻 辑 资 源 但 可极 大 的 提 高处 理 速 度 。

应 用 FPG A 实 现全数 字 匹配滤 波器 同步可 以代替 传统

的 SAW 技术 ,且 由于其 可编程性使 得应用更 加灵活 。

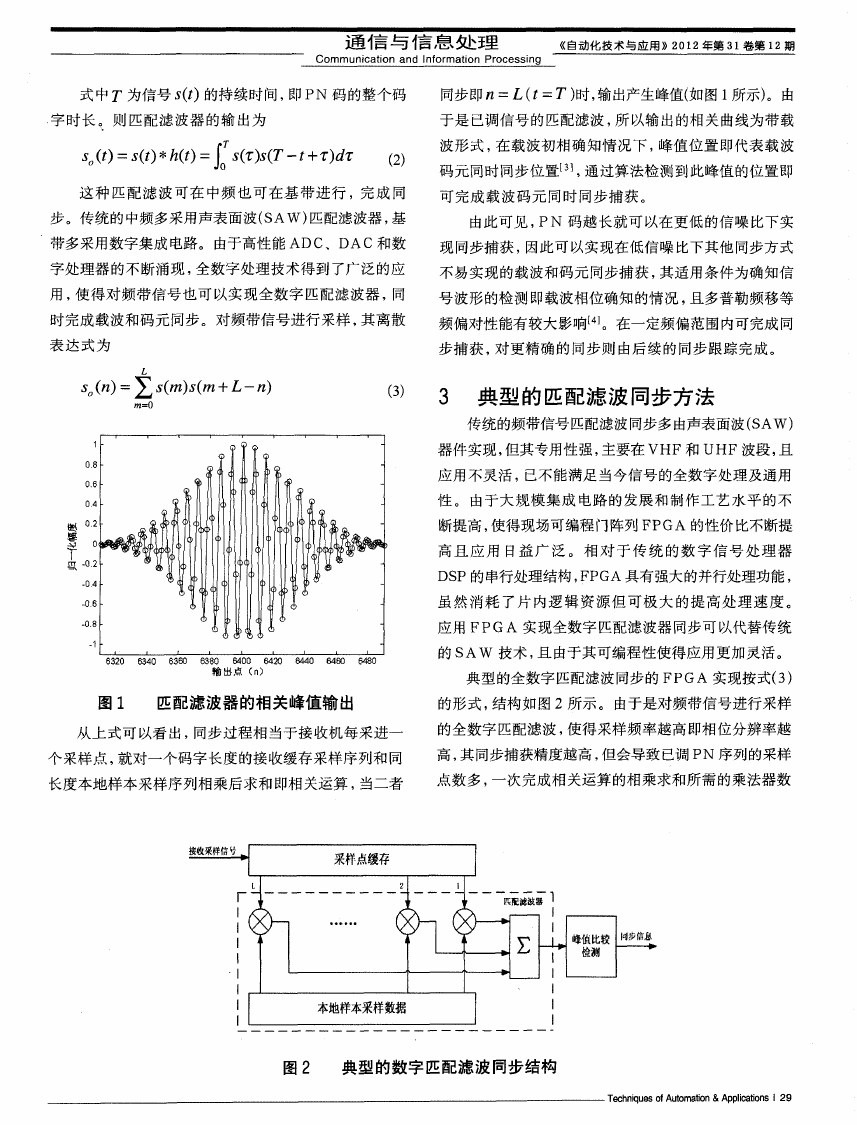

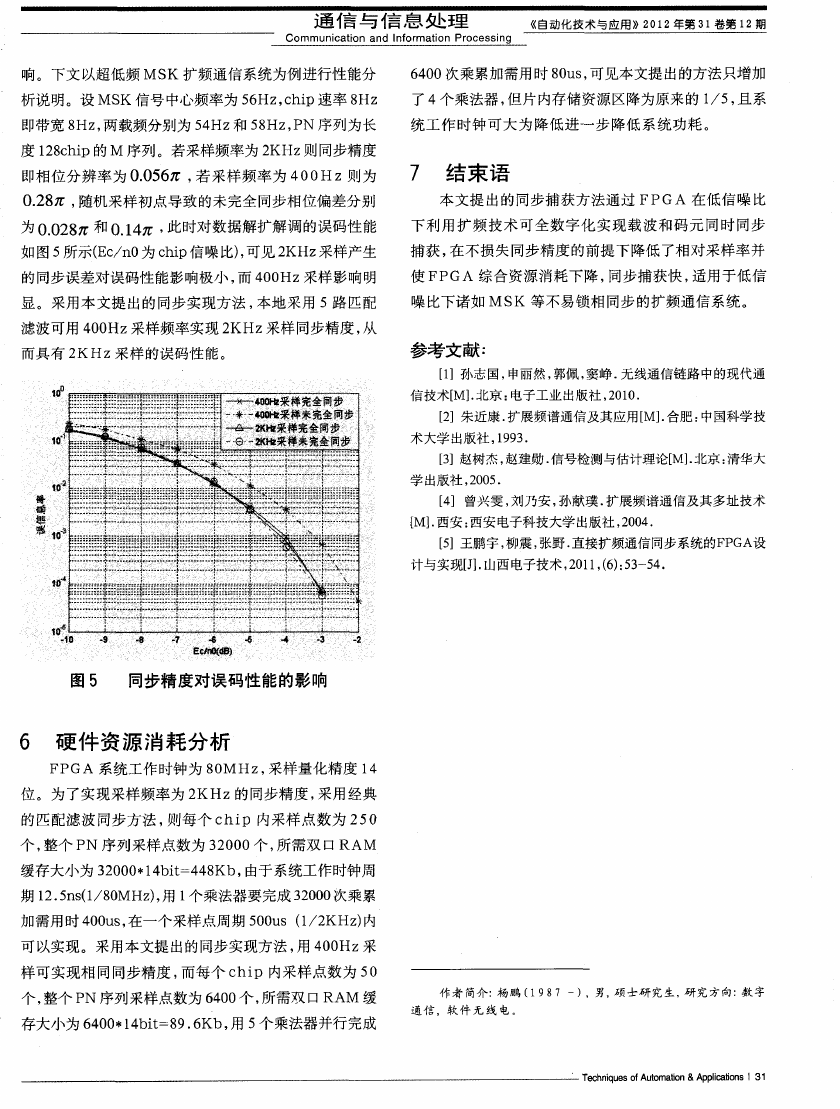

典型 的全数 字 匹配滤 波 同步 的 FPGA 实现按式(3)

图 1 匹配滤 波器 的相关峰 值输 出

的形 式 ,结 构如 图 2所 示 。由于是对频 带信号进 行采样

从上 式可 以看 出 ,同步过程 相 当于 接收机 每采进 一

的全数 字 匹配滤 波 ,使得 采样频率 越高 即相 位分辨率 越

个 采样 点 ,就对 一个码字 长度 的接收缓存 采样序 列和 同

高 ,其 同步捕获精度越高 ,但会导致 已调 PN序 列的采样

长度 本地样本 采样序 列相 乘后求和 即相 关运 算 ,当二者

点数多 ,一 次完成相 关运算 的相乘 求和所需 的乘法器 数

图 2 典 型 的数字 匹配滤 波 同步 结构

�

《自动化技术与应用 20l2年第31卷第l 2期

通 信 与 信 息 处 理

Comm unication and Information P rocessing

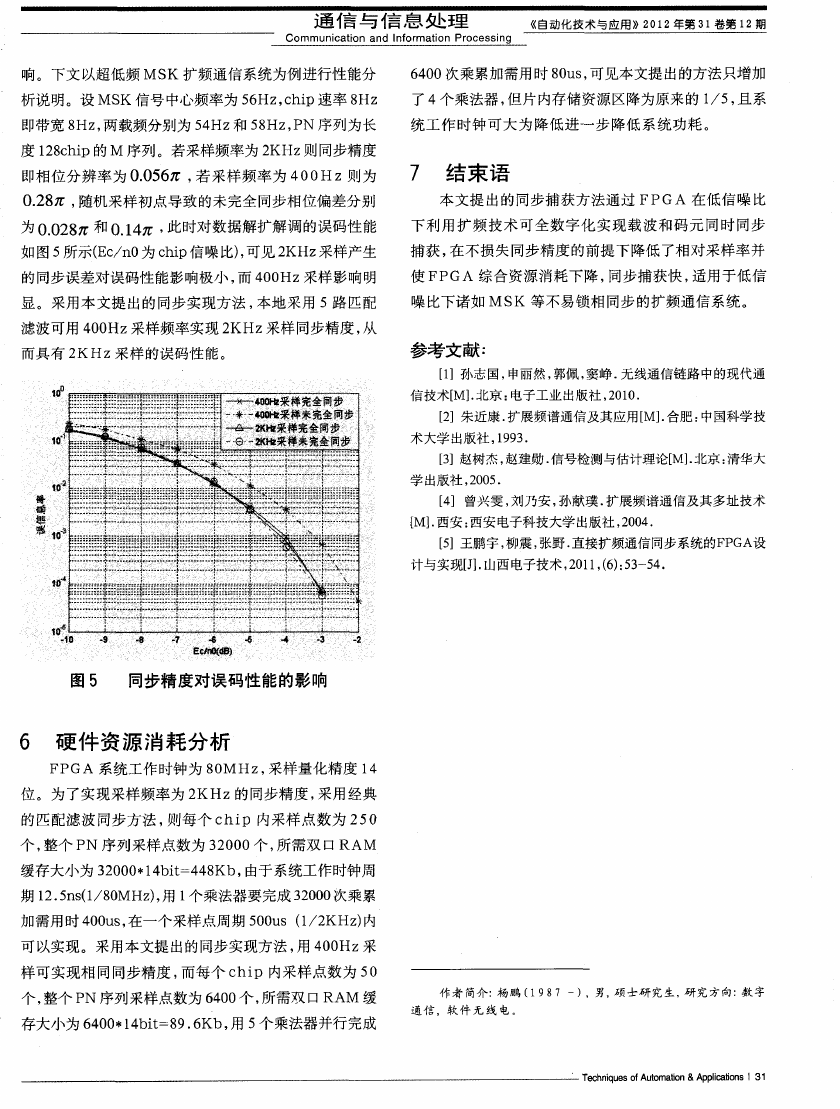

图 3 改进 的数 字 匹配 滤波 同步结 构

L过 多 ,超过 FPGA片 内乘法器资源 ,通常可改用 串行方

式 ,在 采样 间 隔时 间内用一 个乘 加器 完成相 关运算 ,但

这需提 高系统工作时钟(L倍 采样频率),会导致 由于器件

最 高工作 时钟上 限出现 的瓶 颈 问题 ,因此可采 用二者结

合 的方法[5l,即一次从双 口RAM 读 出 N 个数 据用 N个

乘法器 并行完 成一次局 部相关运 算 ,然后依 此 串行 完成

M 次 并 累 加 求 和 ,最 后 得 出相 关 运 算 结 果 ,其 中

L=N M 。可 以看 出 N 决定 片 内消耗资源 ,M 决定系统

工作 频率 ,二 者相 互制约 ,需 进行权 衡分配 。

图 4 本地 多路 信号

行缓存 的双 口 RAM 空间却 由 L的增大 而增大 ,会 占据

片 内很 大 的存 储资源 ,若 要减小 双 口RAM 空 间就要 降

低 采样频 率 ,这 又会 减小 同步精 度 ,使 随后 的数据 解扩

解 调产 生误 码性 能 的损 失 。

由匹配滤 波原理 ,当接 收信号 与本地 信号 完全 同步

时 ,其相 关运 算结果最大 ,而 当未完全 同步时 ,结果 会略

微减小 。据此可 采用 k路 不 同初 相的本地 样本数 据 ,与

采样数据进行 并行 匹配滤波 ,其 中采样频率 为原来的 1/

k倍 ,双 口 RAM 深度 为 L/k,本地样本数据 为原来 的 k

倍 抽取 即频率为 原来的 1/k倍 ,而 k路 本地 样本数据 的

不 同初相 由原 本地 样本 数据 前 k 个点 分别 为初 始点 产

生的 ,结构及本地 样本示意 图如 图 3、4所 示(k=5)。

接收机对接 收信号进 行采样 ,存 入双 口RAM 缓存

中,其深 度为 PN 序列的采样长度 L/k,每进一个采样点

就将缓存 中全部数据与 k路 同长度本地 样本采样数据进

行相 关运 算 ,结果送人峰值 比较检 测模 块。在此模块 中 ,

根 据算法 即将结果 与预设 门限 比较 ,当大于 门 限便将 各

路结 果值 和 地址 信息 即同步 位置 信息 存入 预 设深 度 缓

存 ,以后每 次采样运 算后就依 次存人 并 比较 前后结果 大

小 ,找 出极 大值及地 址信息便 可 同时完成 载波和码 元 同

步 ,门限值和缓存 预设 深度根据 MATLAB仿真得到 。

当 PN序列 已调信号完全采样进入接收机双 口 RAM

4 改 进 的 匹配 滤 波 同步 方 法

时 ,必有一 路匹配 滤波器 输出峰值 最大 ,即判 定此路本地

从典 型的 匹配滤波 同步方 法可 以看 出 ,L 由 PN 序

信 号与接 收信号 完成 同步 ,这 样 既降低 了存 储资源 的消

列 长度及 采样 频率决 定 ,在 序列 长度一 定 的情况 下 ,采

耗 ,又没有 同步精度 的损失 ,仍为原来 的 同步精 度 。

样频率 f,越高则 L越 大 ,这样 虽然可以提高 同步精度 即

相位分辨 率(△ =2 .厂/. ),但增大了匹配滤波运算的

5 同步精 度及 性 能分 析

处理负担 。 由于本地样本采样数据可 由 PN码调 制 DDS

由全 数 字 匹配滤 波 器实 现对 频 带信 号 的 载波 与码

实 时产生 ,不 会 占用 过多 的存储 资源 ,而对 采样数 据进

元 同步 ,其 同步精度对 数据解 扩解调产 生很大 的误码 影

�

通 1言与 1言息 处 理

《自动化技术与应用》201 2年第31卷第1 2期

Comm unication and Information P rocessing

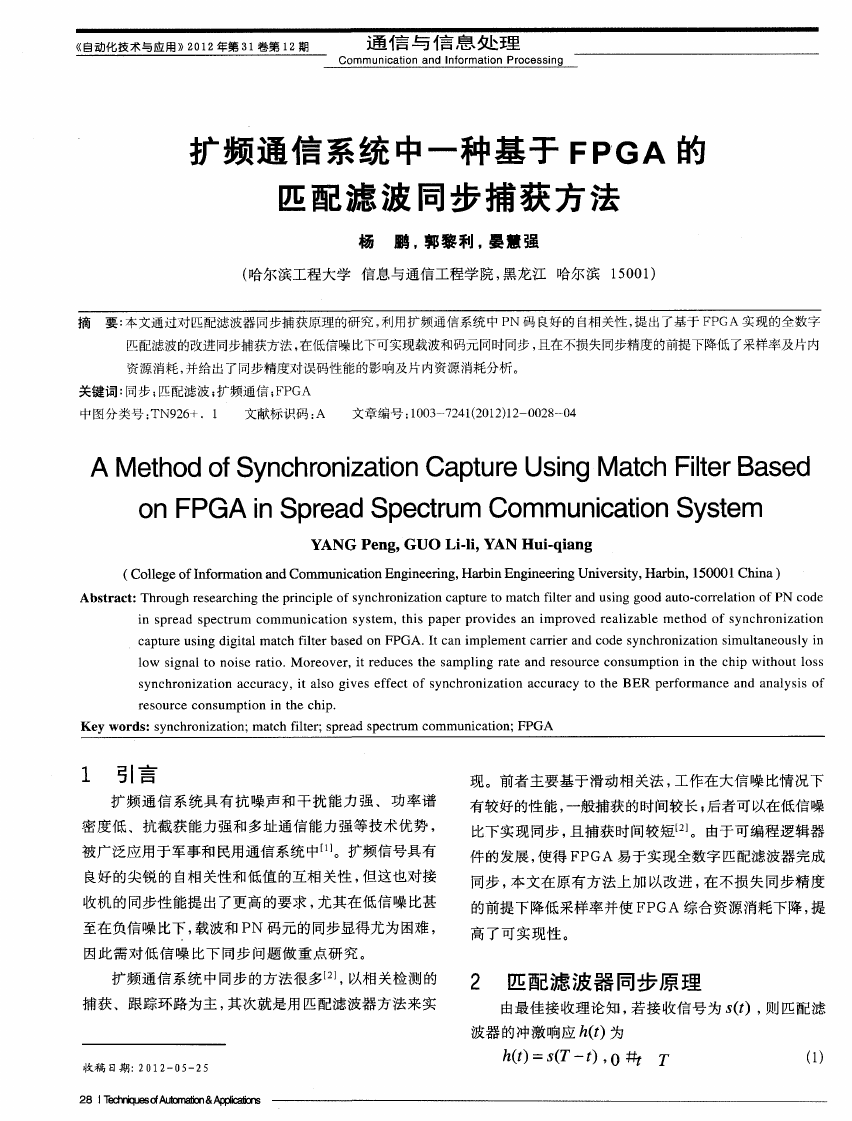

响。下文 以超低频 MSK 扩频通信 系统为例进行 性能分

6400次乘累加需 用时 80us,可见本文提 出的方法只增加

析说 明 。设 MSK信号 中心频率 为 56Hz,chip速率 8Hz

了 4个 乘法器 ,但片 内存储 资源区降为原来 的 I/5,且 系

即带 宽 8Hz,两载频分别为 54Hz和 58Hz,PN序列为 长

统 工作 时 钟可 大为 降 低进一 步 降低 系统 功耗 。

度 128chip的 M 序列 。若 采样频率 为 2KHz则 同步精度

即相位 分辨 率 为 0.056zr,若 采样 频率 为 400H z则为

7 结束 语

0.28:rr,随机采样 初点导 致的未完全 同步相位偏差 分别

本 文提 出的 同步捕获 方法通 过 FPGA 在低信 噪 比

为 0.028:n:和 0.14n:,此时对数 据解扩 解调 的误码性 能

下利 用扩 频 技术 可全 数 字化 实 现载 波和 码元 同时 同步

如 图 5所 示(Ec/n0为 chip信 噪比),可见 2KHz采样 产生

捕 获 ,在 不损 失同步精度 的前提 下降低 了相对 采样率 并

的同步误差对 误码性能影 响极 小 ,而 400Hz采样影 响明

使 FPGA 综合资 源消耗 下降 ,同步捕获快 ,适用 于低信

显。采用 本文提 出的同步实现 方法 ,本地 采用 5路 匹配

噪 比下诸 如 MSK 等不易锁 相 同步的扩频 通信系统 。

滤 波可用 400Hz采样频率实 现 2KHz采样 同步精度 ,从

而具 有 2KHz采样 的误 码性 能。

参考文献 :

[1】孙志 国 ,申丽然 ,郭佩 ,窦峥 .无 线通信链 路中的现代通

信技 术[M].北京 :电子工业 出版社 ,2010.

[2]朱近康 .扩展频谱通信及其应用【M].合肥 :中国科学技

术大学 出版社 ,1993.

[3]赵 树 杰 ,赵 建 勋 .信号 检 测 与估 计 理 论 [M】.北 京 :清 华 大

学 出版 社 ,2005.

[4] 曾 兴 雯 ,刘 乃 安 ,孙 献 璞 .扩 展 频 谱 通 信 及 其 多 址 技 术

】.西安 :西安 电子科技大学 出版社 ,2004.

[5】王鹏宇 ,柳震 ,张野 .直接扩频通信同步系统的FPGA设

计与 实现 .山西 电子技术 ,2011,(6):53—54.

图 5 同步精 度对 误码 性 能的影 响

6 硬 件 资 源 消 耗 分 析

FPGA 系统工作 时钟为 80MHz,采样量 化精度 1 4

位 。为 了实现采样频 率为 2KHz的 同步精度 ,采用经典

的匹配滤 波 同步方 法 ,则每个 ChiP内采样 点数 为 250

个 ,整个 PN 序列采样 点数为 32000个 ,所需双 口RAM

缓存 大小 为 32000*14bit=448Kb,由于 系统工作时钟周

期 12.5ns(1/80MHz),用 1个 乘法器 要完成 32000次乘累

加需 用时 400us,在一个 采样点 周期 500us (1/2KHz)内

可 以实现 。采用本文提 出的同步实现方法 ,用 400Hz采

样 可实 现相 同同步精度 ,而每 个 chip内采样点数 为 50

个 ,整个 PN序列 采样 点数为 6400个 ,所需双 口 RAM 缓

存大小为 6400*14bit=89.6Kb,用 5个乘法器并行 完成

作 者 简介 :杨鹏 (1 9 8 7 一),男,硕 士研 究生,研 究方向 :数 字

通 信 ,软 件 无 线 电 。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc