CXD301

程序说明 V1.0

杜勇 编著

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

工程师是科学家;工程师是艺术家;工程师也是思想家。 一位伟大的工程师曾经提出过

这样的一段感言。

电子工程师一份值得尊敬的职业。把自己的想法灌注到一个个的元件中,巧妙地将其组

合,最后幻化出声音、图像和动作,这个过程就像建筑师建造一座桥梁,音乐家创作一首乐

曲一样,艰辛而美妙。人类将自己的智慧、思想以及创造性灌注到有 形的事物之中,这些事

物便被礼赞为艺术,工程师的作品是可以被称赞的事物之一。

谨以此与广大电子工程师共勉!

1

Bridge Between Theory And Practice. Cameion Workshop

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

版本

1.0 创建文档

文档控制

修改内容

日期

2017.08

Bridge Between Theory And Practice. Cameion Workshop

2

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

目 录

1 版权申明……………………………………………………………… 4

2 数字滤波器技术实验………………………………………………… 4

2.1 FIR 滤波器的板载测试………………………………………………… 4

2.2 IIR 滤波器的板载测试…………………………………………………6

2.3 CIC 滤波器的板载测试………………………………………………… 9

2.4 自适应陷波器的板载测试………………………………………………11

2.5 频域滤波器的板载测试…………………………………………………13

2.6 Costas 环的板载测试…………………………………………………15

3 数字通信同步技 术实验…………………………………………………… 17

3.1 直接载波同步的板载测试………………………………………………18

3.2 同相正交环的板载测试…………………………………………………20

3.3 AFC 环解调的板载测试…………………………………………………22

3.4 微分型同步环的板载测试………………………………………………23

3.5 插值法位同步环的板载测试……………………………………………25

3.6 串口通信的板载测试……………………………………………………27

帧同步电路的板载测试…………………………………………………28

3.7

4 调制解调技术实验…………………………………………………………… 30

4.1 ASK 调制解调的板载测试…………………………………………… 31

4.2 MSK 调制解调的板载测试……………………………………………33

4.3 Costas 环解调的板载测试……………………………………………35

4.4 QPSK 解调的板载测试…………………………………………………37

4.5 直扩调制解调的板载测试………………………………………………38

Bridge Between Theory And Practice. Cameion Workshop

3

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

1 版权申明

本手册版权归属米恩工作室(Cameion Workshop)所有,并保留一切权力。

非经本工作室书面形式同意,任何单位及个人不得擅自摘录或修改本手册部分或

全部内容,违者将追究其法律责任。

感谢您购买 FPGA 数字信号处理板(CXD301),在使用本产品之前,请仔

细阅读该手册内容,并确保知道如何正确使用本产品。不合理的操作可能会损坏

开发板。

此手册将视情不断更新,请及时到官方博客下载并使用最新版本。

工作室已开设该产品的用户交流区,大家可以在交流区中下载相关资料,就

产品使用进行讨论,工作室会定期整理发布与产品相关的信息。

官方博客:http://duyongcn.blog.163.com/

官方网店:https://shop574143230.taobao.com/

技术邮箱:duyongcn@sina.cn

2 数字滤波器技术实验

《数字滤波器技术的 MATLAB 与 FPGA 实现——Xilinx/VHDL 版》对数字滤波器

技术的原理、Matlab 仿真、ModelSim 仿真测试、性能分析等内容进行了详细阐

述,配套使用,更易理解技术实现细节。

2.1 FIR 滤波器的板载测试

(FilterVHDL\Chapter_4 \E4_7_FirSerial\FirFullSerial)

1)功能说明

FIR 低通滤波器:DA 通道 1 输出频率为 200Hz 和 800Hz 的叠加信号,经 FPGA 低通滤波

后,滤除 800Hz 的信号,DA 通道 2 仅输出 200Hz 单频信号。

2)硬件接口电路

本次实验的目的在于验证全串行结构的 FIR 滤波器电路工作情况,即验证顶层文件

Fir8Serial.vhd 程序是否能够完成对输入信号的滤波功能。

CXD301 开发板配置有 2 路独立的 DA 接口、1 路 AD 接口、2 个独立的晶振。为尽量真

实地模拟通信中的滤波过程,采用晶振X2(gclk1)作为驱动时钟,产生频率为200Hz 和 800Hz

的正弦波叠加信号,经 DA1 通道输出;DA1 通道输出的模拟信号通过电路板上的 P2 跳线端

Bridge Between Theory And Practice. Cameion Workshop

4

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

子(管脚 2、3 短接)物理连接至 AD 通道,送入 FPGA 进行处理;FPGA 低通滤波后的信号

经处理后,由 DA2 通道输出;DA2 和 AD 通道的驱动时钟由 X1(gclk2)提供,即实验中的

收、发时钟完全独立。程序下载到电路板后,通过示波器同时观察 DA1、DA2 通道的信号波

形,即可判断滤波前后信号的变化情况。实验电路的 FPGA 接口信号定义如表 2-1 所示。

表 2-1 FIR 低通滤波器实验接口信号定义表

信号名称

管脚定义

传输方向

功能说明

reset

gclk1

gclk2

key1

ad_clk

K3

C10

H3

K1

P6

->FPGA

复位信号,高电平有效

->FPGA

生成合成测试信号的驱动时钟

->FPGA

接收处理及 DA2 转换的驱动时钟

按键信号,按下为高电平;按下时

->FPGA

AD 输入为合成信号,否则为 200Hz

单频信号。

FPGA->

AD 采样时钟信号,2kHz

ad_din[7:0] P7 、T6、R7、T7、T8、R9、T9、P9

->FPGA

AD 采样输入信号,8 比特

da1_clk

P2

FPGA->

DA1 转换时钟信号,2.048MHz

da1_out[7:0] R2 、R1、P1、N3、M3、N1、M2、M1

FPGA->

DA1 转换信号,模拟的测试信号

da2_clk

P15

FPGA->

DA2 转换时钟信号,16kHz

da2_out[7:0]

FPGA->

DA2 转换信号,滤波后输出的信号

L16、M16、M15、N16、P16、R16、

R15、T15

3) 板载测试验证

设计好板载测试程序并完成 FPGA 实现后,可以将程序下载至 CXD301 进行板载测试。

板载测试的硬件连接图如图 2-1 所示。

图 2-1 FIR 滤波器电路板载测试硬件连接图

实验测试需要采用双通道示波器,将示波器通道 1 接 DA1 输出,观察滤波前的信号;通

道 2 接 DA2 输出,观察滤波后的信号。需要注意的是,在测试之前,需要适当调整 CXD301

的电位器 R36,使 P3(AD IN)接口的信号幅值为 0~2V。

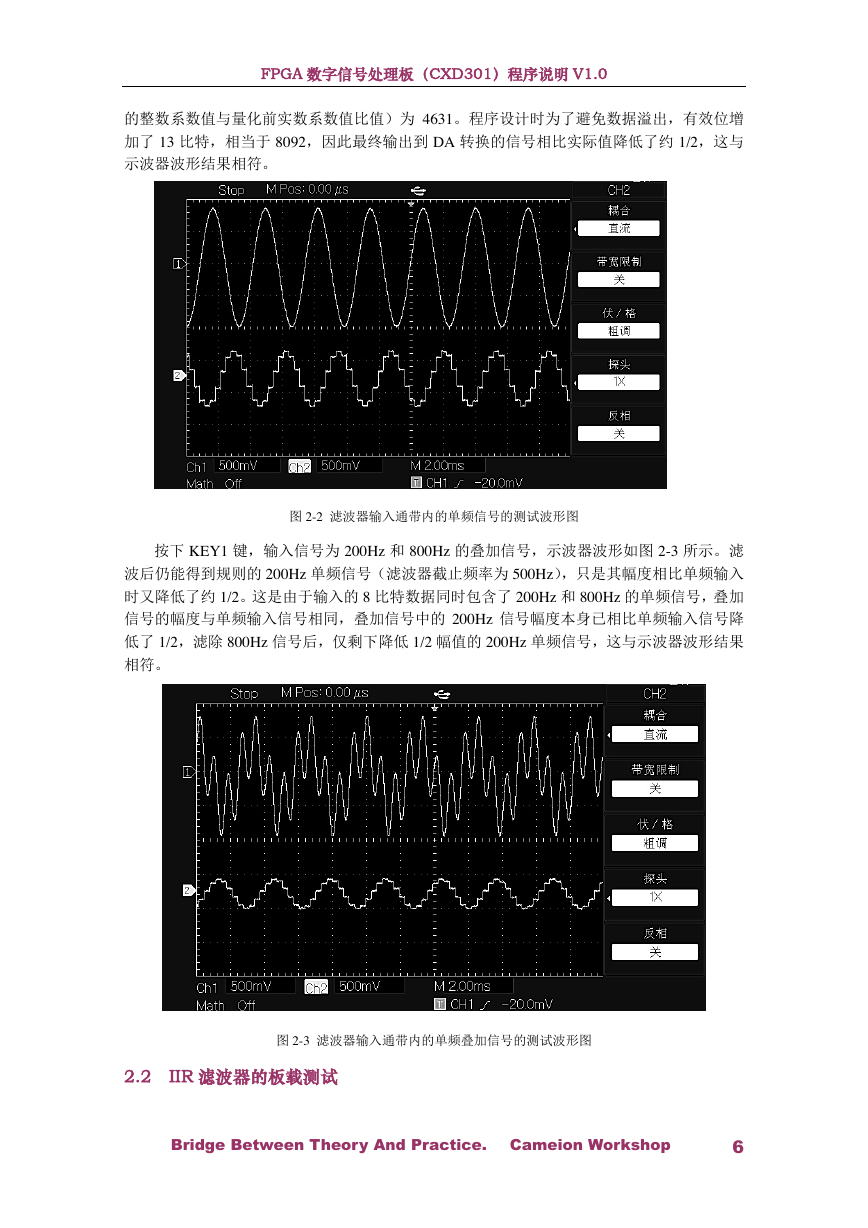

将板载测试程序下载到 CXD301 板上后,合理设置示波器参数,可以看到两个通道的波

形如图 2-2 所示。从图中可以看出,滤波前后的信号均为 200Hz 的单频信号。滤波信号不够

平滑,波形呈阶梯状,这是由于采样频率及转换频率较低引起的。滤波后幅度低于滤波前的

信号,这是由运算中的有效字长效应引起的。滤波器绝对值之和为 6162,实际增益(量化后

Bridge Between Theory And Practice. Cameion Workshop

5

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

的整数系数值与量化前实数系数值比值)为 4631。程序设计时为了避免数据溢出,有效位增

加了 13 比特,相当于 8092,因此最终输出到 DA 转换的信号相比实际值降低了约 1/2,这与

示波器波形结果相符。

图 2-2 滤波器输入通带内的单频信号的测试波形图

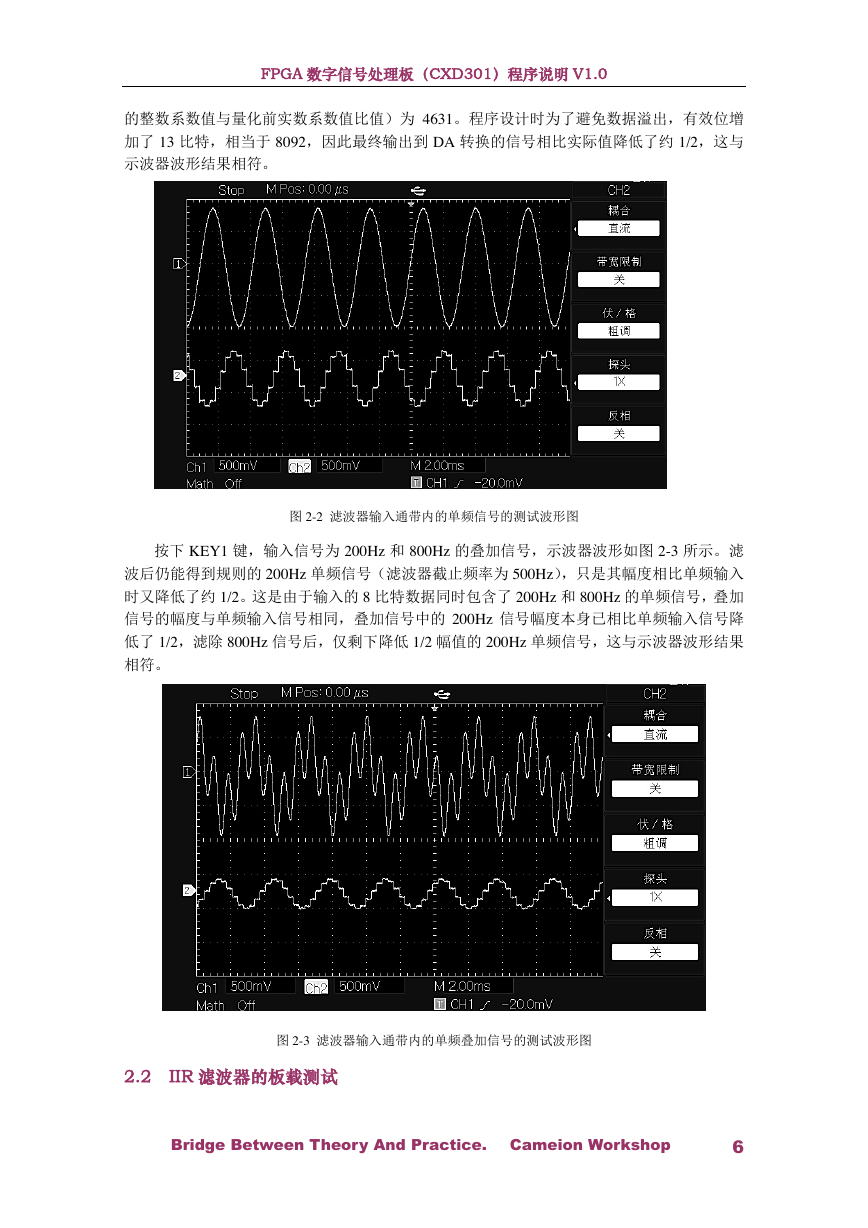

按下 KEY1 键,输入信号为 200Hz 和 800Hz 的叠加信号,示波器波形如图 2-3 所示。滤

波后仍能得到规则的 200Hz 单频信号(滤波器截止频率为 500Hz),只是其幅度相比单频输入

时又降低了约 1/2。这是由于输入的 8 比特数据同时包含了 200Hz 和 800Hz 的单频信号,叠加

信号的幅度与单频输入信号相同,叠加信号中的 200Hz 信号幅度本身已相比单频输入信号降

低了 1/2,滤除 800Hz 信号后,仅剩下降低 1/2 幅值的 200Hz 单频信号,这与示波器波形结果

相符。

图 2-3 滤波器输入通带内的单频叠加信号的测试波形图

2.2 IIR 滤波器的板载测试

Bridge Between Theory And Practice. Cameion Workshop

6

�

FPGA 数字信号处理板(CXD301)程序说明 V1.0

(FilterVHDL\Chapter_5\E5_5_IIRCasDesign\IIRCas)

1)功能说明

IIR 低通滤波器:DA 通道 1 输出频率为 200Hz 和 800Hz 的叠加信号,经 FPGA 低通滤波

后,滤除 800Hz 的信号,DA 通道 2 仅输出 200Hz 单频信号。

2)硬件接口电路

本次实验的目的在于验证 级联型结构的 IIR 滤波器电路工作情况,即验证顶层文件

IIRCas.vhd 程序是否能够完成对输入信号的滤波功能。

CXD301 开发板配置有 2 路独立的 DA 接口、1 路 AD 接口、2 个独立的晶振。为尽量真

实地模拟通信中的滤波过程,采用晶振X2(gclk1)作为驱动时钟,产生频率为200Hz 和 800Hz

的正弦波叠加信号,经 DA1 通道输出;DA1 通道输出的模拟信号通过电路板上的 P2 跳线端

子(管脚 2、3 短接)物理连接至 AD 通道,送入 FPGA 进行处理;FPGA 低通滤波后的信号

经处理后,由 DA2 通道输出;DA2 和 AD 通道的驱动时钟由 X1(gclk2)提供,即实验中的

收、发时钟完全独立。程序下载到电路板后,通过示波器同时观察 DA1、DA2 通道的信号波

形,即可判断滤波前后信号的变化情况。实验电路的 FPGA 接口信号定义如表 2-2 所示。

表 2-2 IIR 低通滤波器实验接口信号定义表

信号名称

管脚定义

传输方向

功能说明

reset

gclk1

gclk2

key1

ad_clk

K3

C10

H3

K1

P6

->FPGA

复位信号,高电平有效

->FPGA

生成合成测试信号的驱动时钟

->FPGA

接收处理及 DA2 转换的驱动时钟

按键信号,按下为高电平;按下时

->FPGA

AD 输入为合成信号,否则为 200Hz

单频信号。

FPGA->

AD 采样时钟信号,2kHz

ad_din[7:0] P7 、T6、R7、T7、T8、R9、T9、P9

->FPGA

AD 采样输入信号,8 比特

da1_clk

P2

FPGA->

DA1 转换时钟信号,2.048MHz

da1_out[7:0] R2 、R1、P1、N3、M3、N1、M2、M1

FPGA->

DA1 转换信号,模拟的测试信号

da2_clk

P15

FPGA->

DA2 转换时钟信号,2kHz

da2_out[7:0]

FPGA->

DA2 转换信号,滤波后输出的信号

L16、M16、M15、N16、P16、R16、

R15、T15

3) 板载测试验证

设计好板载测试程序并完成 FPGA 实现后,可以将程序下载至 CXD301 进行板载测试。

板载测试的硬件连接图如图 2-4 所示。

Bridge Between Theory And Practice. Cameion Workshop

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc