《现代电子技术》2006 年第 13 期总第 228 期

测试 ·测量 ·自动化

基于 VHDL 的数控分频器设计及应用

郭海青

(青海师范大学 青海 西宁 810008)

摘 要 :数控分频器的输出信号频率为输入数据的函数 。用传统的方法设计 ,其设计过程和电路都比较复杂 ,且设计成

果的可修改性和可移植性都较差 。基于 V HDL 的数控分频器设计 ,整个过程简单 、快捷 ,极易修改 ,可移植性强 。他可利用

并行预置数的加法计数器和减法计数器实现 。广泛应用于电子仪器 、乐器等数字电子系统中 。

关键词 :数控分频器 ;V HDL 设计 ;计数器 ;信号

中图分类号 : TP312 文献标识码 :B 文章编号 :1004

373X(2006) 13

099

03

Design and Application of the Numerical Control Frequency

Division Machine Based on VHDL

GUO Haiqing

(Qinghai Normal University ,Xining ,810008 ,China)

Abstract : The output signal of the numerical control f requency division machine is the f unction of the inp ut data. Both the

design p rocess and the circuit are very complicated if designed by the conventional method. Moreover ,the modification and the

replantation of the design f ruit s are very bad. The design process of the numerical control f requency division machine is simple ,

shortcut ,simply modified and replanted. It can realize by using the adder and the subtracter of parallel initialized data. It is

widely applied in the electron instrument and musical instrument of the electron system.

Keywords :numerical control f requency division machine ;V HDL design ;counter ;signal

1 引 言

数控分频器的功能是在输入端输入不同数据时 ,对输

入时钟产生不同的分频比 ,使输出信号的频率为输入数据

的函数。他可广泛应用于数字电子系统中 。

用传统的设计方法设计数控分频器时 ,采用具有预置

数据输入端的通用计数器芯片 ,按设计要求完成设计 ,其

设计过程和电路都比较复杂 ,尤其是当分频系数比较大

时 ,需用多片集成计数器和设计更复杂的控制电路来实

现 ,且设计成果的可修改性和可移植性都较差 。

基于 V HDL 的数控分频器设计 ,采用用软件的方法

设计硬件的 EDA ( 电子设计自动化) 技术 。作为 EDA 技

术重要组成部分的硬件描述语言 ,V HDL 是一种 IEEE 工

业标准的建模语言。由于 V HDL 具有很强的电路行为描

述 、系统描述能力和层次化的程序结构 ,用他设计的数控

分频器作为一个模块 ,可移植到很多数字电路系统中 ,且

极易修改 ,只要修改程序中的某几条语句 ,就可使最大分

频系数得到改变。整个设计过程简单、快捷。另外由于

V HDL 具有与硬件和设计平台无关的特点 ,设计结果可通

过众多 EDA 平台下载到各种 CPLD 或 FP GA 可编程器件

中 ,实现单片化的数字电路 ,使得工作稳定 、可靠。

2 数控分频器的 VHDL 设计

2. 1 利用并行预置数的加法计数器实现[ 1 ]

设计原理 :加法计数器在并行预置数的基础上进行加

计数 ,当计数值溢出时产生预置数据置入控制信号 ,加载

预置数据 ,并且将溢出信号作为分频器的输出信号 ,实现

不同的分频信号输出。

设计实例 :4 位数控分频器

- 略去申明部分

-

entity skf

port (clk :in std logic ;

d :in std logic vector (3 downto 0 ) ;

div is

:out std logic) ;

fout

end skf

div ;

architecture a of skf

signal f ull

begin

process (clk )

variable cnt4 :std logic

: std logic ;

div is

-

- 定义预置数据输入端

- 定义输出端

-

-

- 定义内部溢出标志信号

vector (3 downto 0 ) ;

收稿日期 :2006

02

09

if clk′event and clk = ′1′then

-

- 内部变量 ,位宽同预置数据端 begin

99

�

数 控 技 术

郭海青 :基于 V HDL 的数控分频器设计及应用

if cnt4 = " 1111" then f ull < = ′1′;

cnt4 : = d ;

else cnt4 : = cnt4 + 1 ; f ull < = ′0′;

-

- 当计数计满时 ,产生溢出信号

- 同时 ,同步加载预置数据 d

-

-

- 否则 ,进行加 1 计数

end if ;

end if ;

end process ;

fout < = f ull ; -

end a ;

- 将溢出信号赋予分频器的输出端

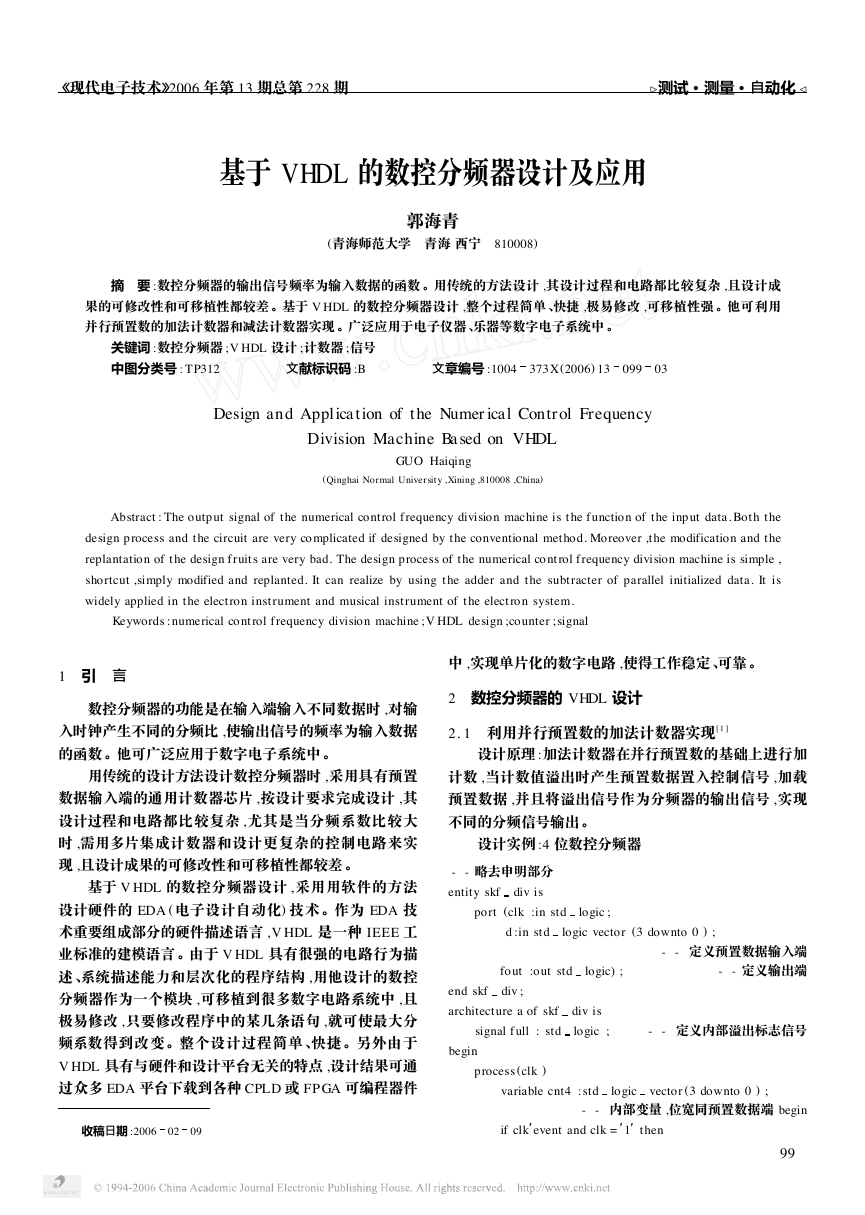

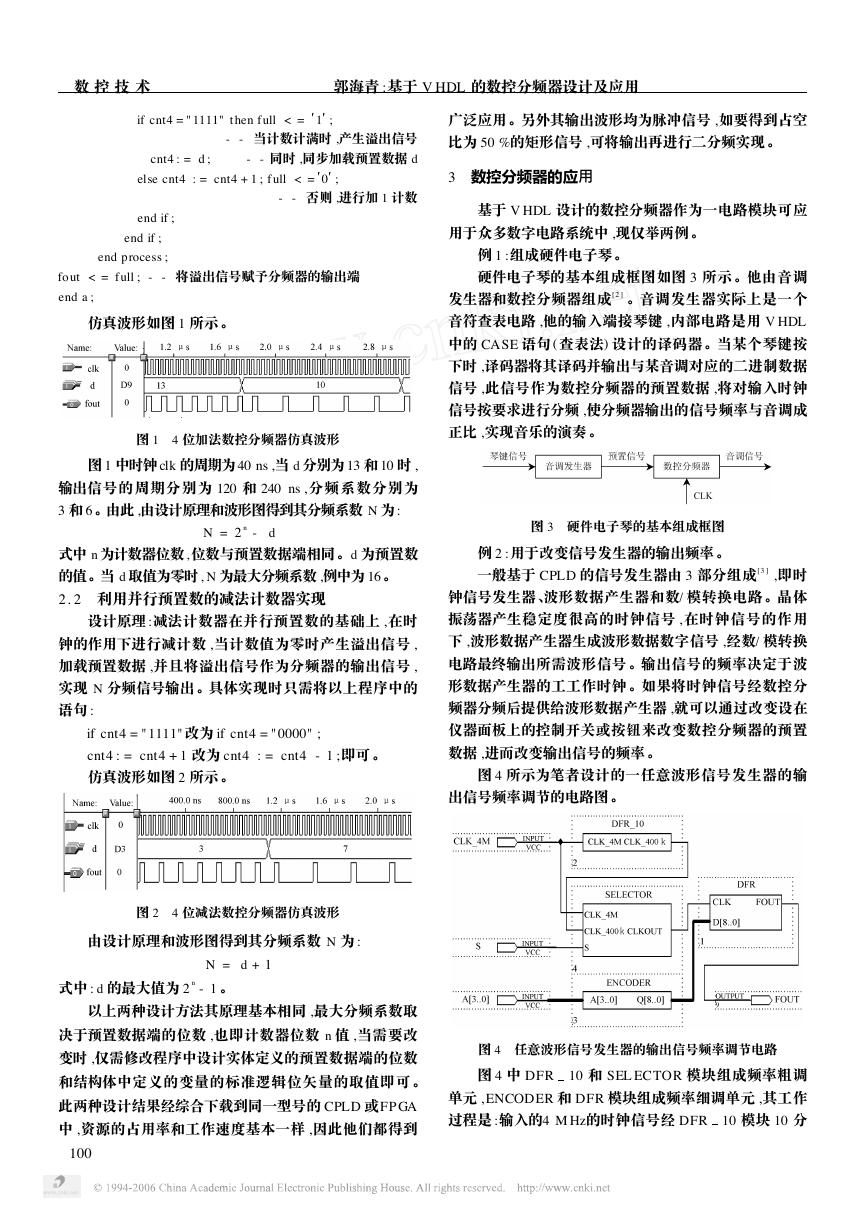

仿真波形如图 1 所示 。

图 1 4 位加法数控分频器仿真波形

图 1 中时钟 clk 的周期为 40 ns ,当 d 分别为 13 和 10 时 ,

输出信号的周期分别为 120 和 240 ns ,分频系数分别为

3 和 6。由此 ,由设计原理和波形图得到其分频系数 N 为 :

N = 2 n - d

式中 n 为计数器位数 ,位数与预置数据端相同。d 为预置数

的值。当 d 取值为零时 , N 为最大分频系数 ,例中为 16。

2. 2 利用并行预置数的减法计数器实现

设计原理 :减法计数器在并行预置数的基础上 ,在时

钟的作用下进行减计数 ,当计数值为零时产生溢出信号 ,

加载预置数据 ,并且将溢出信号作为分频器的输出信号 ,

实现 N 分频信号输出。具体实现时只需将以上程序中的

语句 :

if cnt4 = "1111" 改为 if cnt4 = " 0000" ;

cnt4 : = cnt4 + 1 改为 cnt4 : = cnt4 - 1 ;即可。

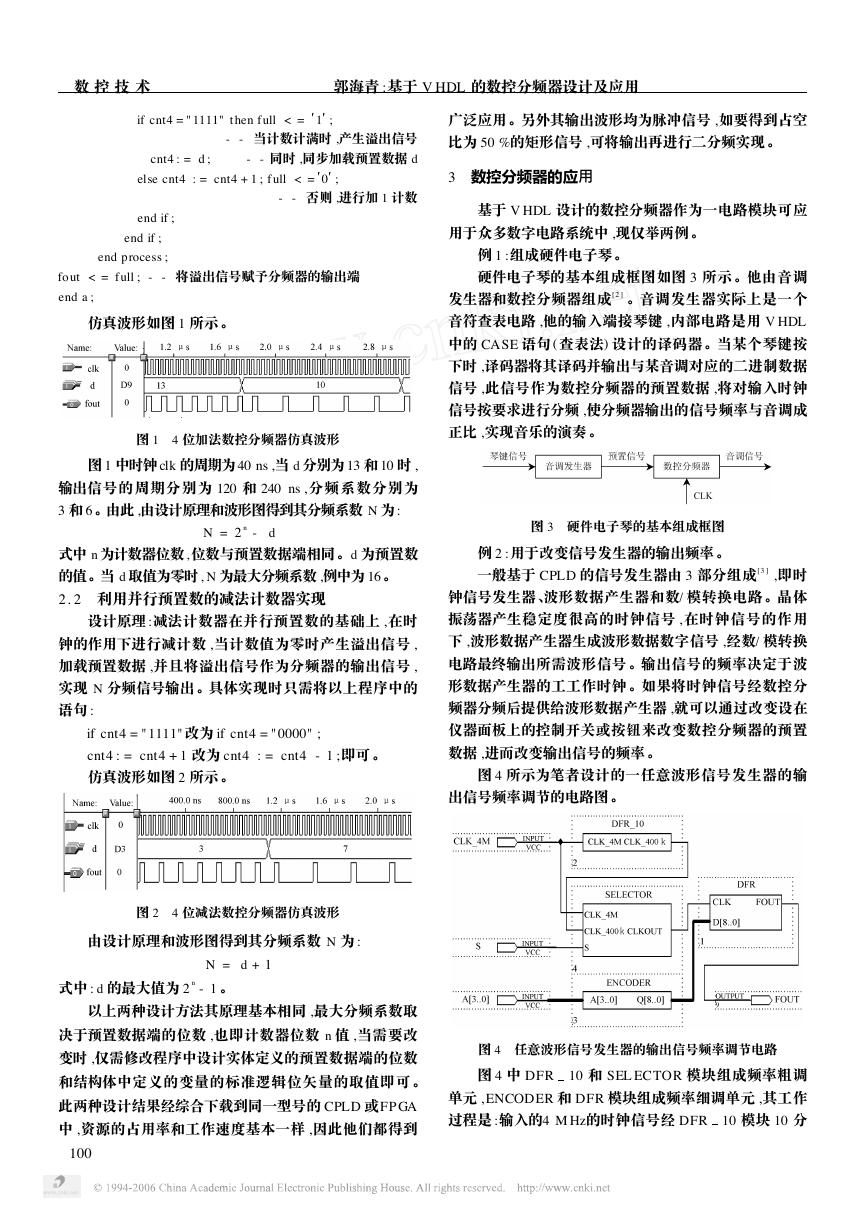

仿真波形如图 2 所示 。

图 2 4 位减法数控分频器仿真波形

由设计原理和波形图得到其分频系数 N 为 :

式中 : d 的最大值为 2 n - 1 。

N = d + 1

以上两种设计方法其原理基本相同 ,最大分频系数取

决于预置数据端的位数 ,也即计数器位数 n 值 ,当需要改

变时 ,仅需修改程序中设计实体定义的预置数据端的位数

和结构体中定义的变量的标准逻辑位矢量的取值即可 。

此两种设计结果经综合下载到同一型号的 CPLD 或FP GA

中 ,资源的占用率和工作速度基本一样 ,因此他们都得到

001

广泛应用 。另外其输出波形均为脉冲信号 ,如要得到占空

比为 50 %的矩形信号 ,可将输出再进行二分频实现 。

3 数控分频器的应用

基于 V HDL 设计的数控分频器作为一电路模块可应

用于众多数字电路系统中 ,现仅举两例 。

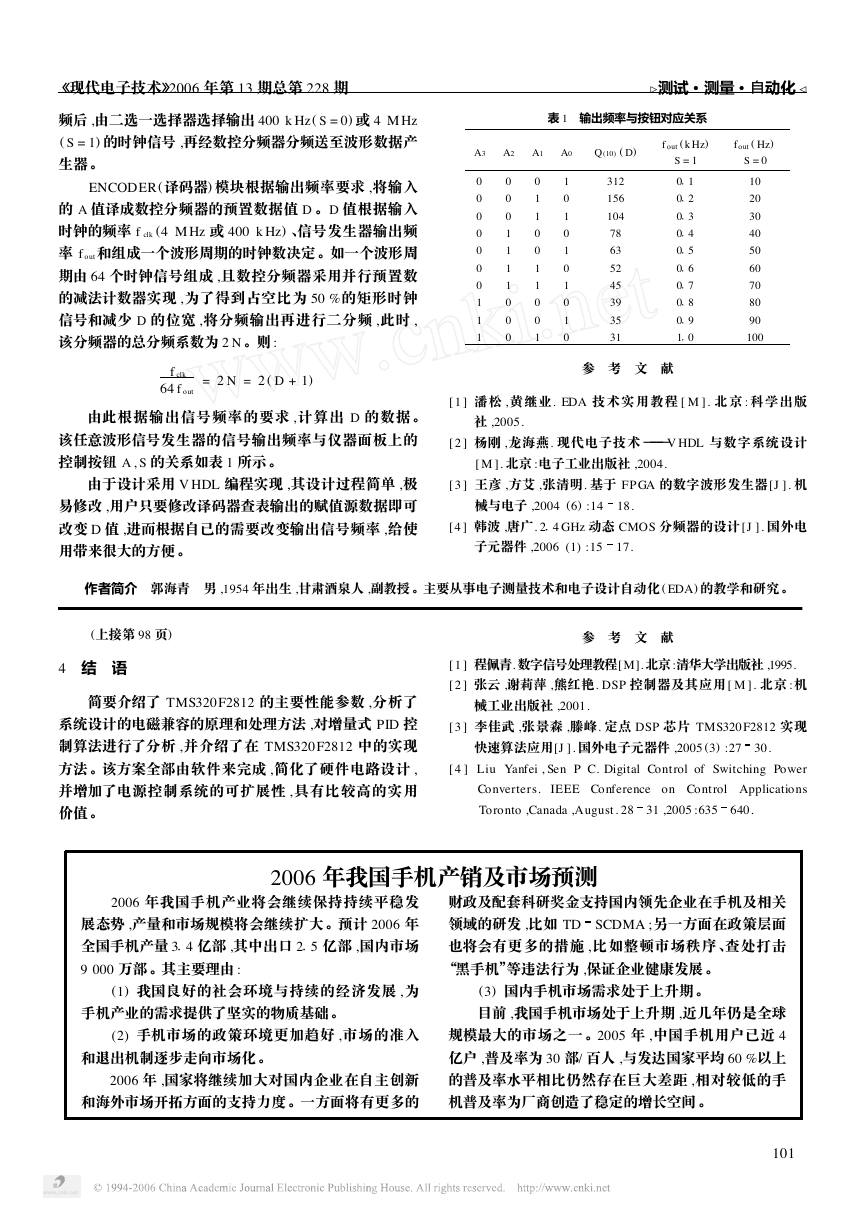

例 1 :组成硬件电子琴 。

硬件电子琴的基本组成框图如图 3 所示。他由音调

发生器和数控分频器组成[2 ] 。音调发生器实际上是一个

音符查表电路 ,他的输入端接琴键 ,内部电路是用 V HDL

中的 CASE 语句 (查表法) 设计的译码器 。当某个琴键按

下时 ,译码器将其译码并输出与某音调对应的二进制数据

信号 ,此信号作为数控分频器的预置数据 ,将对输入时钟

信号按要求进行分频 ,使分频器输出的信号频率与音调成

正比 ,实现音乐的演奏 。

图 3 硬件电子琴的基本组成框图

例 2 :用于改变信号发生器的输出频率。

一般基于 CPLD 的信号发生器由 3 部分组成[3 ] ,即时

钟信号发生器 、波形数据产生器和数/ 模转换电路 。晶体

振荡器产生稳定度很高的时钟信号 ,在时钟信号的作用

下 ,波形数据产生器生成波形数据数字信号 ,经数/ 模转换

电路最终输出所需波形信号 。输出信号的频率决定于波

形数据产生器的工工作时钟 。如果将时钟信号经数控分

频器分频后提供给波形数据产生器 ,就可以通过改变设在

仪器面板上的控制开关或按钮来改变数控分频器的预置

数据 ,进而改变输出信号的频率 。

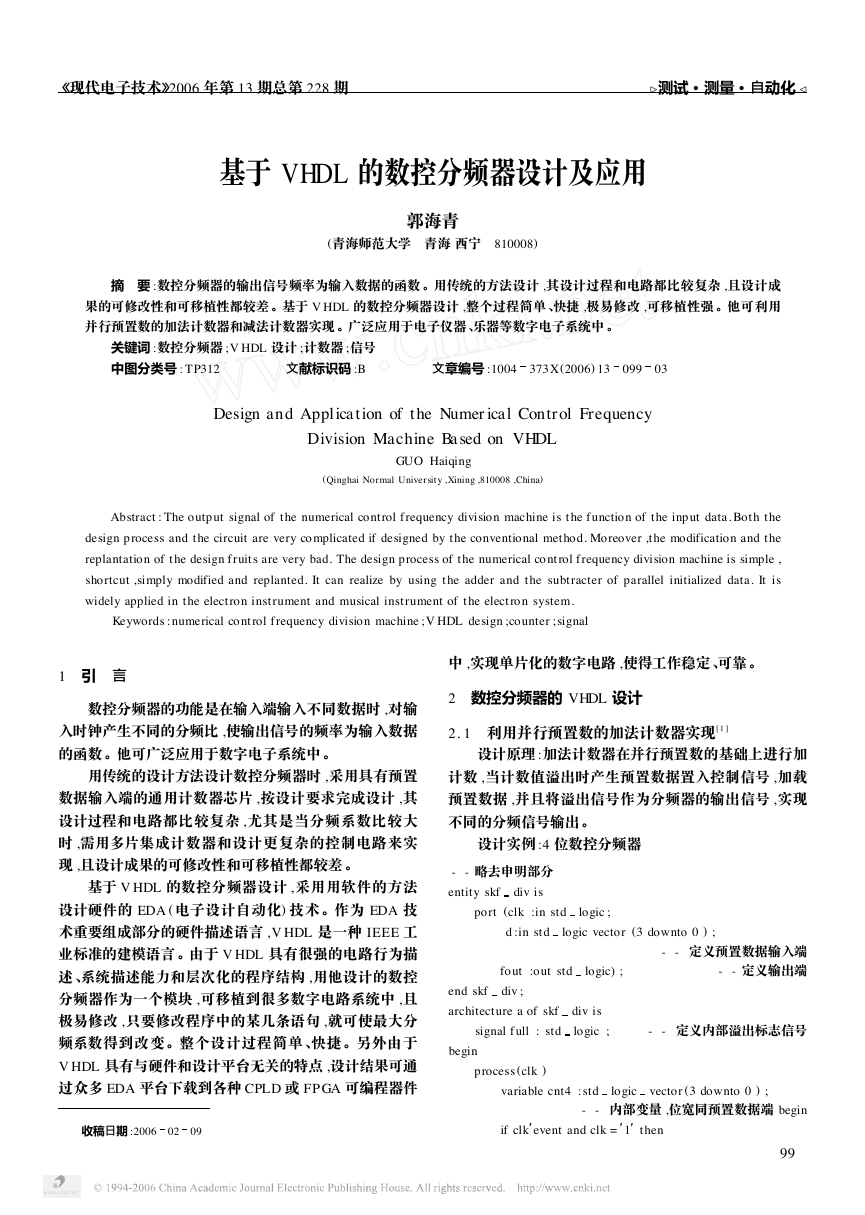

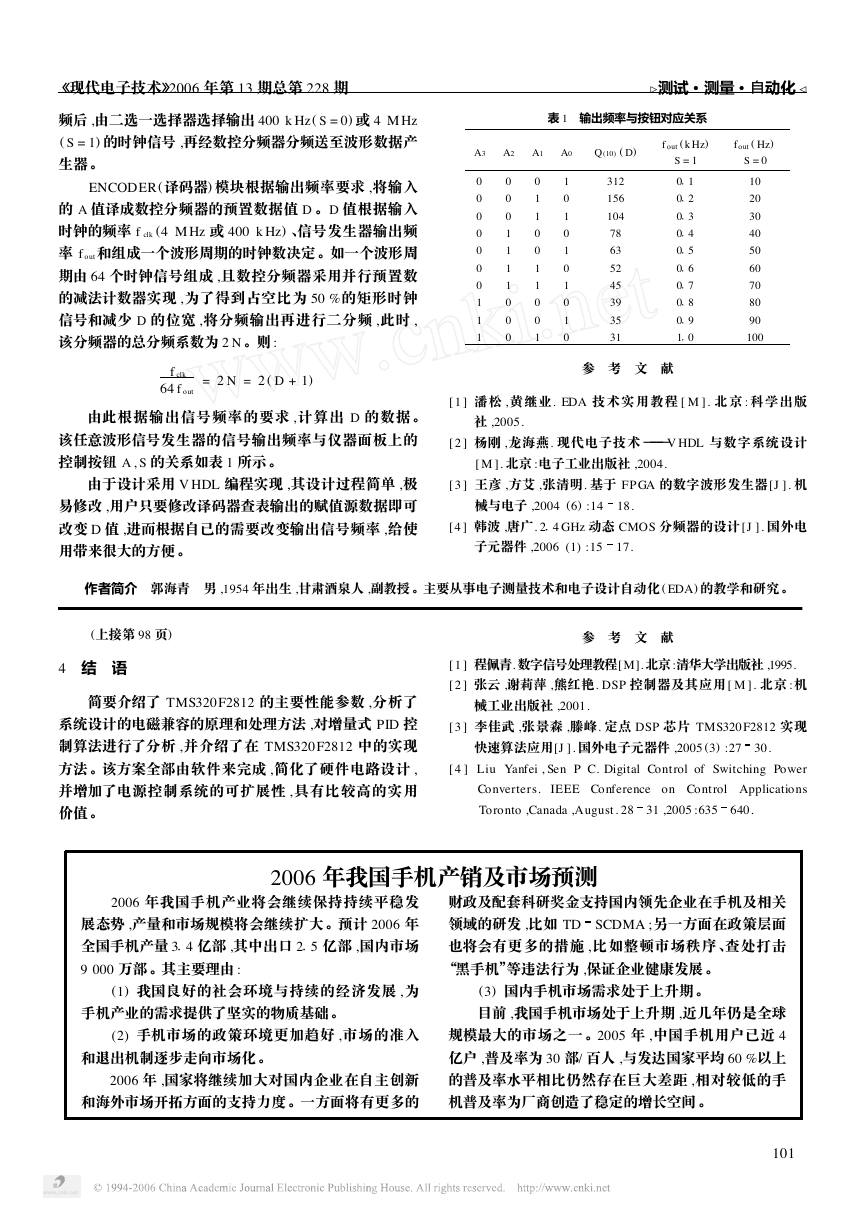

图 4 所示为笔者设计的一任意波形信号发生器的输

出信号频率调节的电路图。

图 4 任意波形信号发生器的输出信号频率调节电路

图 4 中 DFR 10 和 SEL ECTOR 模块组成频率粗调

单元 , ENCODER 和 DFR 模块组成频率细调单元 ,其工作

过程是 :输入的4 M Hz的时钟信号经 DFR 10 模块 10 分

�

《现代电子技术》2006 年第 13 期总第 228 期

测试 ·测量 ·自动化

频后 ,由二选一选择器选择输出 400 k Hz ( S = 0) 或 4 M Hz

( S = 1) 的时钟信号 ,再经数控分频器分频送至波形数据产

生器。

ENCODER(译码器) 模块根据输出频率要求 ,将输入

的 A 值译成数控分频器的预置数据值 D 。D 值根据输入

时钟的频率 f clk (4 M Hz 或 400 k Hz) 、信号发生器输出频

率 f out 和组成一个波形周期的时钟数决定 。如一个波形周

期由 64 个时钟信号组成 ,且数控分频器采用并行预置数

的减法计数器实现 ,为了得到占空比为 50 %的矩形时钟

信号和减少 D 的位宽 ,将分频输出再进行二分频 ,此时 ,

该分频器的总分频系数为 2 N 。则 :

f clk

64 f out

= 2 N = 2 ( D + 1)

由此根据输出信号频率的要求 ,计算出 D 的数据 。

该任意波形信号发生器的信号输出频率与仪器面板上的

控制按钮 A , S 的关系如表 1 所示 。

由于设计采用 V HDL 编程实现 ,其设计过程简单 ,极

易修改 ,用户只要修改译码器查表输出的赋值源数据即可

改变 D 值 ,进而根据自已的需要改变输出信号频率 ,给使

用带来很大的方便。

表 1 输出频率与按钮对应关系

A 3 A 2 A 1 A 0

Q (10) ( D)

f out ( k Hz)

S = 1

fout ( Hz)

S = 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

312

156

104

78

63

52

45

39

35

31

0

0

0

0

0

0

0

0

0

1

1

2

3

4

5

6

7

8

9

0

10

20

30

40

50

60

70

80

90

100

参 考 文 献

[ 1 ] 潘松 , 黄继业. EDA 技术实用教程 [ M ]. 北京 : 科学出版

社 ,2005.

[ 2 ] 杨刚 ,龙海燕. 现代电子技术 ———V HDL 与数字系统设计

[ M ]. 北京 :电子工业出版社 ,2004.

[ 3 ] 王彦 ,方艾 ,张清明. 基于 FP GA 的数字波形发生器 [J ]. 机

械与电子 ,2004 (6) :14

18.

[4 ] 韩波 ,唐广. 2

4 GHz 动态 CMOS 分频器的设计 [J ]. 国外电

子元器件 ,2006 (1) :15

17.

作者简介 郭海青 男 ,1954 年出生 ,甘肃酒泉人 ,副教授 。主要从事电子测量技术和电子设计自动化 ( EDA) 的教学和研究 。

(上接第 98 页)

4 结 语

简要介绍了 TMS320F2812 的主要性能参数 ,分析了

系统设计的电磁兼容的原理和处理方法 ,对增量式 PID 控

制算法进行了分析 ,并介绍了在 TMS320F2812 中的实现

方法。该方案全部由软件来完成 ,简化了硬件电路设计 ,

并增加了电源控制系统的可扩展性 ,具有比较高的实用

价值。

参 考 文 献

[ 1 ] 程佩青. 数字信号处理教程[M]. 北京 :清华大学出版社 ,1995.

[ 2 ] 张云 ,谢莉萍 ,熊红艳. DSP 控制器及其应用 [ M ]. 北京 :机

械工业出版社 ,2001.

[ 3 ] 李佳武 ,张景森 ,滕峰. 定点 DSP 芯片 TMS320F2812 实现

快速算法应用[J ]. 国外电子元器件 ,2005 (3) :27

30.

[ 4 ] Liu Yanfei , Sen P C. Digital Control of Switching Power

IEEE Conference on Control Applications

Converters.

Toronto ,Canada ,August . 28

31 ,2005 :635

640.

2006 年我国手机产销及市场预测

2006 年我国手机产业将会继续保持持续平稳发

展态势 ,产量和市场规模将会继续扩大 。预计 2006 年

全国手机产量 3

5 亿部 ,国内市场

9 000 万部 。其主要理由 :

4 亿部 ,其中出口 2

财政及配套科研奖金支持国内领先企业在手机及相关

领域的研发 ,比如 TD SCDMA ;另一方面在政策层面

也将会有更多的措施 ,比如整顿市场秩序 、查处打击

“黑手机”等违法行为 ,保证企业健康发展。

(1) 我国良好的社会环境与持续的经济发展 ,为

手机产业的需求提供了坚实的物质基础 。

(2) 手机市场的政策环境更加趋好 ,市场的准入

和退出机制逐步走向市场化。

2006 年 ,国家将继续加大对国内企业在自主创新

和海外市场开拓方面的支持力度 。一方面将有更多的

(3) 国内手机市场需求处于上升期 。

目前 ,我国手机市场处于上升期 ,近几年仍是全球

规模最大的市场之一 。2005 年 ,中国手机用户已近 4

亿户 ,普及率为 30 部/ 百人 ,与发达国家平均 60 %以上

的普及率水平相比仍然存在巨大差距 ,相对较低的手

机普及率为厂商创造了稳定的增长空间 。

101

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc