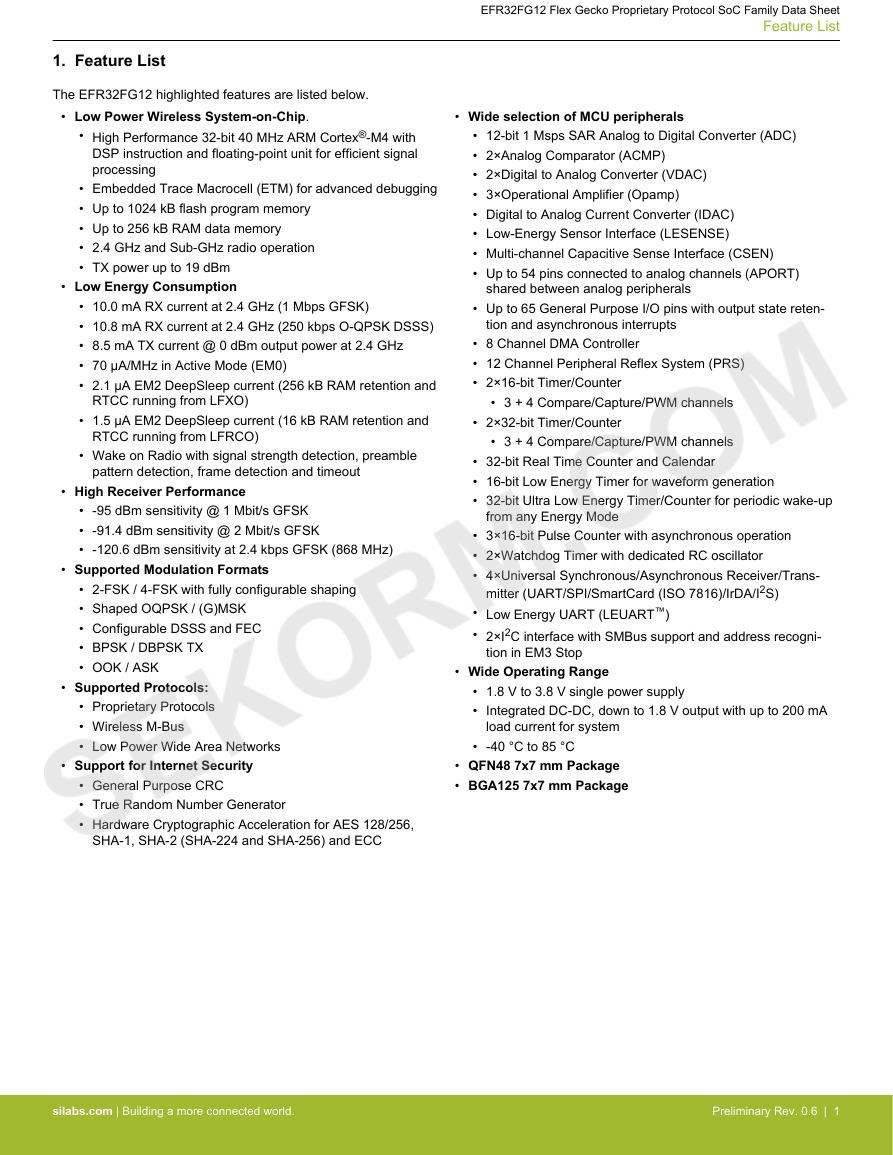

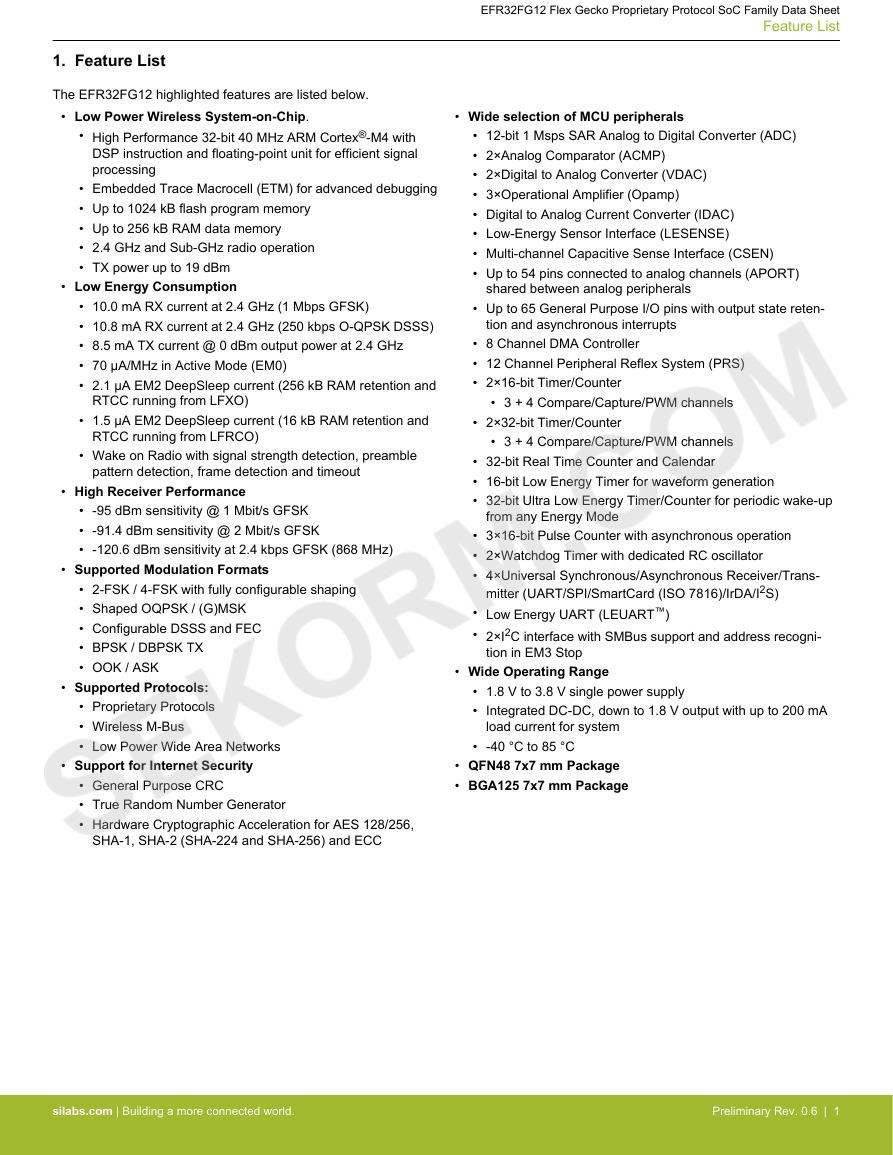

1. Feature List

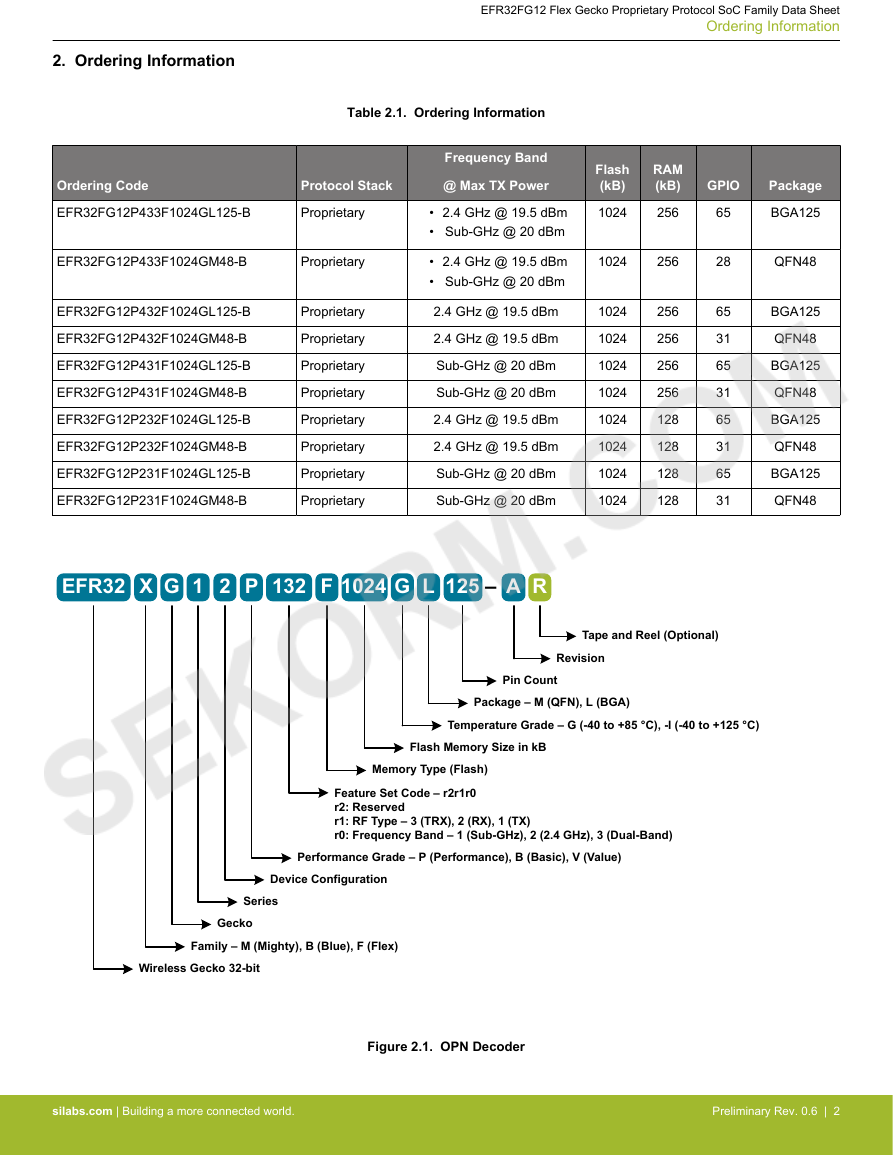

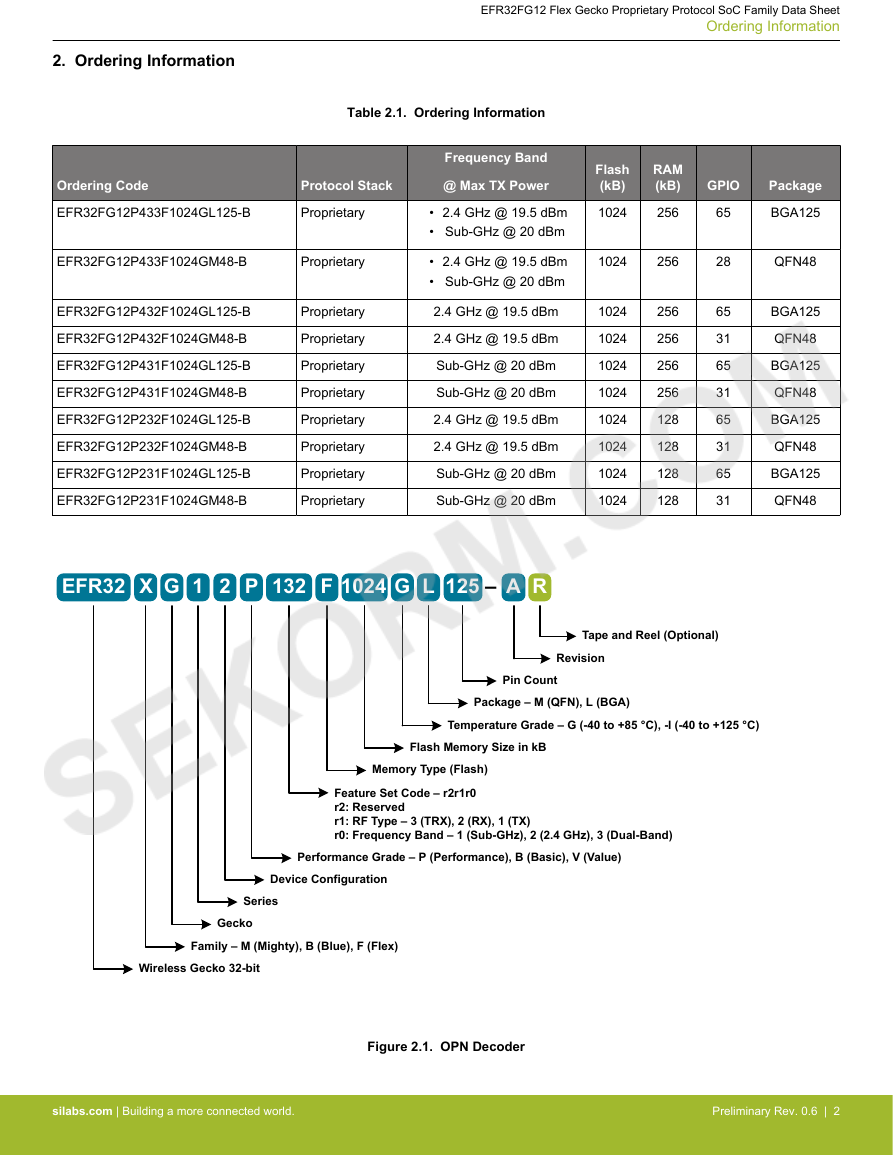

2. Ordering Information

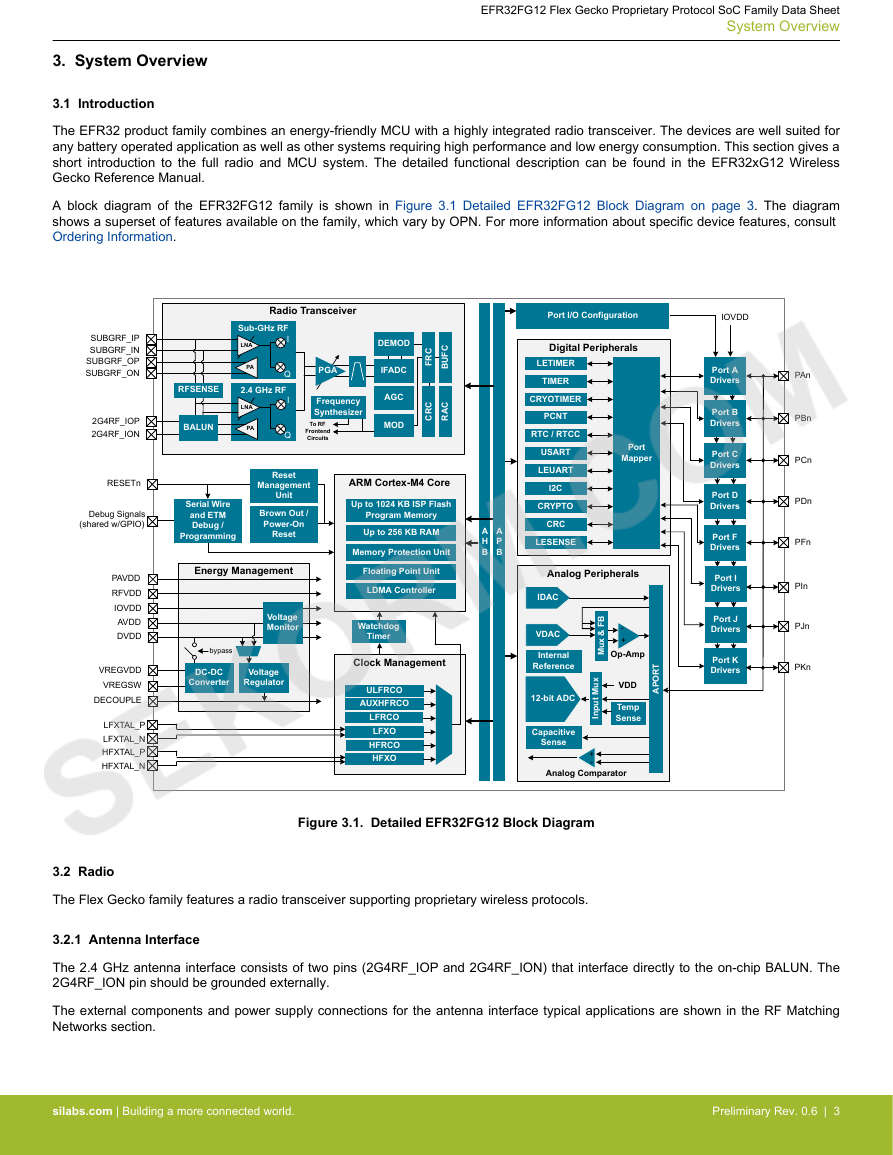

3. System Overview

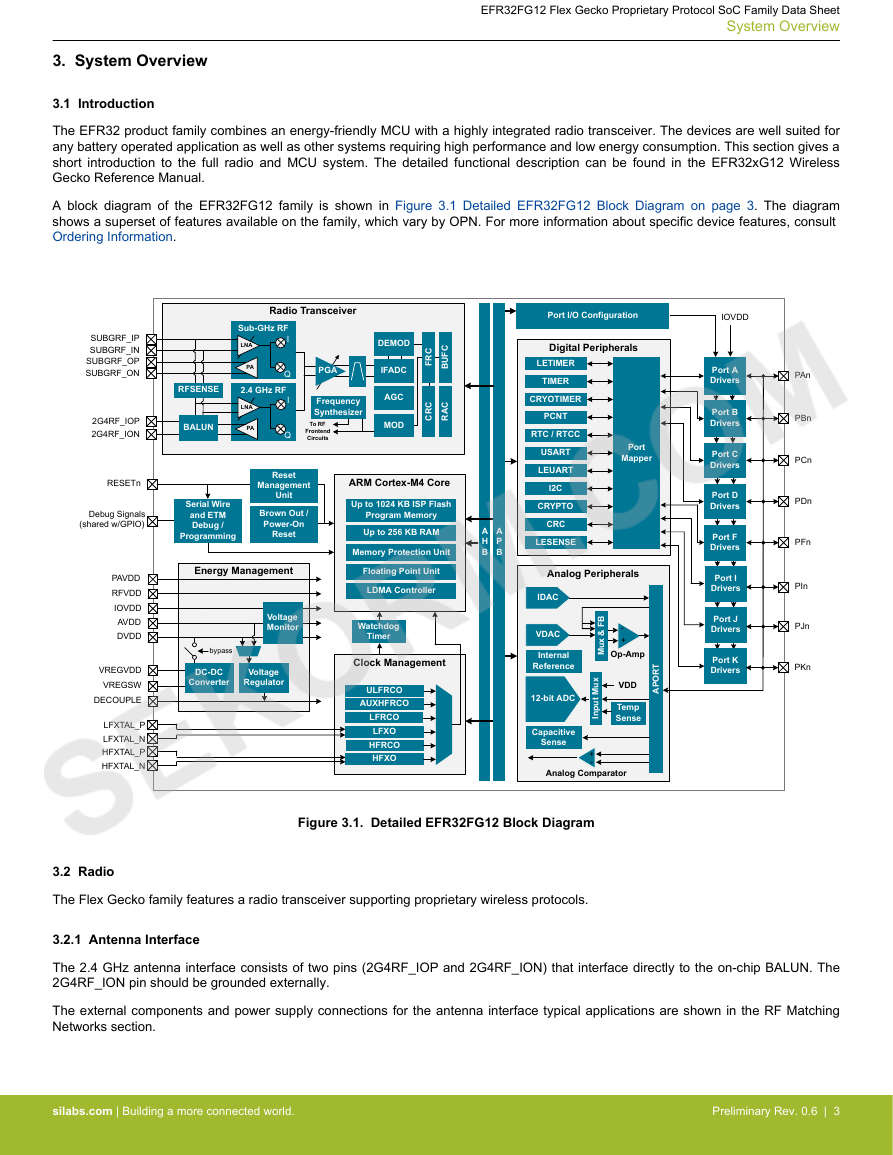

3.1 Introduction

3.2 Radio

3.2.1 Antenna Interface

3.2.2 Fractional-N Frequency Synthesizer

3.2.3 Receiver Architecture

3.2.4 Transmitter Architecture

3.2.5 Wake on Radio

3.2.6 RFSENSE

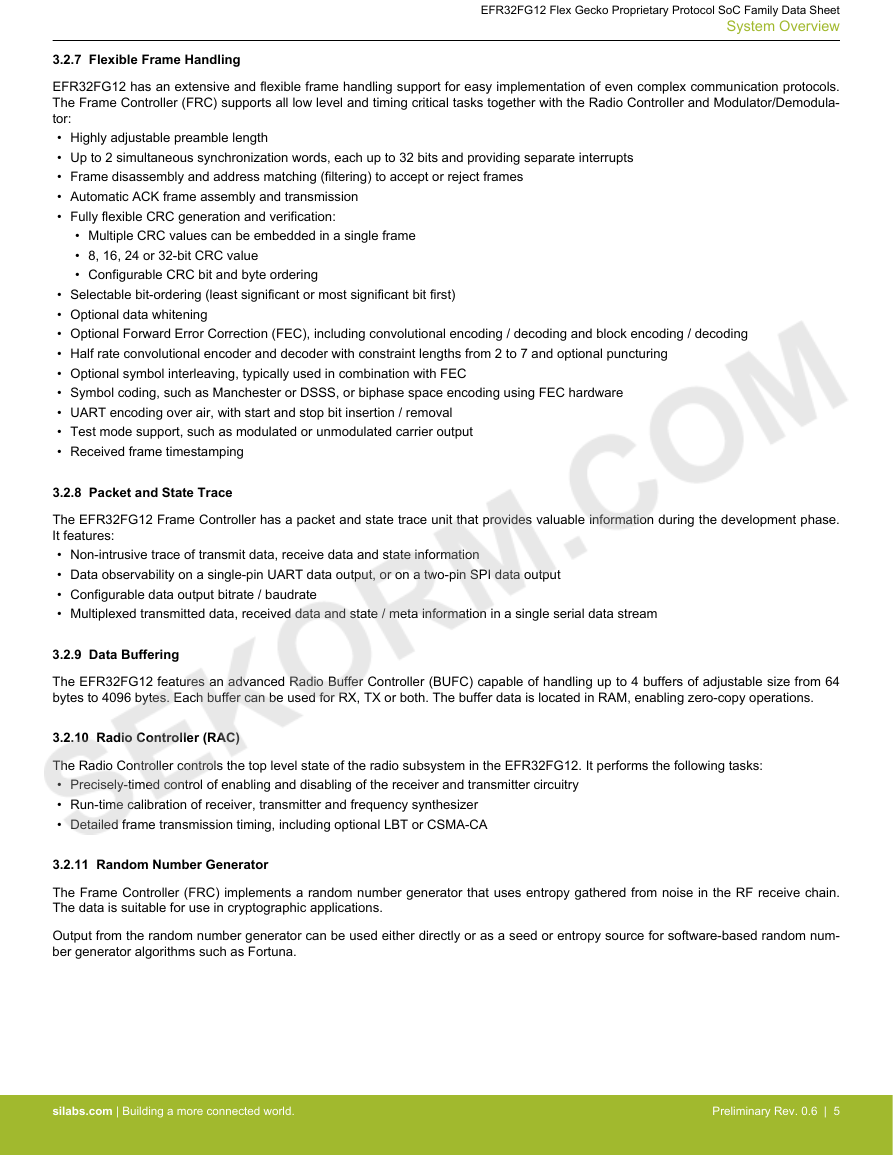

3.2.7 Flexible Frame Handling

3.2.8 Packet and State Trace

3.2.9 Data Buffering

3.2.10 Radio Controller (RAC)

3.2.11 Random Number Generator

3.3 Power

3.3.1 Energy Management Unit (EMU)

3.3.2 DC-DC Converter

3.3.3 Power Domains

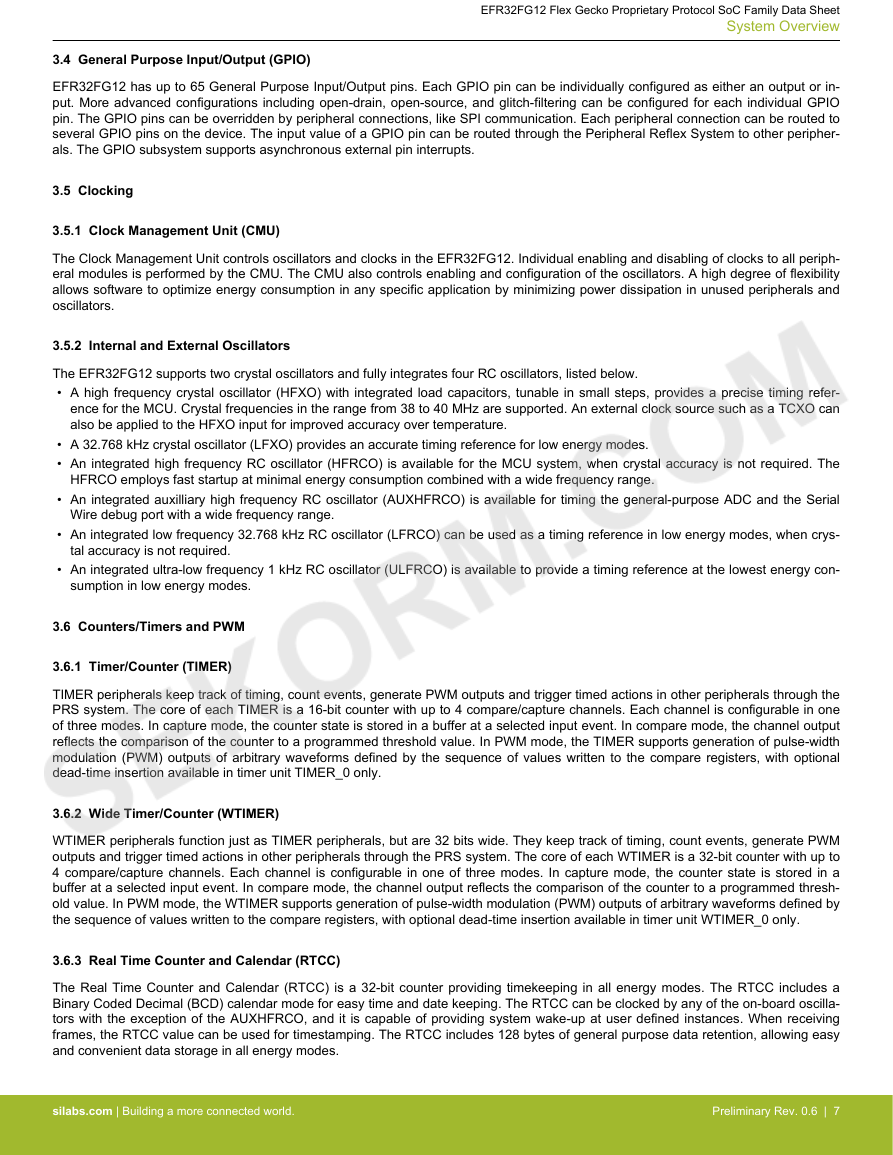

3.4 General Purpose Input/Output (GPIO)

3.5 Clocking

3.5.1 Clock Management Unit (CMU)

3.5.2 Internal and External Oscillators

3.6 Counters/Timers and PWM

3.6.1 Timer/Counter (TIMER)

3.6.2 Wide Timer/Counter (WTIMER)

3.6.3 Real Time Counter and Calendar (RTCC)

3.6.4 Low Energy Timer (LETIMER)

3.6.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

3.6.6 Pulse Counter (PCNT)

3.6.7 Watchdog Timer (WDOG)

3.7 Communications and Other Digital Peripherals

3.7.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

3.7.2 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

3.7.3 Inter-Integrated Circuit Interface (I2C)

3.7.4 Peripheral Reflex System (PRS)

3.7.5 Low Energy Sensor Interface (LESENSE)

3.8 Security Features

3.8.1 GPCRC (General Purpose Cyclic Redundancy Check)

3.8.2 Crypto Accelerator (CRYPTO)

3.8.3 True Random Number Generator (TRNG)

3.8.4 Security Management Unit (SMU)

3.9 Analog

3.9.1 Analog Port (APORT)

3.9.2 Analog Comparator (ACMP)

3.9.3 Analog to Digital Converter (ADC)

3.9.4 Capacitive Sense (CSEN)

3.9.5 Digital to Analog Current Converter (IDAC)

3.9.6 Digital to Analog Converter (VDAC)

3.9.7 Operational Amplifiers

3.10 Reset Management Unit (RMU)

3.11 Core and Memory

3.11.1 Processor Core

3.11.2 Memory System Controller (MSC)

3.11.3 Linked Direct Memory Access Controller (LDMA)

3.12 Memory Map

3.13 Configuration Summary

4. Electrical Specifications

4.1 Electrical Characteristics

4.1.1 Absolute Maximum Ratings

4.1.2 Operating Conditions

4.1.2.1 General Operating Conditions

4.1.3 DC-DC Converter

4.1.4 Current Consumption

4.1.4.1 Current Consumption 3.3 V without DC-DC Converter

4.1.4.2 Current Consumption 3.3 V using DC-DC Converter

4.1.4.3 Current Consumption 1.8 V without DC-DC Converter

4.1.4.4 Current Consumption Using Radio 3.3 V with DC-DC

4.1.5 Wake Up Times

4.1.6 Brown Out Detector (BOD)

4.1.7 Frequency Synthesizer

4.1.8 2.4 GHz RF Transceiver Characteristics

4.1.8.1 RF Transmitter General Characteristics for 2.4 GHz Band

4.1.8.2 RF Receiver General Characteristics for 2.4 GHz Band

4.1.8.3 RF Transmitter Characteristics for 1Mbps 2GFSK in the 2.4GHz Band, 1 Mbps Data Rate

4.1.8.4 RF Receiver Characteristics for 1Mbps 2GFSK in the 2.4GHz Band, 1 Mbps Data Rate

4.1.8.5 RF Transmitter Characteristics for 1Mbps 2GFSK in the 2.4GHz Band, 2 Mbps Data Rate

4.1.8.6 RF Receiver Characteristics for 1Mbps 2GFSK in the 2.4GHz Band, 2 Mbps Data Rate

4.1.8.7 RF Transmitter Characteristics for 802.15.4 DSSS-OQPSK in the 2.4 GHz Band

4.1.8.8 RF Receiver Characteristics for 802.15.4 DSSS-OQPSK in the 2.4 GHz Band

4.1.9 Sub-GHz RF Transceiver Characteristics

4.1.9.1 Sub-GHz RF Transmitter characteristics for 915 MHz Band

4.1.9.2 Sub-GHz RF Receiver Characteristics for 915 MHz Band

4.1.9.3 Sub-GHz RF Transmitter characteristics for 868 MHz Band

4.1.9.4 Sub-GHz RF Receiver Characteristics for 868 MHz Band

4.1.9.5 Sub-GHz RF Transmitter characteristics for 490 MHz Band

4.1.9.6 Sub-GHz RF Receiver Characteristics for 490 MHz Band

4.1.9.7 Sub-GHz RF Transmitter characteristics for 433 MHz Band

4.1.9.8 Sub-GHz RF Receiver Characteristics for 433 MHz Band

4.1.9.9 Sub-GHz RF Transmitter characteristics for 315 MHz Band

4.1.9.10 Sub-GHz RF Receiver Characteristics for 315 MHz Band

4.1.9.11 Sub-GHz RF Transmitter Characteristics for 169 MHz Band

4.1.9.12 Sub-GHz RF Receiver Characteristics for 169 MHz Band

4.1.10 Modem

4.1.11 Oscillators

4.1.11.1 Low-Frequency Crystal Oscillator (LFXO)

4.1.11.2 High-Frequency Crystal Oscillator (HFXO)

4.1.11.3 Low-Frequency RC Oscillator (LFRCO)

4.1.11.4 High-Freqency RC Oscillator (HFRCO)

4.1.11.5 Auxiliary High-Freqency RC Oscillator (AUXHFRCO)

4.1.11.6 Ultra-low Frequency RC Oscillator (ULFRCO)

4.1.12 Flash Memory Characteristics

4.1.13 General-Purpose I/O (GPIO)

4.1.14 Voltage Monitor (VMON)

4.1.15 Analog to Digital Converter (ADC)

4.1.16 Analog Comparator (ACMP)

4.1.17 Digital to Analog Converter (VDAC)

4.1.18 Current Digital to Analog Converter (IDAC)

4.1.19 Capacitive Sense (CSEN)

4.1.20 Operational Amplifier (OPAMP)

4.1.21 Pulse Counter (PCNT)

4.1.22 Analog Port (APORT)

4.1.23 I2C

4.1.23.1 I2C Standard-mode (Sm)

4.1.23.2 I2C Fast-mode (Fm)

4.1.23.3 I2C Fast-mode Plus (Fm+)

4.1.24 USART SPI

4.2 Typical Performance Curves

4.2.1 Supply Current

4.2.2 DC-DC Converter

4.2.3 2.4 GHz Radio

5. Typical Connection Diagrams

5.1 Power

5.2 RF Matching Networks

5.3 Other Connections

6. Pin Definitions

6.1 BGA125 2.4 GHz and Sub-GHz Device Pinout

6.1.1 BGA125 2.4 GHz and Sub-GHz GPIO Overview

6.2 BGA125 2.4 GHz Device Pinout

6.2.1 BGA125 2.4 GHz GPIO Overview

6.3 BGA125 Sub-GHz Device Pinout

6.3.1 BGA125 Sub-GHz GPIO Overview

6.4 QFN48 2.4 GHz and Sub-GHz Device Pinout

6.4.1 QFN48 2.4 GHz and Sub-GHz GPIO Overview

6.5 QFN48 2.4 GHz Device Pinout

6.5.1 QFN48 2.4 GHz GPIO Overview

6.6 QFN48 Sub-GHz Device Pinout

6.6.1 QFN48 Sub-GHz GPIO Overview

6.7 Alternate Functionality Overview

6.8 Analog Port (APORT) Client Maps

7. BGA125 Package Specifications

7.1 BGA125 Package Dimensions

7.2 BGA125 PCB Land Pattern

7.3 BGA125 Package Marking

8. QFN48 Package Specifications

8.1 QFN48 Package Dimensions

8.2 QFN48 PCB Land Pattern

8.3 QFN48 Package Marking

9. Revision History

9.1 Revision 0.6

9.2 Revision 0.5

9.3 Revision 0.2

Table of Contents

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc