ARM Compiler armasm Reference Guide

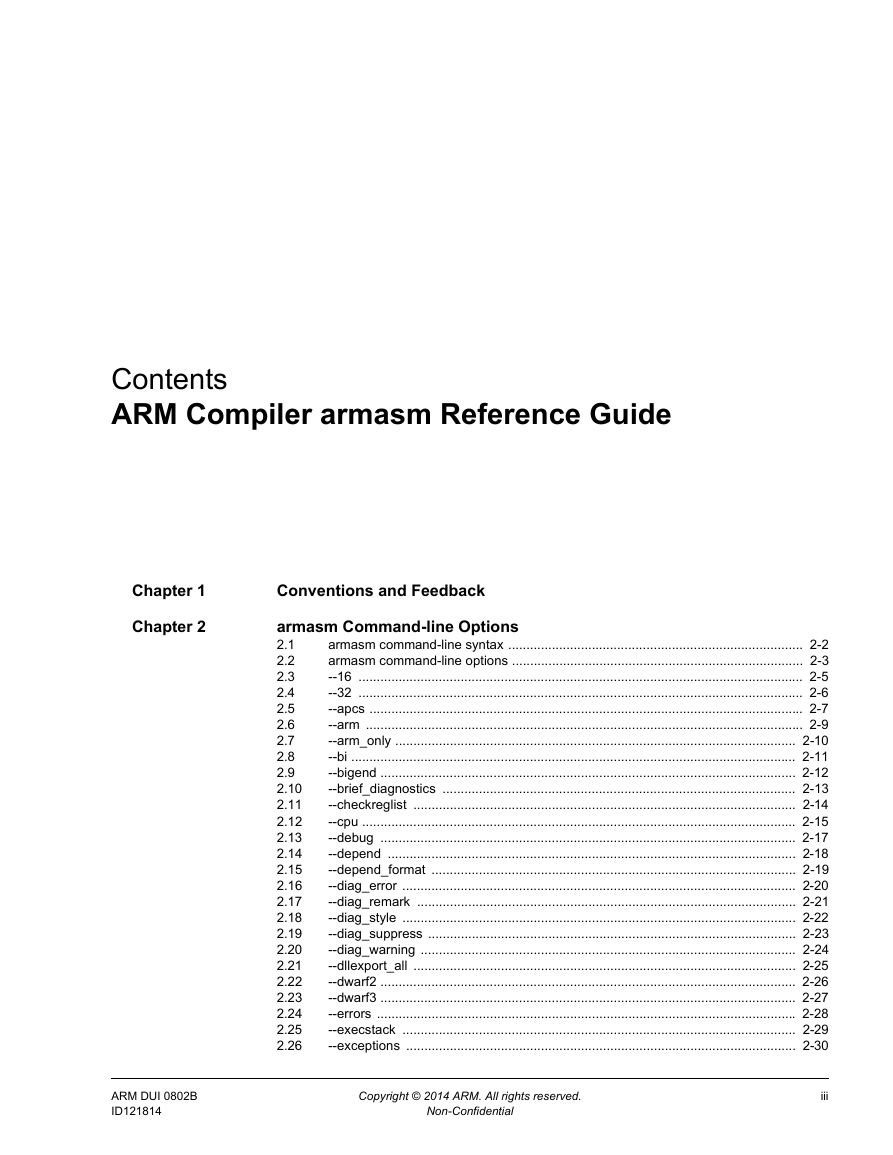

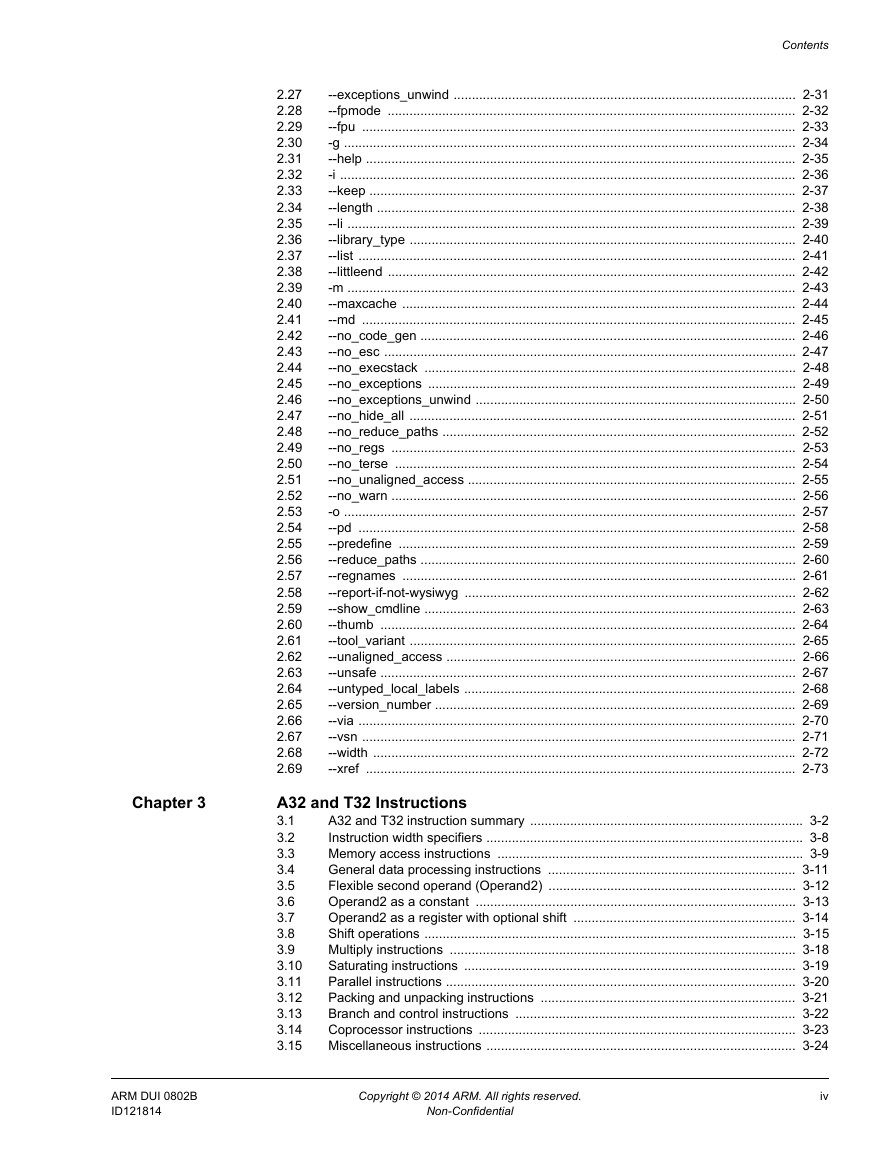

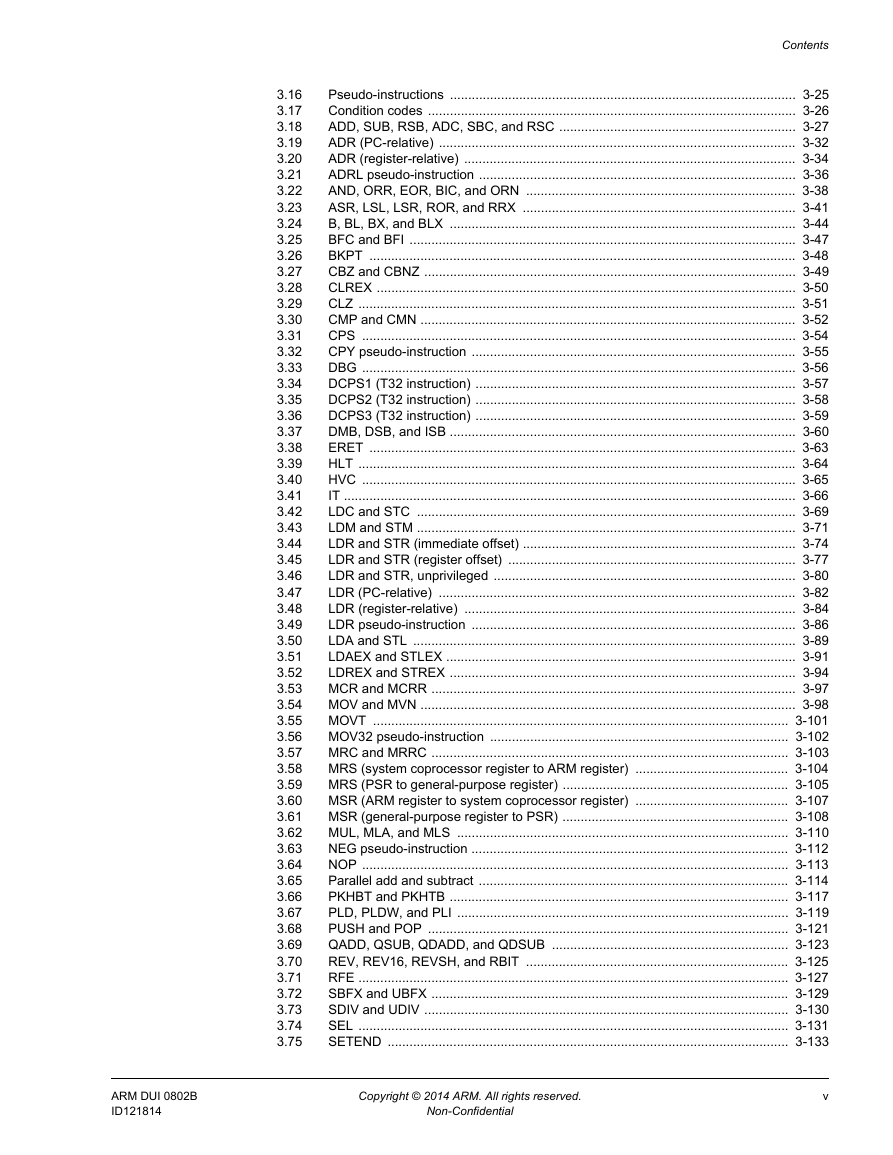

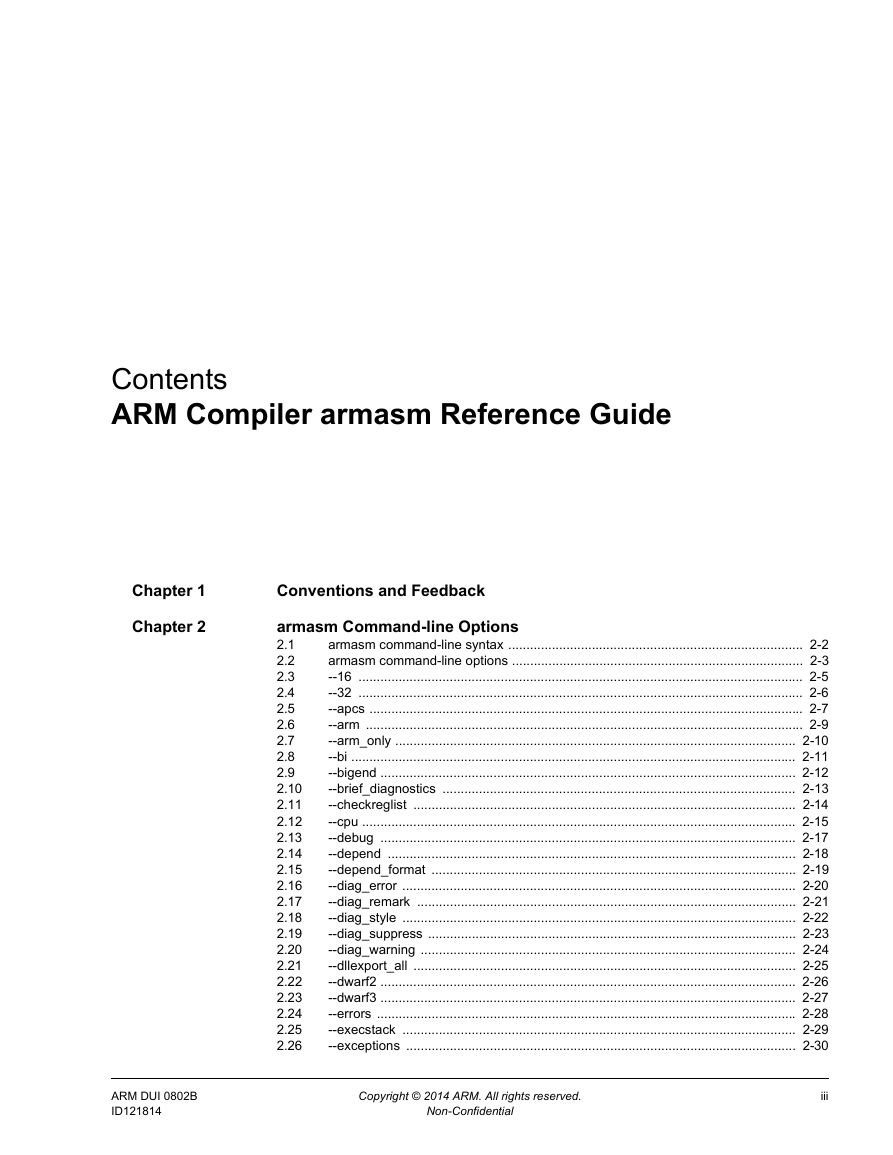

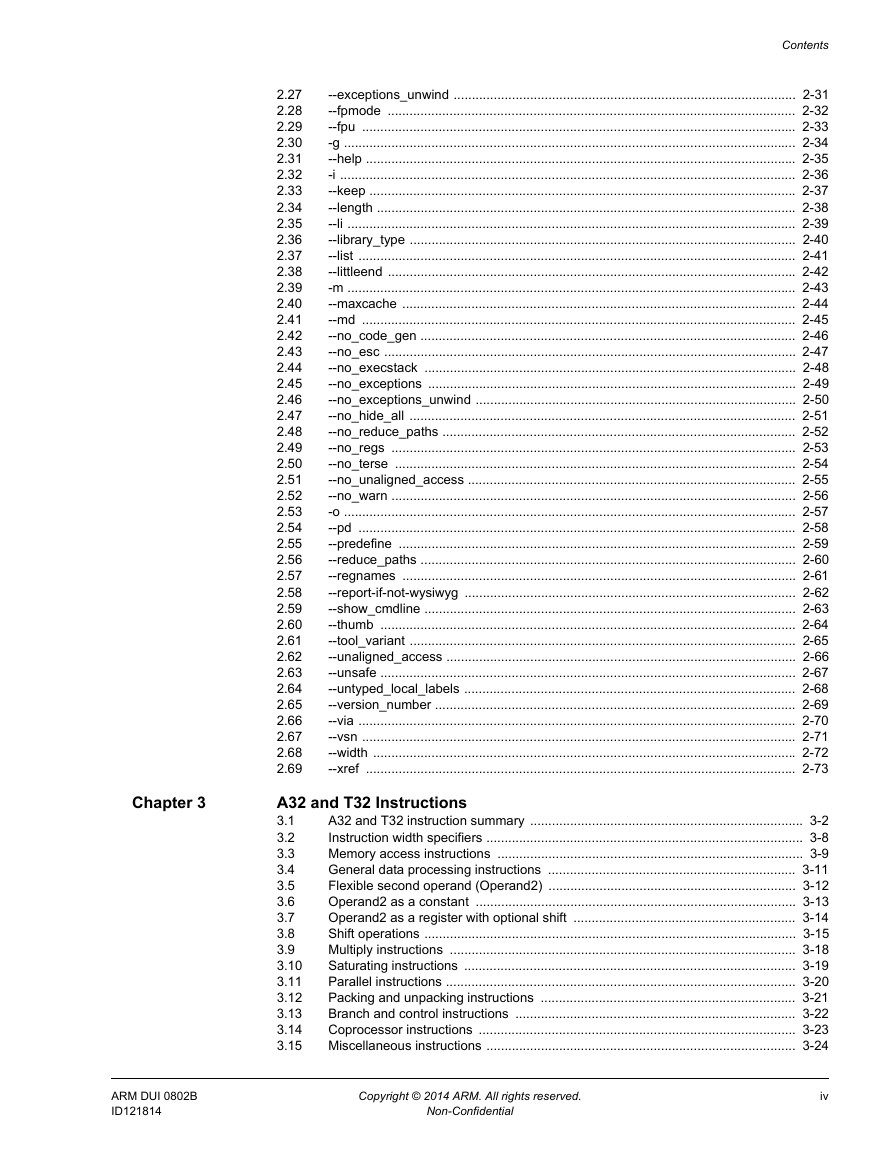

Contents

1: Conventions and Feedback

2: armasm Command-line Options

2.1 armasm command-line syntax

2.2 armasm command-line options

2.3 --16

2.3.1 See also

2.4 --32

2.4.1 See also

2.5 --apcs

2.5.1 Syntax

2.5.2 Example

2.5.3 See also

2.6 --arm

2.6.1 See also

2.7 --arm_only

2.7.1 See also

2.8 --bi

2.8.1 See also

2.9 --bigend

2.9.1 See also

2.10 --brief_diagnostics

2.10.1 See also

2.11 --checkreglist

2.11.1 See also

2.12 --cpu

2.12.1 Syntax

2.12.2 Usage

2.12.3 Examples

2.12.4 See also

2.13 --debug

2.13.1 See also

2.14 --depend

2.14.1 Syntax

2.14.2 See also

2.15 --depend_format

2.15.1 Syntax

2.15.2 See also

2.16 --diag_error

2.16.1 Syntax

2.16.2 Usage

2.16.3 See also

2.17 --diag_remark

2.17.1 Syntax

2.17.2 Usage

2.17.3 See also

2.18 --diag_style

2.18.1 Syntax

2.18.2 Usage

2.18.3 See also

2.19 --diag_suppress

2.19.1 Syntax

2.19.2 Examples

2.19.3 See also

2.20 --diag_warning

2.20.1 Syntax

2.20.2 See also

2.21 --dllexport_all

2.21.1 See also

2.22 --dwarf2

2.22.1 See also

2.23 --dwarf3

2.23.1 See also

2.24 --errors

2.24.1 Syntax

2.25 --execstack

2.25.1 See also

2.26 --exceptions

2.26.1 See also

2.27 --exceptions_unwind

2.27.1 See also

2.28 --fpmode

2.28.1 Syntax

2.28.2 Example

2.28.3 See also

2.29 --fpu

2.29.1 Syntax

2.29.2 Usage

2.29.3 See also

2.30 -g

2.30.1 See also

2.31 --help

2.31.1 See also

2.32 -i

2.32.1 Syntax

2.32.2 See also

2.33 --keep

2.33.1 See also

2.34 --length

2.34.1 Syntax

2.34.2 See also

2.35 --li

2.35.1 See also

2.36 --library_type

2.36.1 Syntax

2.36.2 See also

2.37 --list

2.37.1 Syntax

2.37.2 Usage

2.37.3 See also

2.38 --littleend

2.38.1 See also

2.39 -m

2.39.1 See also

2.40 --maxcache

2.40.1 Syntax

2.41 --md

2.41.1 See also

2.42 --no_code_gen

2.43 --no_esc

2.44 --no_execstack

2.44.1 See also

2.45 --no_exceptions

2.45.1 See also

2.46 --no_exceptions_unwind

2.46.1 See also

2.47 --no_hide_all

2.47.1 See also

2.48 --no_reduce_paths

2.48.1 See also

2.49 --no_regs

2.49.1 See also

2.50 --no_terse

2.50.1 See also

2.51 --no_unaligned_access

2.51.1 See also

2.52 --no_warn

2.52.1 See also

2.53 -o

2.53.1 Syntax

2.54 --pd

2.54.1 See also

2.55 --predefine

2.55.1 Syntax

2.55.2 Usage

2.55.3 See also

2.56 --reduce_paths

2.56.1 See also

2.57 --regnames

2.57.1 Syntax

2.57.2 See also

2.58 --report-if-not-wysiwyg

2.59 --show_cmdline

2.59.1 See also

2.60 --thumb

2.60.1 See also

2.61 --tool_variant

2.61.1 Syntax

2.61.2 Usage

2.62 --unaligned_access

2.62.1 See also

2.63 --unsafe

2.63.1 See also

2.64 --untyped_local_labels

2.64.1 Example

2.64.2 See also

2.65 --version_number

2.65.1 See also

2.66 --via

2.66.1 Syntax

2.66.2 See also

2.67 --vsn

2.67.1 See also

2.68 --width

2.68.1 Syntax

2.68.2 See also

2.69 --xref

2.69.1 See also

3: A32 and T32 Instructions

3.1 A32 and T32 instruction summary

3.2 Instruction width specifiers

3.3 Memory access instructions

3.3.1 See also

3.4 General data processing instructions

3.5 Flexible second operand (Operand2)

3.5.1 See also

3.6 Operand2 as a constant

3.6.1 Instruction substitution

3.6.2 See also

3.7 Operand2 as a register with optional shift

3.7.1 See also

3.8 Shift operations

3.8.1 ASR

3.8.2 LSR

3.8.3 LSL

3.8.4 ROR

3.8.5 RRX

3.8.6 See also

3.9 Multiply instructions

3.10 Saturating instructions

3.10.1 Saturating arithmetic

3.10.2 See also

3.11 Parallel instructions

3.11.1 See also

3.12 Packing and unpacking instructions

3.13 Branch and control instructions

3.14 Coprocessor instructions

3.14.1 See also

3.15 Miscellaneous instructions

3.16 Pseudo-instructions

3.17 Condition codes

3.17.1 See also

3.18 ADD, SUB, RSB, ADC, SBC, and RSC

3.18.1 Syntax

3.18.2 Usage

3.18.3 Use of PC and SP in T32 instructions

3.18.4 Use of PC and SP in A32 instructions

3.18.5 Condition flags

3.18.6 16-bit instructions

3.18.7 Examples

3.18.8 Incorrect example

3.18.9 Multiword arithmetic examples

3.18.10 See also

3.19 ADR (PC-relative)

3.19.1 Syntax

3.19.2 Usage

3.19.3 Offset range and architectures

3.19.4 ADR in T32

3.19.5 Restrictions

3.19.6 See also

3.20 ADR (register-relative)

3.20.1 Syntax

3.20.2 Usage

3.20.3 Restrictions

3.20.4 Offset range and architectures

3.20.5 ADR in T32

3.20.6 See also

3.21 ADRL pseudo-instruction

3.21.1 Syntax

3.21.2 Usage

3.21.3 Availability and range

3.21.4 See also

3.22 AND, ORR, EOR, BIC, and ORN

3.22.1 Syntax

3.22.2 Usage

3.22.3 Use of PC in T32 instructions

3.22.4 Use of PC and SP in A32 instructions

3.22.5 Condition flags

3.22.6 16-bit instructions

3.22.7 Examples

3.22.8 Incorrect example

3.22.9 See also

3.23 ASR, LSL, LSR, ROR, and RRX

3.23.1 Syntax

3.23.2 Usage

3.23.3 Restrictions in T32 code

3.23.4 Use of SP and PC in A32 ASR, LSL, LSR, ROR, and RRX instructions

3.23.5 Condition flags

3.23.6 16-bit instructions

3.23.7 Availability

3.23.8 Examples

3.23.9 See also

3.24 B, BL, BX, and BLX

3.24.1 Syntax

3.24.2 Operation

3.24.3 Instruction availability and branch ranges

3.24.4 Extending branch ranges

3.24.5 B in T32

3.24.6 Register restrictions

3.24.7 Condition flags

3.24.8 Availability

3.24.9 Examples

3.24.10 See also

3.25 BFC and BFI

3.25.1 Syntax

3.25.2 BFC

3.25.3 BFI

3.25.4 Register restrictions

3.25.5 Condition flags

3.25.6 Availability

3.25.7 See also

3.26 BKPT

3.26.1 Syntax

3.26.2 Usage

3.26.3 Availability

3.27 CBZ and CBNZ

3.27.1 Syntax

3.27.2 Usage

3.27.3 Restrictions

3.27.4 Condition flags

3.27.5 Availability

3.28 CLREX

3.28.1 Syntax

3.28.2 Usage

3.28.3 Availability

3.28.4 See also

3.29 CLZ

3.29.1 Syntax

3.29.2 Usage

3.29.3 Register restrictions

3.29.4 Condition flags

3.29.5 Availability

3.29.6 Examples

3.29.7 See also

3.30 CMP and CMN

3.30.1 Syntax

3.30.2 Usage

3.30.3 Use of PC in A32 and T32 instructions

3.30.4 Use of SP in A32 and T32 instructions

3.30.5 Condition flags

3.30.6 16-bit instructions

3.30.7 Examples

3.30.8 Incorrect example

3.30.9 See also

3.31 CPS

3.31.1 Syntax

3.31.2 Condition flags

3.31.3 16-bit instructions

3.31.4 Availability

3.31.5 Examples

3.32 CPY pseudo-instruction

3.32.1 Syntax

3.32.2 Usage

3.32.3 Availability

3.32.4 Register restrictions

3.32.5 Condition flags

3.32.6 See also

3.33 DBG

3.33.1 Syntax

3.33.2 Usage

3.33.3 Availability

3.33.4 See also

3.34 DCPS1 (T32 instruction)

3.34.1 Syntax

3.34.2 Usage

3.34.3 Availability

3.34.4 See also

3.35 DCPS2 (T32 instruction)

3.35.1 Syntax

3.35.2 Usage

3.35.3 Availability

3.35.4 See also

3.36 DCPS3 (T32 instruction)

3.36.1 Syntax

3.36.2 Usage

3.36.3 Availability

3.36.4 See also

3.37 DMB, DSB, and ISB

3.37.1 Syntax

3.37.2 DMB

3.37.3 DSB

3.37.4 ISB

3.37.5 Aliases

3.37.6 Availability

3.37.7 See also

3.38 ERET

3.38.1 Syntax

3.38.2 Usage

3.38.3 Operation

3.38.4 Notes

3.38.5 Availability

3.38.6 See also

3.39 HLT

3.39.1 Syntax

3.39.2 Usage

3.39.3 Availability

3.40 HVC

3.40.1 Syntax

3.40.2 Usage

3.40.3 Notes

3.40.4 Availability

3.40.5 See also

3.41 IT

3.41.1 Syntax

3.41.2 Deprecated syntax

3.41.3 Usage

3.41.4 Restrictions

3.41.5 Condition flags

3.41.6 Exceptions

3.41.7 Availability

3.41.8 Examples

3.41.9 Incorrect examples

3.42 LDC and STC

3.42.1 Syntax

3.42.2 Usage

3.42.3 Availability

3.42.4 Register restrictions

3.42.5 See also

3.43 LDM and STM

3.43.1 Syntax

3.43.2 Restrictions on reglist in 32-bit T32 instructions

3.43.3 Restrictions on reglist in A32 instructions

3.43.4 16-bit instructions

3.43.5 Loading to the PC

3.43.6 Loading or storing the base register, with writeback

3.43.7 Examples

3.43.8 Incorrect examples

3.43.9 See also

3.44 LDR and STR (immediate offset)

3.44.1 Syntax

3.44.2 Offset ranges and availability

3.44.3 Register restrictions

3.44.4 Doubleword register restrictions

3.44.5 Use of PC

3.44.6 Use of SP

3.44.7 Examples

3.44.8 See also

3.45 LDR and STR (register offset)

3.45.1 Syntax

3.45.2 Offset register and shift options

3.45.3 Register restrictions

3.45.4 Doubleword register restrictions

3.45.5 Use of PC

3.45.6 Use of SP

3.45.7 See also

3.46 LDR and STR, unprivileged

3.46.1 Syntax

3.46.2 Offset ranges and availability

3.46.3 See also

3.47 LDR (PC-relative)

3.47.1 Syntax

3.47.2 Offset ranges

3.47.3 LDR (PC-relative) in T32

3.47.4 Doubleword register restrictions

3.47.5 Use of SP

3.47.6 See also

3.48 LDR (register-relative)

3.48.1 Syntax

3.48.2 Offset ranges

3.48.3 LDR (register-relative) in T32

3.48.4 Doubleword register restrictions

3.48.5 Use of PC

3.48.6 Use of SP

3.48.7 See also

3.49 LDR pseudo-instruction

3.49.1 Syntax

3.49.2 Usage

3.49.3 LDR in T32 code

3.49.4 Examples

3.49.5 See also

3.50 LDA and STL

3.50.1 Syntax

3.50.2 Operation

3.50.3 Restrictions

3.50.4 Availability

3.50.5 See also

3.51 LDAEX and STLEX

3.51.1 Syntax

3.51.2 LDAEX

3.51.3 STLEX

3.51.4 Restrictions

3.51.5 Usage

3.51.6 Availability

3.51.7 See also

3.52 LDREX and STREX

3.52.1 Syntax

3.52.2 LDREX

3.52.3 STREX

3.52.4 Restrictions

3.52.5 Usage

3.52.6 Availability

3.52.7 Examples

3.52.8 See also

3.53 MCR and MCRR

3.53.1 Syntax

3.53.2 Usage

3.53.3 Availability

3.53.4 See also

3.54 MOV and MVN

3.54.1 Syntax

3.54.2 Usage

3.54.3 Use of PC and SP in 32-bit T32 instructions

3.54.4 Use of PC and SP in 16-bit T32 instructions

3.54.5 Use of PC and SP in A32 MOV and MVN

3.54.6 Condition flags

3.54.7 16-bit instructions

3.54.8 Availability

3.54.9 Example

3.54.10 Incorrect example

3.54.11 See also

3.55 MOVT

3.55.1 Syntax

3.55.2 Usage

3.55.3 Register restrictions

3.55.4 Condition flags

3.55.5 Availability

3.55.6 See also

3.56 MOV32 pseudo-instruction

3.56.1 Syntax

3.56.2 Usage

3.56.3 Availability

3.56.4 Examples

3.56.5 See also

3.57 MRC and MRRC

3.57.1 Syntax

3.57.2 Usage

3.57.3 Availability

3.57.4 See also

3.58 MRS (system coprocessor register to ARM register)

3.58.1 Syntax

3.58.2 Usage

3.58.3 Availability

3.58.4 See also

3.59 MRS (PSR to general-purpose register)

3.59.1 Syntax

3.59.2 Usage

3.59.3 SPSR

3.59.4 CPSR

3.59.5 Register restrictions

3.59.6 Condition flags

3.59.7 Availability

3.59.8 See also

3.60 MSR (ARM register to system coprocessor register)

3.60.1 Syntax

3.60.2 Usage

3.60.3 Availability

3.60.4 See also

3.61 MSR (general-purpose register to PSR)

3.61.1 Syntax

3.61.2 Usage

3.61.3 Register restrictions

3.61.4 Condition flags

3.61.5 Availability

3.61.6 See also

3.62 MUL, MLA, and MLS

3.62.1 Syntax

3.62.2 Usage

3.62.3 Register restrictions

3.62.4 Condition flags

3.62.5 16-bit instructions

3.62.6 Availability

3.62.7 Examples

3.62.8 See also

3.63 NEG pseudo-instruction

3.63.1 Syntax

3.63.2 Usage

3.63.3 Availability

3.63.4 Register restrictions

3.63.5 Condition flags

3.63.6 See also

3.64 NOP

3.64.1 Syntax

3.64.2 Usage

3.64.3 Availability

3.64.4 See also

3.65 Parallel add and subtract

3.65.1 Syntax

3.65.2 Operation

3.65.3 Register restrictions

3.65.4 GE flags

3.65.5 Availability

3.65.6 Examples

3.65.7 Incorrect examples

3.65.8 See also

3.66 PKHBT and PKHTB

3.66.1 Syntax

3.66.2 Register restrictions

3.66.3 Condition flags

3.66.4 Availability

3.66.5 Examples

3.66.6 Incorrect examples

3.66.7 See also

3.67 PLD, PLDW, and PLI

3.67.1 Syntax

3.67.2 Range of offset

3.67.3 Register or shifted register offset

3.67.4 Address alignment for preloads

3.67.5 Register restrictions

3.67.6 Availability

3.67.7 See also

3.68 PUSH and POP

3.68.1 Syntax

3.68.2 Usage

3.68.3 POP, with reglist including the PC

3.68.4 T32 instructions

3.68.5 Restrictions on reglist in A32 instructions

3.68.6 Examples

3.68.7 See also

3.69 QADD, QSUB, QDADD, and QDSUB

3.69.1 Syntax

3.69.2 Usage

3.69.3 Register restrictions

3.69.4 Q flag

3.69.5 Availability

3.69.6 Examples

3.69.7 See also

3.70 REV, REV16, REVSH, and RBIT

3.70.1 Syntax

3.70.2 Usage

3.70.3 Register restrictions

3.70.4 Condition flags

3.70.5 16-bit instructions

3.70.6 Availability

3.70.7 Examples

3.70.8 See also

3.71 RFE

3.71.1 Syntax

3.71.2 Usage

3.71.3 Operation

3.71.4 Notes

3.71.5 Availability

3.71.6 Example

3.71.7 See also

3.72 SBFX and UBFX

3.72.1 Syntax

3.72.2 Register restrictions

3.72.3 Condition flags

3.72.4 Availability

3.72.5 See also

3.73 SDIV and UDIV

3.73.1 Syntax

3.73.2 Register restrictions

3.73.3 Availability

3.73.4 See also

3.74 SEL

3.74.1 Syntax

3.74.2 Operation

3.74.3 Usage

3.74.4 Register restrictions

3.74.5 Condition flags

3.74.6 Availability

3.74.7 Examples

3.74.8 See also

3.75 SETEND

3.75.1 Syntax

3.75.2 Usage

3.75.3 Availability

3.75.4 Example

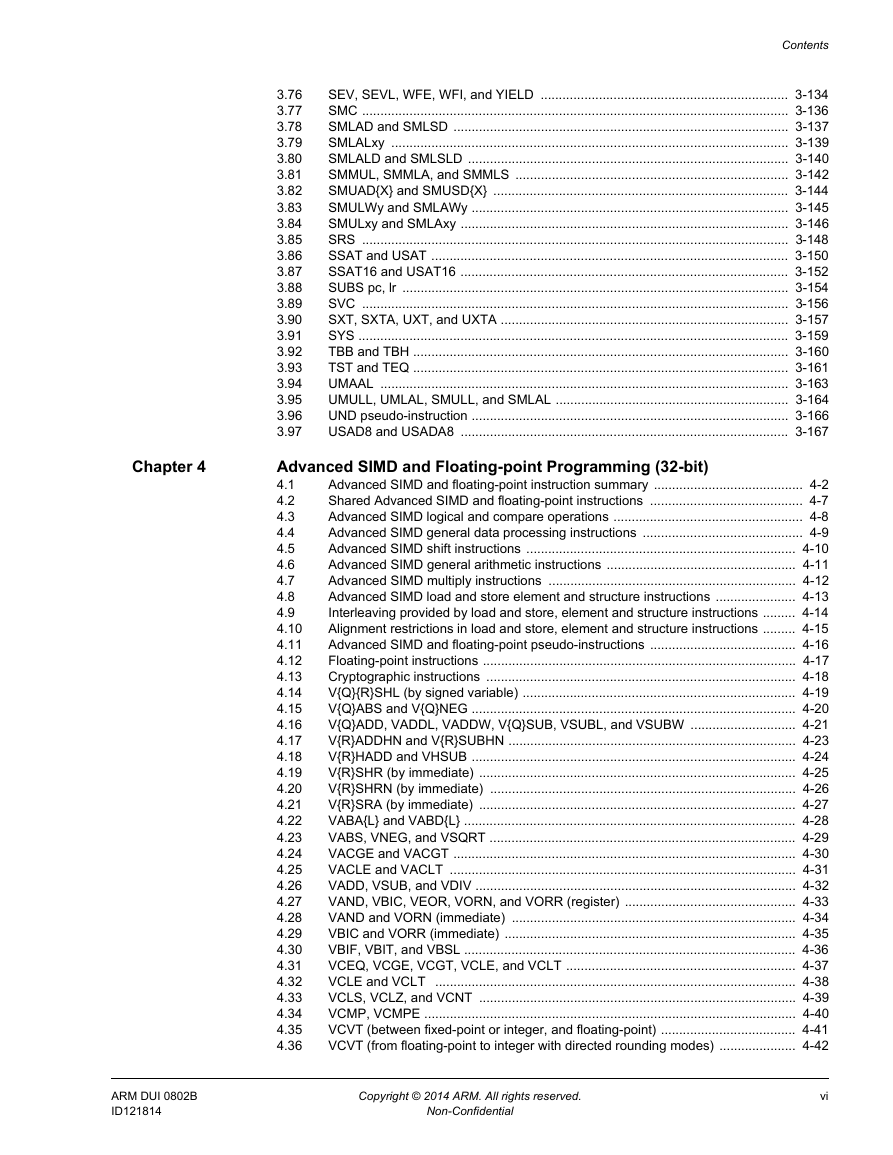

3.76 SEV, SEVL, WFE, WFI, and YIELD

3.76.1 Syntax

3.76.2 Usage

3.76.3 Availability

3.76.4 See also

3.77 SMC

3.77.1 Syntax

3.77.2 Note

3.77.3 Availability

3.77.4 See also

3.78 SMLAD and SMLSD

3.78.1 Syntax

3.78.2 Operation

3.78.3 Register restrictions

3.78.4 Condition flags

3.78.5 Availability

3.78.6 Examples

3.78.7 See also

3.79 SMLALxy

3.79.1 Syntax

3.79.2 Usage

3.79.3 Register restrictions

3.79.4 Condition flags

3.79.5 Availability

3.79.6 Examples

3.79.7 See also

3.80 SMLALD and SMLSLD

3.80.1 Syntax

3.80.2 Operation

3.80.3 Register restrictions

3.80.4 Condition flags

3.80.5 Availability

3.80.6 Examples

3.80.7 See also

3.81 SMMUL, SMMLA, and SMMLS

3.81.1 Syntax

3.81.2 Operation

3.81.3 Register restrictions

3.81.4 Condition flags

3.81.5 Availability

3.81.6 Examples

3.81.7 See also

3.82 SMUAD{X} and SMUSD{X}

3.82.1 Syntax

3.82.2 Usage

3.82.3 Register restrictions

3.82.4 Q flag

3.82.5 Availability

3.82.6 Examples

3.82.7 See also

3.83 SMULWy and SMLAWy

3.83.1 Syntax

3.83.2 Usage

3.83.3 Register restrictions

3.83.4 Condition flags

3.83.5 Availability

3.83.6 See also

3.84 SMULxy and SMLAxy

3.84.1 Syntax

3.84.2 Usage

3.84.3 Register restrictions

3.84.4 Condition flags

3.84.5 Availability

3.84.6 Examples

3.84.7 See also

3.85 SRS

3.85.1 Syntax

3.85.2 Operation

3.85.3 Usage

3.85.4 Notes

3.85.5 Availability

3.85.6 Example

3.85.7 See also

3.86 SSAT and USAT

3.86.1 Syntax

3.86.2 Operation

3.86.3 Register restrictions

3.86.4 Q flag

3.86.5 Availability

3.86.6 Examples

3.86.7 See also

3.87 SSAT16 and USAT16

3.87.1 Syntax

3.87.2 Operation

3.87.3 Register restrictions

3.87.4 Q flag

3.87.5 Availability

3.87.6 Examples

3.87.7 Incorrect examples

3.87.8 See also

3.88 SUBS pc, lr

3.88.1 Syntax

3.88.2 Usage

3.88.3 Notes

3.88.4 Availability

3.88.5 See also

3.89 SVC

3.89.1 Syntax

3.89.2 Usage

3.89.3 Condition flags

3.89.4 Availability

3.89.5 See also

3.90 SXT, SXTA, UXT, and UXTA

3.90.1 Syntax

3.90.2 Operation

3.90.3 Register restrictions

3.90.4 Condition flags

3.90.5 16-bit instructions

3.90.6 Availability

3.90.7 Examples

3.90.8 Incorrect examples

3.90.9 See also

3.91 SYS

3.91.1 Syntax

3.91.2 Usage

3.91.3 Availability

3.91.4 See also

3.92 TBB and TBH

3.92.1 Syntax

3.92.2 Operation

3.92.3 Availability

3.93 TST and TEQ

3.93.1 Syntax

3.93.2 Usage

3.93.3 Register restrictions

3.93.4 Condition flags

3.93.5 Availability

3.93.6 Examples

3.93.7 Incorrect example

3.93.8 See also

3.94 UMAAL

3.94.1 Syntax

3.94.2 Operation

3.94.3 Register restrictions

3.94.4 Condition flags

3.94.5 Availability

3.94.6 Examples

3.94.7 See also

3.95 UMULL, UMLAL, SMULL, and SMLAL

3.95.1 Syntax

3.95.2 Usage

3.95.3 Register restrictions

3.95.4 Condition flags

3.95.5 Availability

3.95.6 Examples

3.95.7 See also

3.96 UND pseudo-instruction

3.96.1 Syntax

3.96.2 UND in T32 code

3.96.3 Disassembly

3.96.4 See also

3.97 USAD8 and USADA8

3.97.1 Syntax

3.97.2 Operation

3.97.3 Register restrictions

3.97.4 Condition flags

3.97.5 Availability

3.97.6 Examples

3.97.7 Incorrect examples

3.97.8 See also

4: Advanced SIMD and Floating-point Programming (32-bit)

4.1 Advanced SIMD and floating-point instruction summary

4.1.1 Summary of advanced SIMD instructions

4.1.2 Summary of shared Advanced SIMD and floating-point instructions

4.1.3 Summary of floating-point instructions

4.2 Shared Advanced SIMD and floating-point instructions

4.3 Advanced SIMD logical and compare operations

4.4 Advanced SIMD general data processing instructions

4.5 Advanced SIMD shift instructions

4.6 Advanced SIMD general arithmetic instructions

4.7 Advanced SIMD multiply instructions

4.8 Advanced SIMD load and store element and structure instructions

4.9 Interleaving provided by load and store, element and structure instructions

4.9.1 See also

4.10 Alignment restrictions in load and store, element and structure instructions

4.10.1 See also

4.11 Advanced SIMD and floating-point pseudo-instructions

4.12 Floating-point instructions

4.13 Cryptographic instructions

4.13.1 See also

4.14 V{Q}{R}SHL (by signed variable)

4.14.1 Syntax

4.14.2 See also

4.15 V{Q}ABS and V{Q}NEG

4.15.1 Syntax

4.15.2 See also

4.16 V{Q}ADD, VADDL, VADDW, V{Q}SUB, VSUBL, and VSUBW

4.16.1 Syntax

4.16.2 See also

4.17 V{R}ADDHN and V{R}SUBHN

4.17.1 Syntax

4.17.2 See also

4.18 V{R}HADD and VHSUB

4.18.1 Syntax

4.18.2 See also

4.19 V{R}SHR (by immediate)

4.19.1 Syntax

4.19.2 See also

4.20 V{R}SHRN (by immediate)

4.20.1 Syntax

4.20.2 See also

4.21 V{R}SRA (by immediate)

4.21.1 Syntax

4.21.2 See also

4.22 VABA{L} and VABD{L}

4.22.1 Syntax

4.22.2 See also

4.23 VABS, VNEG, and VSQRT

4.23.1 Syntax

4.23.2 Usage

4.23.3 Floating-point exceptions

4.23.4 See also

4.24 VACGE and VACGT

4.24.1 Syntax

4.24.2 See also

4.25 VACLE and VACLT

4.25.1 Syntax

4.25.2 See also

4.26 VADD, VSUB, and VDIV

4.26.1 Syntax

4.26.2 Usage

4.26.3 Floating-point exceptions

4.26.4 See also

4.27 VAND, VBIC, VEOR, VORN, and VORR (register)

4.27.1 Syntax

4.27.2 See also

4.28 VAND and VORN (immediate)

4.28.1 Syntax

4.28.2 Immediate values

4.28.3 See also

4.29 VBIC and VORR (immediate)

4.29.1 Syntax

4.29.2 Immediate values

4.29.3 See also

4.30 VBIF, VBIT, and VBSL

4.30.1 Syntax

4.30.2 See also

4.31 VCEQ, VCGE, VCGT, VCLE, and VCLT

4.31.1 Syntax

4.31.2 See also

4.32 VCLE and VCLT

4.32.1 Syntax

4.32.2 See also

4.33 VCLS, VCLZ, and VCNT

4.33.1 Syntax

4.33.2 See also

4.34 VCMP, VCMPE

4.34.1 Syntax

4.34.2 Usage

4.34.3 Floating-point exceptions

4.34.4 See also

4.35 VCVT (between fixed-point or integer, and floating-point)

4.35.1 Syntax

4.35.2 Rounding

4.35.3 See also

4.36 VCVT (from floating-point to integer with directed rounding modes)

4.36.1 Syntax

4.36.2 Notes

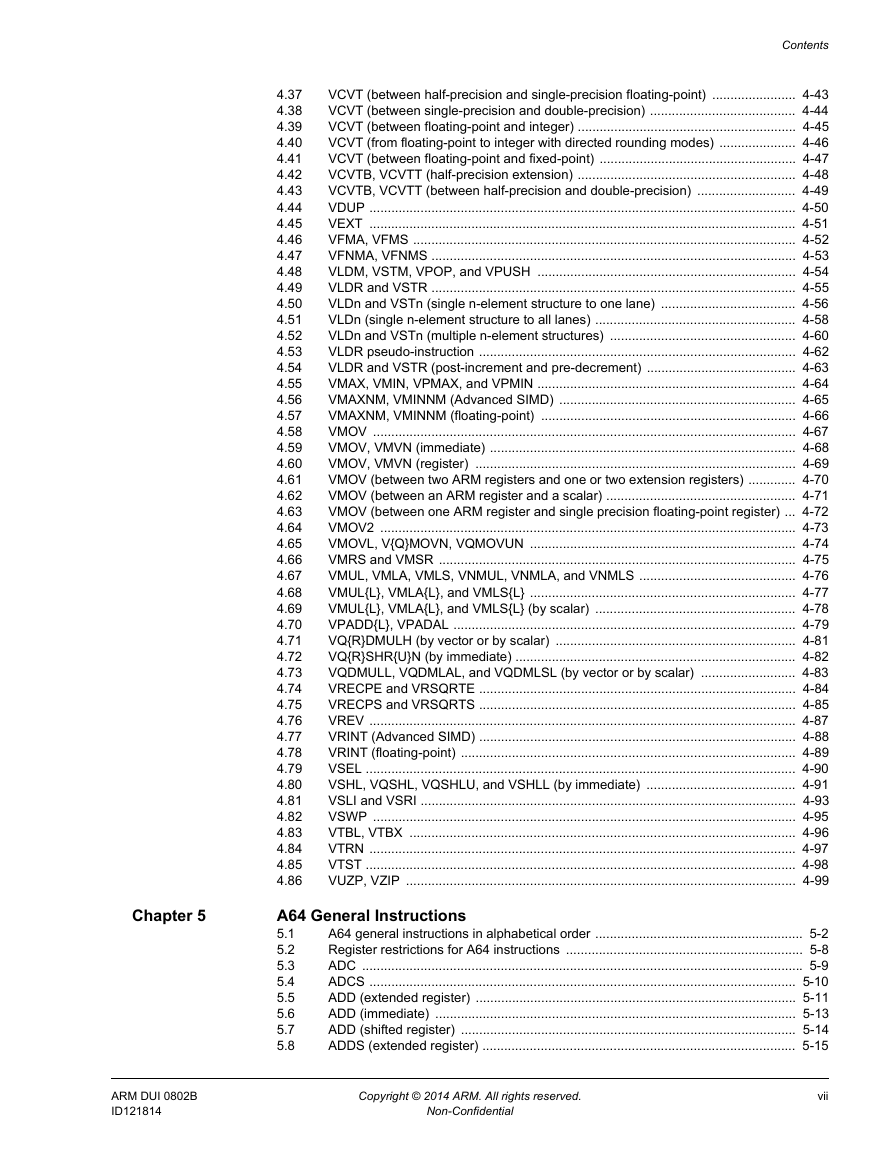

4.37 VCVT (between half-precision and single-precision floating-point)

4.37.1 Syntax

4.37.2 See also

4.38 VCVT (between single-precision and double-precision)

4.38.1 Syntax

4.38.2 Usage

4.38.3 Floating-point exceptions

4.38.4 See also

4.39 VCVT (between floating-point and integer)

4.39.1 Syntax

4.39.2 Usage

4.39.3 Floating-point exceptions

4.39.4 See also

4.40 VCVT (from floating-point to integer with directed rounding modes)

4.40.1 Syntax

4.40.2 Notes

4.40.3 Floating-point exceptions

4.41 VCVT (between floating-point and fixed-point)

4.41.1 Syntax

4.41.2 Usage

4.41.3 Floating-point exceptions

4.41.4 See also

4.42 VCVTB, VCVTT (half-precision extension)

4.42.1 Syntax

4.42.2 Floating-point exceptions

4.42.3 See also

4.43 VCVTB, VCVTT (between half-precision and double-precision)

4.43.1 Syntax

4.43.2 Usage

4.43.3 Floating-point exceptions

4.43.4 See also

4.44 VDUP

4.44.1 Syntax

4.44.2 See also

4.45 VEXT

4.45.1 Syntax

4.45.2 VEXT pseudo-instruction

4.45.3 See also

4.46 VFMA, VFMS

4.46.1 Syntax

4.46.2 See also

4.47 VFNMA, VFNMS

4.47.1 Syntax

4.47.2 Usage

4.47.3 Floating-point exceptions

4.47.4 See also

4.48 VLDM, VSTM, VPOP, and VPUSH

4.48.1 Syntax

4.48.2 See also

4.49 VLDR and VSTR

4.49.1 Syntax

4.49.2 Usage

4.49.3 See also

4.50 VLDn and VSTn (single n-element structure to one lane)

4.50.1 Syntax

4.50.2 See also

4.51 VLDn (single n-element structure to all lanes)

4.51.1 Syntax

4.51.2 See also

4.52 VLDn and VSTn (multiple n-element structures)

4.52.1 Syntax

4.52.2 See also

4.53 VLDR pseudo-instruction

4.53.1 Syntax

4.53.2 Usage

4.53.3 See also

4.54 VLDR and VSTR (post-increment and pre-decrement)

4.54.1 Syntax

4.54.2 Usage

4.54.3 See also

4.55 VMAX, VMIN, VPMAX, and VPMIN

4.55.1 Syntax

4.55.2 Floating-point maximum and minimum

4.55.3 See also

4.56 VMAXNM, VMINNM (Advanced SIMD)

4.56.1 Syntax

4.56.2 Notes

4.57 VMAXNM, VMINNM (floating-point)

4.57.1 Syntax

4.57.2 Notes

4.57.3 Floating-point exceptions

4.58 VMOV

4.58.1 Syntax

4.58.2 Immediate values

4.58.3 See also

4.59 VMOV, VMVN (immediate)

4.59.1 Syntax

4.59.2 See also

4.60 VMOV, VMVN (register)

4.60.1 Syntax

4.60.2 See also

4.61 VMOV (between two ARM registers and one or two extension registers)

4.61.1 Syntax

4.61.2 Usage

4.61.3 See also

4.62 VMOV (between an ARM register and a scalar)

4.62.1 Syntax

4.62.2 Usage

4.62.3 See also

4.63 VMOV (between one ARM register and single precision floating-point register)

4.63.1 Syntax

4.63.2 Usage

4.63.3 See also

4.64 VMOV2

4.64.1 Syntax

4.64.2 Usage

4.64.3 See also

4.65 VMOVL, V{Q}MOVN, VQMOVUN

4.65.1 Syntax

4.65.2 See also

4.66 VMRS and VMSR

4.66.1 Syntax

4.66.2 Usage

4.66.3 Examples

4.66.4 See also

4.67 VMUL, VMLA, VMLS, VNMUL, VNMLA, and VNMLS

4.67.1 Syntax

4.67.2 Usage

4.67.3 Floating-point exceptions

4.67.4 See also

4.68 VMUL{L}, VMLA{L}, and VMLS{L}

4.68.1 Syntax

4.68.2 See also

4.69 VMUL{L}, VMLA{L}, and VMLS{L} (by scalar)

4.69.1 Syntax

4.69.2 See also

4.70 VPADD{L}, VPADAL

4.70.1 Syntax

4.70.2 See also

4.71 VQ{R}DMULH (by vector or by scalar)

4.71.1 Syntax

4.71.2 See also

4.72 VQ{R}SHR{U}N (by immediate)

4.72.1 Syntax

4.72.2 See also

4.73 VQDMULL, VQDMLAL, and VQDMLSL (by vector or by scalar)

4.73.1 Syntax

4.73.2 See also

4.74 VRECPE and VRSQRTE

4.74.1 Syntax

4.74.2 Results for out-of-range inputs

4.74.3 See also

4.75 VRECPS and VRSQRTS

4.75.1 Syntax

4.75.2 Results for out-of-range inputs

4.75.3 Usage

4.75.4 See also

4.76 VREV

4.76.1 Syntax

4.76.2 See also

4.77 VRINT (Advanced SIMD)

4.77.1 Syntax

4.77.2 Notes

4.78 VRINT (floating-point)

4.78.1 Syntax

4.78.2 Notes

4.78.3 Floating-point exceptions

4.78.4 See also

4.79 VSEL

4.79.1 Syntax

4.79.2 Usage

4.79.3 Floating-point exceptions

4.79.4 See also

4.80 VSHL, VQSHL, VQSHLU, and VSHLL (by immediate)

4.80.1 Syntax

4.80.2 See also

4.81 VSLI and VSRI

4.81.1 Syntax

4.81.2 See also

4.82 VSWP

4.82.1 Syntax

4.82.2 See also

4.83 VTBL, VTBX

4.83.1 Syntax

4.83.2 See also

4.84 VTRN

4.84.1 Syntax

4.84.2 See also

4.85 VTST

4.85.1 Syntax

4.85.2 See also

4.86 VUZP, VZIP

4.86.1 Syntax

4.86.2 See also

5: A64 General Instructions

5.1 A64 general instructions in alphabetical order

5.2 Register restrictions for A64 instructions

5.2.1 See also

5.3 ADC

5.3.1 Syntax

5.3.2 See also

5.4 ADCS

5.4.1 Syntax

5.4.2 See also

5.5 ADD (extended register)

5.5.1 Syntax

5.5.2 Usage

5.5.3 See also

5.6 ADD (immediate)

5.6.1 Syntax

5.6.2 See also

5.7 ADD (shifted register)

5.7.1 Syntax

5.7.2 See also

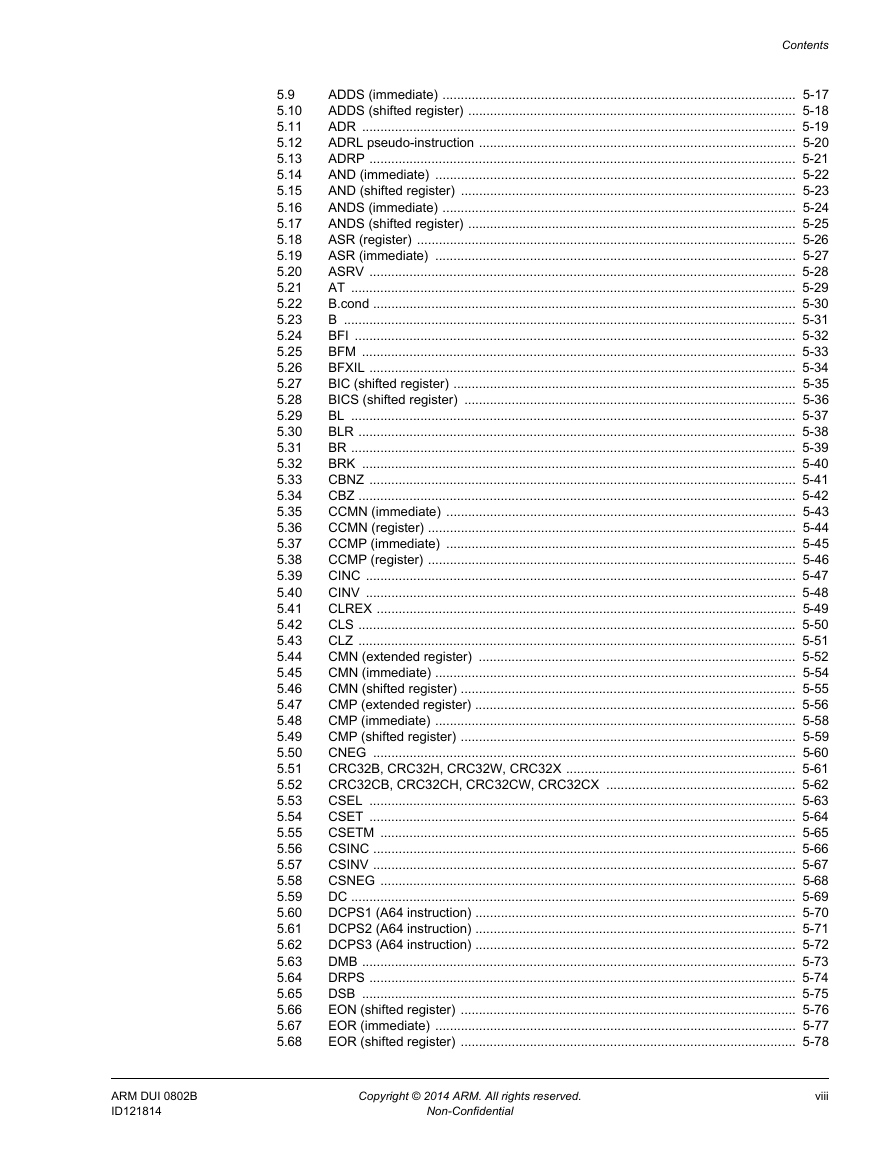

5.8 ADDS (extended register)

5.8.1 Syntax

5.8.2 Usage

5.8.3 See also

5.9 ADDS (immediate)

5.9.1 Syntax

5.9.2 See also

5.10 ADDS (shifted register)

5.10.1 Syntax

5.10.2 See also

5.11 ADR

5.11.1 Syntax

5.11.2 See also

5.12 ADRL pseudo-instruction

5.12.1 Syntax

5.12.2 Usage

5.12.3 Example

5.12.4 See also

5.13 ADRP

5.13.1 Syntax

5.13.2 See also

5.14 AND (immediate)

5.14.1 Syntax

5.14.2 See also

5.15 AND (shifted register)

5.15.1 Syntax

5.15.2 See also

5.16 ANDS (immediate)

5.16.1 Syntax

5.16.2 See also

5.17 ANDS (shifted register)

5.17.1 Syntax

5.17.2 See also

5.18 ASR (register)

5.18.1 Syntax

5.18.2 See also

5.19 ASR (immediate)

5.19.1 Syntax

5.19.2 See also

5.20 ASRV

5.20.1 Syntax

5.20.2 See also

5.21 AT

5.21.1 Syntax

5.21.2 See also

5.22 B.cond

5.22.1 Syntax

5.22.2 See also

5.23 B

5.23.1 Syntax

5.23.2 See also

5.24 BFI

5.24.1 Syntax

5.24.2 See also

5.25 BFM

5.25.1 Syntax

5.25.2 See also

5.26 BFXIL

5.26.1 Syntax

5.26.2 See also

5.27 BIC (shifted register)

5.27.1 Syntax

5.27.2 See also

5.28 BICS (shifted register)

5.28.1 Syntax

5.28.2 See also

5.29 BL

5.29.1 Syntax

5.29.2 See also

5.30 BLR

5.30.1 Syntax

5.30.2 See also

5.31 BR

5.31.1 Syntax

5.31.2 See also

5.32 BRK

5.32.1 Syntax

5.32.2 See also

5.33 CBNZ

5.33.1 Syntax

5.33.2 See also

5.34 CBZ

5.34.1 Syntax

5.34.2 See also

5.35 CCMN (immediate)

5.35.1 Syntax

5.35.2 See also

5.36 CCMN (register)

5.36.1 Syntax

5.36.2 See also

5.37 CCMP (immediate)

5.37.1 Syntax

5.37.2 See also

5.38 CCMP (register)

5.38.1 Syntax

5.38.2 See also

5.39 CINC

5.39.1 Syntax

5.39.2 See also

5.40 CINV

5.40.1 Syntax

5.40.2 See also

5.41 CLREX

5.41.1 Syntax

5.41.2 See also

5.42 CLS

5.42.1 Syntax

5.42.2 See also

5.43 CLZ

5.43.1 Syntax

5.43.2 See also

5.44 CMN (extended register)

5.44.1 Syntax

5.44.2 Usage

5.44.3 See also

5.45 CMN (immediate)

5.45.1 Syntax

5.45.2 See also

5.46 CMN (shifted register)

5.46.1 Syntax

5.46.2 See also

5.47 CMP (extended register)

5.47.1 Syntax

5.47.2 Usage

5.47.3 See also

5.48 CMP (immediate)

5.48.1 Syntax

5.48.2 See also

5.49 CMP (shifted register)

5.49.1 Syntax

5.49.2 See also

5.50 CNEG

5.50.1 Syntax

5.50.2 See also

5.51 CRC32B, CRC32H, CRC32W, CRC32X

5.51.1 Syntax

5.51.2 See also

5.52 CRC32CB, CRC32CH, CRC32CW, CRC32CX

5.52.1 Syntax

5.52.2 See also

5.53 CSEL

5.53.1 Syntax

5.53.2 See also

5.54 CSET

5.54.1 Syntax

5.54.2 See also

5.55 CSETM

5.55.1 Syntax

5.55.2 See also

5.56 CSINC

5.56.1 Syntax

5.56.2 See also

5.57 CSINV

5.57.1 Syntax

5.57.2 See also

5.58 CSNEG

5.58.1 Syntax

5.58.2 See also

5.59 DC

5.59.1 Syntax

5.59.2 See also

5.60 DCPS1 (A64 instruction)

5.60.1 Syntax

5.60.2 See also

5.61 DCPS2 (A64 instruction)

5.61.1 Syntax

5.61.2 See also

5.62 DCPS3 (A64 instruction)

5.62.1 Syntax

5.62.2 See also

5.63 DMB

5.63.1 Syntax

5.63.2 See also

5.64 DRPS

5.64.1 Syntax

5.64.2 See also

5.65 DSB

5.65.1 Syntax

5.65.2 See also

5.66 EON (shifted register)

5.66.1 Syntax

5.66.2 See also

5.67 EOR (immediate)

5.67.1 Syntax

5.67.2 See also

5.68 EOR (shifted register)

5.68.1 Syntax

5.68.2 See also

5.69 ERET

5.69.1 Syntax

5.69.2 See also

5.70 EXTR

5.70.1 Syntax

5.70.2 See also

5.71 HINT

5.71.1 Syntax

5.71.2 See also

5.72 HLT

5.72.1 Syntax

5.72.2 See also

5.73 HVC

5.73.1 Syntax

5.73.2 See also

5.74 IC

5.74.1 Syntax

5.74.2 See also

5.75 ISB

5.75.1 Syntax

5.75.2 See also

5.76 LSL (register)

5.76.1 Syntax

5.76.2 See also

5.77 LSL (immediate)

5.77.1 Syntax

5.77.2 See also

5.78 LSLV

5.78.1 Syntax

5.78.2 See also

5.79 LSR (register)

5.79.1 Syntax

5.79.2 See also

5.80 LSR (immediate)

5.80.1 Syntax

5.80.2 See also

5.81 LSRV

5.81.1 Syntax

5.81.2 See also

5.82 MADD

5.82.1 Syntax

5.82.2 See also

5.83 MNEG

5.83.1 Syntax

5.83.2 See also

5.84 MOV (to or from SP)

5.84.1 Syntax

5.84.2 See also

5.85 MOV (inverted wide immediate)

5.85.1 Syntax

5.85.2 See also

5.86 MOV (wide immediate)

5.86.1 Syntax

5.86.2 See also

5.87 MOV (bitmask immediate)

5.87.1 Syntax

5.87.2 See also

5.88 MOV (register)

5.88.1 Syntax

5.88.2 See also

5.89 MOVK

5.89.1 Syntax

5.89.2 See also

5.90 MOVL pseudo-instruction

5.90.1 Syntax

5.90.2 Usage

5.90.3 Examples

5.90.4 See also

5.91 MOVN

5.91.1 Syntax

5.91.2 See also

5.92 MOVZ

5.92.1 Syntax

5.92.2 See also

5.93 MRS

5.93.1 Syntax

5.93.2 See also

5.94 MSR (immediate)

5.94.1 Syntax

5.94.2 See also

5.95 MSR (register)

5.95.1 Syntax

5.95.2 See also

5.96 MSUB

5.96.1 Syntax

5.96.2 See also

5.97 MUL

5.97.1 Syntax

5.97.2 See also

5.98 MVN

5.98.1 Syntax

5.98.2 See also

5.99 NEG (shifted register)

5.99.1 Syntax

5.99.2 See also

5.100 NEGS

5.100.1 Syntax

5.100.2 See also

5.101 NGC

5.101.1 Syntax

5.101.2 See also

5.102 NGCS

5.102.1 Syntax

5.102.2 See also

5.103 NOP

5.103.1 See also

5.104 ORN (shifted register)

5.104.1 Syntax

5.104.2 See also

5.105 ORR (immediate)

5.105.1 Syntax

5.105.2 See also

5.106 ORR (shifted register)

5.106.1 Syntax

5.106.2 See also

5.107 RBIT

5.107.1 Syntax

5.107.2 See also

5.108 RET

5.108.1 Syntax

5.108.2 See also

5.109 REV

5.109.1 Syntax

5.109.2 See also

5.110 REV16

5.110.1 Syntax

5.110.2 See also

5.111 REV32

5.111.1 Syntax

5.111.2 See also

5.112 ROR (immediate)

5.112.1 Syntax

5.112.2 See also

5.113 ROR (register)

5.113.1 Syntax

5.113.2 See also

5.114 RORV

5.114.1 Syntax

5.114.2 See also

5.115 SBC

5.115.1 Syntax

5.115.2 See also

5.116 SBCS

5.116.1 Syntax

5.116.2 See also

5.117 SBFIZ

5.117.1 Syntax

5.117.2 See also

5.118 SBFM

5.118.1 Syntax

5.118.2 See also

5.119 SBFX

5.119.1 Syntax

5.119.2 See also

5.120 SDIV

5.120.1 Syntax

5.120.2 See also

5.121 SEV

5.121.1 See also

5.122 SEVL

5.122.1 See also

5.123 SMADDL

5.123.1 Syntax

5.123.2 See also

5.124 SMC

5.124.1 Syntax

5.124.2 See also

5.125 SMNEGL

5.125.1 Syntax

5.125.2 See also

5.126 SMSUBL

5.126.1 Syntax

5.126.2 See also

5.127 SMULH

5.127.1 Syntax

5.127.2 See also

5.128 SMULL

5.128.1 Syntax

5.128.2 See also

5.129 SUB (extended register)

5.129.1 Syntax

5.129.2 Usage

5.129.3 See also

5.130 SUB (immediate)

5.130.1 Syntax

5.130.2 See also

5.131 SUB (shifted register)

5.131.1 Syntax

5.131.2 See also

5.132 SUBS (extended register)

5.132.1 Syntax

5.132.2 Usage

5.132.3 See also

5.133 SUBS (immediate)

5.133.1 Syntax

5.133.2 See also

5.134 SUBS (shifted register)

5.134.1 Syntax

5.134.2 See also

5.135 SVC

5.135.1 Syntax

5.135.2 See also

5.136 SXTB

5.136.1 Syntax

5.136.2 See also

5.137 SXTH

5.137.1 Syntax

5.137.2 See also

5.138 SXTW

5.138.1 Syntax

5.138.2 See also

5.139 SYS

5.139.1 Syntax

5.139.2 See also

5.140 SYSL

5.140.1 Syntax

5.140.2 See also

5.141 TBNZ

5.141.1 Syntax

5.141.2 See also

5.142 TBZ

5.142.1 Syntax

5.142.2 See also

5.143 TLBI

5.143.1 Syntax

5.143.2 See also

5.144 TST (immediate)

5.144.1 Syntax

5.144.2 See also

5.145 TST (shifted register)

5.145.1 Syntax

5.145.2 See also

5.146 UBFIZ

5.146.1 Syntax

5.146.2 See also

5.147 UBFM

5.147.1 Syntax

5.147.2 See also

5.148 UBFX

5.148.1 Syntax

5.148.2 See also

5.149 UDIV

5.149.1 Syntax

5.149.2 See also

5.150 UMADDL

5.150.1 Syntax

5.150.2 See also

5.151 UMNEGL

5.151.1 Syntax

5.151.2 See also

5.152 UMSUBL

5.152.1 Syntax

5.152.2 See also

5.153 UMULH

5.153.1 Syntax

5.153.2 See also

5.154 UMULL

5.154.1 Syntax

5.154.2 See also

5.155 UXTB

5.155.1 Syntax

5.155.2 See also

5.156 UXTH

5.156.1 Syntax

5.156.2 See also

5.157 WFE

5.157.1 See also

5.158 WFI

5.158.1 See also

5.159 YIELD

5.159.1 See also

6: A64 Data Transfer Instructions

6.1 A64 data transfer instructions in alphabetical order

6.2 Register restrictions for A64 instructions

6.2.1 See also

6.3 LDAR

6.3.1 Syntax

6.3.2 See also

6.4 LDARB

6.4.1 Syntax

6.4.2 See also

6.5 LDARH

6.5.1 Syntax

6.5.2 See also

6.6 LDAXP

6.6.1 Syntax

6.6.2 See also

6.7 LDAXR

6.7.1 Syntax

6.7.2 See also

6.8 LDAXRB

6.8.1 Syntax

6.8.2 See also

6.9 LDAXRH

6.9.1 Syntax

6.9.2 See also

6.10 LDNP (SIMD and FP)

6.10.1 Syntax

6.10.2 See also

6.11 LDNP

6.11.1 Syntax

6.11.2 See also

6.12 LDP (SIMD and FP)

6.12.1 Syntax

6.12.2 See also

6.13 LDP

6.13.1 Syntax

6.13.2 See also

6.14 LDPSW

6.14.1 Syntax

6.14.2 See also

6.15 LDR (immediate, SIMD and FP)

6.15.1 Syntax

6.15.2 See also

6.16 LDR (immediate)

6.16.1 Syntax

6.16.2 See also

6.17 LDR (literal, SIMD and FP)

6.17.1 Syntax

6.17.2 See also

6.18 LDR (literal)

6.18.1 Syntax

6.18.2 See also

6.19 LDR pseudo-instruction

6.19.1 Syntax

6.19.2 Usage

6.19.3 Examples

6.19.4 See also

6.20 LDR (register, SIMD and FP)

6.20.1 Syntax

6.20.2 Usage

6.20.3 See also

6.21 LDR (register)

6.21.1 Syntax

6.21.2 Usage

6.21.3 See also

6.22 LDRB (immediate)

6.22.1 Syntax

6.22.2 See also

6.23 LDRB (register)

6.23.1 Syntax

6.23.2 Usage

6.23.3 See also

6.24 LDRH (immediate)

6.24.1 Syntax

6.24.2 See also

6.25 LDRH (register)

6.25.1 Syntax

6.25.2 Usage

6.25.3 See also

6.26 LDRSB (immediate)

6.26.1 Syntax

6.26.2 See also

6.27 LDRSB (register)

6.27.1 Syntax

6.27.2 Usage

6.27.3 See also

6.28 LDRSH (immediate)

6.28.1 Syntax

6.28.2 See also

6.29 LDRSH (register)

6.29.1 Syntax

6.29.2 Usage

6.29.3 See also

6.30 LDRSW (immediate)

6.30.1 Syntax

6.30.2 See also

6.31 LDRSW (literal)

6.31.1 Syntax

6.31.2 See also

6.32 LDRSW (register)

6.32.1 Syntax

6.32.2 Usage

6.32.3 See also

6.33 LDTR

6.33.1 Syntax

6.33.2 See also

6.34 LDTRB

6.34.1 Syntax

6.34.2 See also

6.35 LDTRH

6.35.1 Syntax

6.35.2 See also

6.36 LDTRSB

6.36.1 Syntax

6.36.2 See also

6.37 LDTRSH

6.37.1 Syntax

6.37.2 See also

6.38 LDTRSW

6.38.1 Syntax

6.38.2 See also

6.39 LDUR (SIMD and FP)

6.39.1 Syntax

6.39.2 See also

6.40 LDUR

6.40.1 Syntax

6.40.2 See also

6.41 LDURB

6.41.1 Syntax

6.41.2 See also

6.42 LDURH

6.42.1 Syntax

6.42.2 See also

6.43 LDURSB

6.43.1 Syntax

6.43.2 See also

6.44 LDURSH

6.44.1 Syntax

6.44.2 See also

6.45 LDURSW

6.45.1 Syntax

6.45.2 See also

6.46 LDXP

6.46.1 Syntax

6.46.2 See also

6.47 LDXR

6.47.1 Syntax

6.47.2 See also

6.48 LDXRB

6.48.1 Syntax

6.48.2 See also

6.49 LDXRH

6.49.1 Syntax

6.49.2 See also

6.50 PRFM (immediate)

6.50.1 Syntax

6.50.2 See also

6.51 PRFM (literal)

6.51.1 Syntax

6.51.2 See also

6.52 PRFM (register)

6.52.1 Syntax

6.52.2 Usage

6.52.3 See also

6.53 PRFUM

6.53.1 Syntax

6.53.2 See also

6.54 STLR

6.54.1 Syntax

6.54.2 See also

6.55 STLRB

6.55.1 Syntax

6.55.2 See also

6.56 STLRH

6.56.1 Syntax

6.56.2 See also

6.57 STLXP

6.57.1 Syntax

6.57.2 See also

6.58 STLXR

6.58.1 Syntax

6.58.2 See also

6.59 STLXRB

6.59.1 Syntax

6.59.2 See also

6.60 STLXRH

6.60.1 Syntax

6.60.2 See also

6.61 STNP (SIMD and FP)

6.61.1 Syntax

6.61.2 See also

6.62 STNP

6.62.1 Syntax

6.62.2 See also

6.63 STP (SIMD and FP)

6.63.1 Syntax

6.63.2 See also

6.64 STP

6.64.1 Syntax

6.64.2 See also

6.65 STR (immediate, SIMD and FP)

6.65.1 Syntax

6.65.2 See also

6.66 STR (immediate)

6.66.1 Syntax

6.66.2 See also

6.67 STR (register, SIMD and FP)

6.67.1 Syntax

6.67.2 Usage

6.67.3 See also

6.68 STR (register)

6.68.1 Syntax

6.68.2 Usage

6.68.3 See also

6.69 STRB (immediate)

6.69.1 Syntax

6.69.2 See also

6.70 STRB (register)

6.70.1 Syntax

6.70.2 Usage

6.70.3 See also

6.71 STRH (immediate)

6.71.1 Syntax

6.71.2 See also

6.72 STRH (register)

6.72.1 Syntax

6.72.2 Usage

6.72.3 See also

6.73 STTR

6.73.1 Syntax

6.73.2 See also

6.74 STTRB

6.74.1 Syntax

6.74.2 See also

6.75 STTRH

6.75.1 Syntax

6.75.2 See also

6.76 STUR (SIMD and FP)

6.76.1 Syntax

6.76.2 See also

6.77 STUR

6.77.1 Syntax

6.77.2 See also

6.78 STURB

6.78.1 Syntax

6.78.2 See also

6.79 STURH

6.79.1 Syntax

6.79.2 See also

6.80 STXP

6.80.1 Syntax

6.80.2 See also

6.81 STXR

6.81.1 Syntax

6.81.2 See also

6.82 STXRB

6.82.1 Syntax

6.82.2 See also

6.83 STXRH

6.83.1 Syntax

6.83.2 See also

7: A64 Floating-point Instructions

7.1 A64 floating-point instructions in alphabetical order

7.2 FABS (scalar)

7.2.1 Syntax

7.2.2 See also

7.3 FADD (scalar)

7.3.1 Syntax

7.3.2 See also

7.4 FCCMP

7.4.1 Syntax

7.4.2 See also

7.5 FCCMPE

7.5.1 Syntax

7.5.2 See also

7.6 FCMP

7.6.1 Syntax

7.6.2 See also

7.7 FCMPE

7.7.1 Syntax

7.7.2 See also

7.8 FCSEL

7.8.1 Syntax

7.8.2 See also

7.9 FCVT

7.9.1 Syntax

7.9.2 See also

7.10 FCVTAS (scalar)

7.10.1 Syntax

7.10.2 See also

7.11 FCVTAU (scalar)

7.11.1 Syntax

7.11.2 See also

7.12 FCVTMS (scalar)

7.12.1 Syntax

7.12.2 See also

7.13 FCVTMU (scalar)

7.13.1 Syntax

7.13.2 See also

7.14 FCVTNS (scalar)

7.14.1 Syntax

7.14.2 See also

7.15 FCVTNU (scalar)

7.15.1 Syntax

7.15.2 See also

7.16 FCVTPS (scalar)

7.16.1 Syntax

7.16.2 See also

7.17 FCVTPU (scalar)

7.17.1 Syntax

7.17.2 See also

7.18 FCVTZS (scalar, fixed-point)

7.18.1 Syntax

7.18.2 See also

7.19 FCVTZS (scalar, integer)

7.19.1 Syntax

7.19.2 See also

7.20 FCVTZU (scalar, fixed-point)

7.20.1 Syntax

7.20.2 See also

7.21 FCVTZU (scalar, integer)

7.21.1 Syntax

7.21.2 See also

7.22 FDIV (scalar)

7.22.1 Syntax

7.22.2 See also

7.23 FMADD

7.23.1 Syntax

7.23.2 See also

7.24 FMAX (scalar)

7.24.1 Syntax

7.24.2 See also

7.25 FMAXNM (scalar)

7.25.1 Syntax

7.25.2 See also

7.26 FMIN (scalar)

7.26.1 Syntax

7.26.2 See also

7.27 FMINNM (scalar)

7.27.1 Syntax

7.27.2 See also

7.28 FMOV (register)

7.28.1 Syntax

7.28.2 See also

7.29 FMOV (general)

7.29.1 Syntax

7.29.2 See also

7.30 FMOV (scalar, immediate)

7.30.1 Syntax

7.30.2 See also

7.31 FMSUB

7.31.1 Syntax

7.31.2 See also

7.32 FMUL (scalar)

7.32.1 Syntax

7.32.2 See also

7.33 FNEG (scalar)

7.33.1 Syntax

7.33.2 See also

7.34 FNMADD

7.34.1 Syntax

7.34.2 See also

7.35 FNMSUB

7.35.1 Syntax

7.35.2 See also

7.36 FNMUL

7.36.1 Syntax

7.36.2 See also

7.37 FRINTA (scalar)

7.37.1 Syntax

7.37.2 See also

7.38 FRINTI (scalar)

7.38.1 Syntax

7.38.2 See also

7.39 FRINTM (scalar)

7.39.1 Syntax

7.39.2 See also

7.40 FRINTN (scalar)

7.40.1 Syntax

7.40.2 See also

7.41 FRINTP (scalar)

7.41.1 Syntax

7.41.2 See also

7.42 FRINTX (scalar)

7.42.1 Syntax

7.42.2 See also

7.43 FRINTZ (scalar)

7.43.1 Syntax

7.43.2 See also

7.44 FSQRT (scalar)

7.44.1 Syntax

7.44.2 See also

7.45 FSUB (scalar)

7.45.1 Syntax

7.45.2 See also

7.46 SCVTF (scalar, fixed-point)

7.46.1 Syntax

7.46.2 See also

7.47 SCVTF (scalar, integer)

7.47.1 Syntax

7.47.2 See also

7.48 UCVTF (scalar, fixed-point)

7.48.1 Syntax

7.48.2 See also

7.49 UCVTF (scalar, integer)

7.49.1 Syntax

7.49.2 See also

8: A64 SIMD Scalar Instructions

8.1 A64 SIMD scalar instructions in alphabetical order

8.2 ABS (scalar)

8.2.1 Syntax

8.2.2 See also

8.3 ADD (scalar)

8.3.1 Syntax

8.3.2 See also

8.4 ADDP (scalar)

8.4.1 Syntax

8.4.2 See also

8.5 CMEQ (scalar, register)

8.5.1 Syntax

8.5.2 See also

8.6 CMEQ (scalar, zero)

8.6.1 Syntax

8.6.2 See also

8.7 CMGE (scalar, register)

8.7.1 Syntax

8.7.2 See also

8.8 CMGE (scalar, zero)

8.8.1 Syntax

8.8.2 See also

8.9 CMGT (scalar, register)

8.9.1 Syntax

8.9.2 See also

8.10 CMGT (scalar, zero)

8.10.1 Syntax

8.10.2 See also

8.11 CMHI (scalar, register)

8.11.1 Syntax

8.11.2 See also

8.12 CMHS (scalar, register)

8.12.1 Syntax

8.12.2 See also

8.13 CMLE (scalar, zero)

8.13.1 Syntax

8.13.2 See also

8.14 CMLT (scalar, zero)

8.14.1 Syntax

8.14.2 See also

8.15 CMTST (scalar)

8.15.1 Syntax

8.15.2 See also

8.16 DUP (scalar, element)

8.16.1 Syntax

8.16.2 Usage

8.16.3 See also

8.17 FABD (scalar)

8.17.1 Syntax

8.17.2 See also

8.18 FACGE (scalar)

8.18.1 Syntax

8.18.2 See also

8.19 FACGT (scalar)

8.19.1 Syntax

8.19.2 See also

8.20 FADDP (scalar)

8.20.1 Syntax

8.20.2 Usage

8.20.3 See also

8.21 FCMEQ (scalar, register)

8.21.1 Syntax

8.21.2 See also

8.22 FCMEQ (scalar, zero)

8.22.1 Syntax

8.22.2 See also

8.23 FCMGE (scalar, register)

8.23.1 Syntax

8.23.2 See also

8.24 FCMGE (scalar, zero)

8.24.1 Syntax

8.24.2 See also

8.25 FCMGT (scalar, register)

8.25.1 Syntax

8.25.2 See also

8.26 FCMGT (scalar, zero)

8.26.1 Syntax

8.26.2 See also

8.27 FCMLE (scalar, zero)

8.27.1 Syntax

8.27.2 See also

8.28 FCMLT (scalar, zero)

8.28.1 Syntax

8.28.2 See also

8.29 FCVTAS (scalar)

8.29.1 Syntax

8.29.2 See also

8.30 FCVTAU (scalar)

8.30.1 Syntax

8.30.2 See also

8.31 FCVTMS (scalar)

8.31.1 Syntax

8.31.2 See also

8.32 FCVTMU (scalar)

8.32.1 Syntax

8.32.2 See also

8.33 FCVTNS (scalar)

8.33.1 Syntax

8.33.2 See also

8.34 FCVTNU (scalar)

8.34.1 Syntax

8.34.2 See also

8.35 FCVTPS (scalar)

8.35.1 Syntax

8.35.2 See also

8.36 FCVTPU (scalar)

8.36.1 Syntax

8.36.2 See also

8.37 FCVTXN (scalar)

8.37.1 Syntax

8.37.2 See also

8.38 FCVTZS (scalar, fixed-point)

8.38.1 Syntax

8.38.2 Usage

8.38.3 See also

8.39 FCVTZS (scalar, integer)

8.39.1 Syntax

8.39.2 See also

8.40 FCVTZU (scalar, fixed-point)

8.40.1 Syntax

8.40.2 Usage

8.40.3 See also

8.41 FCVTZU (scalar, integer)

8.41.1 Syntax

8.41.2 See also

8.42 FMAXNMP (scalar)

8.42.1 Syntax

8.42.2 Usage

8.42.3 See also

8.43 FMAXP (scalar)

8.43.1 Syntax

8.43.2 Usage

8.43.3 See also

8.44 FMINNMP (scalar)

8.44.1 Syntax

8.44.2 Usage

8.44.3 See also

8.45 FMINP (scalar)

8.45.1 Syntax

8.45.2 Usage

8.45.3 See also

8.46 FMLA (scalar, by element)

8.46.1 Syntax

8.46.2 Usage

8.46.3 See also

8.47 FMLS (scalar, by element)

8.47.1 Syntax

8.47.2 Usage

8.47.3 See also

8.48 FMUL (scalar, by element)

8.48.1 Syntax

8.48.2 Usage

8.48.3 See also

8.49 FMULX (scalar, by element)

8.49.1 Syntax

8.49.2 Usage

8.49.3 See also

8.50 FMULX (scalar)

8.50.1 Syntax

8.50.2 See also

8.51 FRECPE (scalar)

8.51.1 Syntax

8.51.2 See also

8.52 FRECPS (scalar)

8.52.1 Syntax

8.52.2 See also

8.53 FRECPX (scalar)

8.53.1 Syntax

8.53.2 See also

8.54 FRSQRTE (scalar)

8.54.1 Syntax

8.54.2 See also

8.55 FRSQRTS (scalar)

8.55.1 Syntax

8.55.2 See also

8.56 MOV (scalar)

8.56.1 Syntax

8.56.2 Usage

8.56.3 See also

8.57 NEG (scalar)

8.57.1 Syntax

8.57.2 See also

8.58 SCVTF (scalar, fixed-point)

8.58.1 Syntax

8.58.2 Usage

8.58.3 See also

8.59 SCVTF (scalar, integer)

8.59.1 Syntax

8.59.2 See also

8.60 SHL (scalar)

8.60.1 Syntax

8.60.2 See also

8.61 SLI (scalar)

8.61.1 Syntax

8.61.2 See also

8.62 SQABS (scalar)

8.62.1 Syntax

8.62.2 See also

8.63 SQADD (scalar)

8.63.1 Syntax

8.63.2 See also

8.64 SQDMLAL (scalar, by element)

8.64.1 Syntax

8.64.2 Usage

8.64.3 See also

8.65 SQDMLAL (scalar)

8.65.1 Syntax

8.65.2 Usage

8.65.3 See also

8.66 SQDMLSL (scalar, by element)

8.66.1 Syntax

8.66.2 Usage

8.66.3 See also

8.67 SQDMLSL (scalar)

8.67.1 Syntax

8.67.2 Usage

8.67.3 See also

8.68 SQDMULH (scalar, by element)

8.68.1 Syntax

8.68.2 Usage

8.68.3 See also

8.69 SQDMULH (scalar)

8.69.1 Syntax

8.69.2 See also

8.70 SQDMULL (scalar, by element)

8.70.1 Syntax

8.70.2 Usage

8.70.3 See also

8.71 SQDMULL (scalar)

8.71.1 Syntax

8.71.2 Usage

8.71.3 See also

8.72 SQNEG (scalar)

8.72.1 Syntax

8.72.2 See also

8.73 SQRDMULH (scalar, by element)

8.73.1 Syntax

8.73.2 Usage

8.73.3 See also

8.74 SQRDMULH (scalar)

8.74.1 Syntax

8.74.2 See also

8.75 SQRSHL (scalar)

8.75.1 Syntax

8.75.2 See also

8.76 SQRSHRN (scalar)

8.76.1 Syntax

8.76.2 Usage

8.76.3 See also

8.77 SQRSHRUN (scalar)

8.77.1 Syntax

8.77.2 Usage

8.77.3 See also

8.78 SQSHL (scalar, immediate)

8.78.1 Syntax

8.78.2 Usage

8.78.3 See also

8.79 SQSHL (scalar, register)

8.79.1 Syntax

8.79.2 See also

8.80 SQSHLU (scalar)

8.80.1 Syntax

8.80.2 Usage

8.80.3 See also

8.81 SQSHRN (scalar)

8.81.1 Syntax

8.81.2 Usage

8.81.3 See also

8.82 SQSHRUN (scalar)

8.82.1 Syntax

8.82.2 Usage

8.82.3 See also

8.83 SQSUB (scalar)

8.83.1 Syntax

8.83.2 See also

8.84 SQXTN (scalar)

8.84.1 Syntax

8.84.2 Usage

8.84.3 See also

8.85 SQXTUN (scalar)

8.85.1 Syntax

8.85.2 Usage

8.85.3 See also

8.86 SRI (scalar)

8.86.1 Syntax

8.86.2 See also

8.87 SRSHL (scalar)

8.87.1 Syntax

8.87.2 See also

8.88 SRSHR (scalar)

8.88.1 Syntax

8.88.2 See also

8.89 SRSRA (scalar)

8.89.1 Syntax

8.89.2 See also

8.90 SSHL (scalar)

8.90.1 Syntax

8.90.2 See also

8.91 SSHR (scalar)

8.91.1 Syntax

8.91.2 See also

8.92 SSRA (scalar)

8.92.1 Syntax

8.92.2 See also

8.93 SUB (scalar)

8.93.1 Syntax

8.93.2 See also

8.94 SUQADD (scalar)

8.94.1 Syntax

8.94.2 See also

8.95 UCVTF (scalar, fixed-point)

8.95.1 Syntax

8.95.2 Usage

8.95.3 See also

8.96 UCVTF (scalar, integer)

8.96.1 Syntax

8.96.2 See also

8.97 UQADD (scalar)

8.97.1 Syntax

8.97.2 See also

8.98 UQRSHL (scalar)

8.98.1 Syntax

8.98.2 See also

8.99 UQRSHRN (scalar)

8.99.1 Syntax

8.99.2 Usage

8.99.3 See also

8.100 UQSHL (scalar, immediate)

8.100.1 Syntax

8.100.2 Usage

8.100.3 See also

8.101 UQSHL (scalar, register)

8.101.1 Syntax

8.101.2 See also

8.102 UQSHRN (scalar)

8.102.1 Syntax

8.102.2 Usage

8.102.3 See also

8.103 UQSUB (scalar)

8.103.1 Syntax

8.103.2 See also

8.104 UQXTN (scalar)

8.104.1 Syntax

8.104.2 Usage

8.104.3 See also

8.105 URSHL (scalar)

8.105.1 Syntax

8.105.2 See also

8.106 URSHR (scalar)

8.106.1 Syntax

8.106.2 See also

8.107 URSRA (scalar)

8.107.1 Syntax

8.107.2 See also

8.108 USHL (scalar)

8.108.1 Syntax

8.108.2 See also

8.109 USHR (scalar)

8.109.1 Syntax

8.109.2 See also

8.110 USQADD (scalar)

8.110.1 Syntax

8.110.2 See also

8.111 USRA (scalar)

8.111.1 Syntax

8.111.2 See also

9: A64 SIMD Vector Instructions

9.1 A64 SIMD vector instructions in alphabetical order

9.2 ABS (vector)

9.2.1 Syntax

9.2.2 See also

9.3 ADD (vector)

9.3.1 Syntax

9.3.2 See also

9.4 ADDHN, ADDHN2 (vector)

9.4.1 Syntax

9.4.2 Usage

9.4.3 See also

9.5 ADDP (vector)

9.5.1 Syntax

9.5.2 See also

9.6 ADDV (vector)

9.6.1 Syntax

9.6.2 Usage

9.6.3 See also

9.7 AND (vector)

9.7.1 Syntax

9.7.2 See also

9.8 BIC (vector, immediate)

9.8.1 Syntax

9.8.2 See also

9.9 BIC (vector, register)

9.9.1 Syntax

9.9.2 See also

9.10 BIF (vector)

9.10.1 Syntax

9.10.2 See also

9.11 BIT (vector)

9.11.1 Syntax

9.11.2 See also

9.12 BSL (vector)

9.12.1 Syntax

9.12.2 See also

9.13 CLS (vector)

9.13.1 Syntax

9.13.2 See also

9.14 CLZ (vector)

9.14.1 Syntax

9.14.2 See also

9.15 CMEQ (vector, register)

9.15.1 Syntax

9.15.2 See also

9.16 CMEQ (vector, zero)

9.16.1 Syntax

9.16.2 See also

9.17 CMGE (vector, register)

9.17.1 Syntax

9.17.2 See also

9.18 CMGE (vector, zero)

9.18.1 Syntax

9.18.2 See also

9.19 CMGT (vector, register)

9.19.1 Syntax

9.19.2 See also

9.20 CMGT (vector, zero)

9.20.1 Syntax

9.20.2 See also

9.21 CMHI (vector, register)

9.21.1 Syntax

9.21.2 See also

9.22 CMHS (vector, register)

9.22.1 Syntax

9.22.2 See also

9.23 CMLE (vector, zero)

9.23.1 Syntax

9.23.2 See also

9.24 CMLT (vector, zero)

9.24.1 Syntax

9.24.2 See also

9.25 CMTST (vector)

9.25.1 Syntax

9.25.2 See also

9.26 CNT (vector)

9.26.1 Syntax

9.26.2 See also

9.27 DUP (vector, element)

9.27.1 Syntax

9.27.2 Usage

9.27.3 See also

9.28 DUP (vector, general)

9.28.1 Syntax

9.28.2 Usage

9.28.3 See also

9.29 EOR (vector)

9.29.1 Syntax

9.29.2 See also

9.30 EXT (vector)

9.30.1 Syntax

9.30.2 Usage

9.30.3 See also

9.31 FABD (vector)

9.31.1 Syntax

9.31.2 See also

9.32 FABS (vector)

9.32.1 Syntax

9.32.2 See also

9.33 FACGE (vector)

9.33.1 Syntax

9.33.2 See also

9.34 FACGT (vector)

9.34.1 Syntax

9.34.2 See also

9.35 FADD (vector)

9.35.1 Syntax

9.35.2 See also

9.36 FADDP (vector)

9.36.1 Syntax

9.36.2 See also

9.37 FCMEQ (vector, register)

9.37.1 Syntax

9.37.2 See also

9.38 FCMEQ (vector, zero)

9.38.1 Syntax

9.38.2 See also

9.39 FCMGE (vector, register)

9.39.1 Syntax

9.39.2 See also

9.40 FCMGE (vector, zero)

9.40.1 Syntax

9.40.2 See also

9.41 FCMGT (vector, register)

9.41.1 Syntax

9.41.2 See also

9.42 FCMGT (vector, zero)

9.42.1 Syntax

9.42.2 See also

9.43 FCMLE (vector, zero)

9.43.1 Syntax

9.43.2 See also

9.44 FCMLT (vector, zero)

9.44.1 Syntax

9.44.2 See also

9.45 FCVTAS (vector)

9.45.1 Syntax

9.45.2 See also

9.46 FCVTAU (vector)

9.46.1 Syntax

9.46.2 See also

9.47 FCVTL, FCVTL2 (vector)

9.47.1 Syntax

9.47.2 Usage

9.47.3 See also

9.48 FCVTMS (vector)

9.48.1 Syntax

9.48.2 See also

9.49 FCVTMU (vector)

9.49.1 Syntax

9.49.2 See also

9.50 FCVTN, FCVTN2 (vector)

9.50.1 Syntax

9.50.2 Usage

9.50.3 See also

9.51 FCVTNS (vector)

9.51.1 Syntax

9.51.2 See also

9.52 FCVTNU (vector)

9.52.1 Syntax

9.52.2 See also

9.53 FCVTPS (vector)

9.53.1 Syntax

9.53.2 See also

9.54 FCVTPU (vector)

9.54.1 Syntax

9.54.2 See also

9.55 FCVTXN, FCVTXN2 (vector)

9.55.1 Syntax

9.55.2 Usage

9.55.3 See also

9.56 FCVTZS (vector, fixed-point)

9.56.1 Syntax

9.56.2 Usage

9.56.3 See also

9.57 FCVTZS (vector, integer)

9.57.1 Syntax

9.57.2 See also

9.58 FCVTZU (vector, fixed-point)

9.58.1 Syntax

9.58.2 Usage

9.58.3 See also

9.59 FCVTZU (vector, integer)

9.59.1 Syntax

9.59.2 See also

9.60 FDIV (vector)

9.60.1 Syntax

9.60.2 See also

9.61 FMAX (vector)

9.61.1 Syntax

9.61.2 See also

9.62 FMAXNM (vector)

9.62.1 Syntax

9.62.2 See also

9.63 FMAXNMP (vector)

9.63.1 Syntax

9.63.2 See also

9.64 FMAXNMV (vector)

9.64.1 Syntax

9.64.2 See also

9.65 FMAXP (vector)

9.65.1 Syntax

9.65.2 See also

9.66 FMAXV (vector)

9.66.1 Syntax

9.66.2 See also

9.67 FMIN (vector)

9.67.1 Syntax

9.67.2 See also

9.68 FMINNM (vector)

9.68.1 Syntax

9.68.2 See also

9.69 FMINNMP (vector)

9.69.1 Syntax

9.69.2 See also

9.70 FMINNMV (vector)

9.70.1 Syntax

9.70.2 See also

9.71 FMINP (vector)

9.71.1 Syntax

9.71.2 See also

9.72 FMINV (vector)

9.72.1 Syntax

9.72.2 See also

9.73 FMLA (vector, by element)

9.73.1 Syntax

9.73.2 Usage

9.73.3 See also

9.74 FMLA (vector)

9.74.1 Syntax

9.74.2 See also

9.75 FMLS (vector, by element)

9.75.1 Syntax

9.75.2 Usage

9.75.3 See also

9.76 FMLS (vector)

9.76.1 Syntax

9.76.2 See also

9.77 FMOV (vector, immediate)

9.77.1 Syntax

9.77.2 See also

9.78 FMUL (vector, by element)

9.78.1 Syntax

9.78.2 Usage

9.78.3 See also

9.79 FMUL (vector)

9.79.1 Syntax

9.79.2 See also

9.80 FMULX (vector, by element)

9.80.1 Syntax

9.80.2 Usage

9.80.3 See also

9.81 FMULX (vector)

9.81.1 Syntax

9.81.2 See also

9.82 FNEG (vector)

9.82.1 Syntax

9.82.2 See also

9.83 FRECPE (vector)

9.83.1 Syntax

9.83.2 See also

9.84 FRECPS (vector)

9.84.1 Syntax

9.84.2 See also

9.85 FRINTA (vector)

9.85.1 Syntax

9.85.2 See also

9.86 FRINTI (vector)

9.86.1 Syntax

9.86.2 See also

9.87 FRINTM (vector)

9.87.1 Syntax

9.87.2 See also

9.88 FRINTN (vector)

9.88.1 Syntax

9.88.2 See also

9.89 FRINTP (vector)

9.89.1 Syntax

9.89.2 See also

9.90 FRINTX (vector)

9.90.1 Syntax

9.90.2 See also

9.91 FRINTZ (vector)

9.91.1 Syntax

9.91.2 See also

9.92 FRSQRTE (vector)

9.92.1 Syntax

9.92.2 See also

9.93 FRSQRTS (vector)

9.93.1 Syntax

9.93.2 See also

9.94 FSQRT (vector)

9.94.1 Syntax

9.94.2 See also

9.95 FSUB (vector)

9.95.1 Syntax

9.95.2 See also

9.96 INS (vector, element)

9.96.1 Syntax

9.96.2 Usage

9.96.3 See also

9.97 INS (vector, general)

9.97.1 Syntax

9.97.2 Usage

9.97.3 See also

9.98 LD1 (vector, multiple structures)

9.98.1 Syntax

9.98.2 Usage

9.98.3 See also

9.99 LD1 (vector, single structure)

9.99.1 Syntax

9.99.2 See also

9.100 LD1R (vector)

9.100.1 Syntax

9.100.2 Usage

9.100.3 See also

9.101 LD2 (vector, multiple structures)

9.101.1 Syntax

9.101.2 See also

9.102 LD2 (vector, single structure)

9.102.1 Syntax

9.102.2 See also

9.103 LD2R (vector)

9.103.1 Syntax

9.103.2 Usage

9.103.3 See also

9.104 LD3 (vector, multiple structures)

9.104.1 Syntax

9.104.2 See also

9.105 LD3 (vector, single structure)

9.105.1 Syntax

9.105.2 See also

9.106 LD3R (vector)

9.106.1 Syntax

9.106.2 Usage

9.106.3 See also

9.107 LD4 (vector, multiple structures)

9.107.1 Syntax

9.107.2 See also

9.108 LD4 (vector, single structure)

9.108.1 Syntax

9.108.2 See also

9.109 LD4R (vector)

9.109.1 Syntax

9.109.2 Usage

9.109.3 See also

9.110 MLA (vector, by element)

9.110.1 Syntax

9.110.2 Usage

9.110.3 See also

9.111 MLA (vector)

9.111.1 Syntax

9.111.2 See also

9.112 MLS (vector, by element)

9.112.1 Syntax

9.112.2 Usage

9.112.3 See also

9.113 MLS (vector)

9.113.1 Syntax

9.113.2 See also

9.114 MOV (vector, element)

9.114.1 Syntax

9.114.2 Usage

9.114.3 See also

9.115 MOV (vector, from general)

9.115.1 Syntax

9.115.2 Usage

9.115.3 See also

9.116 MOV (vector)

9.116.1 Syntax

9.116.2 See also

9.117 MOV (vector, to general)

9.117.1 Syntax

9.117.2 See also

9.118 MOVI (vector)

9.118.1 Syntax

9.118.2 See also

9.119 MUL (vector, by element)

9.119.1 Syntax

9.119.2 Usage

9.119.3 See also

9.120 MUL (vector)

9.120.1 Syntax

9.120.2 See also

9.121 MVN (vector)

9.121.1 Syntax

9.121.2 See also

9.122 MVNI (vector)

9.122.1 Syntax

9.122.2 See also

9.123 NEG (vector)

9.123.1 Syntax

9.123.2 See also

9.124 NOT (vector)

9.124.1 Syntax

9.124.2 See also

9.125 ORN (vector)

9.125.1 Syntax

9.125.2 See also

9.126 ORR (vector, immediate)

9.126.1 Syntax

9.126.2 See also

9.127 ORR (vector, register)

9.127.1 Syntax

9.127.2 See also

9.128 PMUL (vector)

9.128.1 Syntax

9.128.2 See also

9.129 PMULL, PMULL2 (vector)

9.129.1 Syntax

9.129.2 Usage

9.129.3 See also

9.130 RADDHN, RADDHN2 (vector)

9.130.1 Syntax

9.130.2 Usage

9.130.3 See also

9.131 RBIT (vector)

9.131.1 Syntax

9.131.2 See also

9.132 REV16 (vector)

9.132.1 Syntax

9.132.2 See also

9.133 REV32 (vector)

9.133.1 Syntax

9.133.2 See also

9.134 REV64 (vector)

9.134.1 Syntax

9.134.2 See also

9.135 RSHRN, RSHRN2 (vector)

9.135.1 Syntax

9.135.2 Usage

9.135.3 See also

9.136 RSUBHN, RSUBHN2 (vector)

9.136.1 Syntax

9.136.2 Usage

9.136.3 See also

9.137 SABA (vector)

9.137.1 Syntax

9.137.2 See also

9.138 SABAL, SABAL2 (vector)

9.138.1 Syntax

9.138.2 Usage

9.138.3 See also

9.139 SABD (vector)

9.139.1 Syntax

9.139.2 See also

9.140 SABDL, SABDL2 (vector)

9.140.1 Syntax

9.140.2 Usage

9.140.3 See also

9.141 SADALP (vector)

9.141.1 Syntax

9.141.2 Usage

9.141.3 See also

9.142 SADDL, SADDL2 (vector)

9.142.1 Syntax

9.142.2 Usage

9.142.3 See also

9.143 SADDLP (vector)

9.143.1 Syntax

9.143.2 Usage

9.143.3 See also

9.144 SADDLV (vector)

9.144.1 Syntax

9.144.2 Usage

9.144.3 See also

9.145 SADDW, SADDW2 (vector)

9.145.1 Syntax

9.145.2 Usage

9.145.3 See also

9.146 SCVTF (vector, fixed-point)

9.146.1 Syntax

9.146.2 Usage

9.146.3 See also

9.147 SCVTF (vector, integer)

9.147.1 Syntax

9.147.2 See also

9.148 SHADD (vector)

9.148.1 Syntax

9.148.2 See also

9.149 SHL (vector)

9.149.1 Syntax

9.149.2 Usage

9.149.3 See also

9.150 SHLL, SHLL2 (vector)

9.150.1 Syntax

9.150.2 Usage

9.150.3 See also

9.151 SHRN, SHRN2 (vector)

9.151.1 Syntax

9.151.2 Usage

9.151.3 See also

9.152 SHSUB (vector)

9.152.1 Syntax

9.152.2 See also

9.153 SLI (vector)

9.153.1 Syntax

9.153.2 Usage

9.153.3 See also

9.154 SMAX (vector)

9.154.1 Syntax

9.154.2 See also

9.155 SMAXP (vector)

9.155.1 Syntax

9.155.2 See also

9.156 SMAXV (vector)

9.156.1 Syntax

9.156.2 Usage

9.156.3 See also

9.157 SMIN (vector)

9.157.1 Syntax

9.157.2 See also

9.158 SMINP (vector)

9.158.1 Syntax

9.158.2 See also

9.159 SMINV (vector)

9.159.1 Syntax

9.159.2 Usage

9.159.3 See also

9.160 SMLAL, SMLAL2 (vector, by element)

9.160.1 Syntax

9.160.2 Usage

9.160.3 See also

9.161 SMLAL, SMLAL2 (vector)

9.161.1 Syntax

9.161.2 Usage

9.161.3 See also

9.162 SMLSL, SMLSL2 (vector, by element)

9.162.1 Syntax

9.162.2 Usage

9.162.3 See also

9.163 SMLSL, SMLSL2 (vector)

9.163.1 Syntax

9.163.2 Usage

9.163.3 See also

9.164 SMOV (vector)

9.164.1 Syntax

9.164.2 Usage

9.164.3 See also

9.165 SMULL, SMULL2 (vector, by element)

9.165.1 Syntax

9.165.2 Usage

9.165.3 See also

9.166 SMULL, SMULL2 (vector)

9.166.1 Syntax

9.166.2 Usage

9.166.3 See also

9.167 SQABS (vector)

9.167.1 Syntax

9.167.2 See also

9.168 SQADD (vector)

9.168.1 Syntax

9.168.2 See also

9.169 SQDMLAL, SQDMLAL2 (vector, by element)

9.169.1 Syntax

9.169.2 Usage

9.169.3 See also

9.170 SQDMLAL, SQDMLAL2 (vector)

9.170.1 Syntax

9.170.2 Usage

9.170.3 See also

9.171 SQDMLSL, SQDMLSL2 (vector, by element)

9.171.1 Syntax

9.171.2 Usage

9.171.3 See also

9.172 SQDMLSL, SQDMLSL2 (vector)

9.172.1 Syntax

9.172.2 Usage

9.172.3 See also

9.173 SQDMULH (vector, by element)

9.173.1 Syntax

9.173.2 Usage

9.173.3 See also

9.174 SQDMULH (vector)

9.174.1 Syntax

9.174.2 See also

9.175 SQDMULL, SQDMULL2 (vector, by element)

9.175.1 Syntax

9.175.2 Usage

9.175.3 See also

9.176 SQDMULL, SQDMULL2 (vector)

9.176.1 Syntax

9.176.2 Usage

9.176.3 See also

9.177 SQNEG (vector)

9.177.1 Syntax

9.177.2 See also

9.178 SQRDMULH (vector, by element)

9.178.1 Syntax

9.178.2 Usage

9.178.3 See also

9.179 SQRDMULH (vector)

9.179.1 Syntax

9.179.2 See also

9.180 SQRSHL (vector)

9.180.1 Syntax

9.180.2 See also

9.181 SQRSHRN, SQRSHRN2 (vector)

9.181.1 Syntax

9.181.2 Usage

9.181.3 See also

9.182 SQRSHRUN, SQRSHRUN2 (vector)

9.182.1 Syntax

9.182.2 Usage

9.182.3 See also

9.183 SQSHL (vector, immediate)

9.183.1 Syntax

9.183.2 Usage

9.183.3 See also

9.184 SQSHL (vector, register)

9.184.1 Syntax

9.184.2 See also

9.185 SQSHLU (vector)

9.185.1 Syntax

9.185.2 Usage

9.185.3 See also

9.186 SQSHRN, SQSHRN2 (vector)

9.186.1 Syntax

9.186.2 Usage

9.186.3 See also

9.187 SQSHRUN, SQSHRUN2 (vector)

9.187.1 Syntax

9.187.2 Usage

9.187.3 See also

9.188 SQSUB (vector)

9.188.1 Syntax

9.188.2 See also

9.189 SQXTN, SQXTN2 (vector)

9.189.1 Syntax

9.189.2 Usage

9.189.3 See also

9.190 SQXTUN, SQXTUN2 (vector)

9.190.1 Syntax

9.190.2 Usage

9.190.3 See also

9.191 SRHADD (vector)

9.191.1 Syntax

9.191.2 See also

9.192 SRI (vector)

9.192.1 Syntax

9.192.2 Usage

9.192.3 See also

9.193 SRSHL (vector)

9.193.1 Syntax

9.193.2 See also

9.194 SRSHR (vector)

9.194.1 Syntax

9.194.2 Usage

9.194.3 See also

9.195 SRSRA (vector)

9.195.1 Syntax

9.195.2 Usage

9.195.3 See also

9.196 SSHL (vector)

9.196.1 Syntax

9.196.2 See also

9.197 SSHLL, SSHLL2 (vector)

9.197.1 Syntax

9.197.2 Usage

9.197.3 See also

9.198 SSHR (vector)

9.198.1 Syntax

9.198.2 Usage

9.198.3 See also

9.199 SSRA (vector)

9.199.1 Syntax

9.199.2 Usage

9.199.3 See also

9.200 SSUBL, SSUBL2 (vector)

9.200.1 Syntax

9.200.2 Usage

9.200.3 See also

9.201 SSUBW, SSUBW2 (vector)

9.201.1 Syntax

9.201.2 Usage

9.201.3 See also

9.202 ST1 (vector, multiple structures)

9.202.1 Syntax

9.202.2 Usage

9.202.3 See also

9.203 ST1 (vector, single structure)

9.203.1 Syntax

9.203.2 See also

9.204 ST2 (vector, multiple structures)

9.204.1 Syntax

9.204.2 See also

9.205 ST2 (vector, single structure)

9.205.1 Syntax

9.205.2 See also

9.206 ST3 (vector, multiple structures)

9.206.1 Syntax

9.206.2 See also

9.207 ST3 (vector, single structure)

9.207.1 Syntax

9.207.2 See also

9.208 ST4 (vector, multiple structures)

9.208.1 Syntax

9.208.2 See also

9.209 ST4 (vector, single structure)

9.209.1 Syntax

9.209.2 See also

9.210 SUB (vector)

9.210.1 Syntax

9.210.2 See also

9.211 SUBHN, SUBHN2 (vector)

9.211.1 Syntax

9.211.2 Usage

9.211.3 See also

9.212 SUQADD (vector)

9.212.1 Syntax

9.212.2 See also

9.213 SXTL, SXTL2 (vector)

9.213.1 Syntax

9.213.2 Usage

9.213.3 See also

9.214 TBL (vector)

9.214.1 Syntax

9.214.2 See also

9.215 TBX (vector)

9.215.1 Syntax

9.215.2 See also

9.216 TRN1 (vector)

9.216.1 Syntax

9.216.2 See also

9.217 TRN2 (vector)

9.217.1 Syntax

9.217.2 See also

9.218 UABA (vector)

9.218.1 Syntax

9.218.2 See also

9.219 UABAL, UABAL2 (vector)

9.219.1 Syntax

9.219.2 Usage

9.219.3 See also

9.220 UABD (vector)

9.220.1 Syntax

9.220.2 See also

9.221 UABDL, UABDL2 (vector)

9.221.1 Syntax

9.221.2 Usage

9.221.3 See also

9.222 UADALP (vector)

9.222.1 Syntax

9.222.2 Usage

9.222.3 See also

9.223 UADDL, UADDL2 (vector)

9.223.1 Syntax

9.223.2 Usage

9.223.3 See also

9.224 UADDLP (vector)

9.224.1 Syntax

9.224.2 Usage

9.224.3 See also

9.225 UADDLV (vector)

9.225.1 Syntax

9.225.2 Usage

9.225.3 See also

9.226 UADDW, UADDW2 (vector)

9.226.1 Syntax

9.226.2 Usage

9.226.3 See also

9.227 UCVTF (vector, fixed-point)

9.227.1 Syntax

9.227.2 Usage

9.227.3 See also

9.228 UCVTF (vector, integer)

9.228.1 Syntax

9.228.2 See also

9.229 UHADD (vector)

9.229.1 Syntax

9.229.2 See also

9.230 UHSUB (vector)

9.230.1 Syntax

9.230.2 See also

9.231 UMAX (vector)

9.231.1 Syntax

9.231.2 See also

9.232 UMAXP (vector)

9.232.1 Syntax

9.232.2 See also

9.233 UMAXV (vector)

9.233.1 Syntax

9.233.2 Usage

9.233.3 See also

9.234 UMIN (vector)

9.234.1 Syntax

9.234.2 See also

9.235 UMINP (vector)

9.235.1 Syntax

9.235.2 See also

9.236 UMINV (vector)

9.236.1 Syntax

9.236.2 Usage

9.236.3 See also

9.237 UMLAL, UMLAL2 (vector, by element)

9.237.1 Syntax

9.237.2 Usage

9.237.3 See also

9.238 UMLAL, UMLAL2 (vector)

9.238.1 Syntax

9.238.2 Usage

9.238.3 See also

9.239 UMLSL, UMLSL2 (vector, by element)

9.239.1 Syntax

9.239.2 Usage

9.239.3 See also

9.240 UMLSL, UMLSL2 (vector)

9.240.1 Syntax

9.240.2 Usage

9.240.3 See also

9.241 UMOV (vector)

9.241.1 Syntax

9.241.2 Usage

9.241.3 See also

9.242 UMULL, UMULL2 (vector, by element)

9.242.1 Syntax

9.242.2 Usage

9.242.3 See also

9.243 UMULL, UMULL2 (vector)

9.243.1 Syntax

9.243.2 Usage

9.243.3 See also

9.244 UQADD (vector)

9.244.1 Syntax

9.244.2 See also

9.245 UQRSHL (vector)

9.245.1 Syntax

9.245.2 See also

9.246 UQRSHRN, UQRSHRN2 (vector)

9.246.1 Syntax

9.246.2 Usage

9.246.3 See also

9.247 UQSHL (vector, immediate)

9.247.1 Syntax

9.247.2 Usage

9.247.3 See also

9.248 UQSHL (vector, register)

9.248.1 Syntax

9.248.2 See also

9.249 UQSHRN, UQSHRN2 (vector)

9.249.1 Syntax

9.249.2 Usage

9.249.3 See also

9.250 UQSUB (vector)

9.250.1 Syntax

9.250.2 See also

9.251 UQXTN, UQXTN2 (vector)

9.251.1 Syntax

9.251.2 Usage

9.251.3 See also

9.252 URECPE (vector)

9.252.1 Syntax

9.252.2 See also

9.253 URHADD (vector)

9.253.1 Syntax

9.253.2 See also

9.254 URSHL (vector)

9.254.1 Syntax

9.254.2 See also

9.255 URSHR (vector)

9.255.1 Syntax

9.255.2 Usage

9.255.3 See also

9.256 URSQRTE (vector)

9.256.1 Syntax

9.256.2 See also

9.257 URSRA (vector)

9.257.1 Syntax

9.257.2 Usage

9.257.3 See also

9.258 USHL (vector)

9.258.1 Syntax

9.258.2 See also

9.259 USHLL, USHLL2 (vector)

9.259.1 Syntax

9.259.2 Usage

9.259.3 See also

9.260 USHR (vector)

9.260.1 Syntax

9.260.2 Usage

9.260.3 See also

9.261 USQADD (vector)

9.261.1 Syntax

9.261.2 See also

9.262 USRA (vector)

9.262.1 Syntax

9.262.2 Usage

9.262.3 See also

9.263 USUBL, USUBL2 (vector)

9.263.1 Syntax

9.263.2 Usage

9.263.3 See also

9.264 USUBW, USUBW2 (vector)

9.264.1 Syntax

9.264.2 Usage

9.264.3 See also