中国科技论文在线

http://www.paper.edu.cn

基于 FPGA 的 SVPWM 实现方法

付凤超, 戴鹏

中国矿业大学 信息与电气工程学院,江苏 徐州(221008 )

E-mail:fufengchao@163.com

摘 要:SVPWM 算法以其输出电流谐波含量小、数字化容易等特点,在高性能电机调速系

统中得到了广泛的应用。但同时它对处理器的处理速度也有了更高的要求,一般处理速度需

要达到数百纳秒级。结合 FPGA 处理速度快的特点,本文提出了一种基于 FPGA 的 SVPWM

的实现方法。它大大加快了处理速度,提高了控制精度。

关键词:FPGA;SVPWM;多轴控制;死区

中图分类号:TM34

1.引言

SVPWM 从交流电机角度出发,控制开关,形成 PWM 波,使电机中产生的实际磁链

矢量逼近跟踪定子磁链给定的理想圆型磁链。这样它能明显减小逆变器输出电流的谐波成分

及电动机的谐波损耗、降低脉动转矩。并且其控制简单,数字化方便,电压利用率高,已经

成为现在电流调速中的主流发展方向。

目前实现 SVPWM 的算法是使用电机控制专用 DSP,例如 TI 公司的 TMS320F2812 或

AD 公司的 ADMC 系列,但这些控制器只能产生 6 路或 12 路得 PWM 信号,不能满足多轴

控制的需要,如果控制多轴系统需要增加 DSP 的数量,是结构复杂,成本提高。

结合 FPGA 处理速度快、I/O 接口丰富的特点[1],本文提出了一种基于 FPGA 的 SVPWM

的实现方法。它大大加快了处理速度,提高了控制精度。且当需要实现多轴控制时,它可以

输出多路的 PWM 波,简化控制系统机构,降低控制器成本[2]。

2.SVPWM 原理及 FPGA 实现方法

2.1.SVPWM 原理[3]

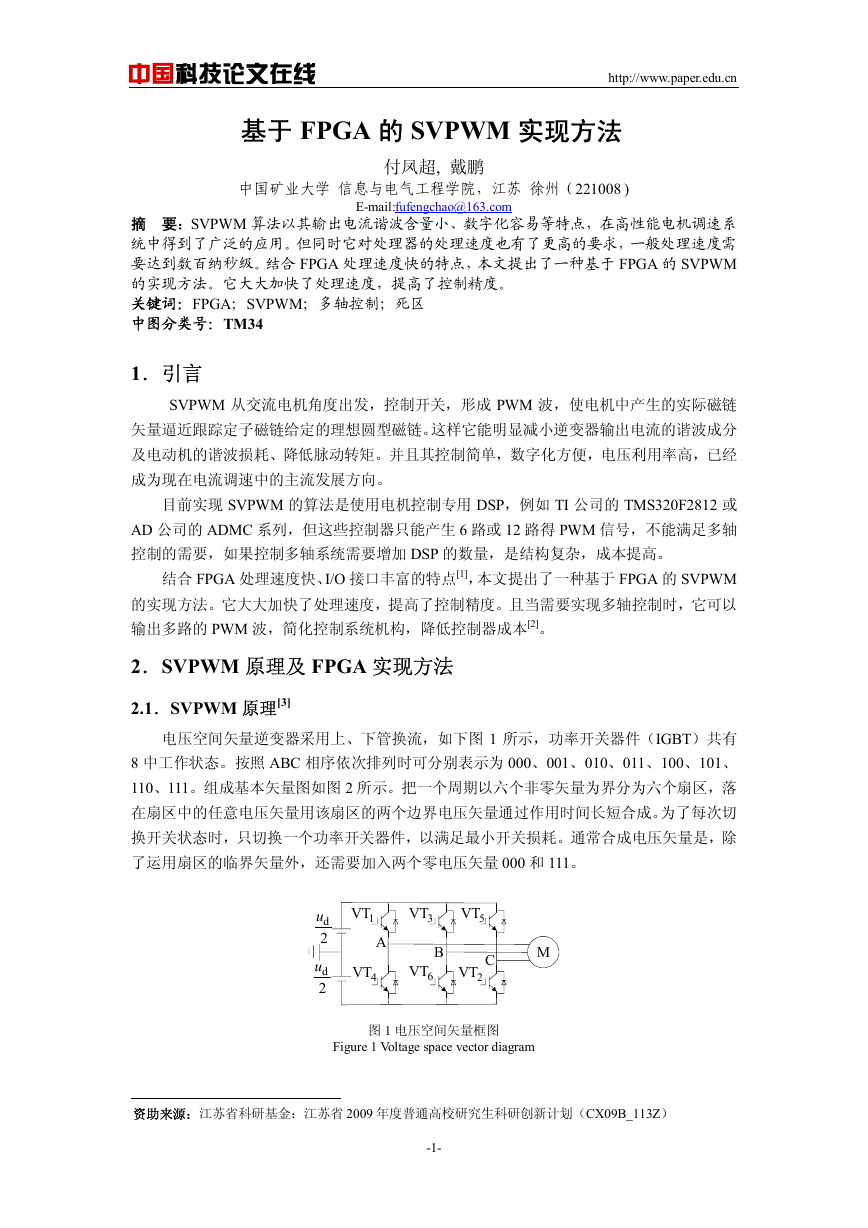

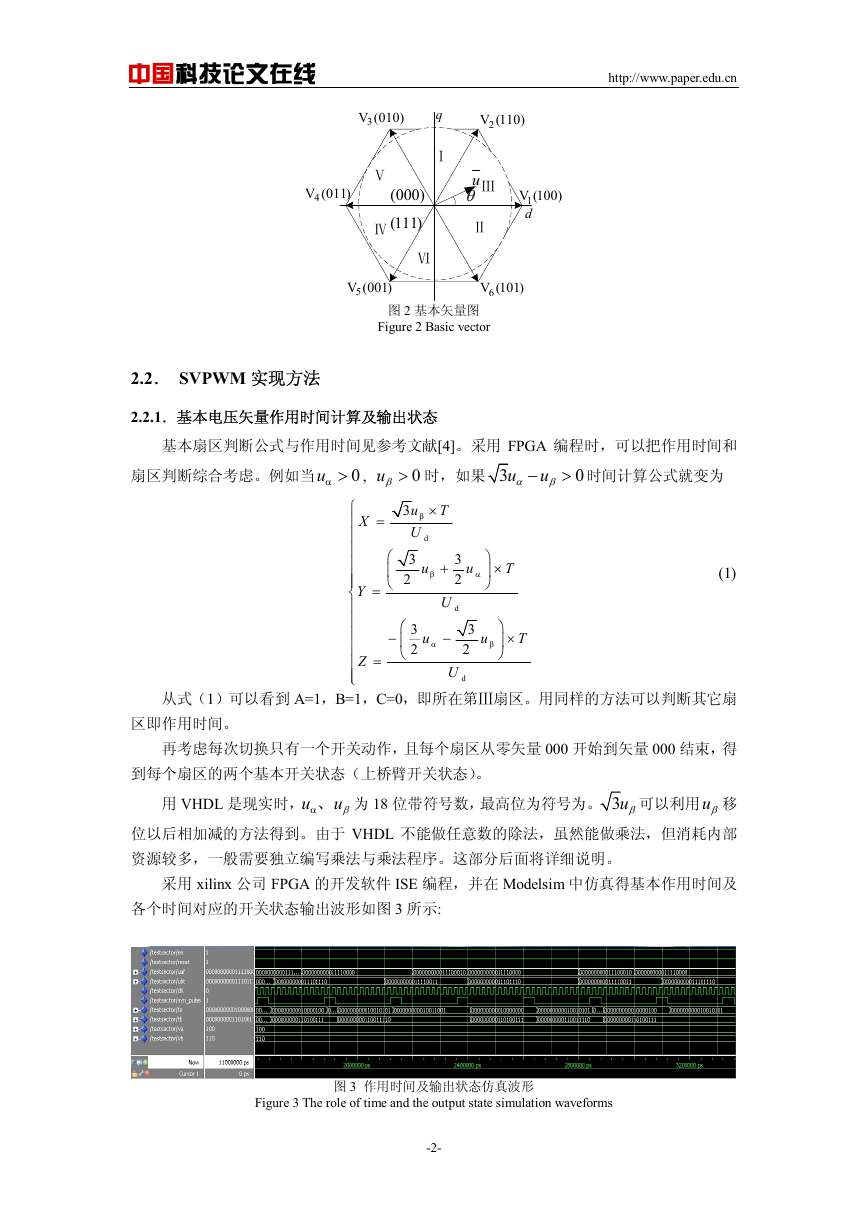

电压空间矢量逆变器采用上、下管换流,如下图 1 所示,功率开关器件(IGBT)共有

8 中工作状态。按照 ABC 相序依次排列时可分别表示为 000、001、010、011、100、101、

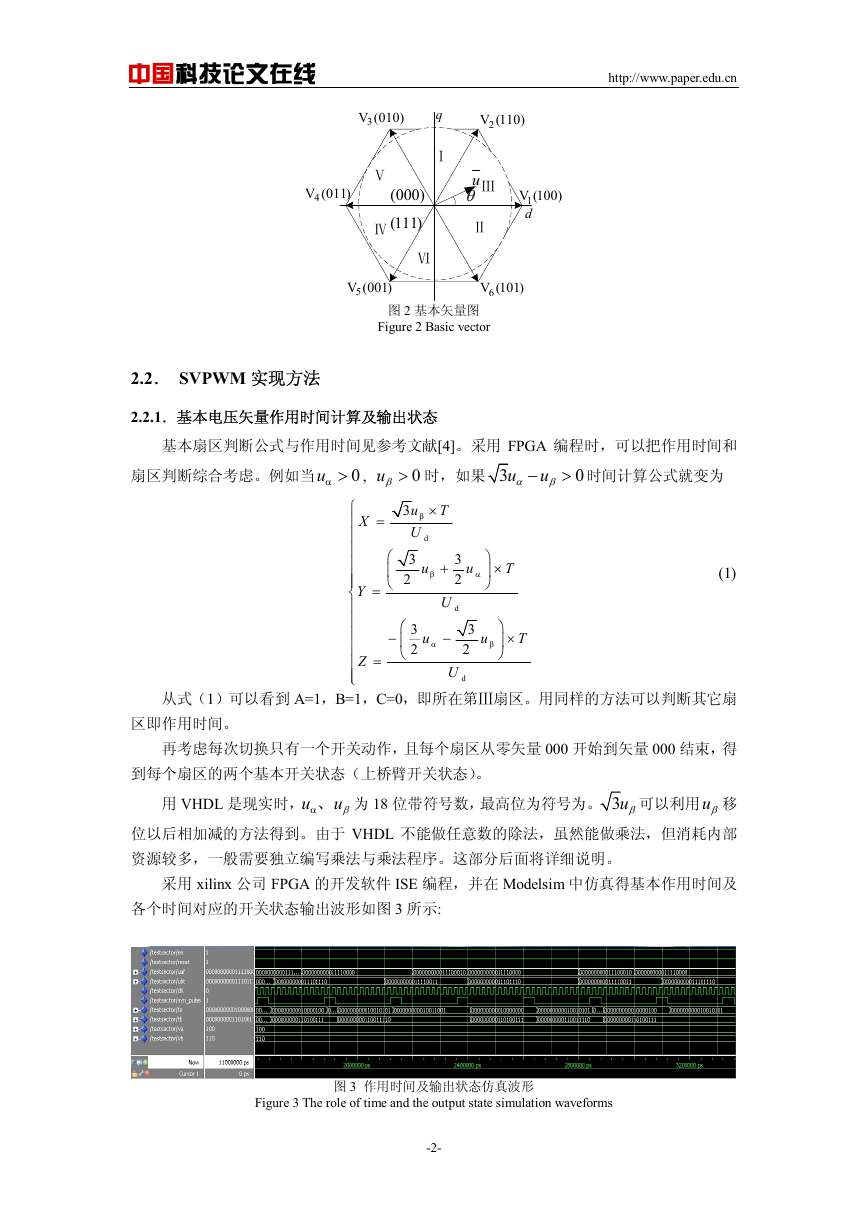

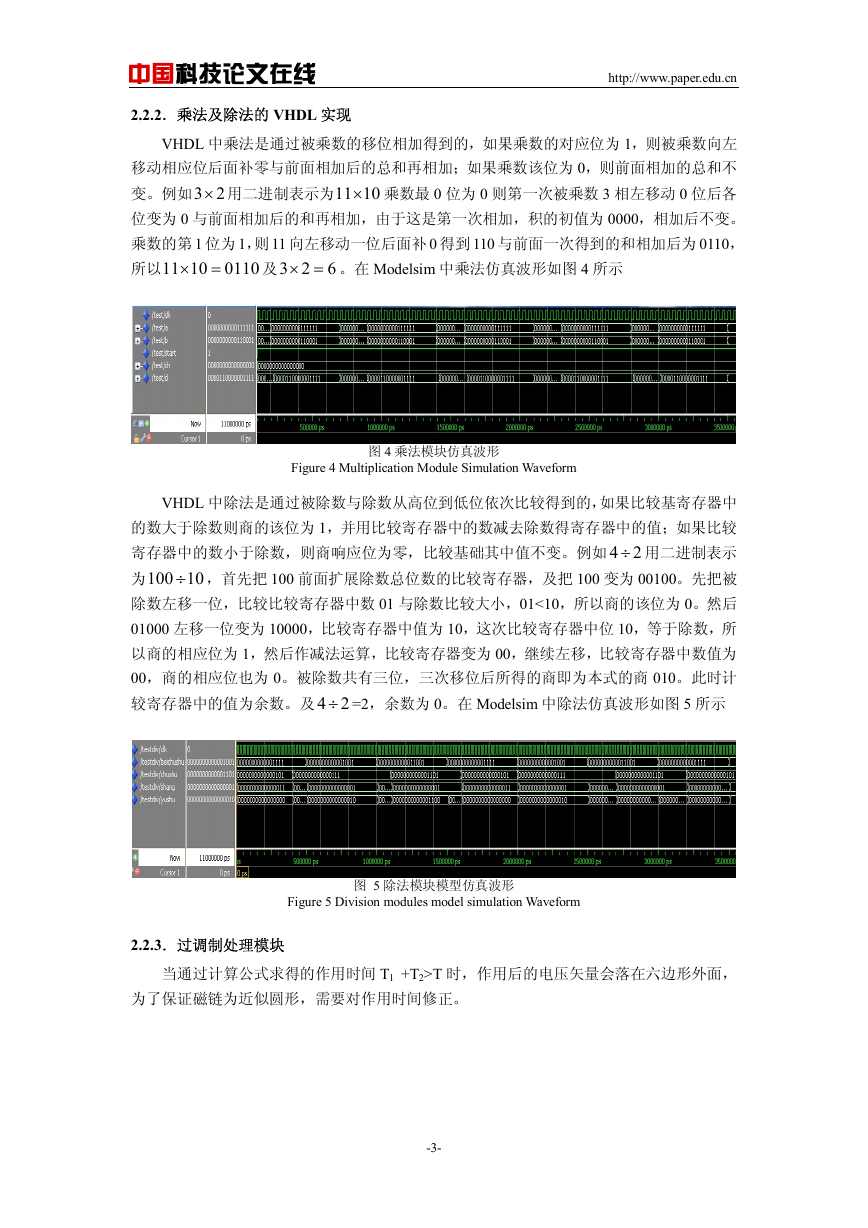

110、111。组成基本矢量图如图 2 所示。把一个周期以六个非零矢量为界分为六个扇区,落

在扇区中的任意电压矢量用该扇区的两个边界电压矢量通过作用时间长短合成。为了每次切

换开关状态时,只切换一个功率开关器件,以满足最小开关损耗。通常合成电压矢量是,除

了运用扇区的临界矢量外,还需要加入两个零电压矢量 000 和 111。

1VT

A

4VT

3VT

5VT

B

6VT

C

2VT

u

d

2

u

d

2

图 1 电压空间矢量框图

Figure 1 Voltage space vector diagram

M

资助来源:江苏省科研基金:江苏省 2009 年度普通高校研究生科研创新计划(CX09B_113Z)

-1-

�

中国科技论文在线

http://www.paper.edu.cn

3V (010)

q

Ⅰ

Ⅴ

Ⅳ

(000)

(111)

Ⅵ

2V (110)

u

θ

Ⅲ

Ⅱ

1V (100)

d

4V (011)

5V (001)

6V (101)

图 2 基本矢量图

Figure 2 Basic vector

2.2. SVPWM 实现方法

2.2.1.基本电压矢量作用时间计算及输出状态

基本扇区判断公式与作用时间见参考文献[4]。采用 FPGA 编程时,可以把作用时间和

> 时间计算公式就变为

uα

u

uβ > 时,如果 3

β−

uα > ,

0

扇区判断综合考虑。例如当

0

0

X

=

⎛

⎜

⎝

Y

=

×

T

d

3

u

β

U

3

2

u

u

α

⎞

⎟

⎠

×

T

3

2

d

+

β

U

(1)

−

3

2

⎛

⎜

⎝

Z

=

u

α

−

3

2

u

β

U

d

×

T

⎞

⎟

⎠

⎧

⎪

⎪

⎪

⎪

⎪⎪

⎨

⎪

⎪

⎪

⎪

⎪

⎪⎩

从式(1)可以看到 A=1,B=1,C=0,即所在第Ⅲ扇区。用同样的方法可以判断其它扇

区即作用时间。

再考虑每次切换只有一个开关动作,且每个扇区从零矢量 000 开始到矢量 000 结束,得

到每个扇区的两个基本开关状态(上桥臂开关状态)。

用 VHDL 是现实时,u

α、 为 18 位带符号数,最高位为符号为。 3uβ可以利用uβ 移

位以后相加减的方法得到。由于 VHDL 不能做任意数的除法,虽然能做乘法,但消耗内部

资源较多,一般需要独立编写乘法与乘法程序。这部分后面将详细说明。

uβ

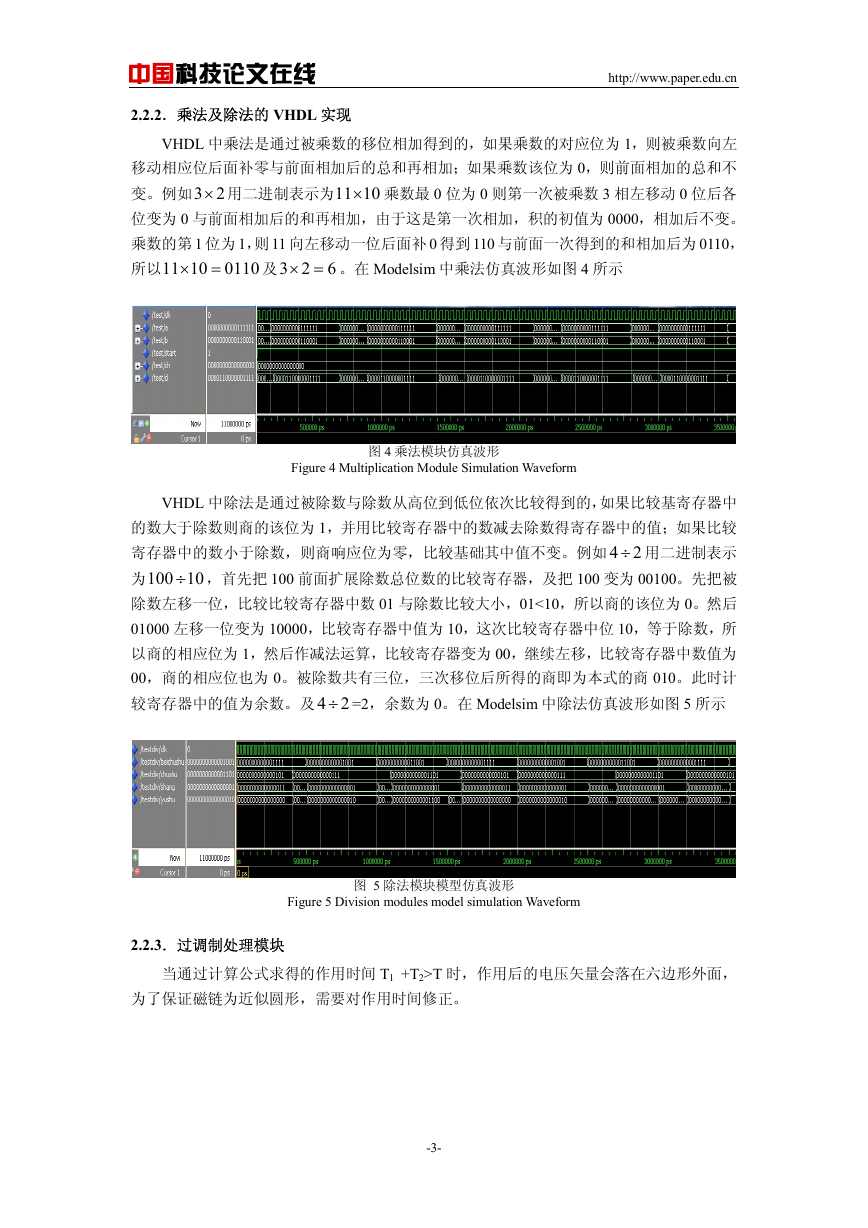

采用 xilinx 公司 FPGA 的开发软件 ISE 编程,并在 Modelsim 中仿真得基本作用时间及

各个时间对应的开关状态输出波形如图 3 所示:

图 3 作用时间及输出状态仿真波形

Figure 3 The role of time and the output state simulation waveforms

-2-

�

中国科技论文在线

2.2.2.乘法及除法的 VHDL 实现

http://www.paper.edu.cn

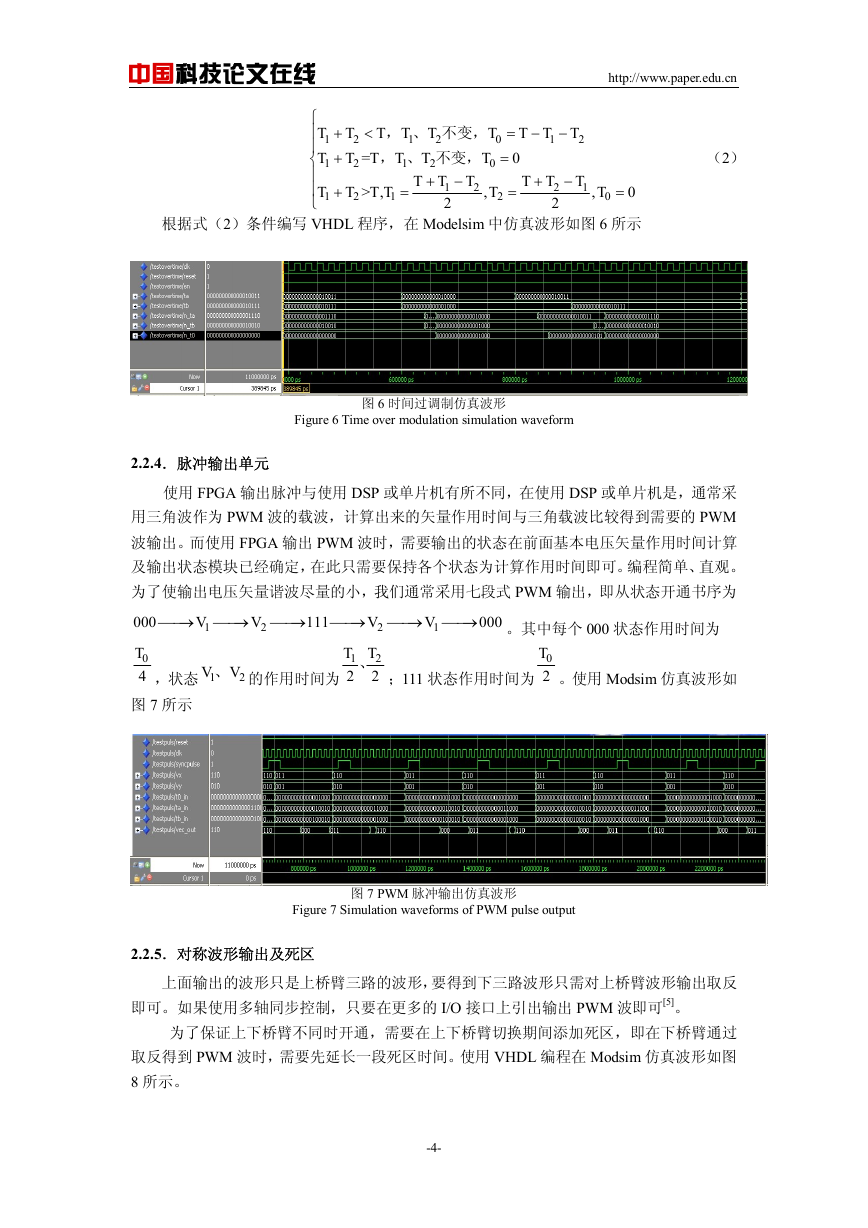

VHDL 中乘法是通过被乘数的移位相加得到的,如果乘数的对应位为 1,则被乘数向左

移动相应位后面补零与前面相加后的总和再相加;如果乘数该位为 0,则前面相加的总和不

变。例如3 2× 用二进制表示为11 10× 乘数最 0 位为 0 则第一次被乘数 3 相左移动 0 位后各

位变为 0 与前面相加后的和再相加,由于这是第一次相加,积的初值为 0000,相加后不变。

乘数的第 1 位为 1,则 11 向左移动一位后面补 0 得到 110 与前面一次得到的和相加后为 0110,

所以11 10 0110

× = 。在 Modelsim 中乘法仿真波形如图 4 所示

及3 2 6

×

=

图 4 乘法模块仿真波形

Figure 4 Multiplication Module Simulation Waveform

VHDL 中除法是通过被除数与除数从高位到低位依次比较得到的,如果比较基寄存器中

的数大于除数则商的该位为 1,并用比较寄存器中的数减去除数得寄存器中的值;如果比较

寄存器中的数小于除数,则商响应位为零,比较基础其中值不变。例如 4 2÷ 用二进制表示

为100 10÷ ,首先把 100 前面扩展除数总位数的比较寄存器,及把 100 变为 00100。先把被

除数左移一位,比较比较寄存器中数 01 与除数比较大小,01<10,所以商的该位为 0。然后

01000 左移一位变为 10000,比较寄存器中值为 10,这次比较寄存器中位 10,等于除数,所

以商的相应位为 1,然后作减法运算,比较寄存器变为 00,继续左移,比较寄存器中数值为

00,商的相应位也为 0。被除数共有三位,三次移位后所得的商即为本式的商 010。此时计

较寄存器中的值为余数。及 4 2÷ =2,余数为 0。在 Modelsim 中除法仿真波形如图 5 所示

图 5 除法模块模型仿真波形

Figure 5 Division modules model simulation Waveform

2.2.3.过调制处理模块

当通过计算公式求得的作用时间 T1 +T2>T 时,作用后的电压矢量会落在六边形外面,

为了保证磁链为近似圆形,需要对作用时间修正。

-3-

�

中国科技论文在线

http://www.paper.edu.cn

<

⎧

T T T

T T

T

T T T

⎪ +

= −

, 、 不变,

0

2

1

2

2

⎪

0

T

T T =T T T

=

+

, 、 不变,

⎨

2

0

1

⎪

T T T

+

2

⎪ +

T T >T,T

1

1

⎩

T T

2

2

,T

2

1

2

−

−

+

−

=

=

2

2

1

1

1

(2)

,T

0

=

0

T

1

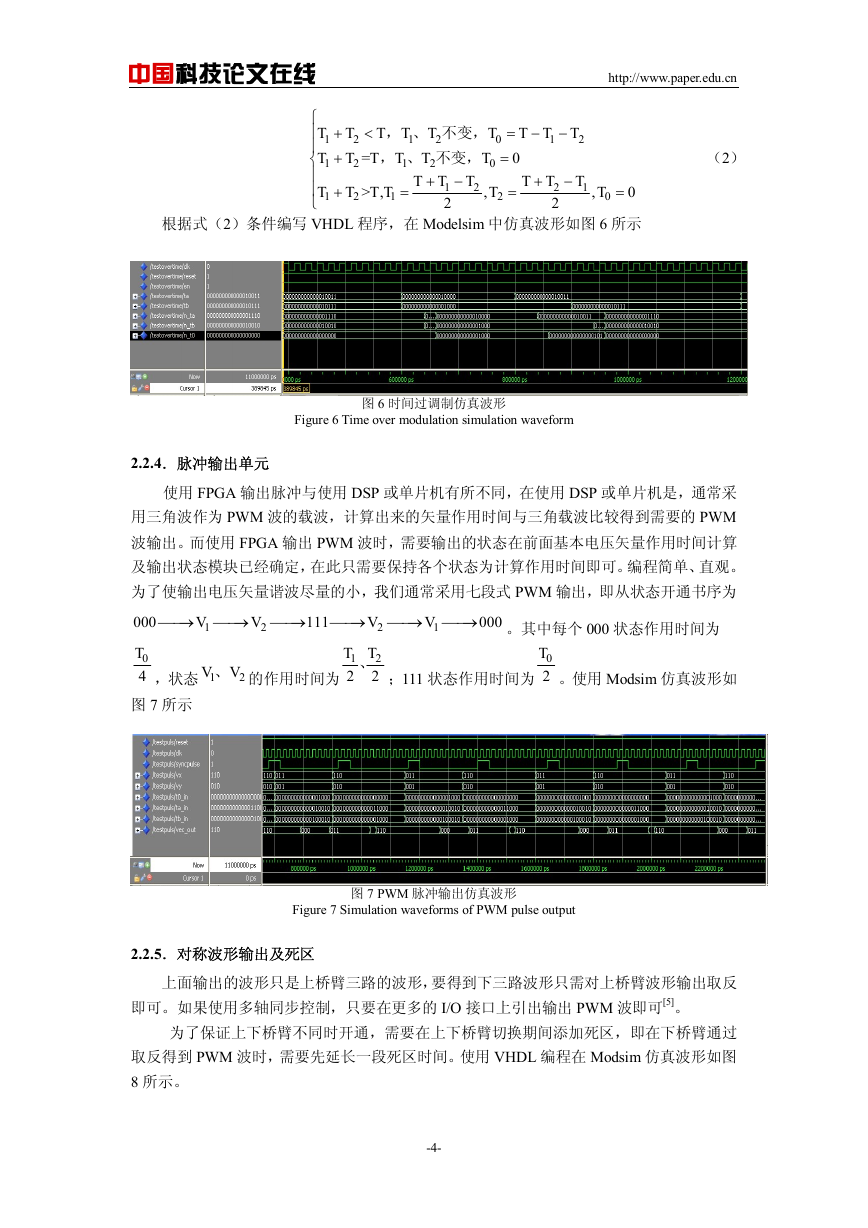

根据式(2)条件编写 VHDL 程序,在 Modelsim 中仿真波形如图 6 所示

图 6 时间过调制仿真波形

Figure 6 Time over modulation simulation waveform

2.2.4.脉冲输出单元

使用 FPGA 输出脉冲与使用 DSP 或单片机有所不同,在使用 DSP 或单片机是,通常采

用三角波作为 PWM 波的载波,计算出来的矢量作用时间与三角载波比较得到需要的 PWM

波输出。而使用 FPGA 输出 PWM 波时,需要输出的状态在前面基本电压矢量作用时间计算

及输出状态模块已经确定,在此只需要保持各个状态为计算作用时间即可。编程简单、直观。

为了使输出电压矢量谐波尽量的小,我们通常采用七段式 PWM 输出,即从状态开通书序为

000

0T

4 ,状态 1

图 7 所示

⎯⎯→ ⎯⎯→ ⎯⎯→ ⎯⎯→ ⎯⎯→ ⎯⎯→ 。其中每个 000 状态作用时间为

0T

2 。使用 Modsim 仿真波形如

V V、 的作用时间为

;111 状态作用时间为

T T

2

1

、

2

2

000

111

V

2

V

2

V

1

V

1

2

图 7 PWM 脉冲输出仿真波形

Figure 7 Simulation waveforms of PWM pulse output

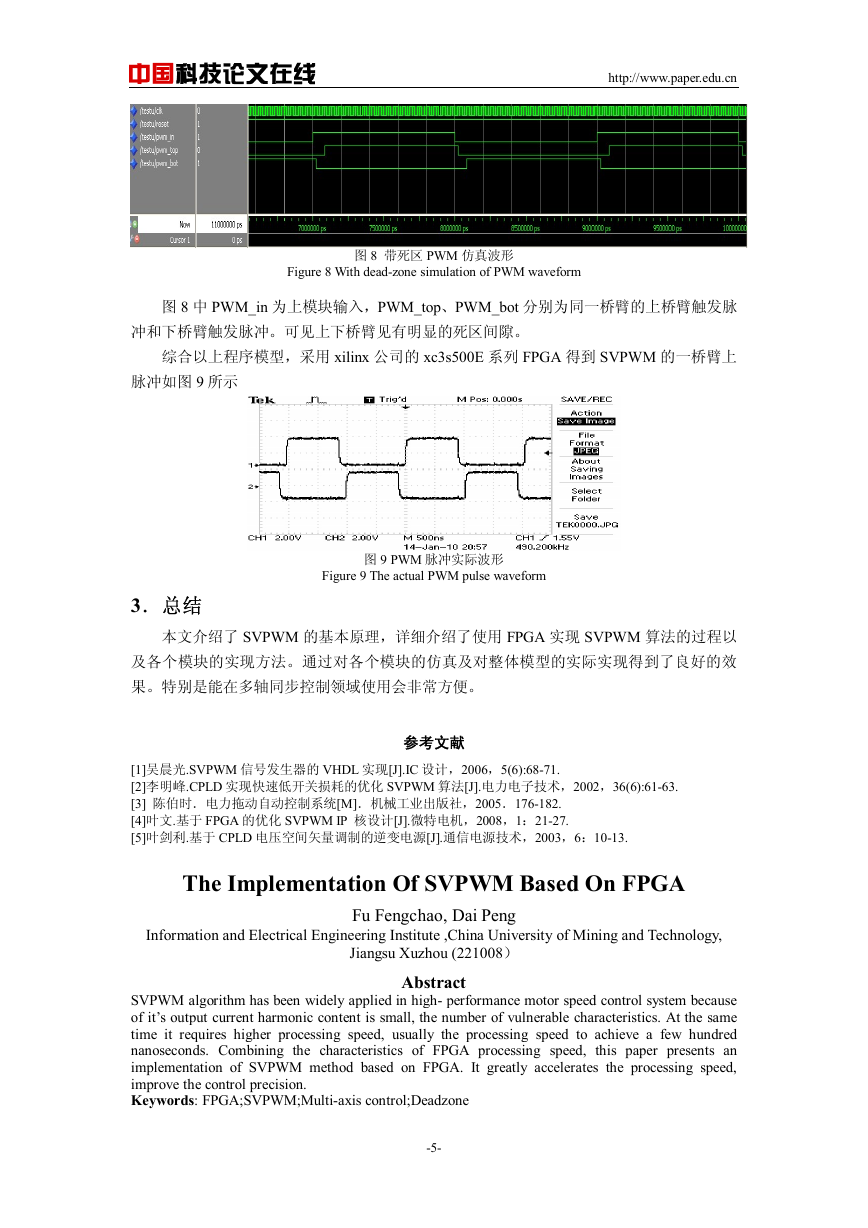

2.2.5.对称波形输出及死区

上面输出的波形只是上桥臂三路的波形,要得到下三路波形只需对上桥臂波形输出取反

即可。如果使用多轴同步控制,只要在更多的 I/O 接口上引出输出 PWM 波即可[5]。

为了保证上下桥臂不同时开通,需要在上下桥臂切换期间添加死区,即在下桥臂通过

取反得到 PWM 波时,需要先延长一段死区时间。使用 VHDL 编程在 Modsim 仿真波形如图

8 所示。

-4-

�

中国科技论文在线

http://www.paper.edu.cn

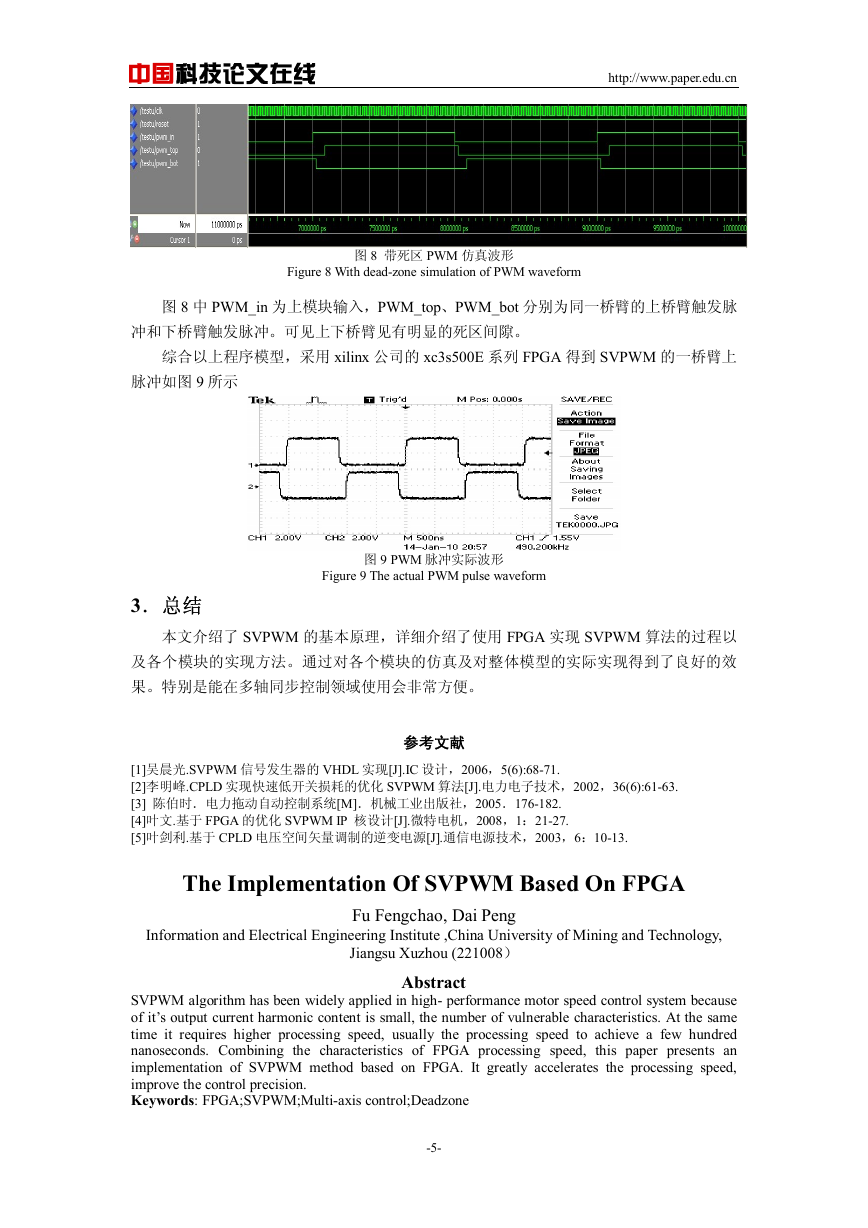

图 8 带死区 PWM 仿真波形

Figure 8 With dead-zone simulation of PWM waveform

图 8 中 PWM_in 为上模块输入,PWM_top、PWM_bot 分别为同一桥臂的上桥臂触发脉

冲和下桥臂触发脉冲。可见上下桥臂见有明显的死区间隙。

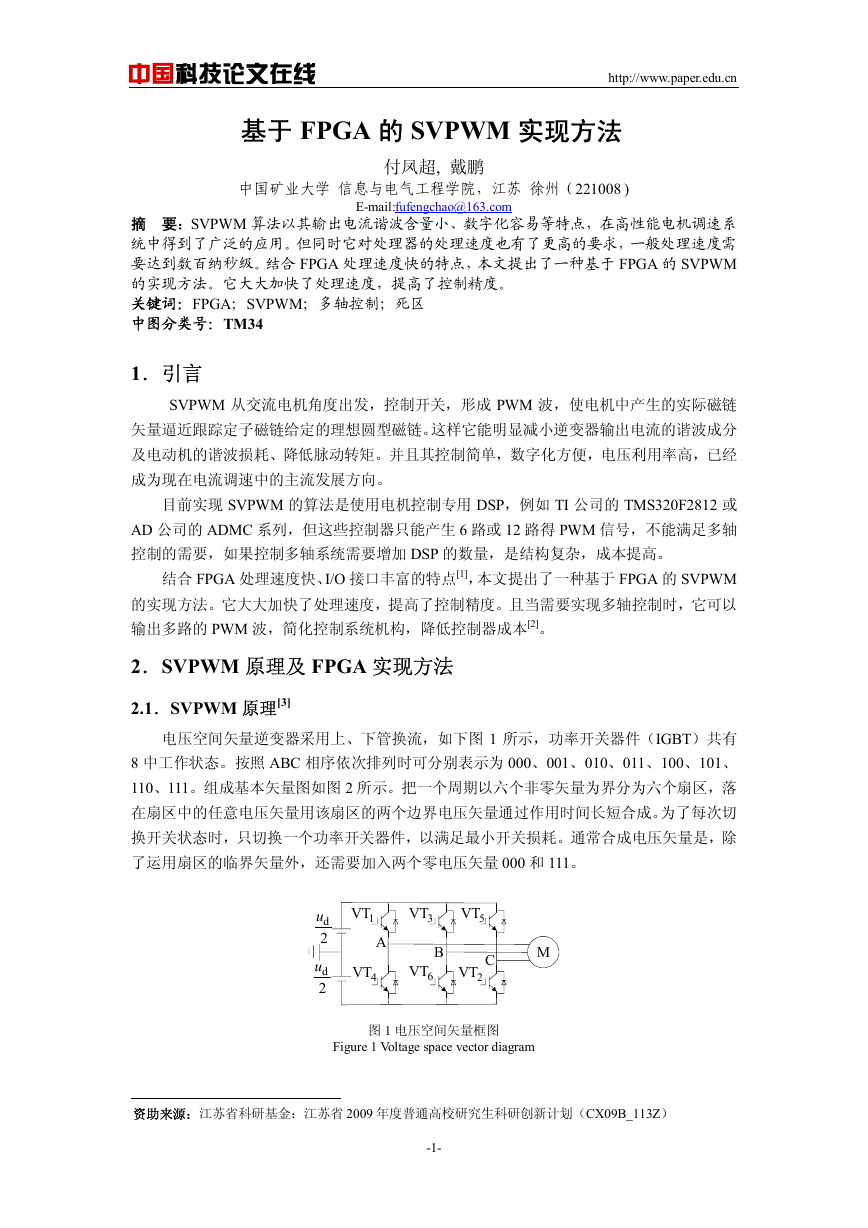

综合以上程序模型,采用 xilinx 公司的 xc3s500E 系列 FPGA 得到 SVPWM 的一桥臂上

脉冲如图 9 所示

图 9 PWM 脉冲实际波形

Figure 9 The actual PWM pulse waveform

3.总结

本文介绍了 SVPWM 的基本原理,详细介绍了使用 FPGA 实现 SVPWM 算法的过程以

及各个模块的实现方法。通过对各个模块的仿真及对整体模型的实际实现得到了良好的效

果。特别是能在多轴同步控制领域使用会非常方便。

参考文献

[1]吴晨光.SVPWM 信号发生器的 VHDL 实现[J].IC 设计,2006,5(6):68-71.

[2]李明峰.CPLD 实现快速低开关损耗的优化 SVPWM 算法[J].电力电子技术,2002,36(6):61-63.

[3] 陈伯时.电力拖动自动控制系统[M].机械工业出版社,2005.176-182.

[4]叶文.基于 FPGA 的优化 SVPWM IP 核设计[J].微特电机,2008,1:21-27.

[5]叶剑利.基于 CPLD 电压空间矢量调制的逆变电源[J].通信电源技术,2003,6:10-13.

The Implementation Of SVPWM Based On FPGA

Information and Electrical Engineering Institute ,China University of Mining and Technology,

Fu Fengchao, Dai Peng

Jiangsu Xuzhou (221008)

Abstract

SVPWM algorithm has been widely applied in high- performance motor speed control system because

of it’s output current harmonic content is small, the number of vulnerable characteristics. At the same

time it requires higher processing speed, usually the processing speed to achieve a few hundred

nanoseconds. Combining the characteristics of FPGA processing speed, this paper presents an

implementation of SVPWM method based on FPGA. It greatly accelerates the processing speed,

improve the control precision.

Keywords: FPGA;SVPWM;Multi-axis control;Deadzone

-5-

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc