NiosIIPIO 的说明与双向操作注意点

最近想使用 NiosII 里的并口 PIO 口进行双向操作,即需要输出的时候设置为输出方向,

需要输入的时候设置为输入方向。在这期间,因为没认真仔细阅读参考文档,走了一点点的

弯路。下面就简单的介绍下并行输入/输出 PIO。

PIO 核概述

具有 Avalon 接口的并行输入/输出(parallelinput/output-PIO) 核,在 Avalon 存储器映射

(AvalonMemory-MappedAvalon-MM )从端口和通用 I/O 端口之间提供了一个存储器映射

接口。I/O 端口既可以连接片上用户逻辑,也可以连接到 FPGA 与外设连接的 I/O 引脚。

PIO 核提供容易的 I/O 访问用户逻辑或外部设备,在这种情况下 “位控制”的方法是有

效的。下面列举了几种应用的例子:

①控制 LED、②获取开关数据、③控制显示设备、④片外设备的配置与通信,例如特定应

用的标准产品(ASSP)。

功能描述

每个 PIO 核可以提供最多32个 I/O 端口。像微处理器这样的智能主机通过读/写寄存器

映射的 Avalon-MM 接口控制 PIO 端口。在主机控制下,PIO 核捕获输入端口的数据,并驱

动数据到输出端口。当 PIO 端口直接与 I/O 引脚相连时,主机通过写 PIO 核中的控制寄存

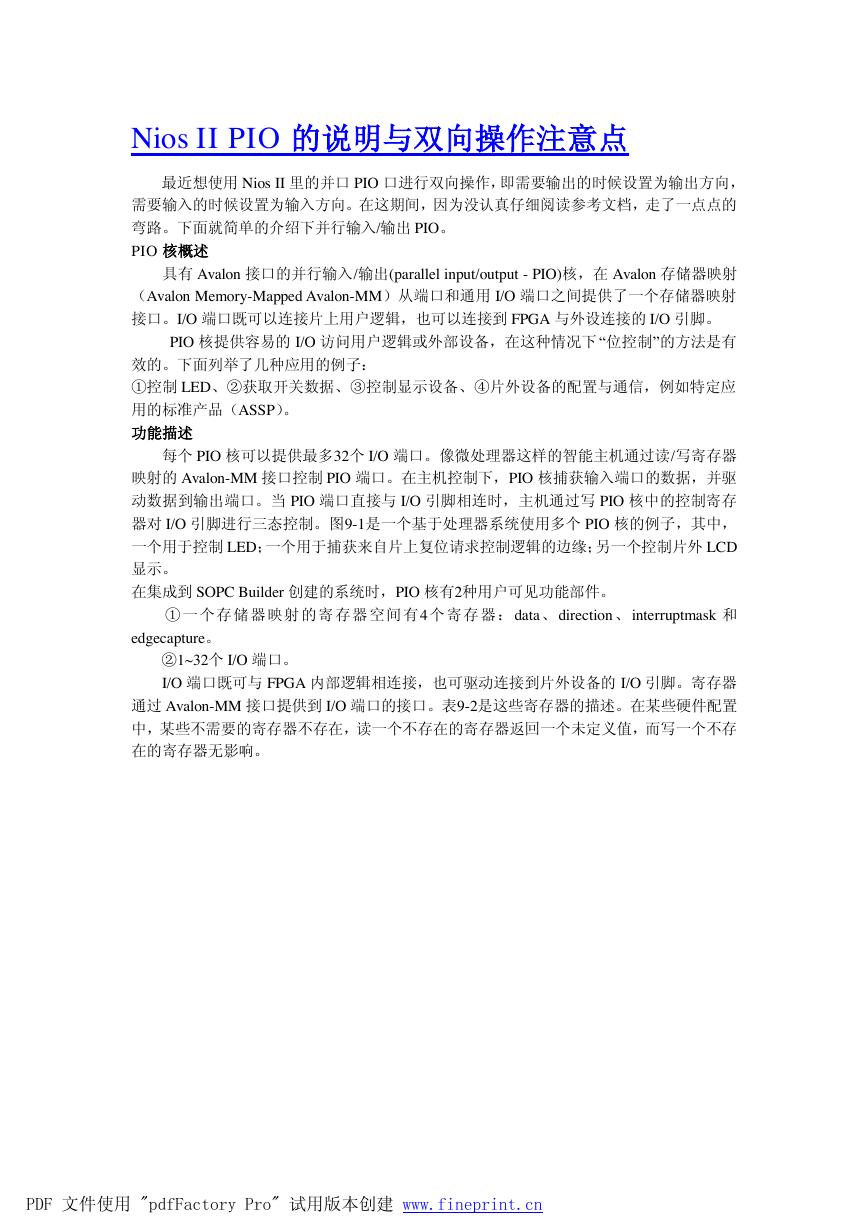

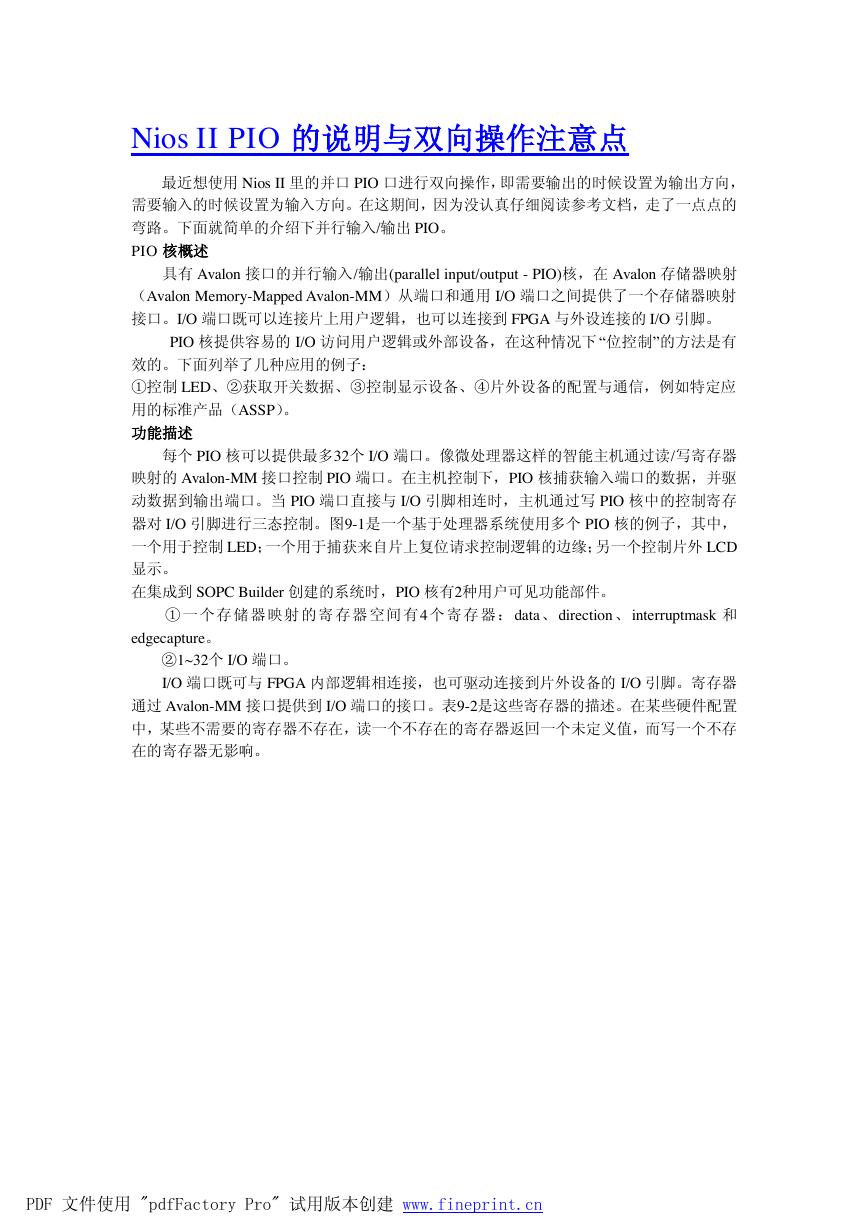

器对 I/O 引脚进行三态控制。图9-1是一个基于处理器系统使用多个 PIO 核的例子,其中,

一个用于控制 LED;一个用于捕获来自片上复位请求控制逻辑的边缘;另一个控制片外 LCD

显示。

在集成到 SOPCBuilder 创建的系统时,PIO 核有2种用户可见功能部件。

① 一个存储器映射 的 寄 存器 空间 有4 个 寄存 器:data、direction、interruptmask 和

edgecapture。

②1~32个 I/O 端口。

I/O 端口既可与 FPGA 内部逻辑相连接,也可驱动连接到片外设备的 I/O 引脚。寄存器

通过 Avalon-MM 接口提供到 I/O 端口的接口。表9-2是这些寄存器的描述。在某些硬件配置

中,某些不需要的寄存器不存在,读一个不存在的寄存器返回一个未定义值,而写一个不存

在的寄存器无影响。

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

�

图 使用多个 PIO 核的系统实例

数据输入/输出

PIO 核的 I/O 端口既可以连接片上逻辑也可以连接片外逻辑,PIO 核可以配置为输入、

输出或双向。若用来控制双向 I/O 引脚,则 PIO 核提供具有三态控制的双向模式。

读和写数据寄存器的硬件逻辑是独立的。读数据寄存器返回当前输入端口的值;写数据

寄存器影响驱动输出端口的值。由于这些端口是独立的,因此读数据寄存器并不返回上次写

入的数据。

边沿捕获

PIO 核可配置为对输入端口进行边沿捕获(EdgeCapture ),它可以捕获低到高的跳变、

高到低的跳变或者2种跳变均捕获。只要在输入端检测到边沿,该条件就会在 edgecapture 寄

存器中指示。边沿的检测类型在系统创建时指明,且不能通过寄存器进行更改。

IRQ 的产生

PIO 核可以配置为在不同的输入条件下产生 IRQ。IRQ 产生的条件可以是下面两种:

① Level-sensitive(电平检测) — PIO 核硬件能检测一个高电平,可在核的外部插入一

个“非”门来检测低电平。

② Edge-sensitive(边沿检测) — PIO 核的边沿捕获配置决定何种边沿类型能触发 IRQ。

每个输入端口的中断可以分别屏蔽,中断屏蔽决定哪一个输入端口能产生中断。

在 SOPCBuilder 中实例化 PIO 核

设计者在 SOPCBuilder 中使用 MegaWizard 向导来配置硬件特性设置。下面描述可用的

选项。

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

�

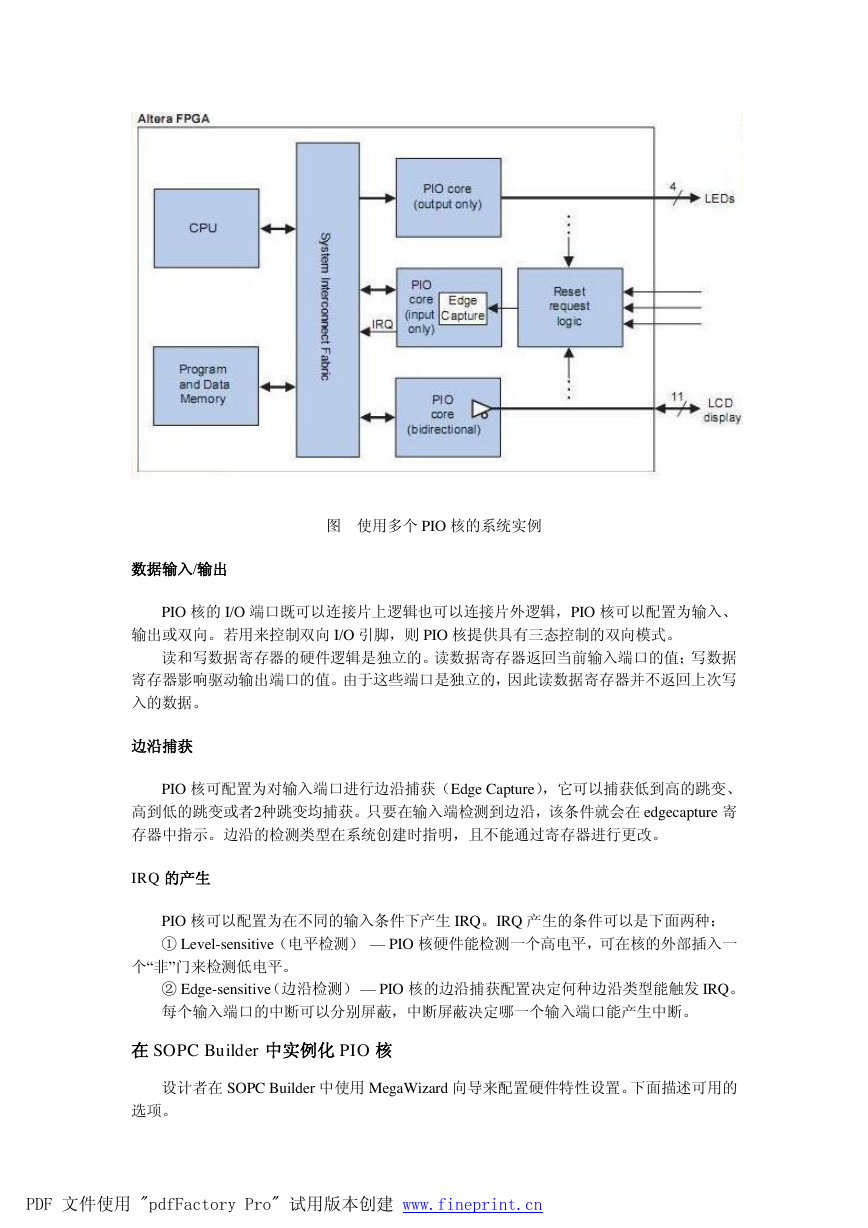

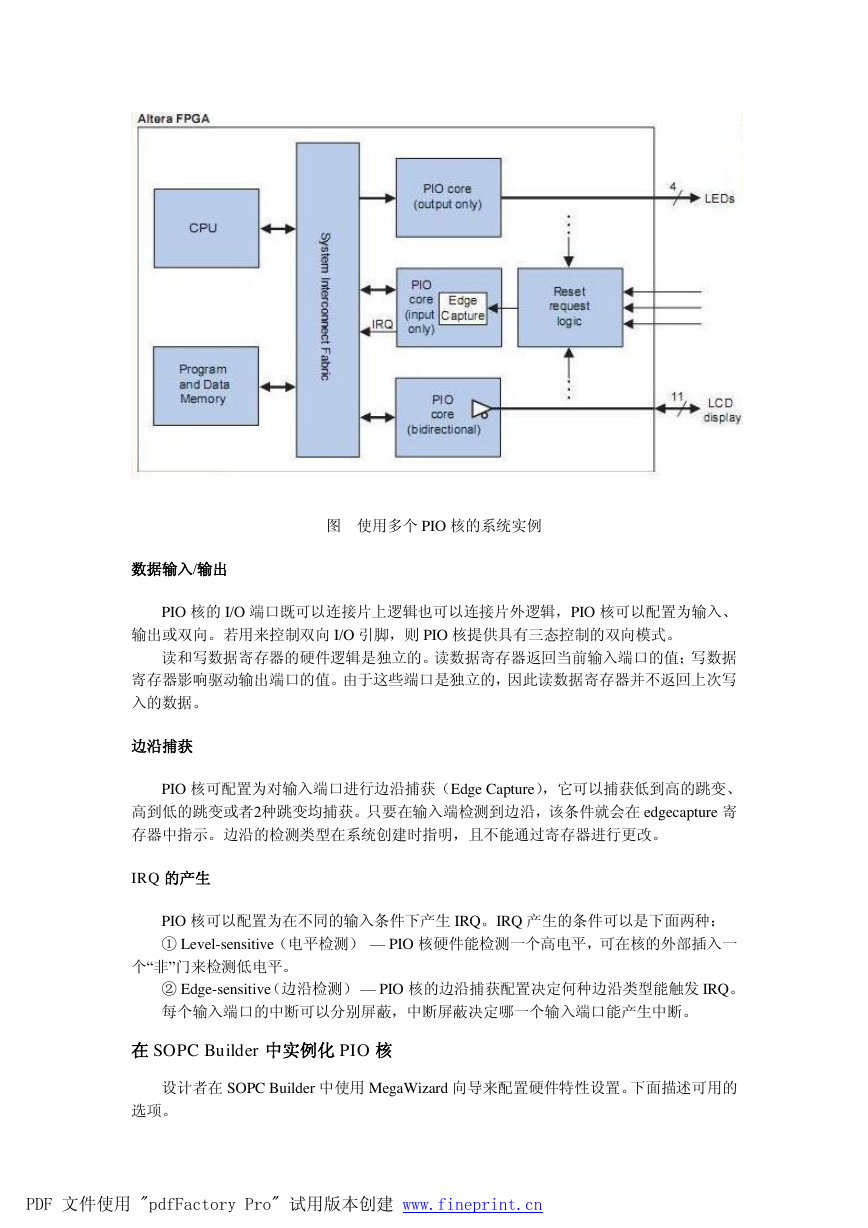

MegaWizard 向导有基本设置(BasicSettings )和输入选项(InputOptions )两个标签。

BasicSettings (基本设置)

BasicSettings (基本设置)标签页允许设计者指定 PIO 端口的宽度和方向。

① Width(宽度)设置可以是1~32之间的任何整数值。如果设定值为 n,则 I/O 端口宽

为 n 位。

② Direction(方向)设置有4个选项,如下表所示。

设 置

Bidirectional(tristate)ports

双向(三态)端口

Inputportsonly

输入端口

Bothinputandoutputports

输入/输出端口

Outputportsonly

输出端口

表 方向设置

描 述

在这种模式下,每个 PIO 位共享一个设备引脚用于驱动或捕获

数据。每个引脚的方向可以分别选择。如果设置 FPGAI/O 引

脚的方向为输入,引脚的状态为高阻三态。

在这种模式下,PIO 端口只能捕获输入。

在这种模式下,输入和输出端口总线是分开的,n 位宽的单向

总线。

在这种模式下,PIO 端口只能捕获输出。

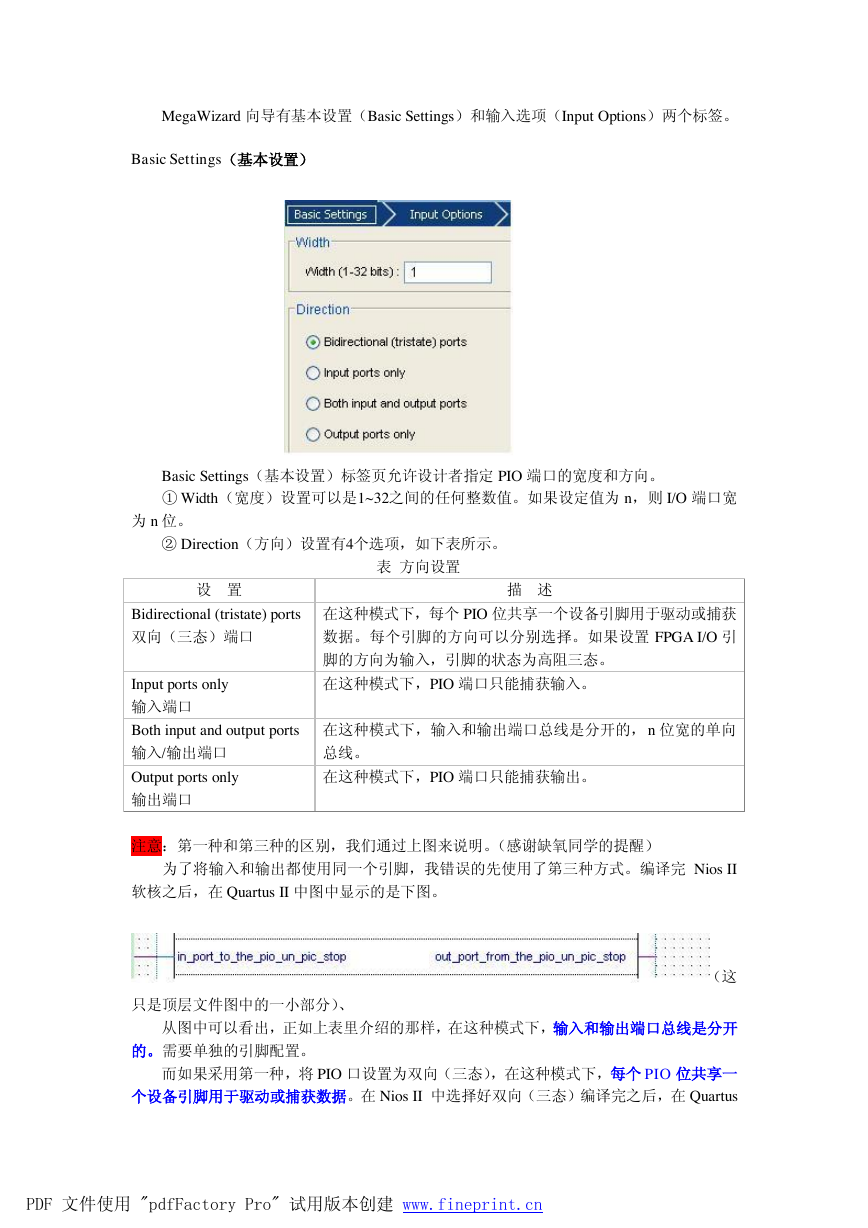

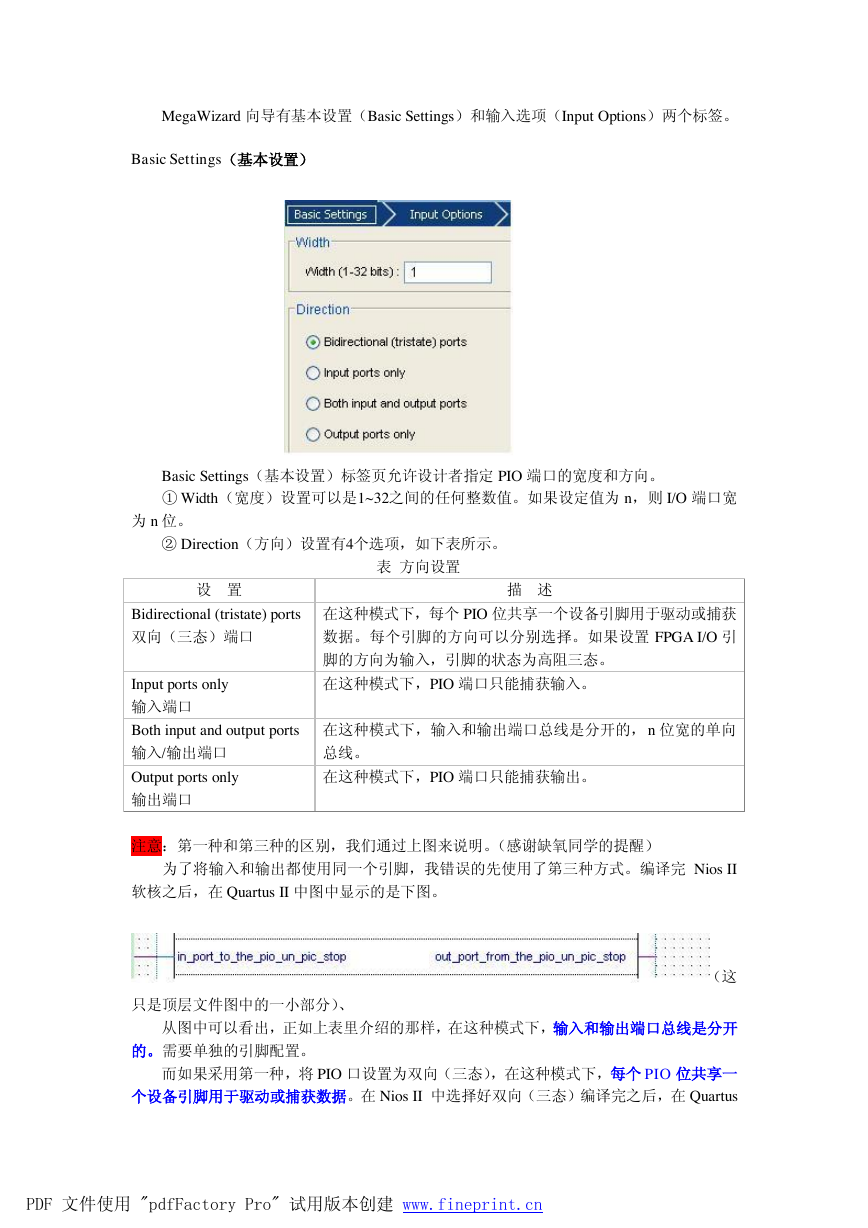

注意:第一种和第三种的区别,我们通过上图来说明。(感谢缺氧同学的提醒)

为了将输入和输出都使用同一个引脚,我错误的先使用了第三种方式。编译完 NiosII

软核之后,在 QuartusII 中图中显示的是下图。

只是顶层文件图中的一小部分)、

从图中可以看出,正如上表里介绍的那样,在这种模式下,输入和输出端口总线是分开

的。需要单独的引脚配置。

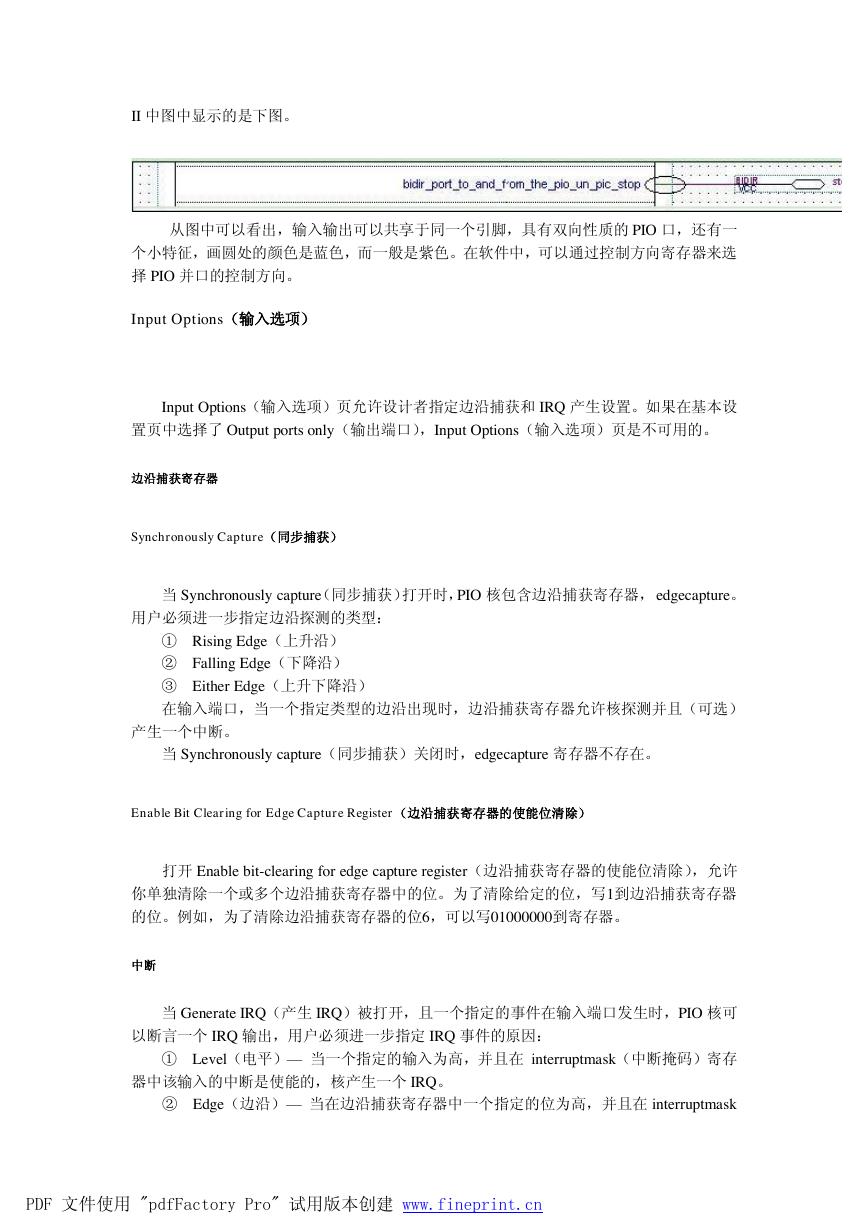

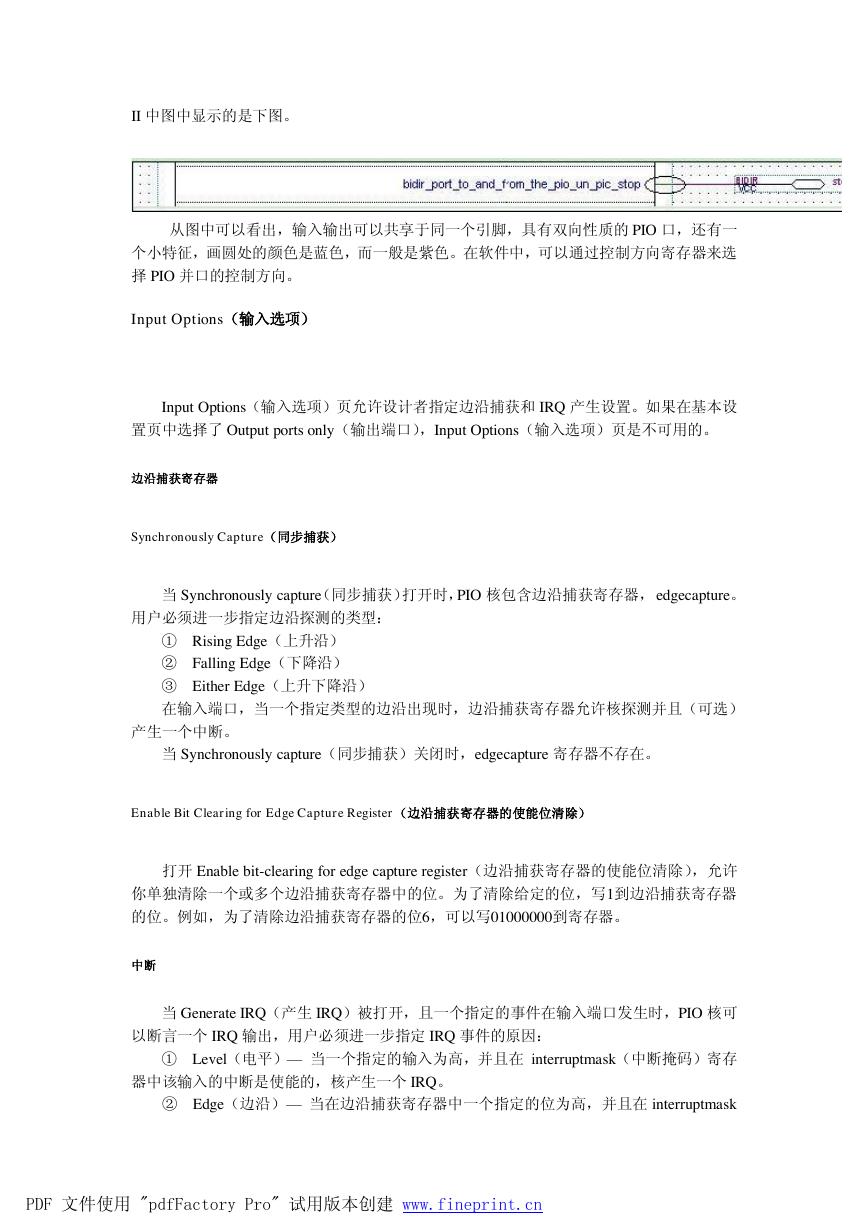

而如果采用第一种,将 PIO 口设置为双向(三态),在这种模式下,每个 PIO 位共享一

个设备引脚用于驱动或捕获数据。在 NiosII 中选择好双向(三态)编译完之后,在 Quartus

(这

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

�

II 中图中显示的是下图。

从图中可以看出,输入输出可以共享于同一个引脚,具有双向性质的 PIO 口,还有一

个小特征,画圆处的颜色是蓝色,而一般是紫色。在软件中,可以通过控制方向寄存器来选

择 PIO 并口的控制方向。

InputOptions (输入选项)

InputOptions (输入选项)页允许设计者指定边沿捕获和 IRQ 产生设置。如果在基本设

置页中选择了 Outputportsonly (输出端口),InputOptions (输入选项)页是不可用的。

边沿捕获寄存器

SynchronouslyCapture (同步捕获)

当 Synchronouslycapture(同步捕获)打开时,PIO 核包含边沿捕获寄存器,edgecapture。

用户必须进一步指定边沿探测的类型:

① RisingEdge (上升沿)

② FallingEdge (下降沿)

③ EitherEdge (上升下降沿)

在输入端口,当一个指定类型的边沿出现时,边沿捕获寄存器允许核探测并且(可选)

产生一个中断。

当 Synchronouslycapture (同步捕获)关闭时,edgecapture 寄存器不存在。

EnableBitClearingforEdgeCaptureRegister (边沿捕获寄存器的使能位清除)

打开 Enablebit-clearingforedgecaptureregister (边沿捕获寄存器的使能位清除),允许

你单独清除一个或多个边沿捕获寄存器中的位。为了清除给定的位,写1到边沿捕获寄存器

的位。例如,为了清除边沿捕获寄存器的位6,可以写01000000到寄存器。

中断

当 GenerateIRQ (产生 IRQ)被打开,且一个指定的事件在输入端口发生时,PIO 核可

以断言一个 IRQ 输出,用户必须进一步指定 IRQ 事件的原因:

① Level(电平)— 当一个指定的输入为高,并且在 interruptmask(中断掩码)寄存

器中该输入的中断是使能的,核产生一个 IRQ。

② Edge(边沿)— 当在边沿捕获寄存器中一个指定的位为高,并且在 interruptmask

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

�

(中断掩码)寄存器中该位的中断是使能的,核产生一个 IRQ。

当 GenerateIRQ (产生 IRQ)关闭时,interruptmask 寄存器不存在。

今天的学习就到这里了。

PDF 文件使用 "pdfFactory Pro" 试用版本创建 www.fineprint.cn

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc