1. 按照半导体集成电路的集成度来分,分为哪些类型?

小规模集成电路 (SSI)、中规模集成电路 (MSI)、大规模集成电路 (LSI)、

超大规模集成电路 (VLSI)、特大规模集成电路 (ULSI)、巨大规模集成电路

(GSI)。

2. 按照器件类型分,半导体集成电路分为哪几类?

BJT 型、MOS 型、Bi-CMOS 型

3. 按电路功能或信号类型分,半导体集成电路分为哪几类?

数字集成电路、模拟集成电路、数模混合集成电路

4. 电离后向半导体提供空穴的杂质是受主杂质,电离后向半导体提供电子的杂

质是施主杂质。

5. 由于载流子存在浓度梯度而产生的电流是扩散电流,由于载流子在一定电场

力的作用下而产生电流是漂移电流。

6. 在热力学温度零度时,能量比 FE 小的量子态被电子占据的概率为 100%,如

果温度大于热力学温度零度时,能量比 FE 小的量子态被电子占据的概率为大

于 50%。

7. 费米分布函数适用于简并的电子系统,波耳兹曼分布函数适用于非简并的电

子系统。

8. 热平衡状态下,无论本征半导体还是杂质半导体,其电子浓度和空穴浓度的

乘积为常数,由温度和禁带宽度决定。

9. 一块半导体材料,光照在材料中会产生非平衡载流子,其中非平衡载流子的

寿命为τ。若光照忽然停止,经过τ时间后,非平衡载流子衰减为原来的 1/e。

10. 在一定温度下,光照在半导体材料中会产生非平衡载流子,光照稳定后,半

导体的热平衡状态被打破,将没有统一的费米能级,但导带和价带处于各自

的平衡态,因此存在导带费米能级和价带费米能级,称其为“准费米能级”。

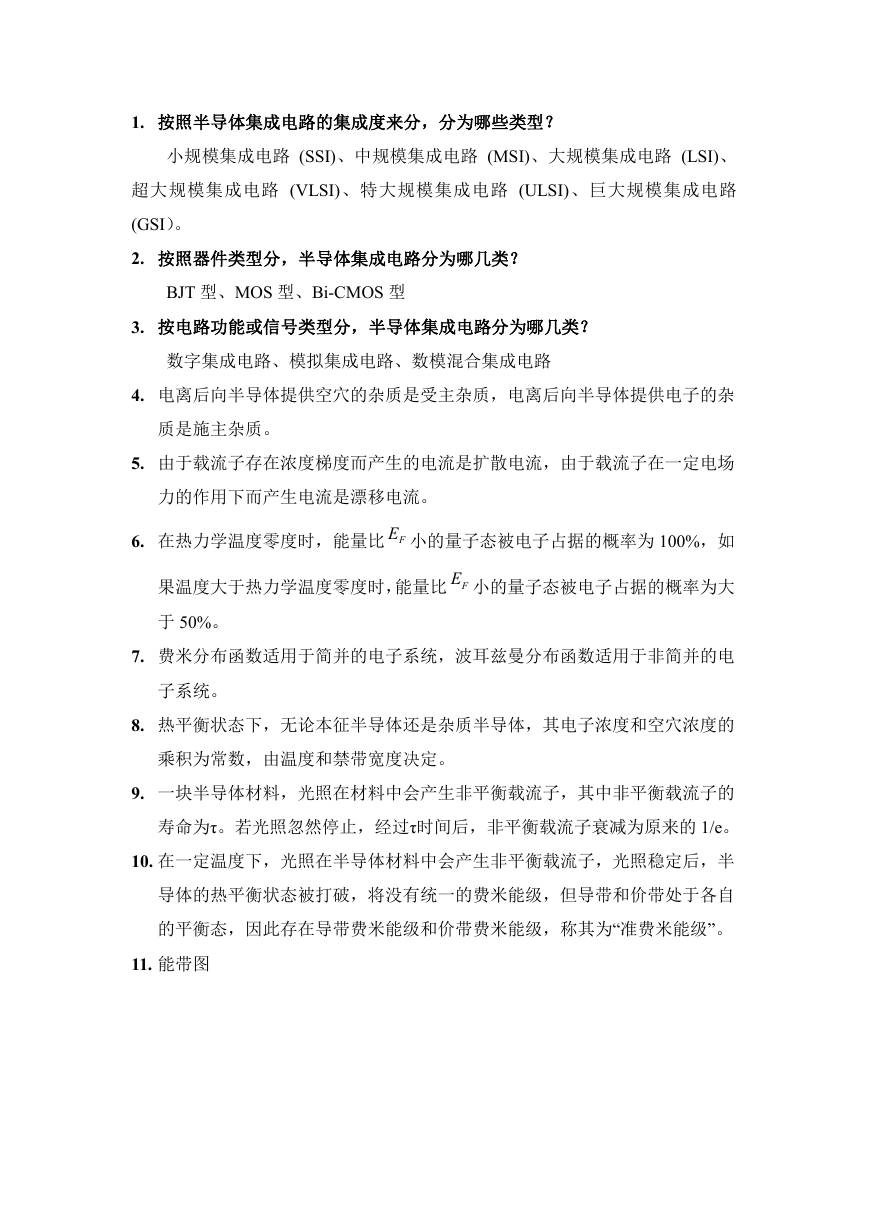

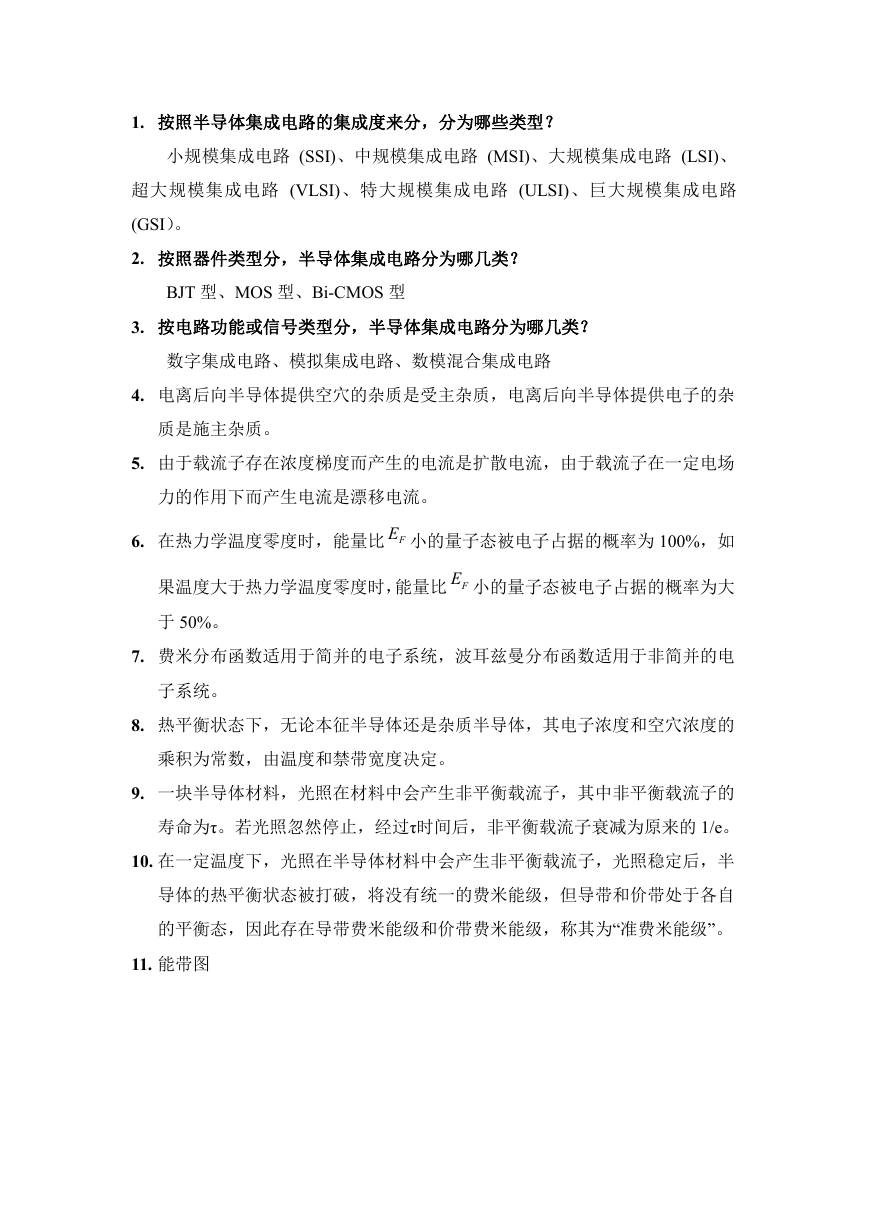

11. 能带图

�

12. 电导率与电阻率

本征半导体:

i qn

p

n

,

=

iqn

1

p

n

一般半导体:

qn

0

n

qp

0

p

,

=

1

qp

0

p

qn

0

n

N 型半导体:

0

nqn

,

P 型半导体:

0

pqp

,

1=

nqn

0

1=

pqp

0

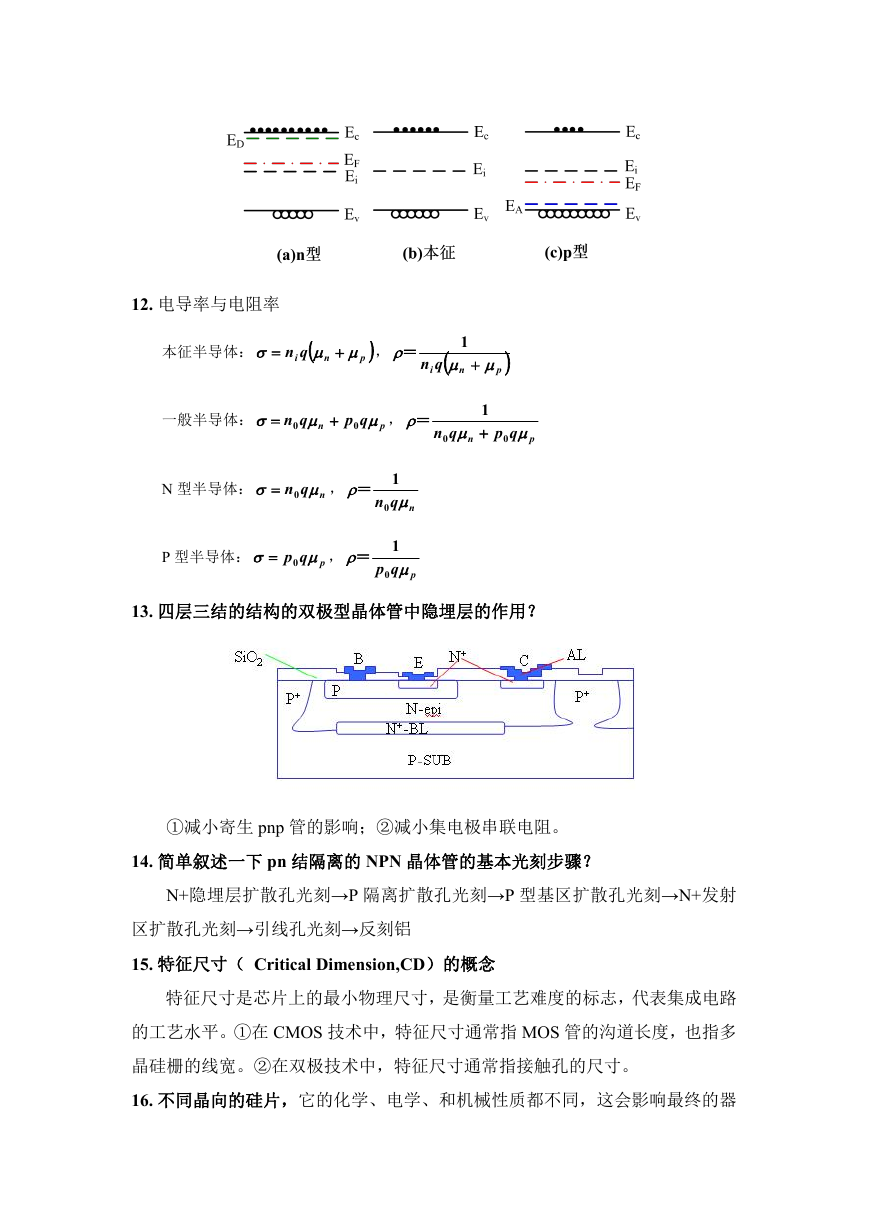

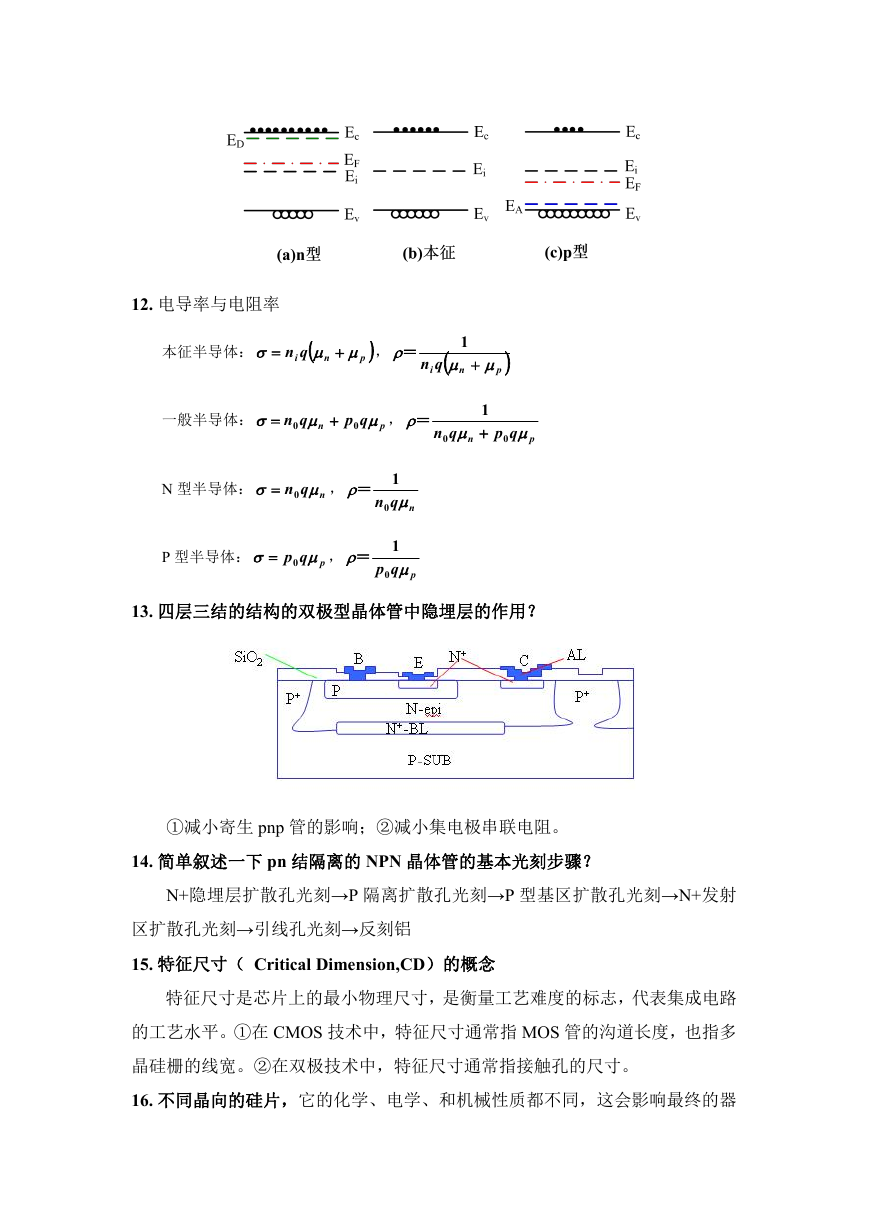

13. 四层三结的结构的双极型晶体管中隐埋层的作用?

①减小寄生 pnp 管的影响;②减小集电极串联电阻。

14. 简单叙述一下 pn 结隔离的 NPN 晶体管的基本光刻步骤?

N+隐埋层扩散孔光刻→P 隔离扩散孔光刻→P 型基区扩散孔光刻→N+发射

区扩散孔光刻→引线孔光刻→反刻铝

15. 特征尺寸( Critical Dimension,CD)的概念

特征尺寸是芯片上的最小物理尺寸,是衡量工艺难度的标志,代表集成电路

的工艺水平。①在 CMOS 技术中,特征尺寸通常指 MOS 管的沟道长度,也指多

晶硅栅的线宽。②在双极技术中,特征尺寸通常指接触孔的尺寸。

16. 不同晶向的硅片,它的化学、电学、和机械性质都不同,这会影响最终的器

�

件性能。例如迁移率,界面态等。MOS 集成电路通常用(100)晶面或<100>

晶向;双极集成电路通常用(111)晶面或<111>晶向。

17. 硅热氧化的概念、氧化的工艺目的、氧化方式及其化学反应式。

氧化的概念:硅热氧化是氧分子或水分子在高温下与硅发生化学反应,并在

硅片表面生长氧化硅的过程。

氧化的工艺目的:在硅片上生长一层二氧化硅层以保护硅片表面、器件隔离、

屏蔽掺杂、形成电介质层等。

氧化方式及其化学反应式:①干氧氧化:Si+O2 →SiO2

②湿氧氧化:Si + H2O +O2 → SiO2+H2

③水汽氧化:Si + H2O → SiO2 + H2

硅的氧化温度:750 ℃ ~1100℃

18. SiO2 在集成电路中的用途

①栅氧层:做 MOS 结构的电介质层(热生长)

②场氧层:限制带电载流子的场区隔离(热生长或沉积)

③保护层:保护器件以免划伤和离子沾污(热生长)

④注入阻挡层:局部离子注入掺杂时,阻挡注入掺杂(热生长)

⑤垫氧层:减小氮化硅与硅之间应力(热生长)

⑥注入缓冲层:减小离子注入损伤及沟道效应(热生长)

⑦层间介质:用于导电金属之间的绝缘(沉积)

19. 热生长氧化层与沉积氧化层的区别

①结构及质量:热生长的比沉积的结构致密,质量好。

②成膜温度:热生长的比沉积的温度高。可在 400℃获得沉积氧化层,在第

一层金属布线形成完进行,做为金属之间的层间介质和顶层钝化层。

③硅消耗:热生长的消耗硅,沉积的不消耗硅。

20. 杂质在硅中的扩散机制

①间隙式扩散;②替位式扩散。

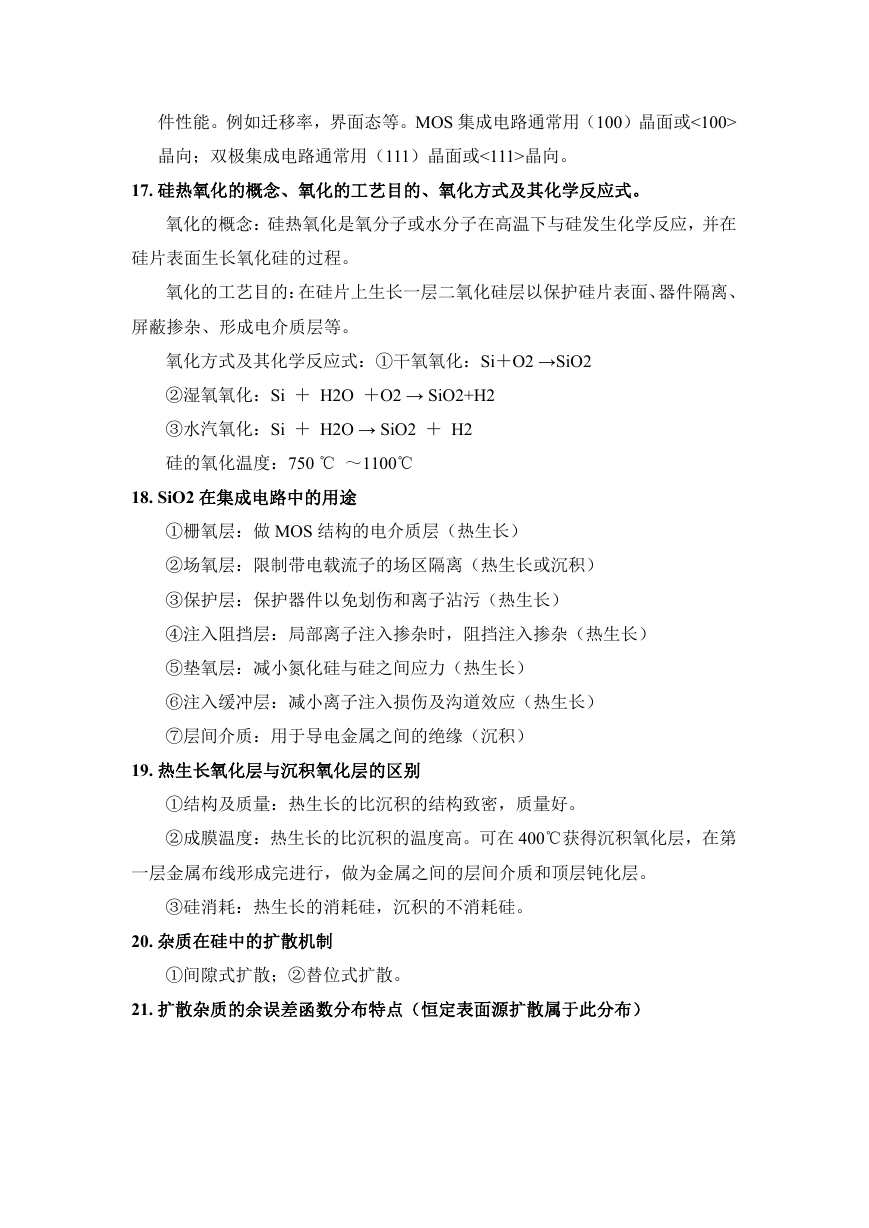

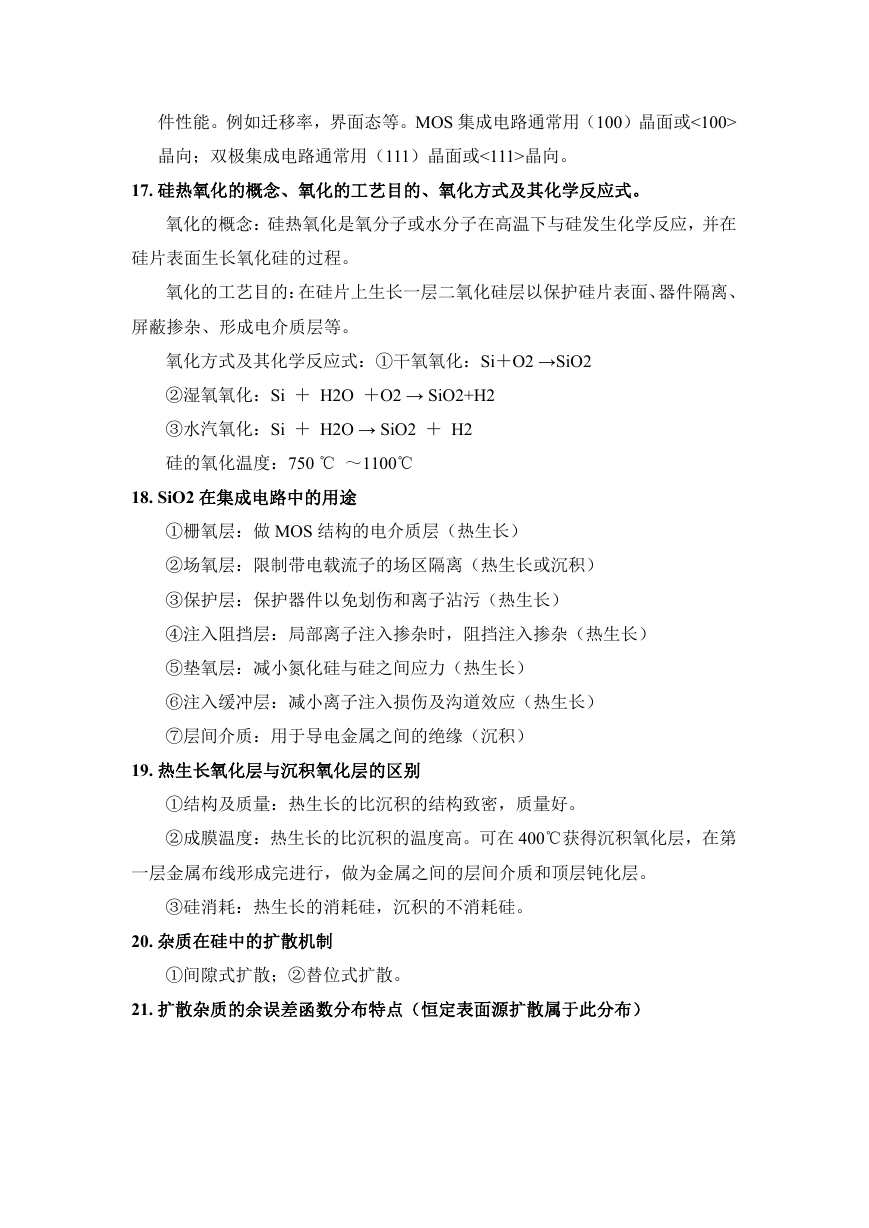

21. 扩散杂质的余误差函数分布特点(恒定表面源扩散属于此分布)

�

①杂质表面浓度由该种杂质在扩散温度下的固溶度所决定。当扩散温度不变

时,表面杂质浓度维持不变;

②扩散时间越长,扩散温度越高,则扩散进入硅片内的杂质总量就越多;

③扩散时间越长,扩散温度越高,杂质扩散得越深。

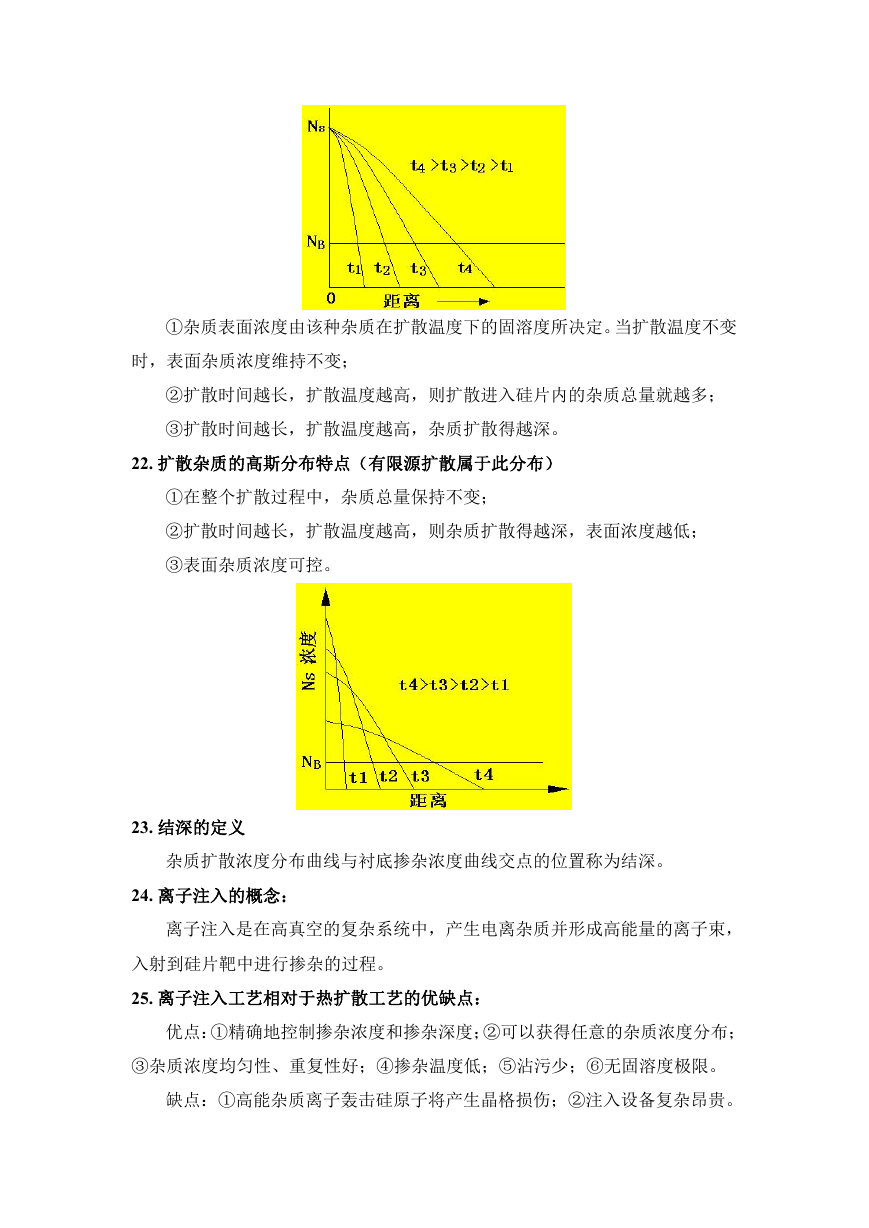

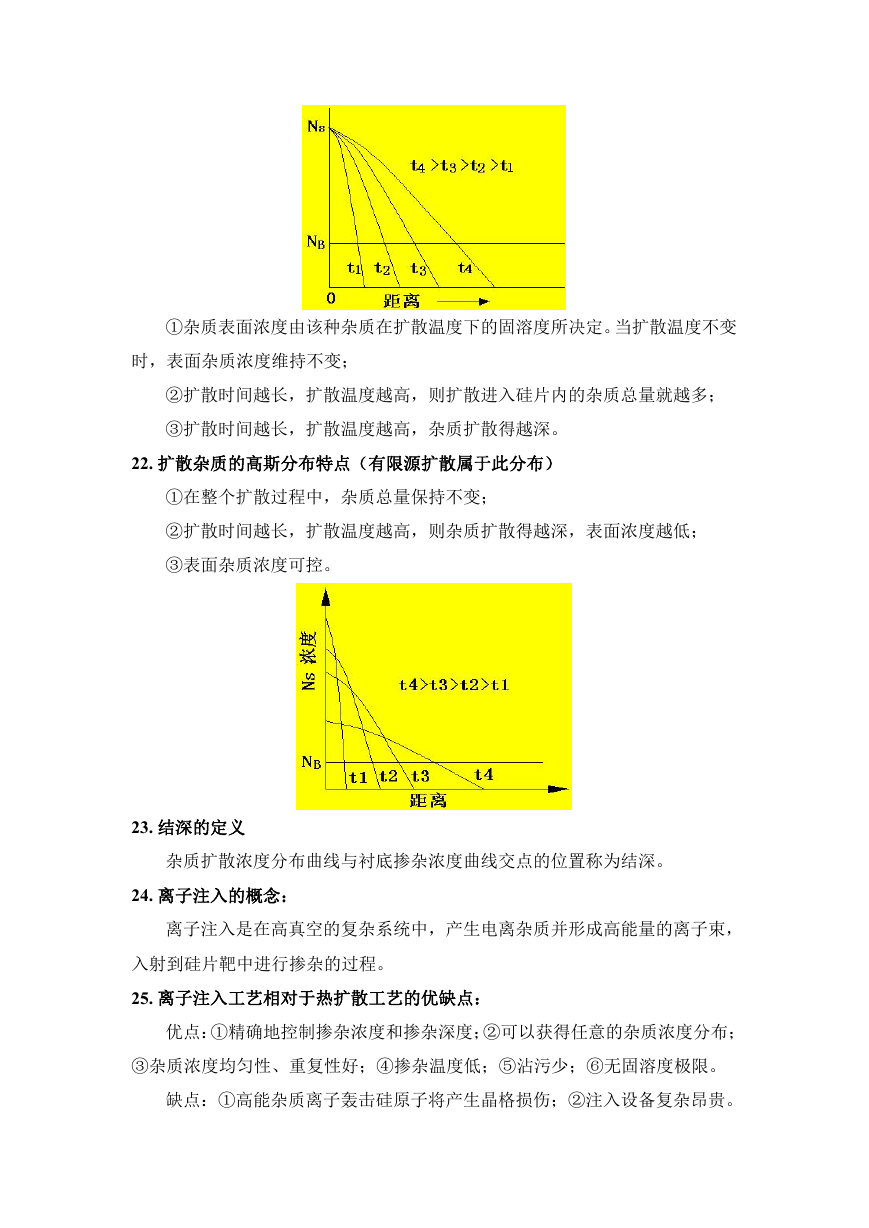

22. 扩散杂质的高斯分布特点(有限源扩散属于此分布)

①在整个扩散过程中,杂质总量保持不变;

②扩散时间越长,扩散温度越高,则杂质扩散得越深,表面浓度越低;

③表面杂质浓度可控。

23. 结深的定义

杂质扩散浓度分布曲线与衬底掺杂浓度曲线交点的位置称为结深。

24. 离子注入的概念:

离子注入是在高真空的复杂系统中,产生电离杂质并形成高能量的离子束,

入射到硅片靶中进行掺杂的过程。

25. 离子注入工艺相对于热扩散工艺的优缺点:

优点:①精确地控制掺杂浓度和掺杂深度;②可以获得任意的杂质浓度分布;

③杂质浓度均匀性、重复性好;④掺杂温度低;⑤沾污少;⑥无固溶度极限。

缺点:①高能杂质离子轰击硅原子将产生晶格损伤;②注入设备复杂昂贵。

�

26. 离子注入效应

沟道效应:当注入离子未与硅原子碰撞减速,而是穿透了晶格间隙时就发生

了沟道效应。控制沟道效应的方法:①倾斜硅片;②缓冲氧化层;③硅预非晶化

(低能量(1KEV)浅注入应用非常有效);④使用质量较大的原子。

注入损伤:高能杂质离子轰击硅原子将产生晶格损伤。消除晶格损伤的方法:

①注入缓冲层;②离子注入退火工艺。

27. 离子注入退火

工艺目的:消除晶格损伤,并且使注入的杂质转入替位位置从而实现电激活。

①高温热退火

通常的退火温度:>950℃,时间:30 分钟左右

缺点:高温会导致杂质的再分布。

②快速热退火

采用 RTP,在较短的时间(10-3~10-2 秒)内完成退火。

优点:杂质浓度分布基本不发生变化

28. 在先进的 CMOS 工艺中,离子注入的应用

①深埋层注入;②倒掺杂阱注入;③穿通阻挡层注入;④阈值电压调整注入;

⑤ 轻掺杂漏区(LDD)注入;⑥源漏注入;⑦多晶硅栅掺杂注入;⑧沟槽电容

器注入;⑨超浅结注入;⑩绝缘体上的硅(SOI)中的氧注入。

29. 光刻的概念

光刻是把掩膜版上的电路图形精确地转移到硅片表面光刻胶膜上的过程。光

刻是集成电路制造的关键工艺。

30. 光刻工艺的 8 个基本步骤:

①气相成底膜;②旋转涂胶;③软烘;④对准和曝光;⑤曝光后烘培(PEB);

⑥显影;⑦坚膜烘培;⑧显影检查。

31. 什么是光刻胶、光刻胶的用途、光刻对光刻胶的要求

光刻胶是一种有机化合物,它受紫外线曝光后在显影液中的溶解度发生显著

变化,而未曝光的部分在显影液中几乎不溶解。

光刻胶的用途:①做硅片上的图形模版(从掩膜版转移到硅片上的图

形);②在后续工艺中,保护下面的材料(例如刻蚀或离子注入)。

�

光刻对光刻胶的要求:①分辨率高;②对比度好;③敏感度好;④粘滞性好

⑤粘附性好;⑥抗蚀性好;⑦颗粒少。

32. 正胶和负胶区别

正胶:曝光的部分易溶解,占主导地位;负胶:曝光的部分不易溶解。负胶

的粘附性和抗刻蚀性能好,但分辨率低。

33. 刻蚀的概念、工艺目的、分类、应用

概念:用化学或物理的方法,有选择地去除硅片表面层材料的过程称为刻蚀。

工艺目的:把光刻胶图形精确地转移到硅片上,最后达到复制掩膜版图形的

目的。刻蚀是在硅片上复制图形的最后图形转移工艺,是集成电路制造的重要工

艺之一。

刻蚀的分类:①按工艺目的分类:有图形刻蚀、无图形刻蚀。无图形刻蚀:

材料去除和回蚀。②按工艺手段分类:干法刻蚀和湿法刻蚀。③按刻蚀材料分类:

金属刻蚀、介质刻蚀、硅刻蚀。

应用:在硅片上制作不同的特征图形,包括选择性氧化的氮化硅掩蔽层、沟

槽隔离和硅槽电容的沟槽、多晶硅栅、金属互联线、接触孔和通孔。

34. 干法刻蚀与湿法刻蚀

把硅片置于气态产生的等离子体,等离子体中的带正电离子物理轰击硅片表

面,等离子体中的反应粒子与硅片表面发生化学反应,从而去除暴露的表面材料。

干法刻蚀用物理和化学方法,可实现各向异性刻蚀,能实现图形的精确转移。干

法刻蚀是集成电路刻蚀工艺的主流技术,广泛用于有图形刻蚀、回蚀和部分材料

去除工艺。

把硅片置于液体化学试剂,化学腐蚀液与硅片表面发生化学反应,从而去除

暴露的表面材料。湿法刻蚀用化学方法,一般是各向同性刻蚀,不能实现图形的

精确转移。湿法刻蚀基本只用于部分材料去除工艺。

35. 干法刻蚀的优缺点(与湿法刻蚀比)

优点:①刻蚀剖面各向异性,非常好的侧壁剖面控制;②好的 CD 控制;③

最小的光刻胶脱落或粘附问题;④好的片内、片间、批间的刻蚀均匀性;⑤化学

品使用费用低。(为什么现代集成电路工艺多采用干法刻蚀?)

缺点:①对下层材料的刻蚀选择比较差;②等离子体诱导损伤;③设备昂贵。

�

36. 为什么多晶硅的干法刻蚀要采用氯基气体而不是氟基气体?

不用 SF6 等 F 基气体是因为 Cl 基气体刻蚀多晶硅对下层的栅氧化层有较高

的选择比。

37. 化学气相沉积 CVD 的概念

Chemical Vapor Deposition. 化学气相沉积是利用电阻加热、等离子体、光辐

射等能源使某些气态物质发生化学反应,生成固态物质并沉积在衬底表面形成薄

膜的过程。

38. 沉积多晶硅采用什么 CVD 工具?掺杂的 Poly-Si 的主要用途。写出掺杂的

Poly-Si 做栅电极的 6 个原因。

沉积多晶硅采用 LPCVD。

用途:①掺杂的 Poly-Si 在 MOS 器件中用做栅电极;②掺杂的 Poly-Si

做多晶电阻及桥联;③PIP 电容的上下电极。

掺杂的 Poly-Si 做栅电极的原因:

①通过掺杂可得到特定的电阻;②与 SiO2 有优良的界面特性;③和后续高

温工艺的兼容性;④比金属电极(如 Al)更高的可靠性;⑤在陡峭的结构上沉

积的均匀性;⑥实现栅的自对准工艺。

39. 蒸发的优缺点

优点:①成膜速率高(能蒸发 5 微米厚的铝膜);②金属膜纯度高

缺点:①台阶覆盖能力差;②不能沉积金属合金

40. 溅射的优缺点

优点:①台阶覆盖能力好;②能沉积金属合金;③能进行原位溅射刻蚀

缺点:溅射速率低, 金属膜含氩

41. 高能离子轰击

①离子反射(能量很小);②离子吸附(<10eV),能量转化热能;③离子注

入(>10keV),能量改变结构;④溅射(0.5keV~5keV),溅射原子能量 10~50eV。

42. 铝互连的优缺点

优点:①电阻率低;②铝的成本低;③与硅和二氧化硅的粘附性好;④易于

沉积成膜(蒸发、溅射);⑤易于刻蚀;⑥抗腐蚀性能好,因为铝表面总是有一

层抗腐蚀性好的氧化层(Al2O3);⑦接触电阻低(欧姆接触)。

�

缺点:①结穿刺现象;②电迁移现象。

43. 铝的结穿刺现象

在纯铝和硅的界面加热合金化过程中(450~500℃) ,硅开始溶解在铝中

直到在铝中的浓度达到 0.5%,该过程消耗硅并在硅中形成空洞,可穿透浅结,

引起短路。

解决方法:①使用含硅(1~2%)的铝合金,铝中硅已饱和,抑制硅向铝中

扩散;②引入阻挡层金属(例如 TiN)以抑制硅扩散。

44. 电迁移现象

当金属线流过大密度的电流时,电子和金属原子的碰撞引起金属原子的移动

导致金属原子的消耗和堆积。电迁移现象会造成金属线开路、两条邻近的金属线

短路。纯铝的电迁移现象非常严重。

解决方法:使用含 0.5 %铜的铝合金

45. 铜互连的优缺点及采取的工艺措施

优点:①电阻率更低;②电流密度高:抗电迁徙能力好于铝,铜合金中加入

Al 或 Ti 进一步增强抗电迁移;③更少的工艺步骤:采用大马士革方法,减少

20%~30%;④易于沉积(铜 CVD、电镀铜);⑤铜的成本低。

缺点:①不能干法刻蚀铜;②铜在硅和二氧化硅中扩散很快,芯片中的铜杂

质沾污使电路性能变坏;③抗腐蚀性能差;④粘附性差。

工艺措施:①采用大马士革工艺回避干法刻蚀铜;②采用电镀来满足大马士

革工艺对间隙填充的要求;③用阻挡层金属(例如 Ta)增强粘附阻挡扩散;④

用金属钨做底层金属解决了器件的铜沾污。

46. 化学机械平坦化 CMP

(Chemical Mechanical Planarization)也称为化学机械抛光 CMP(Chemical

Mechanical Polish)是通过化学反应和机械研磨相结合的方法对表面起伏的硅片

进行平坦化的过程。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc