东华理工大学机械与电子工程学院

基于 VHDL 语言的 8 位数字密码锁设计

一、摘要:

数字控制的电子密码锁已经广泛应用在办公室、公司、宾馆、

小区住宅等场所。

EDA 技术的应用引起了电子产品系统开发的革命性变革。利用先

进的 EDA 工具,基于硬件描述语言,可以进行系统级数字逻辑电路的

设计。本文简述了 VHDL 语言的功能及其特点,并以 8 位串行数字锁

设计为例,介绍了在 QUARTUS II 6.0 开发软件下,利用 VHDL 硬件描

述语言设计数字逻辑电路的过程和方法。

关键词: QUARTUS II 6.0 EDA 电子密码锁(电子设计自动化)

VHDL 语言 语言设计 串行 密码锁 硬件描述语言 数字逻辑电路

Based on VHDL language 8 digits combination lock design

Digital control of electronic locks has widely used in

office, companies, hotels, residential area and etc.

EDA technology application caused a electronic product

development system of the revolutionary transformation. Using

advanced EDA tools, hardware based description language, can

undertake system in digital logic circuit design. This paper

describes the function and characteristics of VHDL language,

and eight serial number lock design as an example, this paper

introduces QUARTUS II 6.0 software development in of VHDL

1

�

hardware design of digital logic circuit process and method.

Keywords: QUARTUS II 6.0, EDA (electronic design

automation), electronic locks and VHDL language, language

design, serial, locks and hardware description language,

digital logic circuit

二、引言:

电子密码锁系统主要由电子锁体、电子密匙等部分组成,一把电

子密匙里能存放多组开锁密码,用户在使用过程中能够随时修改开锁

密码,更新或配制钥匙里开锁密码。一把电子锁可配制多把钥匙。语

音方面的广泛应用,使得具有语音播放的电子密码锁使用起来更加方

便。语音密码锁的体积小、保密性能好、使用方便,是用在保险箱、

电话或是房门上不可少的部分。

数字集成技术和电子设计自动化(E1ectronic Design

Automation,EDA)技术的发展迅速,数字系统设计的理论和方法也在

相应地变化和发展着。应用可编程逻辑器件(Programmable Logic

Device,PLD)实现数字系统的设计,是目前利用 EDA 技术设计数字系

统的潮流。利用基于 EDA 技术的设计方法,设计者只需对系统功能进

行描述,就可在 EDA 工具的帮助下完成系统设计。这种设计方法以数

字系统设计软件为工具,将测试码或测试序列测试验证后,将系统实

现在 PLD 芯片或专业集成电路上,这样最大程度地缩短了设计和开发

时间,降低了成本,提高了系统的可靠性。本文详细介绍了基于 EDA

技术数字密码锁的设计过程。

2

�

三、密码锁系统的设计

1、设计要求:

数字密码锁的密码为 8 位十进制数字,密码可以设置和修改;开

锁时间定为 30 秒;可用七段显示器显示开锁倒计时时间值;开锁计

时时间 30 秒到,锁没开则用蜂鸣器报警,开锁时允许修改输入错误

的密码数字。具体要求如下:

(1)分析功能要求,设计系统构成模块,画出方框图。

(2)编写模块的 Verilog HDL 语言的设计程序

(3)在 Quartus II 软件或其他 EDA 软件上完成设计和仿真

(4)根据实验装置上的 CPLD/FPGA 芯片,在是配时选择相应的

芯片,将设计生成配置文件或 JEDEC 文件,然后将配置文件或 JEDEC

文件下载到实验装置上运行,操作实验装置上设定设定的功能开关,

验证设计功能。

2、设计分析

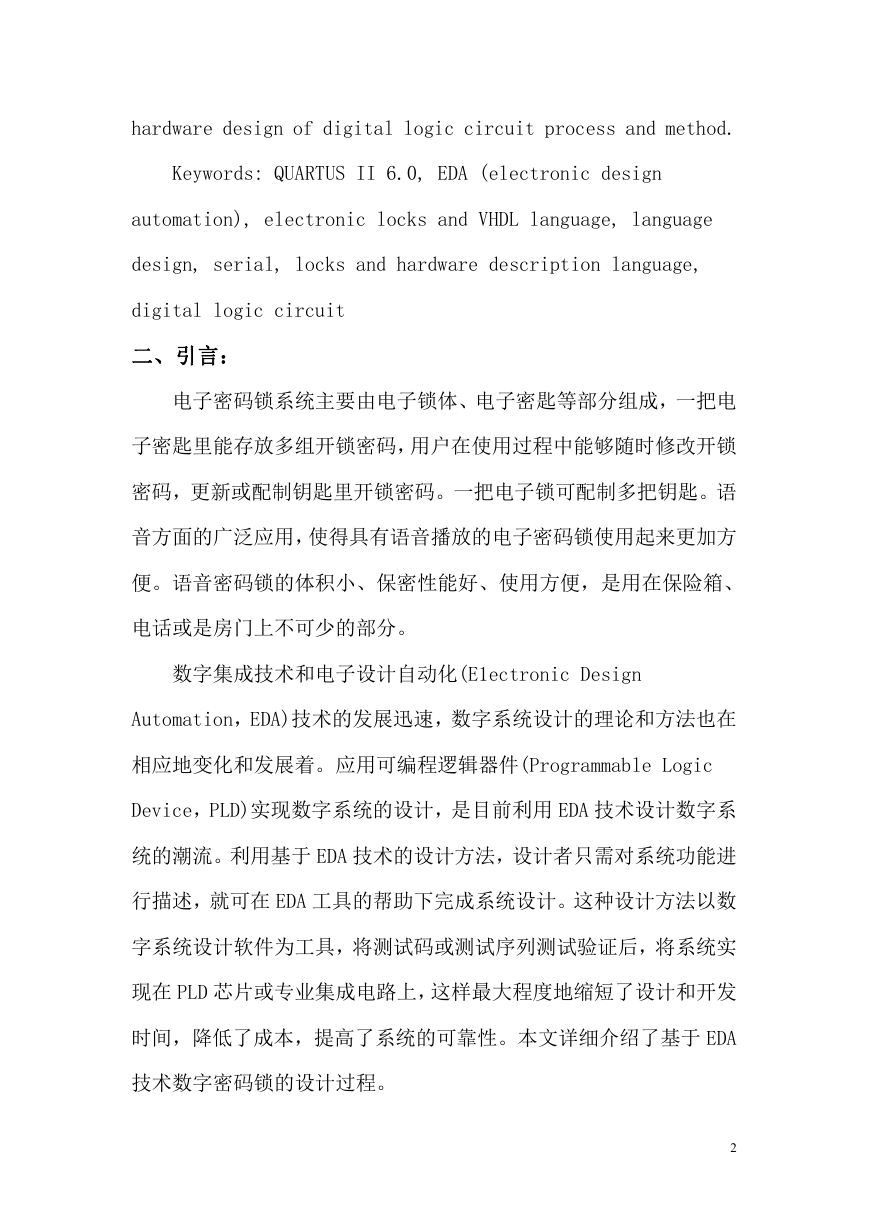

此系统可以分为密码输入删除控制模块、寄存模块、比较并延时

模块、扫描显示模块几部分。数字密码锁系统框图如图所示。

密码输入与删除控制模块设计考虑:

1)编码器:对数据开关 K1...K10 的电平信号,分别代表数字

1...9,采用热码方式编码。

2)设置与删除密码操作及显示按设计要求处理。

3)信号设置

Set 密码确认信号——当 8 位密码输入完成,按 set 键则密

3

�

送锁存器锁存,比较模块得数据 A、密码显示电路清零。

Back:数字删除按键——每按一次删除最后输入的数字。

Lock:密码锁状态显示信号——lock=0(LED 灯灭)表示锁未开

lock=1(LED 灯亮)表示锁已开。

Close:关锁信号——当密码送寄存器锁存后,按下 close

则密码锁 lock=0,锁被锁上。

Check:密码检验信号——在 lock=0 状态下,从数据开关输

8 位开锁密码后按下 check,则开锁密码送寄存模块锁存为 B。如果

A=B,则 D 触发器置“1”,锁被打开,否则 lock 保持为 0.

万能密码:可以预设一个 8 位十进制数,如:“00000007”。

数字密码锁系统框图:

1

Close

1D

C1

Sd

开锁延时

A = B

比较模块

A

B

寄存模块

密码输入/删除

控制模块

K1

k2

..............k10

扫 描 显 示 模

块

LOCK

Set

Check

Back

4

�

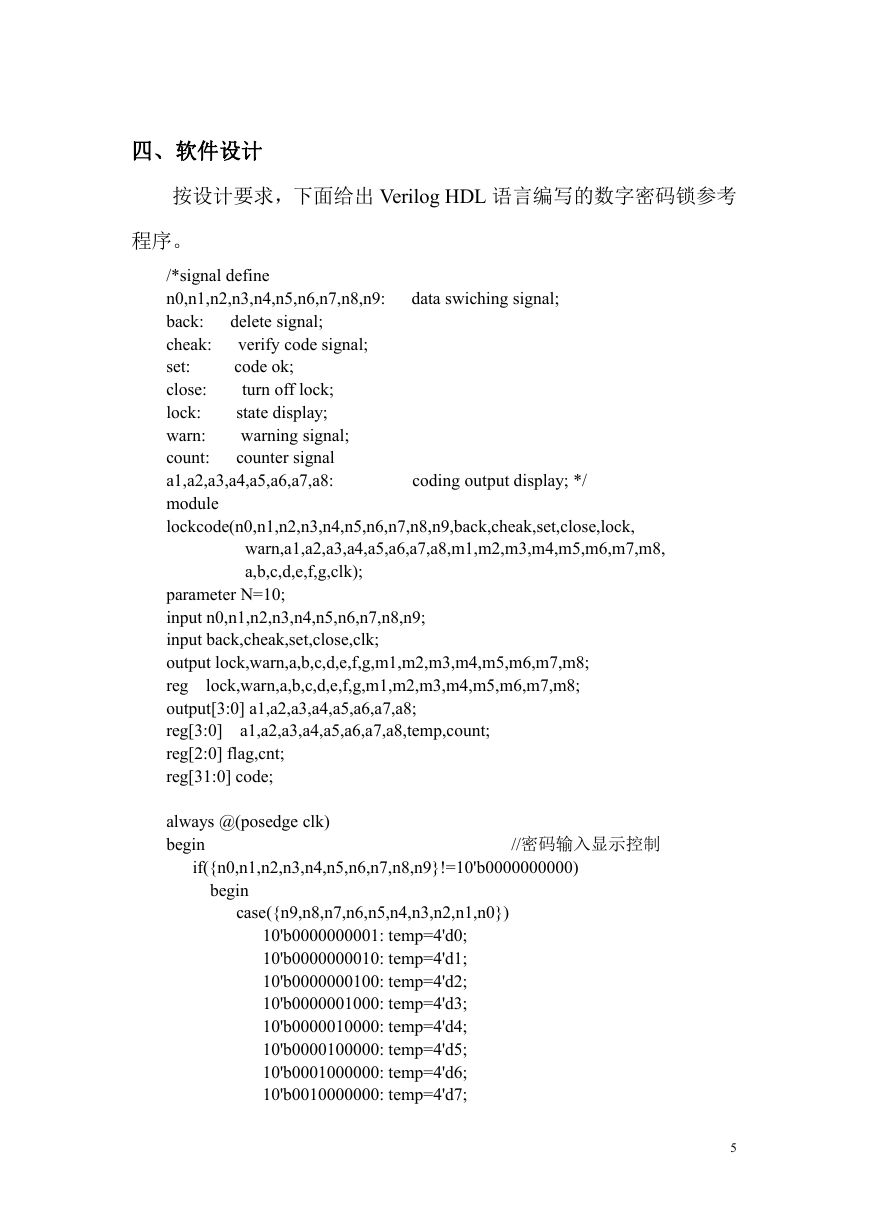

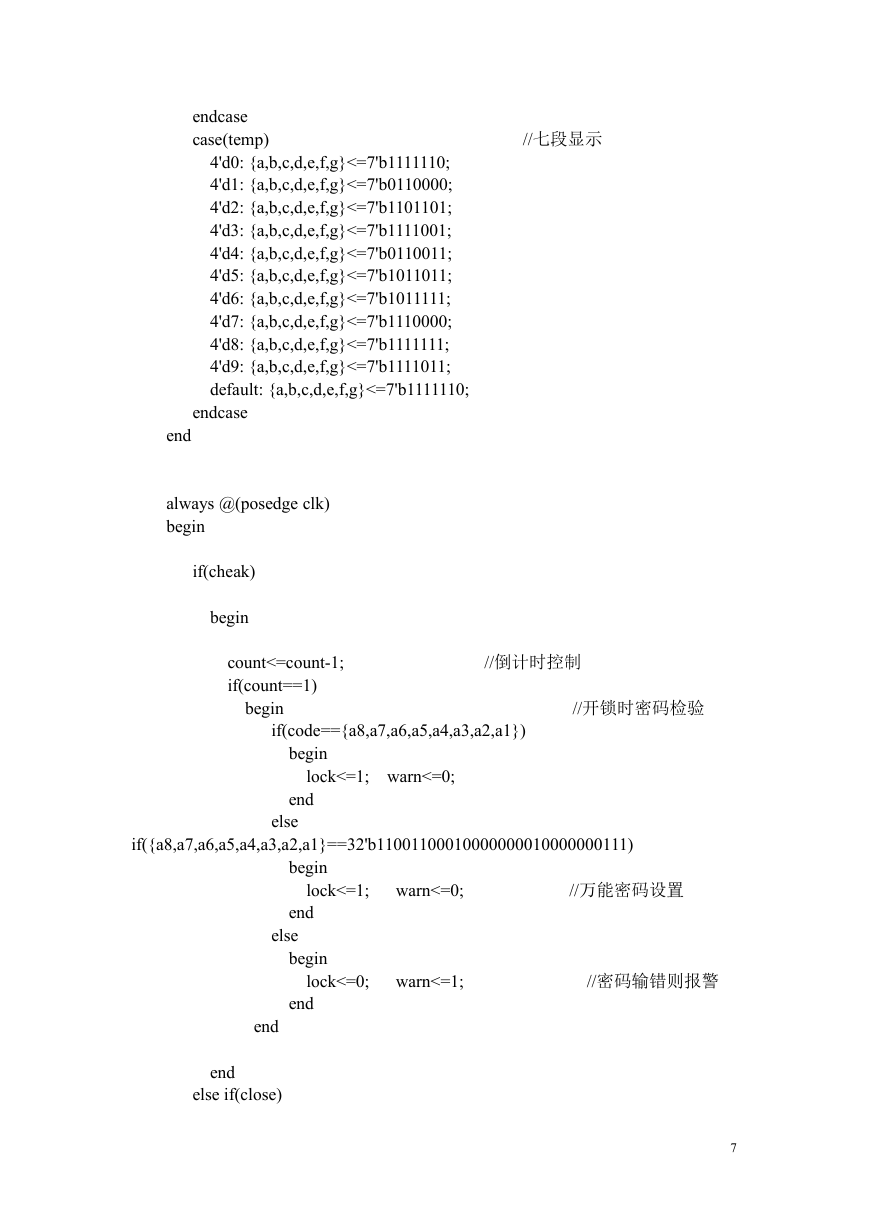

四、软件设计

按设计要求,下面给出 Verilog HDL 语言编写的数字密码锁参考

程序。

data swiching signal;

/*signal define

n0,n1,n2,n3,n4,n5,n6,n7,n8,n9:

delete signal;

back:

verify code signal;

cheak:

code ok;

set:

turn off lock;

close:

state display;

lock:

warning signal;

warn:

count:

counter signal

a1,a2,a3,a4,a5,a6,a7,a8:

module

lockcode(n0,n1,n2,n3,n4,n5,n6,n7,n8,n9,back,cheak,set,close,lock,

coding output display; */

warn,a1,a2,a3,a4,a5,a6,a7,a8,m1,m2,m3,m4,m5,m6,m7,m8,

a,b,c,d,e,f,g,clk);

parameter N=10;

input n0,n1,n2,n3,n4,n5,n6,n7,n8,n9;

input back,cheak,set,close,clk;

output lock,warn,a,b,c,d,e,f,g,m1,m2,m3,m4,m5,m6,m7,m8;

reg

lock,warn,a,b,c,d,e,f,g,m1,m2,m3,m4,m5,m6,m7,m8;

output[3:0] a1,a2,a3,a4,a5,a6,a7,a8;

reg[3:0]

reg[2:0] flag,cnt;

reg[31:0] code;

a1,a2,a3,a4,a5,a6,a7,a8,temp,count;

always @(posedge clk)

begin

//密码输入显示控制

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000)

begin

case({n9,n8,n7,n6,n5,n4,n3,n2,n1,n0})

10'b0000000001: temp=4'd0;

10'b0000000010: temp=4'd1;

10'b0000000100: temp=4'd2;

10'b0000001000: temp=4'd3;

10'b0000010000: temp=4'd4;

10'b0000100000: temp=4'd5;

10'b0001000000: temp=4'd6;

10'b0010000000: temp=4'd7;

5

�

10'b0100000000: temp=4'd8;

10'b1000000000: temp=4'd9;

endcase

a8<=a7; a7<=a6; a6<=a5; a5<=a4;

a4<=a3; a3<=a2; a2<=a1; a1<=temp;

a1<=a2; a2<=a3; a3<=a4; a4<=a5;

a5<=a6; a6<=a7; a7<=a8; a8<=4'b0;

end

else if(back)

begin

end

end

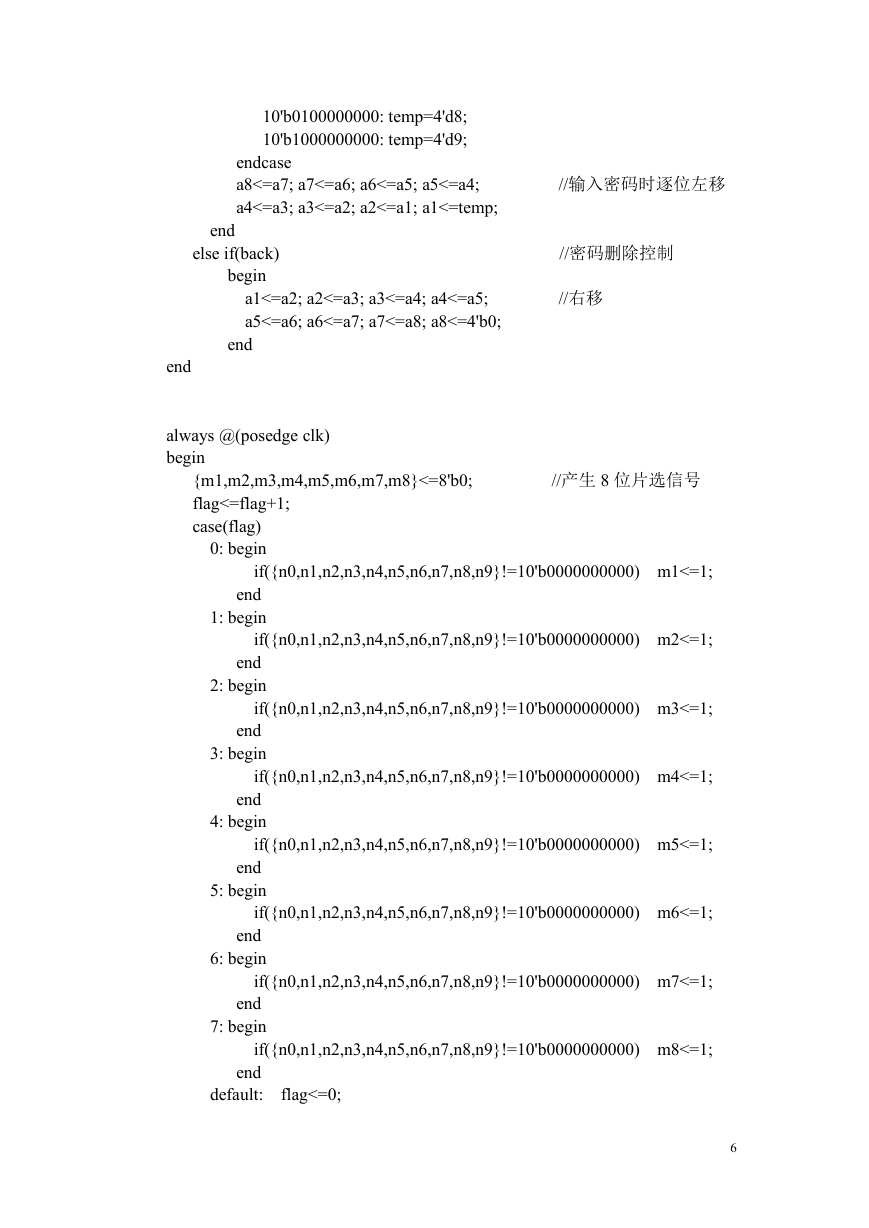

always @(posedge clk)

begin

{m1,m2,m3,m4,m5,m6,m7,m8}<=8'b0;

flag<=flag+1;

case(flag)

0: begin

//输入密码时逐位左移

//密码删除控制

//右移

//产生 8 位片选信号

end

1: begin

end

2: begin

end

3: begin

end

4: begin

end

5: begin

end

6: begin

end

7: begin

end

default:

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m1<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m2<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m3<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m4<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m5<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m6<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m7<=1;

if({n0,n1,n2,n3,n4,n5,n6,n7,n8,n9}!=10'b0000000000) m8<=1;

flag<=0;

6

�

endcase

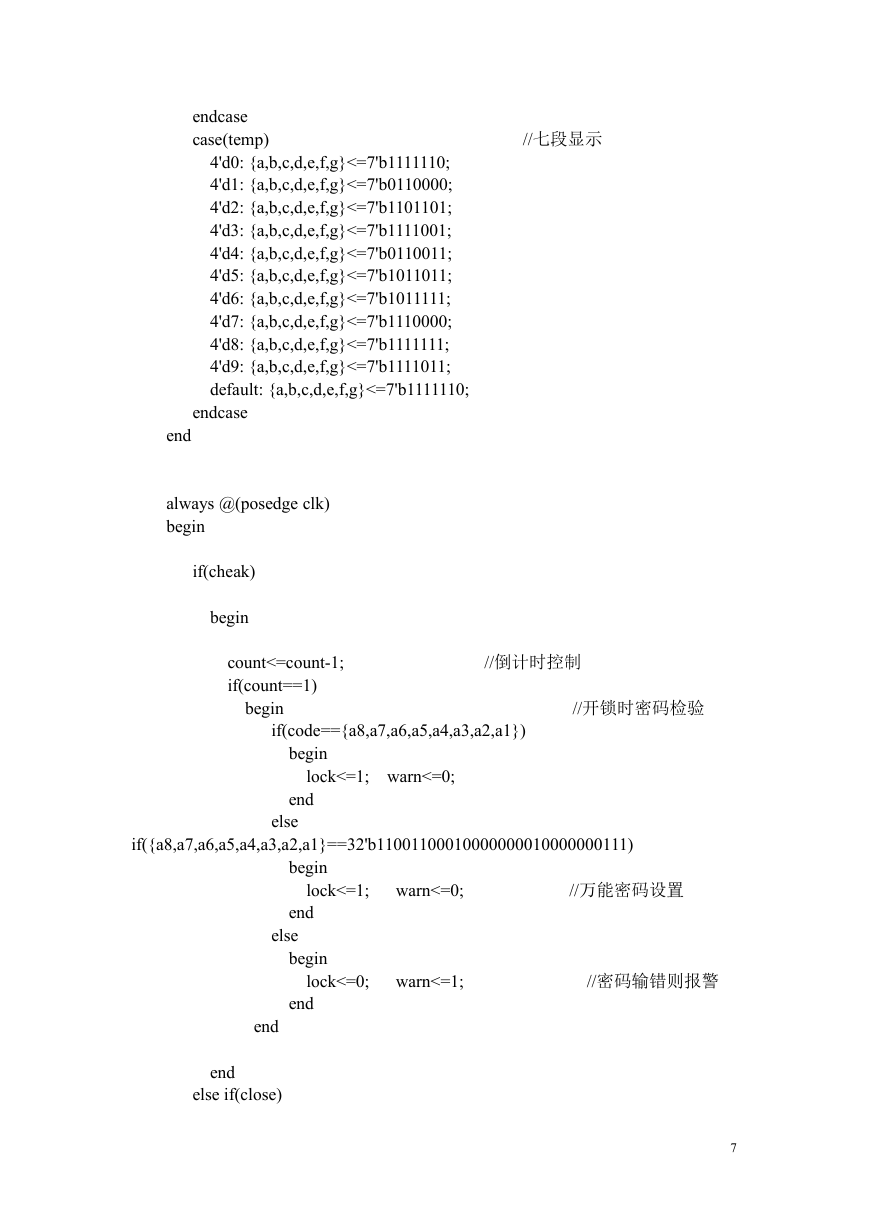

case(temp)

4'd0: {a,b,c,d,e,f,g}<=7'b1111110;

4'd1: {a,b,c,d,e,f,g}<=7'b0110000;

4'd2: {a,b,c,d,e,f,g}<=7'b1101101;

4'd3: {a,b,c,d,e,f,g}<=7'b1111001;

4'd4: {a,b,c,d,e,f,g}<=7'b0110011;

4'd5: {a,b,c,d,e,f,g}<=7'b1011011;

4'd6: {a,b,c,d,e,f,g}<=7'b1011111;

4'd7: {a,b,c,d,e,f,g}<=7'b1110000;

4'd8: {a,b,c,d,e,f,g}<=7'b1111111;

4'd9: {a,b,c,d,e,f,g}<=7'b1111011;

default: {a,b,c,d,e,f,g}<=7'b1111110;

endcase

end

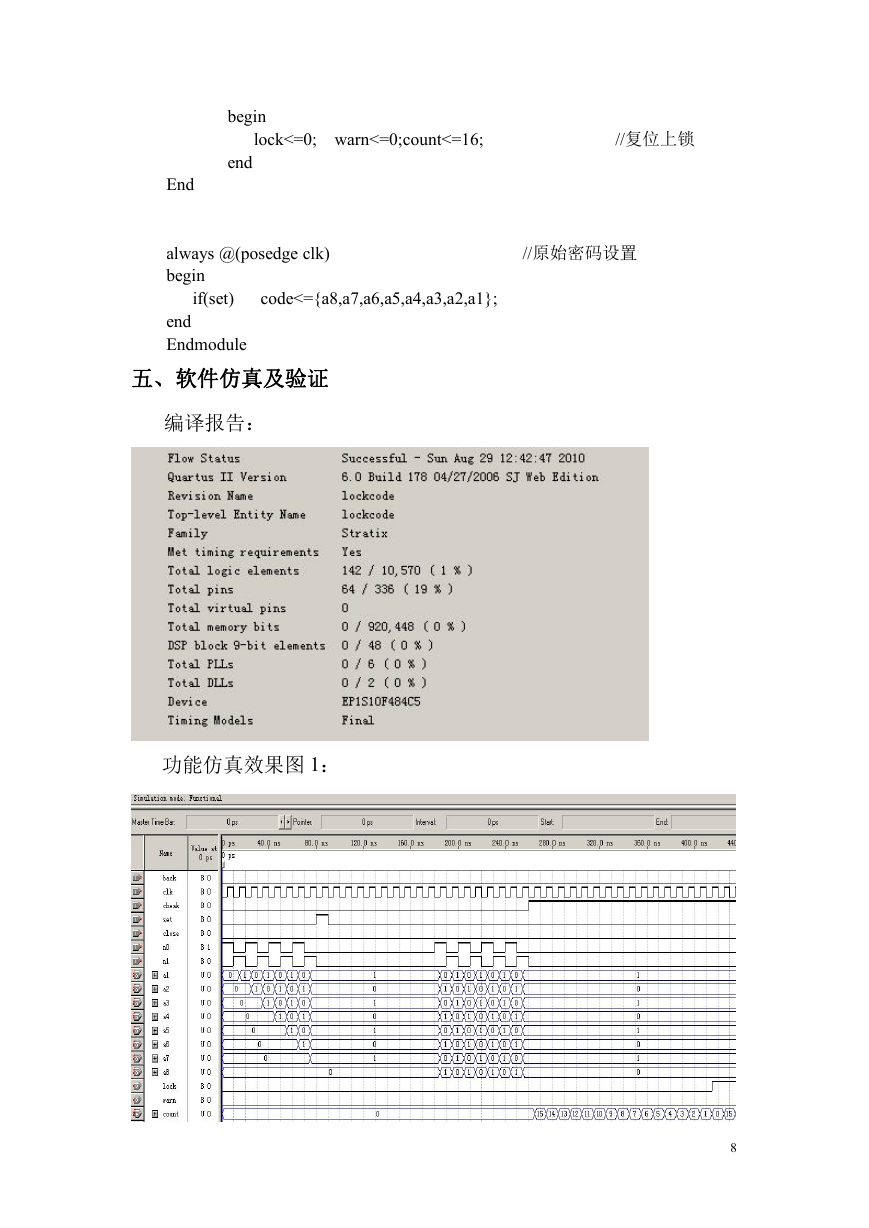

always @(posedge clk)

begin

if(cheak)

begin

count<=count-1;

if(count==1)

begin

//七段显示

//倒计时控制

//开锁时密码检验

if(code=={a8,a7,a6,a5,a4,a3,a2,a1})

lock<=1; warn<=0;

begin

end

else

if({a8,a7,a6,a5,a4,a3,a2,a1}==32'b11001100010000000010000000111)

begin

lock<=1;

end

else

begin

end

lock<=0;

end

end

else if(close)

warn<=0;

//万能密码设置

warn<=1;

//密码输错则报警

7

�

begin

end

End

lock<=0; warn<=0;count<=16;

always @(posedge clk)

begin

end

Endmodule

if(set)

code<={a8,a7,a6,a5,a4,a3,a2,a1};

五、软件仿真及验证

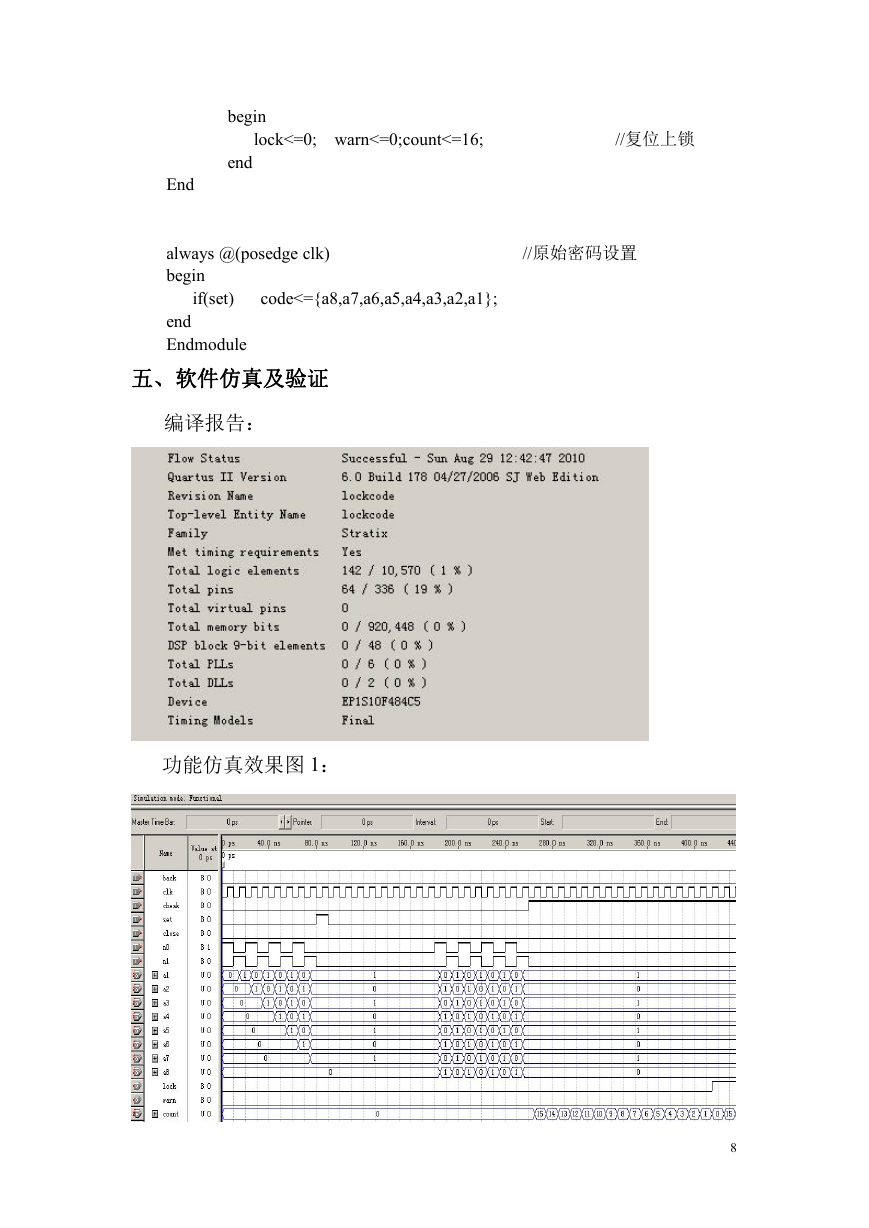

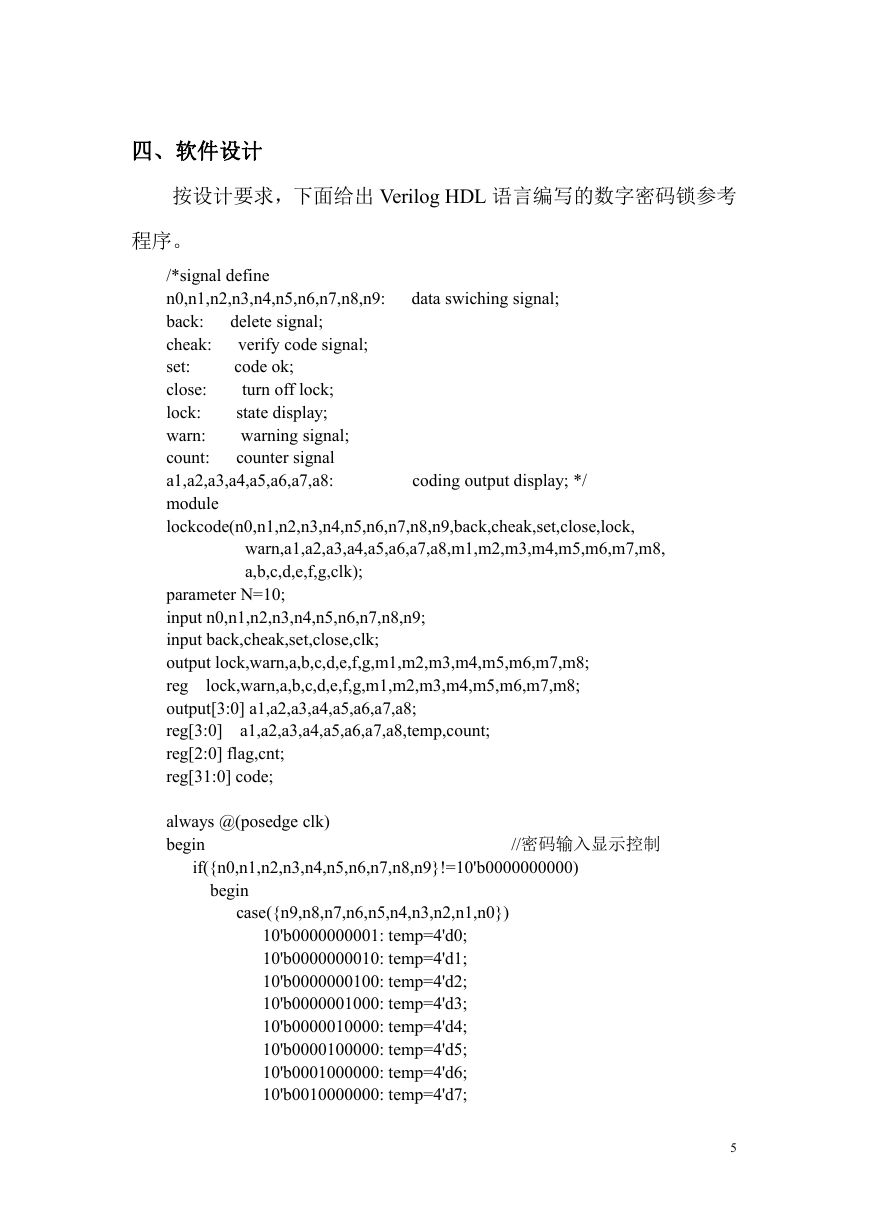

编译报告:

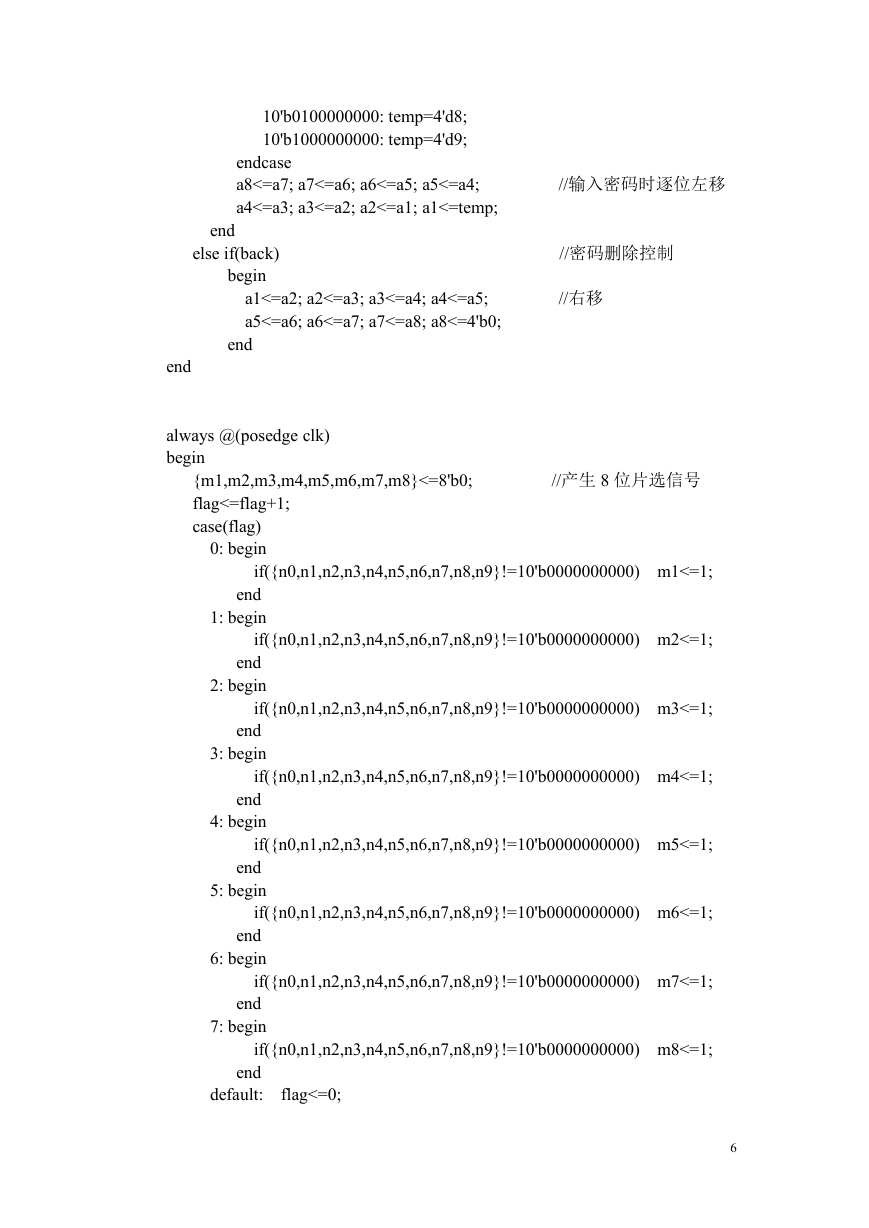

功能仿真效果图 1:

//复位上锁

//原始密码设置

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc