1

2

3

4

5

6

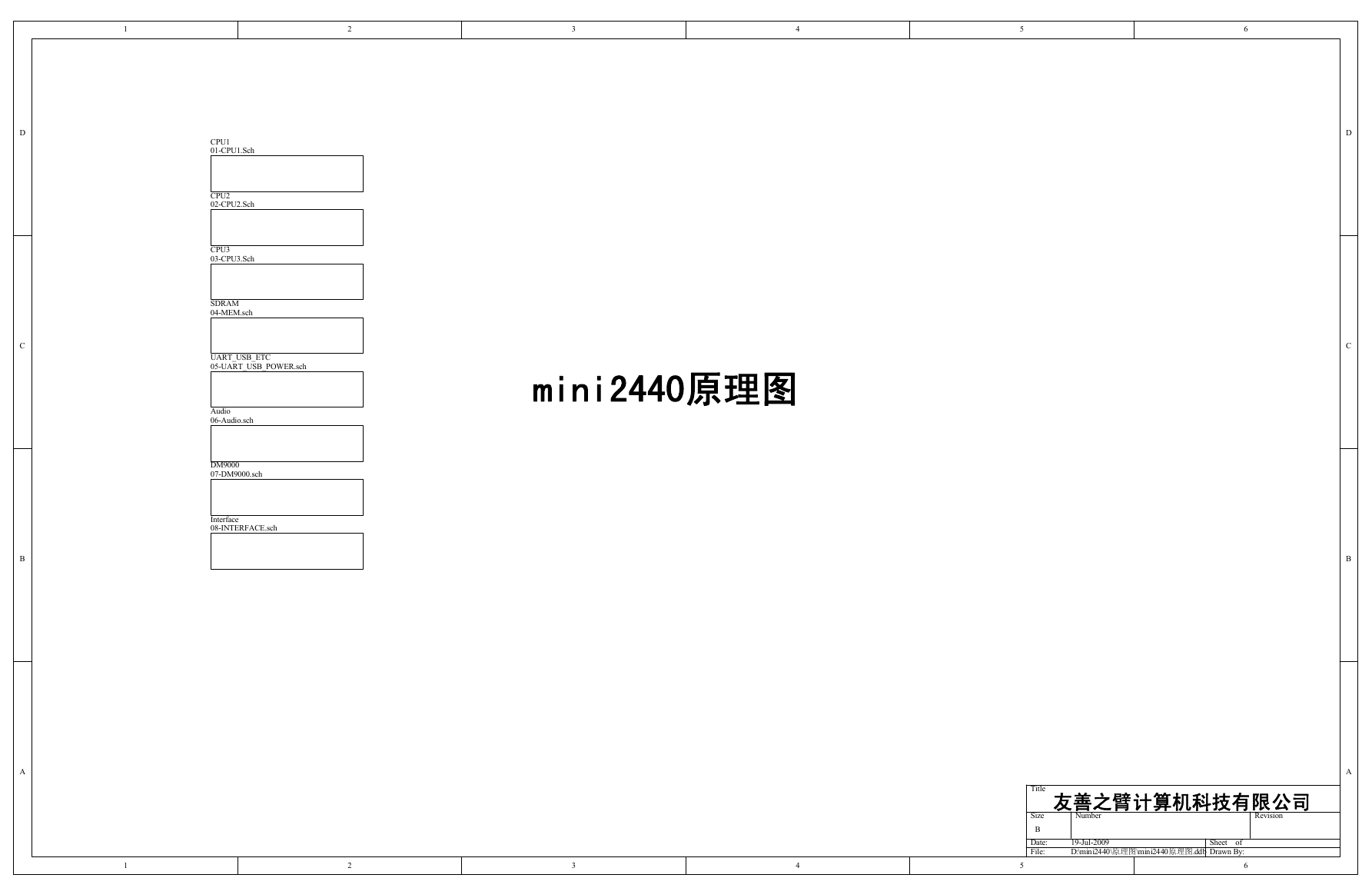

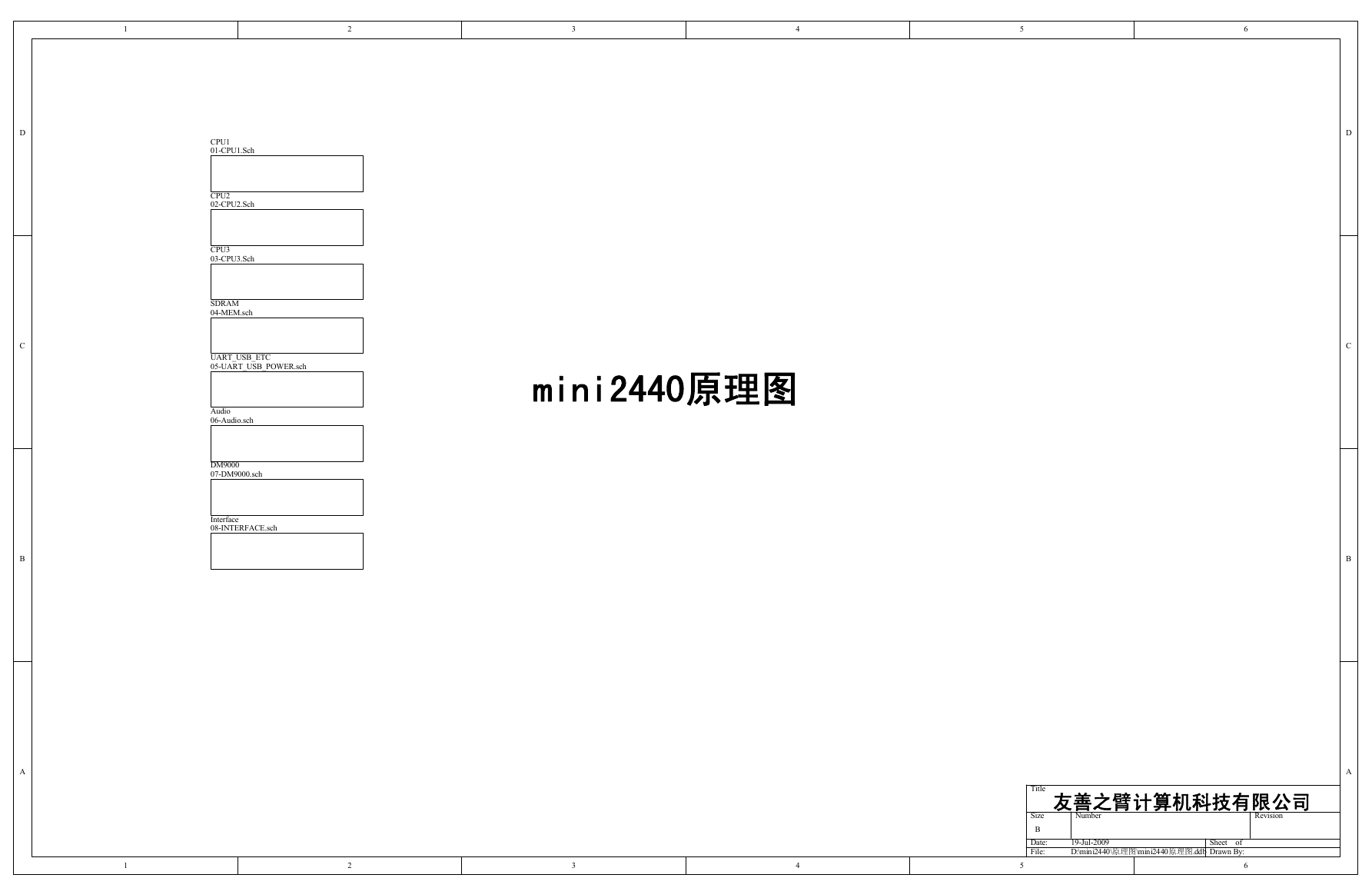

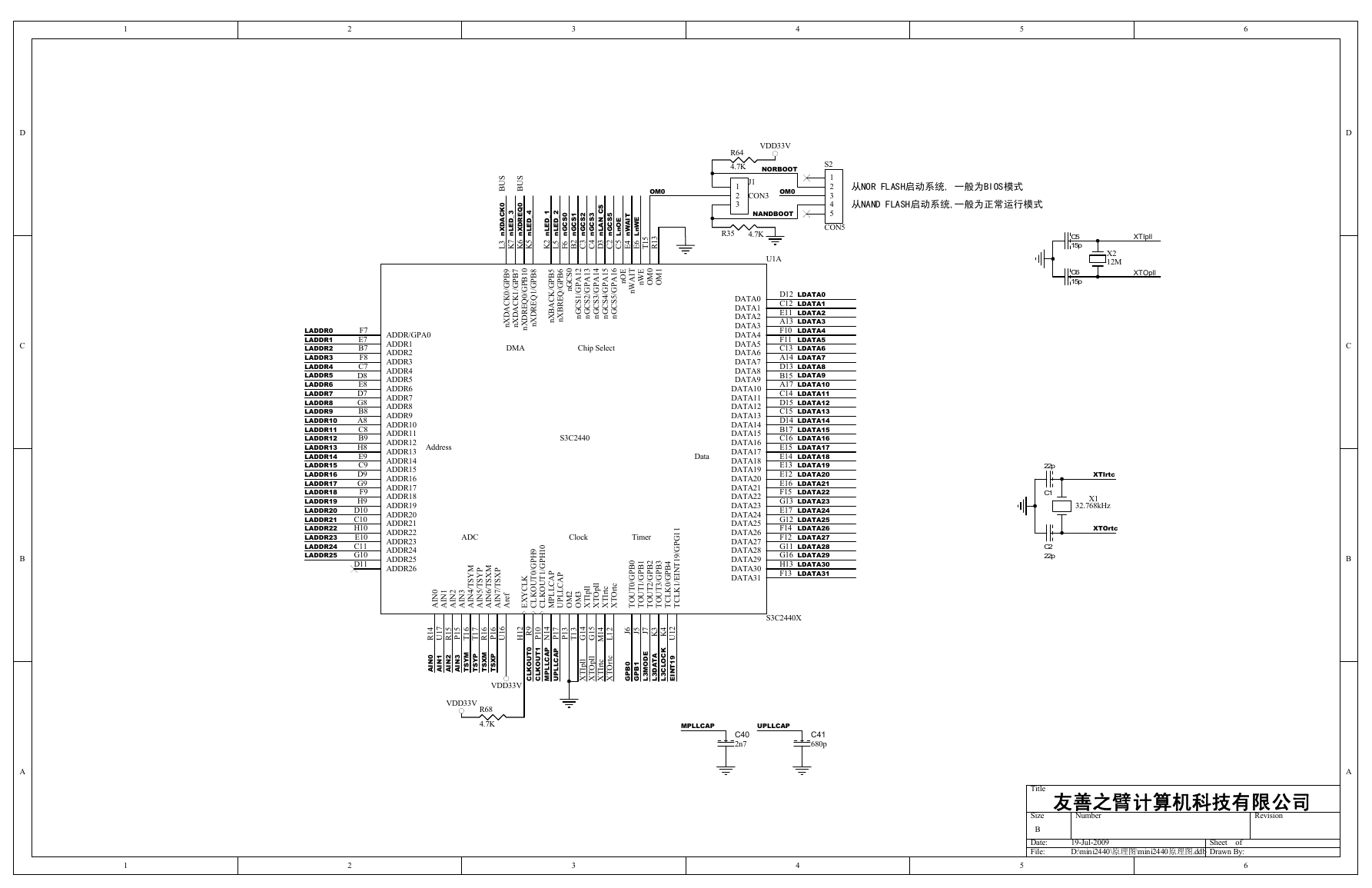

CPU1

01-CPU1.Sch

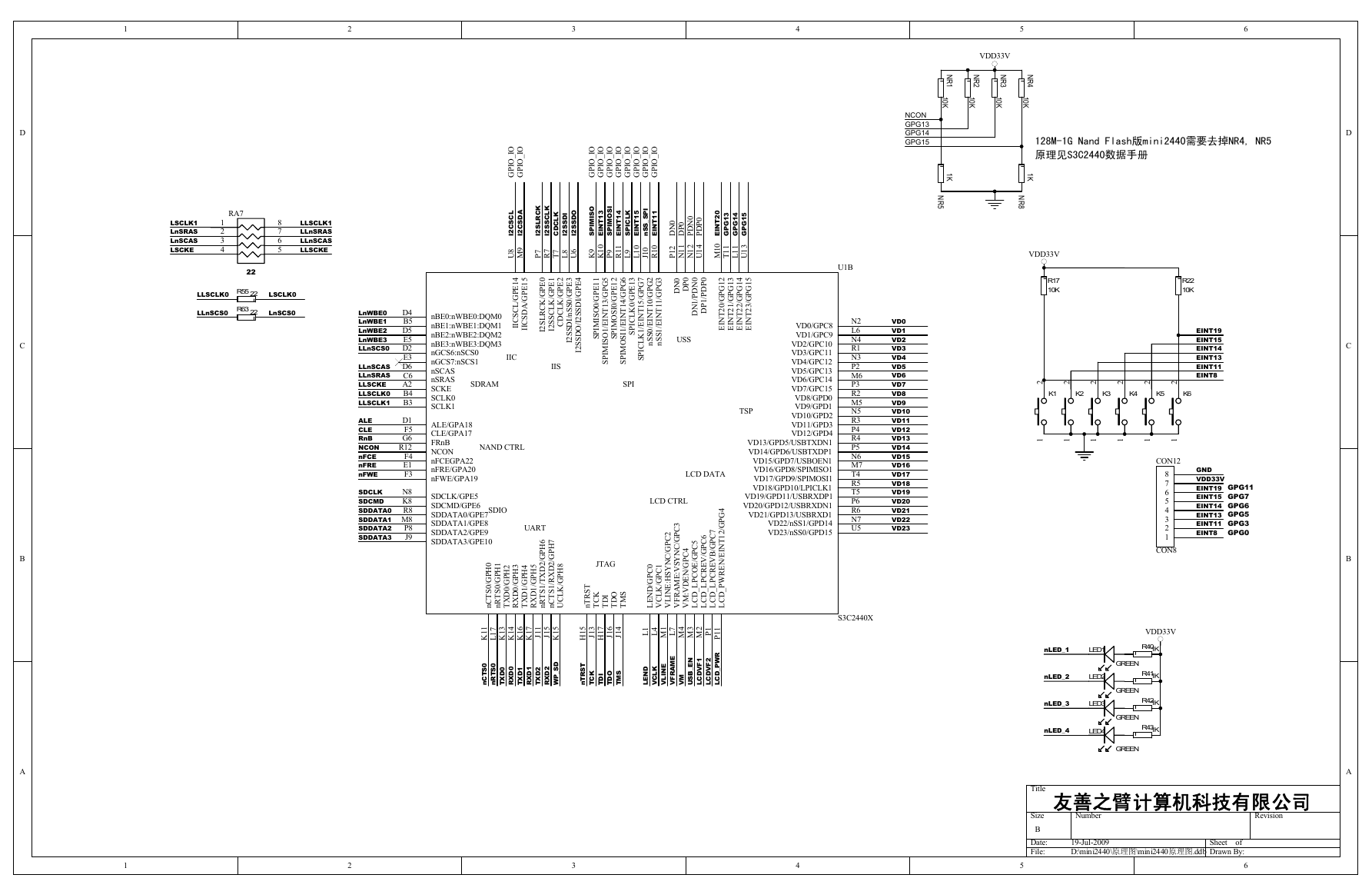

CPU2

02-CPU2.Sch

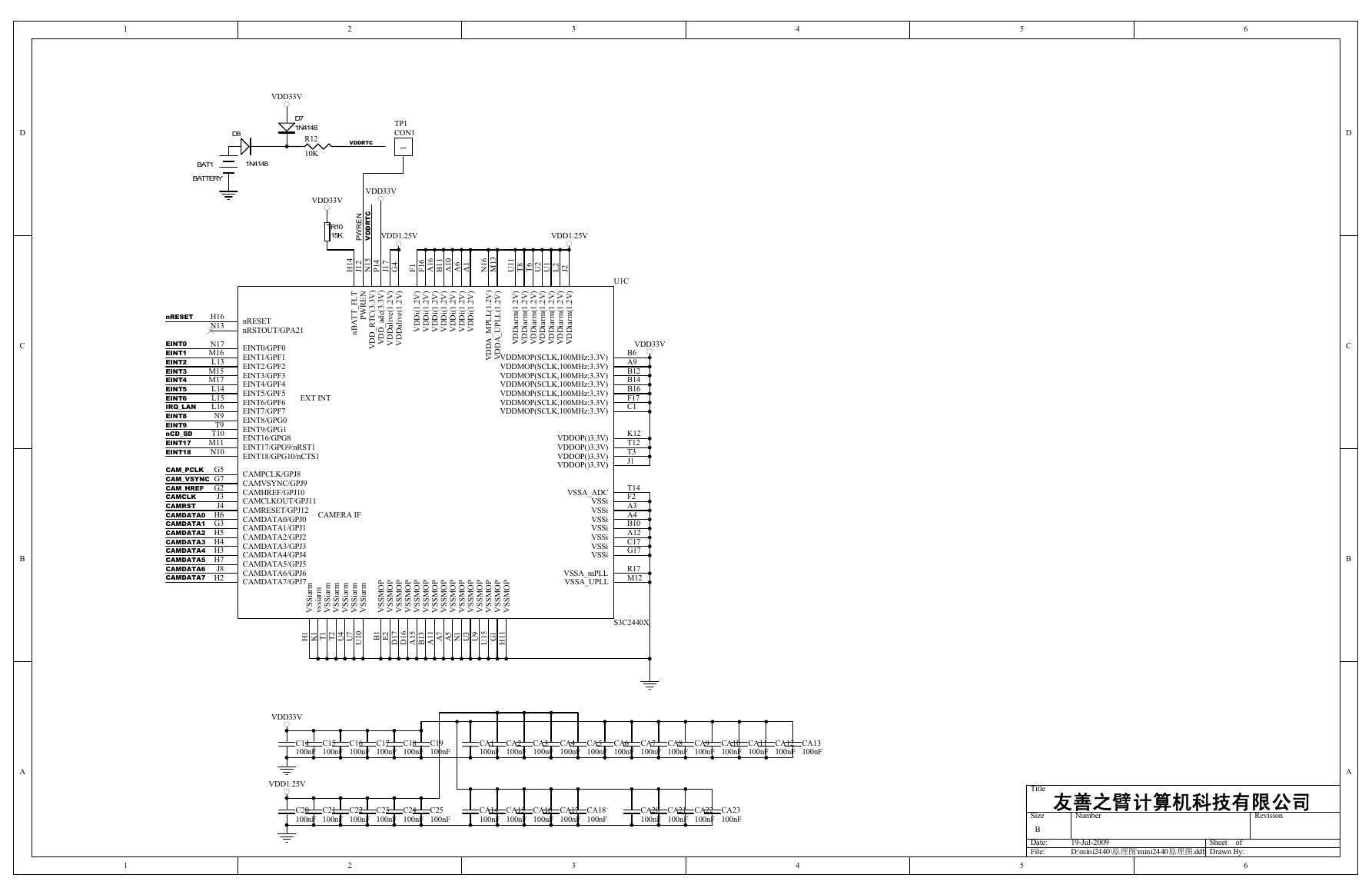

CPU3

03-CPU3.Sch

SDRAM

04-MEM.sch

UART_USB_ETC

05-UART_USB_POWER.sch

Audio

06-Audio.sch

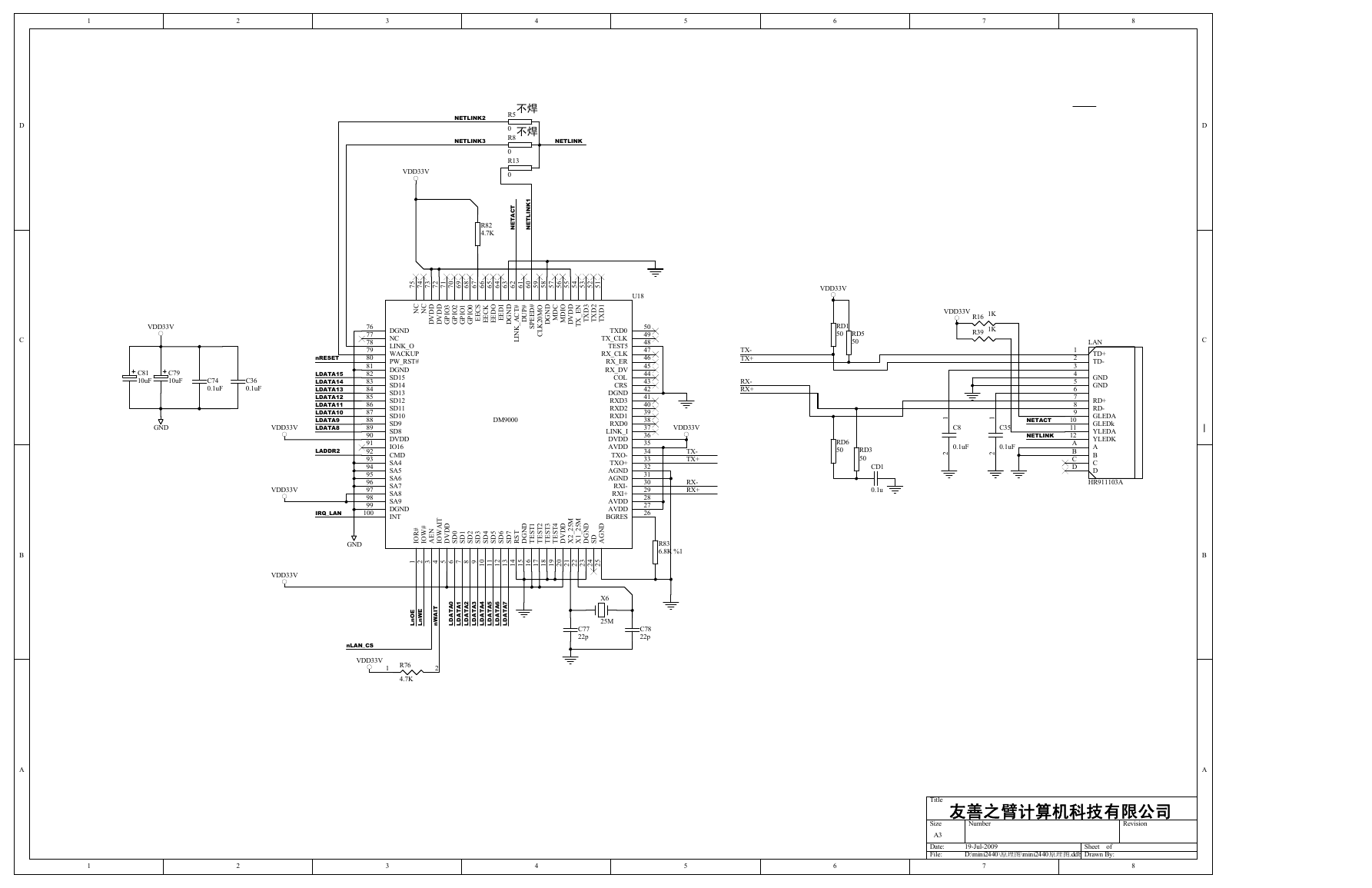

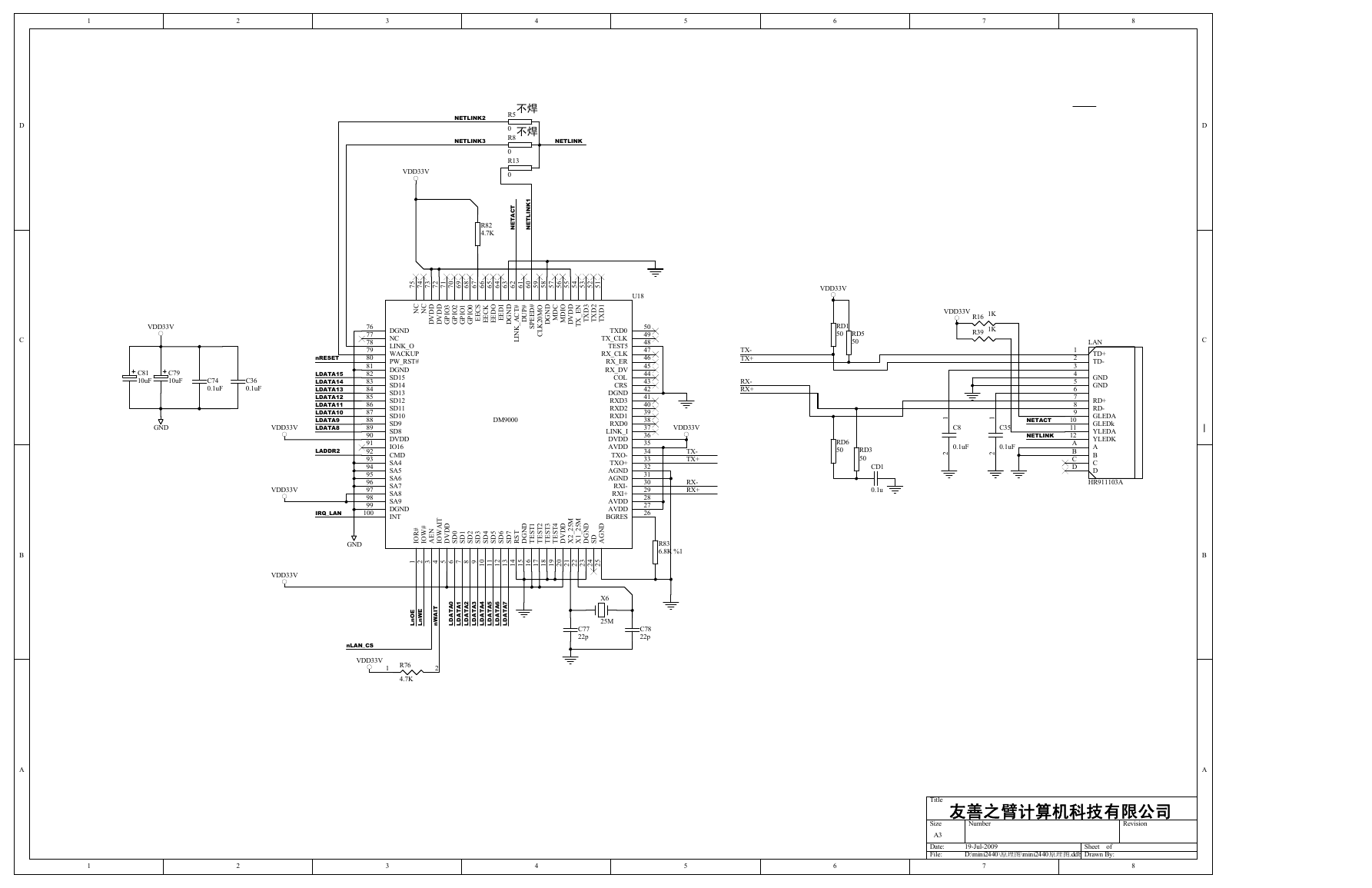

DM9000

07-DM9000.sch

Interface

08-INTERFACE.sch

D

C

B

A

mini2440原理图

1

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

D

C

B

A

�

1

2

3

4

5

6

D

C

B

A

R64

4.7K

1

2

3

VDD33V

NORBOOT

J1

CON3

OM0

NANDBOOT

R35

4.7K

U1A

S2

1

2

3

4

5

CON5

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA16

DATA17

DATA18

DATA19

DATA20

DATA21

DATA22

DATA23

DATA24

DATA25

DATA26

DATA27

DATA28

DATA29

DATA30

DATA31

D12

C12

E11

A13

F10

F11

C13

A14

D13

B15

A17

C14

D15

C15

D14

B17

C16

E15

E14

E13

E12

E16

F15

G13

E17

G12

F14

F12

G11

G16

H13

F13

LDATA0

LDATA1

LDATA2

LDATA3

LDATA4

LDATA5

LDATA6

LDATA7

LDATA8

LDATA9

LDATA10

LDATA11

LDATA12

LDATA13

LDATA14

LDATA15

LDATA16

LDATA17

LDATA18

LDATA19

LDATA20

LDATA21

LDATA22

LDATA23

LDATA24

LDATA25

LDATA26

LDATA27

LDATA28

LDATA29

LDATA30

LDATA31

S3C2440X

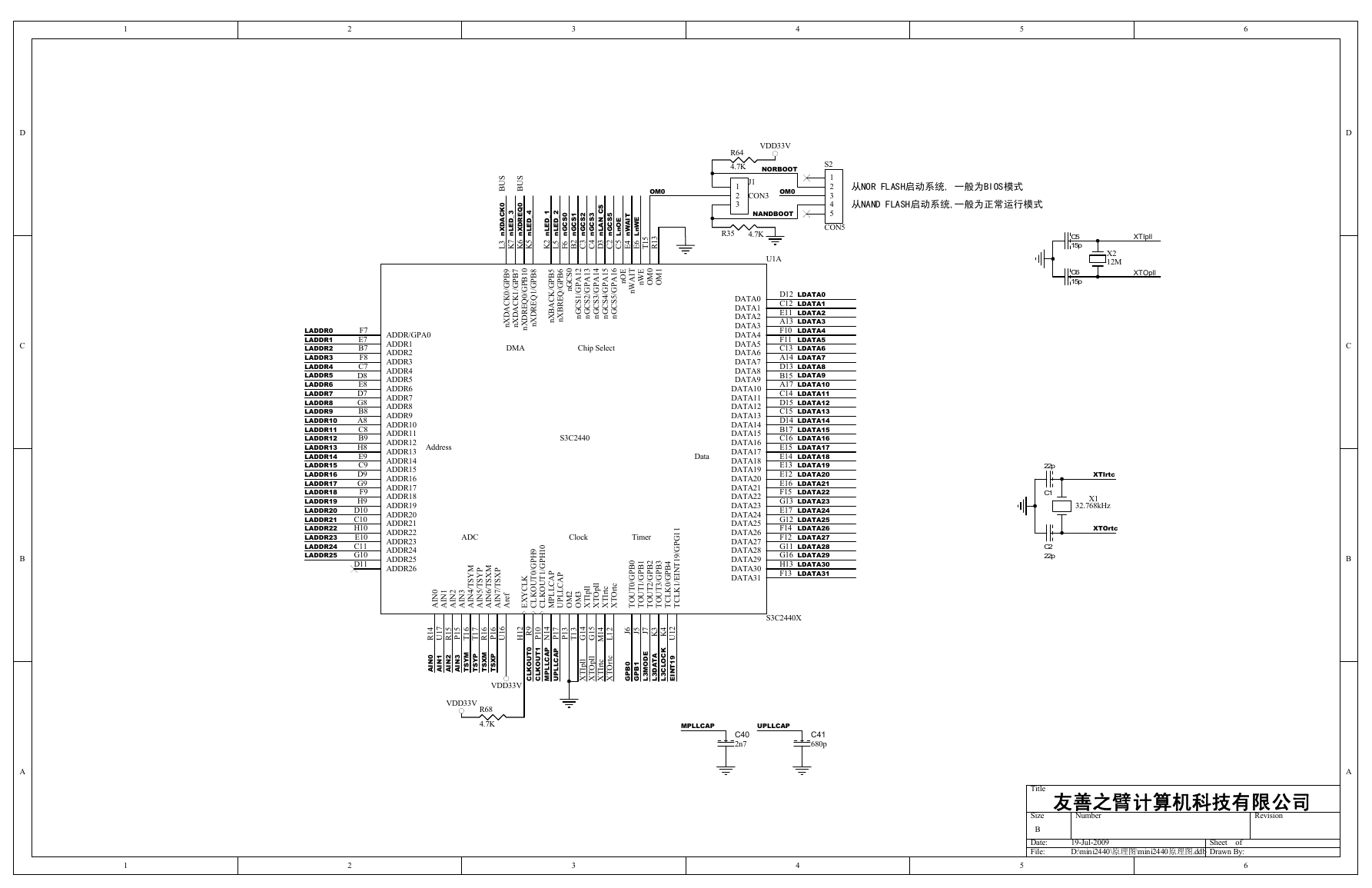

从NOR FLASH启动系统, 一般为BIOS模式

从NAND FLASH启动系统,一般为正常运行模式

C5

15p

C6

15p

X2

12M

XTIpll

XTOpll

XTIrtc

X1

32.768kHz

XTOrtc

22p

C1

C2

22p

1

1

G

P

G

/

9

1

T

N

I

E

/

1

K

L

C

T

LADDR0

LADDR1

LADDR2

LADDR3

LADDR4

LADDR5

LADDR6

LADDR7

LADDR8

LADDR9

LADDR10

LADDR11

LADDR12

LADDR13

LADDR14

LADDR15

LADDR16

LADDR17

LADDR18

LADDR19

LADDR20

LADDR21

LADDR22

LADDR23

LADDR24

LADDR25

F7

E7

B7

F8

C7

D8

E8

D7

G8

B8

A8

C8

B9

H8

E9

C9

D9

G9

F9

H9

D10

C10

H10

E10

C11

G10

D11

ADDR/GPA0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

ADDR20

ADDR21

ADDR22

ADDR23

ADDR24

ADDR25

ADDR26

Address

S

U

B

S

U

B

OM0

0

K

C

A

D

X

n

0

Q

E

R

D

X

n

4

_

D

E

L

n

3

_

D

E

L

n

1

_

D

E

L

n

2

_

D

E

L

n

0

S

C

G

n

1

S

C

G

n

2

S

C

G

n

3

S

C

G

n

S

C

_

N

A

L

n

5

S

C

G

n

T

I

A

W

n

E

W

n

L

E

O

n

L

2

K

5

L

6

F

2

B

3

C

4

C

3

D

2

C

5

C

4

E

6

E

5

1

T

3

1

R

3

L

7

K

6

K

5

K

9

B

P

G

/

0

K

C

A

D

X

n

7

B

P

G

/

1

K

C

A

D

X

n

8

B

P

G

/

1

Q

E

R

D

X

n

0

1

B

P

G

/

0

Q

E

R

D

X

n

E

W

n

0

M

O

1

M

O

E

O

n

T

I

A

W

n

/

/

5

B

P

G

K

C

A

B

X

n

6

B

P

G

Q

E

R

B

X

n

0

S

C

G

n

2

1

A

P

G

/

1

S

C

G

n

3

1

A

P

G

/

2

S

C

G

n

4

1

A

P

G

/

3

S

C

G

n

5

1

A

P

G

/

4

S

C

G

n

6

1

A

P

G

/

5

S

C

G

n

DMA

Chip Select

S3C2440

Data

ADC

Clock

Timer

M

Y

S

T

/

4

N

A

P

Y

S

T

/

5

N

A

M

X

S

T

/

6

N

A

P

X

S

T

/

7

N

A

I

I

I

I

f

e

r

A

0

N

A

1

N

A

2

N

A

3

N

A

I

I

I

I

0

1

H

P

G

/

1

T

U

O

K

L

C

9

H

P

G

/

0

T

U

O

K

L

C

K

L

C

Y

X

E

P

A

C

L

L

P

M

P

A

C

L

L

P

U

l

l

p

O

T

X

l

l

p

I

T

X

c

t

r

I

T

X

c

t

r

O

T

X

2

M

O

3

M

O

0

B

P

G

/

0

T

U

O

T

1

B

P

G

/

1

T

U

O

T

2

B

P

G

/

2

T

U

O

T

3

B

P

G

/

3

T

U

O

T

4

B

P

G

/

0

K

L

C

T

4

1

R

7

1

U

5

1

R

5

1

P

6

1

T

7

1

T

6

1

R

6

1

P

6

1

U

9

R

2

1

H

0

1

P

4

1

N

7

1

P

3

1

P

3

1

T

4

1

G

5

1

G

4

1

M

2

1

L

6

J

5

J

7

J

3

K

4

K

2

1

U

0

T

U

O

K

L

C

1

T

U

O

K

L

C

P

A

C

L

L

P

M

P

A

C

L

L

P

U

0

N

I

A

1

N

I

A

2

N

I

A

3

N

I

A

M

Y

S

T

P

Y

S

T

M

X

S

T

P

X

S

T

VDD33V

VDD33V

R68

4.7K

l

l

p

O

T

X

c

t

r

I

T

X

l

l

p

I

T

X

c

t

r

O

T

X

E

D

O

M

3

L

A

T

A

D

3

L

K

C

O

L

C

3

L

9

1

T

N

I

E

0

B

P

G

1

B

P

G

MPLLCAP

UPLLCAP

C40

2n7

C41

680p

1

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

D

C

B

A

�

1

2

3

4

LSCLK1

LnSRAS

LnSCAS

LSCKE

RA7

1

2

3

4

8

7

6

5

LLSCLK1

LLnSRAS

LLnSCAS

LLSCKE

22

R55 22

R63 22

LLSCLK0

LLnSCS0

LSCLK0

LnSCS0

LnWBE0

LnWBE1

LnWBE2

LnWBE3

LLnSCS0

LLnSCAS

LLnSRAS

LLSCKE

LLSCLK0

LLSCLK1

ALE

CLE

RnB

NCON

nFCE

nFRE

nFWE

SDCLK

SDCMD

SDDATA0

SDDATA1

SDDATA2

SDDATA3

D4

B5

D5

E5

D2

E3

D6

C6

A2

B4

B3

D1

F5

G6

R12

F4

E1

F3

N8

K8

R8

M8

P8

J9

D

C

B

A

O

I

_

O

I

P

G

O

I

_

O

I

P

G

L

C

S

C

2

I

A

D

S

C

2

I

8

U

9

M

4

1

E

P

G

L

C

S

C

5

1

E

P

G

A

D

S

C

/

/

I

I

I

I

O

I

_

O

I

P

G

O

I

_

O

I

P

G

O

I

_

O

I

P

G

O

I

_

O

I

P

G

O

I

_

O

I

P

G

O

I

_

O

I

P

G

O

I

_

O

I

P

G

O

I

_

O

I

P

G

K

C

R

L

S

2

I

K

L

C

S

S

2

I

K

L

C

D

C

I

D

S

S

2

I

O

D

S

S

2

I

O

S

I

M

I

P

S

I

S

O

M

I

P

S

3

1

T

N

I

E

4

1

T

N

I

E

K

L

C

I

P

S

5

1

T

N

I

E

I

P

S

_

S

S

n

1

1

T

N

I

E

7

P

7

R

7

T

8

L

6

U

0

1

K

9

K

1

1

R

0

1

L

0

1

J

0

1

R

9

L

9

P

0

N

D

0

P

D

0

N

D

P

0

P

D

P

2

1

P

1

1

N

2

1

N

4

1

U

0

2

T

N

I

E

3

1

G

P

G

4

1

G

P

G

5

1

G

P

G

0

1

M

1

1

T

1

1

L

3

1

U

/

/

/

0

E

P

G

K

C

R

L

S

2

I

1

E

P

G

K

L

C

S

S

2

I

2

E

P

G

K

L

C

D

C

3

E

P

G

/

0

S

S

n

/

I

D

S

S

2

I

4

E

P

G

/

I

D

S

S

2

I

/

O

D

S

S

2

I

2

G

P

G

/

0

1

T

N

I

E

/

0

S

S

n

3

G

P

G

/

1

1

T

N

I

E

/

1

S

S

n

1

1

E

P

G

/

0

O

S

I

M

I

P

S

2

1

E

P

G

/

0

I

S

O

M

I

P

S

5

G

P

G

/

3

1

T

N

I

E

/

1

O

S

I

M

I

P

S

6

G

P

G

/

4

1

T

N

I

E

/

1

I

S

O

M

I

P

S

3

1

E

P

G

/

0

K

L

C

I

P

S

7

G

P

G

/

5

1

T

N

I

E

/

1

K

L

C

I

P

S

0

N

D

0

P

D

0

N

D

P

/

1

N

D

0

P

D

P

/

1

P

D

USS

2

1

G

P

G

/

0

2

T

N

I

E

3

1

G

P

G

/

1

2

T

N

I

E

4

1

G

P

G

/

2

2

T

N

I

E

5

1

G

P

G

/

3

2

T

N

I

E

TSP

VD0/GPC8

VD1/GPC9

VD2/GPC10

VD3/GPC11

VD4/GPC12

VD5/GPC13

VD6/GPC14

VD7/GPC15

VD8/GPD0

VD9/GPD1

VD10/GPD2

VD11/GPD3

VD12/GPD4

VD13/GPD5/USBTXDN1

VD14/GPD6/USBTXDP1

VD15/GPD7/USBOEN1

VD16/GPD8/SPIMISO1

VD17/GPD9/SPIMOSI1

VD18/GPD10/LPICLK1

VD19/GPD11/USBRXDP1

VD20/GPD12/USBRXDN1

VD21/GPD13/USBRXD1

VD22/nSS1/GPD14

VD23/nSS0/GPD15

nBE0:nWBE0:DQM0

nBE1:nWBE1:DQM1

nBE2:nWBE2:DQM2

nBE3:nWBE3:DQM3

nGCS6:nSCS0

nGCS7:nSCS1

nSCAS

nSRAS

SCKE

SCLK0

SCLK1

SDRAM

IIC

IIS

ALE/GPA18

CLE/GPA17

FRnB

NCON

nFCEGPA22

nFRE/GPA20

nFWE/GPA19

NAND CTRL

SDCLK/GPE5

SDCMD/GPE6

SDDATA0/GPE7

SDDATA1/GPE8

SDDATA2/GPE9

SDDATA3/GPE10

SDIO

UART

6

H

P

G

/

2

D

X

T

/

1

S

T

R

n

7

H

P

G

/

2

D

X

R

/

1

S

T

C

n

/

8

H

P

G

K

L

C

U

0

H

P

G

/

0

S

T

C

n

1

H

P

G

/

0

S

T

R

n

2

H

P

G

/

0

D

X

T

3

H

P

G

/

0

D

X

R

4

H

P

G

/

1

D

X

T

5

H

P

G

/

1

D

X

R

1

1

K

7

1

L

3

1

K

4

1

K

6

1

K

7

1

K

1

1

J

5

1

J

5

1

K

SPI

JTAG

T

S

R

T

n

K

C

T

I

D

T

O

D

T

S

M

T

5

1

H

3

1

J

7

1

H

6

1

J

4

1

J

LCD DATA

LCD CTRL

/

/

3

C

P

G

C

N

Y

S

V

E

M

A

R

F

V

2

C

P

G

C

N

Y

S

H

E

N

I

L

V

:

:

/

/

7

C

P

G

B

V

E

R

C

P

L

_

D

C

L

6

C

P

G

V

E

R

C

P

L

_

D

C

L

/

/

5

C

P

G

E

O

C

P

L

_

D

C

L

4

C

P

G

N

E

D

V

M

V

:

4

G

P

G

/

2

1

T

N

I

E

N

E

R

W

P

_

D

C

L

/

/

0

C

P

G

D

N

E

L

1

C

P

G

K

L

C

V

/

1

L

4

L

1

M

7

L

4

M

3

M

2

M

1

P

1

1

P

0

S

T

C

n

0

S

T

R

n

0

D

X

T

0

D

X

R

1

D

X

T

1

D

X

R

2

D

X

T

2

D

X

R

D

S

_

P

W

T

S

R

T

n

K

C

T

I

D

T

O

D

T

S

M

T

E

M

A

R

F

V

M

V

N

E

_

B

S

U

1

F

V

D

C

L

2

F

V

D

C

L

R

W

P

_

D

C

L

D

N

E

L

K

L

C

V

E

N

I

L

V

5

VDD33V

N

R

1

N

R

2

N

R

3

N

R

4

1

0

K

1

0

K

1

0

K

1

0

K

6

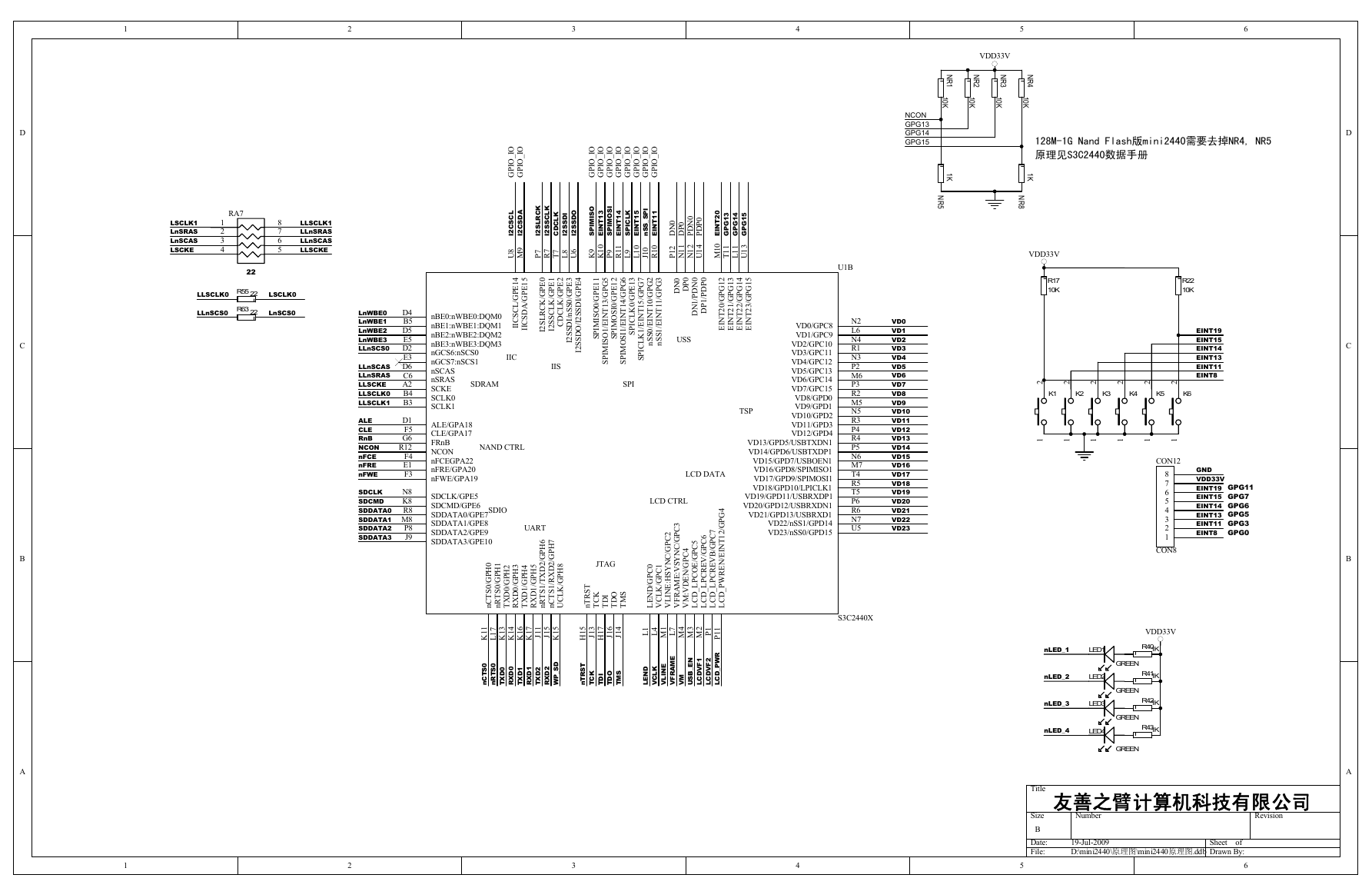

NCON

GPG13

GPG14

GPG15

128M-1G Nand Flash版mini2440需要去掉NR4, NR5

原理见S3C2440数据手册

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VD8

VD9

VD10

VD11

VD12

VD13

VD14

VD15

VD16

VD17

VD18

VD19

VD20

VD21

VD22

VD23

U1B

N2

L6

N4

R1

N3

P2

M6

P3

R2

M5

N5

R3

P4

R4

P5

N6

M7

T4

R5

T5

P6

R6

N7

U5

S3C2440X

1

K

N

R

5

1

K

N

R

8

VDD33V

R17

10K

R22

10K

EINT19

EINT15

EINT14

EINT13

EINT11

EINT8

2

2

2

2

2

2

K1

K2

K3

K4

K5

K6

1

1

1

1

1

1

CON12

8

7

6

5

4

3

2

1

CON8

GND

VDD33V

EINT19

EINT15

EINT14

EINT13

EINT11

EINT8

GPG11

GPG7

GPG6

GPG5

GPG3

GPG0

nLED_1

nLED_2

nLED_3

nLED_4

LED1

LED2

LED3

LED4

VDD33V

R401K

R411K

R421K

R431K

GREEN

GREEN

GREEN

GREEN

D

C

B

A

1

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

�

D

C

B

A

1

2

3

4

5

6

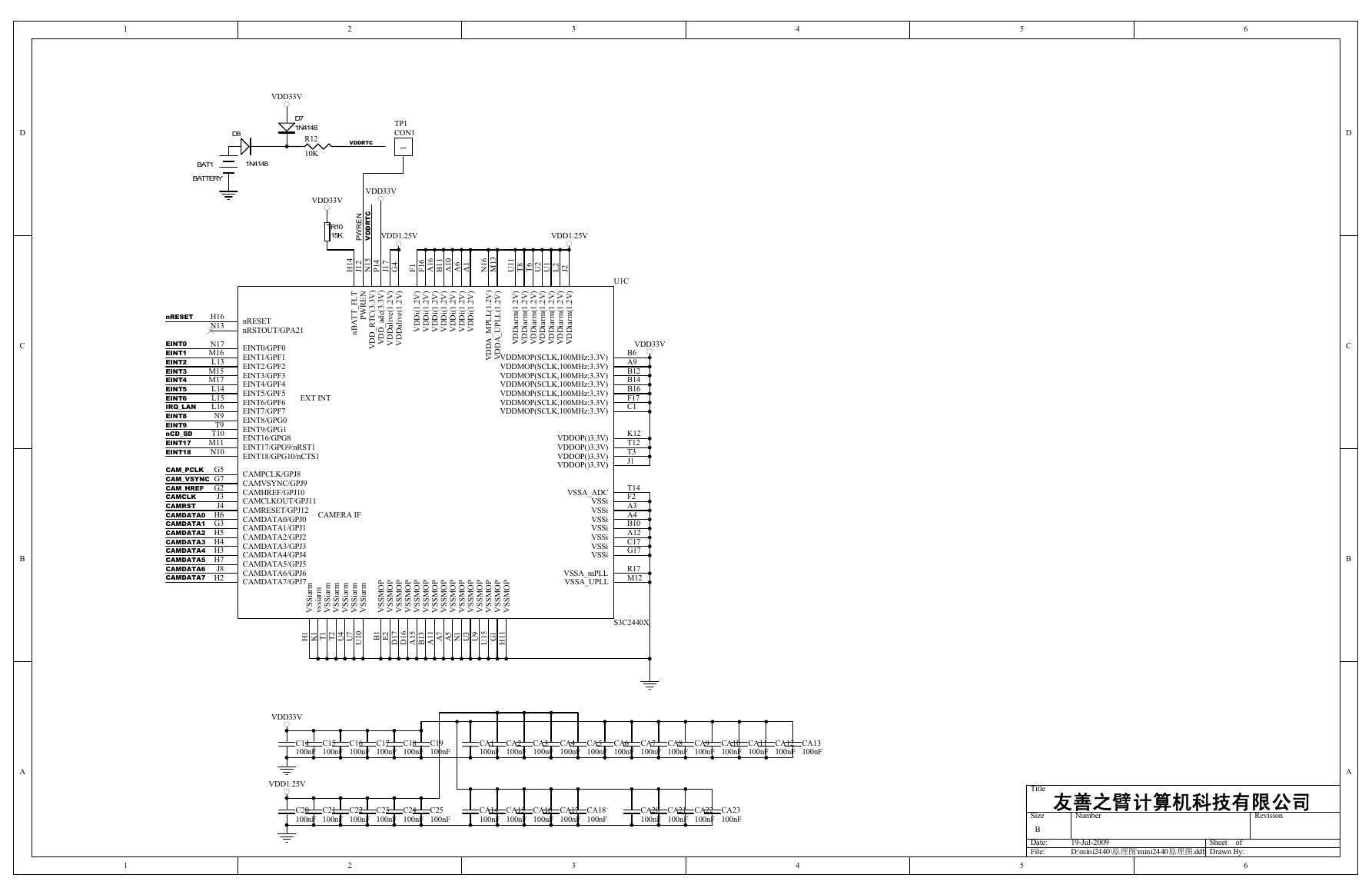

VDD33V

D7

1N4148

R12

10K

D8

BAT1

BATTERY

1N4148

TP1

CON1

1

VDDRTC

VDD33V

VDD33V

R10

15K

N

E

R

W

P

C

T

R

D

D

V

VDD1.25V

VDD1.25V

4

1

H

2

1

J

5

1

N

4

1

P

7

1

J

4

G

6

1

F

6

1

A

1

1

B

0

1

A

1

F

6

A

1

A

6

1

N

3

1

M

1

1

U

8

T

6

T

2

U

1

U

2

L

2

J

N

E

R

W

P

T

L

F

_

T

T

A

B

n

)

)

.

.

V

3

3

(

c

d

a

_

D

D

V

V

3

3

(

C

T

R

_

D

D

V

)

)

V

2

V

2

.

.

1

(

e

v

i

l

a

D

D

V

1

(

e

v

i

l

a

D

D

V

)

)

)

)

)

)

)

V

2

1

(

i

V

2

1

(

i

V

2

1

(

i

V

2

1

(

i

V

2

1

(

i

V

2

1

(

i

V

2

1

(

i

.

.

.

.

.

.

.

D

D

V

D

D

V

D

D

V

D

D

V

D

D

V

D

D

V

D

D

V

)

)

)

)

)

)

)

.

.

.

.

.

.

.

V

2

1

(

m

r

a

i

D

D

V

V

2

1

(

m

r

a

i

D

D

V

V

2

1

(

m

r

a

i

D

D

V

V

2

1

(

m

r

a

i

D

D

V

V

2

1

(

m

r

a

i

D

D

V

V

2

1

(

m

r

a

i

D

D

V

V

2

1

(

m

r

a

i

D

D

V

)

)

.

.

V

2

1

(

L

L

P

M

_

A

D

D

V

V

2

1

(

L

L

P

U

_

A

D

D

V

VDDMOP(SCLK,100MHz:3.3V)

VDDMOP(SCLK,100MHz:3.3V)

VDDMOP(SCLK,100MHz:3.3V)

VDDMOP(SCLK,100MHz:3.3V)

VDDMOP(SCLK,100MHz:3.3V)

VDDMOP(SCLK,100MHz:3.3V)

VDDMOP(SCLK,100MHz:3.3V)

U1C

VDD33V

B6

A9

B12

B14

B16

F17

C1

nRESET

EINT0

EINT1

EINT2

EINT3

EINT4

EINT5

EINT6

IRQ_LAN

EINT8

EINT9

nCD_SD

EINT17

EINT18

H16

N13

N17

M16

L13

M15

M17

L14

L15

L16

N9

T9

T10

M11

N10

CAM_PCLK

CAM_VSYNC

CAM_HREF

CAMCLK

CAMRST

CAMDATA0

CAMDATA1

CAMDATA2

CAMDATA3

CAMDATA4

CAMDATA5

CAMDATA6

CAMDATA7

G5

G7

G2

J3

J4

H6

G3

H5

H4

H3

H7

J8

H2

nRESET

nRSTOUT/GPA21

EINT0/GPF0

EINT1/GPF1

EINT2/GPF2

EINT3/GPF3

EINT4/GPF4

EINT5/GPF5

EINT6/GPF6

EINT7/GPF7

EINT8/GPG0

EINT9/GPG1

EINT16/GPG8

EINT17/GPG9/nRST1

EINT18/GPG10/nCTS1

EXT INT

CAMPCLK/GPJ8

CAMVSYNC/GPJ9

CAMHREF/GPJ10

CAMCLKOUT/GPJ11

CAMRESET/GPJ12

CAMDATA0/GPJ0

CAMDATA1/GPJ1

CAMDATA2/GPJ2

CAMDATA3/GPJ3

CAMDATA4/GPJ4

CAMDATA5/GPJ5

CAMDATA6/GPJ6

CAMDATA7/GPJ7

VDDOP()3.3V)

VDDOP()3.3V)

VDDOP()3.3V)

VDDOP()3.3V)

VSSA_ADC

VSSi

VSSi

VSSi

VSSi

VSSi

VSSi

VSSi

VSSA_mPLL

VSSA_UPLL

K12

T12

T3

J1

T14

F2

A3

A4

B10

A12

C17

G17

R17

M12

S3C2440X

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

P

O

M

S

S

V

CAMERA IF

m

r

a

i

S

S

V

m

r

a

i

s

s

v

m

r

a

i

m

r

a

i

m

r

a

i

m

r

a

i

m

r

a

i

S

S

V

S

S

V

S

S

V

S

S

V

S

S

V

1

H

1

K

1

T

2

T

4

U

7

U

0

1

U

1

B

2

E

7

1

D

6

1

D

5

1

A

3

1

B

1

1

A

7

A

5

A

1

N

3

U

9

U

1

G

5

1

U

1

1

H

VDD33V

C14

100nF

C15

100nF

C16

100nF

C17

100nF

C18

100nF

C19

100nF

CA1

100nF

CA2

100nF

CA3

100nF

CA4

100nF

CA5

100nF

CA6

100nF

CA7

100nF

CA8

100nF

CA9

100nF

CA10

100nF

CA11

100nF

CA12

100nF

CA13

100nF

VDD1.25V

C20

100nF

C21

100nF

C22

100nF

C23

100nF

C24

100nF

C25

100nF

CA14

100nF

CA15

100nF

CA16

100nF

CA17

100nF

CA18

100nF

CA20

100nF

CA21

100nF

CA22

100nF

CA23

100nF

1

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

D

C

B

A

�

1

2

LADDR2

LADDR3

LADDR4

LADDR5

LADDR6

LADDR7

LADDR8

LADDR9

LADDR10

LADDR11

LADDR12

LADDR13

LADDR14

LADDR24

LADDR25

LnWBE0

LnWBE1

LSCKE

LSCLK0

23

24

25

26

29

30

31

32

33

34

22

35

36

20

21

15

39

37

38

28

41

54

6

12

46

52

U6

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

BA0

BA1

LDQM

UDQM

SCKE

SCLK

VSS0

VSS1

VSS2

VSSQ0

VSSQ1

VSSQ2

VSSQ3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

nSCS

nSRAS

nSCAS

nWE

VDD0

VDD1

VDD2

VDDQ0

VDDQ1

VDDQ2

VDDQ3

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

LDATA0

LDATA1

LDATA2

LDATA3

LDATA4

LDATA5

LDATA6

LDATA7

LDATA8

LDATA9

LDATA10

LDATA11

LDATA12

LDATA13

LDATA14

LDATA15

LnSCS0

LnSRAS

LnSCAS

LnWE

VDD33V

19

18

17

16

1

14

27

3

9

43

49

HY57V561620(32MB)/或其他兼容型号

VDD33V

C30

100nF

C31

100nF

C32

100nF

C33

100nF

NAND FLASH

I/O7

I/O6

I/O5

I/O4

I/O3

I/O2

I/O1

I/O0

WP

VCC

VCC

LDATA7

LDATA6

LDATA5

LDATA4

LDATA3

LDATA2

LDATA1

LDATA0

VDD33V

44

43

42

41

32

31

30

29

19

12

37

C10

0.1uF

VDD33V

U2

K9F1208

RnB

nFCE

CLE

ALE

nFWE

nFRE

R6

10K

7

9

16

17

18

8

6

13

36

R/B

CE

CLE

ALE

WE

RE

SE

VSS

VSS

NandFlash可兼容三星或现代64M/128M-1G各型号

D

C

B

A

1

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

nSCS

nSRAS

nSCAS

nWE

VDD0

VDD1

VDD2

VDDQ0

VDDQ1

VDDQ2

VDDQ3

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

19

18

17

16

1

14

27

3

9

43

49

LADDR2

LADDR3

LADDR4

LADDR5

LADDR6

LADDR7

LADDR8

LADDR9

LADDR10

LADDR11

LADDR12

LADDR13

LADDR14

LADDR24

LADDR25

LnWBE2

LnWBE3

LSCKE

LSCLK1

23

24

25

26

29

30

31

32

33

34

22

35

36

20

21

15

39

37

38

28

41

54

6

12

46

52

U7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

BA0

BA1

LDQM

UDQM

SCKE

SCLK

VSS0

VSS1

VSS2

VSSQ0

VSSQ1

VSSQ2

VSSQ3

LDATA16

LDATA17

LDATA18

LDATA19

LDATA20

LDATA21

LDATA22

LDATA23

LDATA24

LDATA25

LDATA26

LDATA27

LDATA28

LDATA29

LDATA30

LDATA31

LnSCS0

LnSRAS

LnSCAS

LnWE

VDD33V

HY57V561620 (32MB)/或其他兼容型号

VDD33V

C27

100nF

C28

100nF

C29

100nF

NOR FLASH

4

5

6

VDD33V

VDD33V

4

3

2

1

5

6

7

8

4

3

2

1

RA8

RA9

5

6

7

8

nCD_SD

WP_SD

SDDATA1

SDDATA0

SDCLK

SDCMD

SDDATA3

SDDATA2

VDD33V

CON7

nCD

WP

DAT1

DAT0

GND

CLK

VDD

GND

CMD

CD/DAT3

DAT2

11

10

8

7

6

5

4

3

2

1

9

SD/MMC CARD

PAD4

PAD3

PAD2

PAD1

15

14

13

12

LADDR1

LADDR2

LADDR3

LADDR4

LADDR5

LADDR6

LADDR7

LADDR8

LADDR9

LADDR10

LADDR11

LADDR12

LADDR13

LADDR14

LADDR15

LADDR16

LADDR17

LADDR18

LADDR19

LADDR20

LADDR21

LADDR22

VDD33V

25

24

23

22

21

20

19

18

8

7

6

5

4

3

2

1

48

17

16

9

10

13

15

47

27

46

U10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20/NC

A21/NC

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

VDD

OE

WE

CE

NC

NC

VSS

VSS

/RST/NC

/WP

29

31

33

35

38

40

42

44

30

32

34

36

39

41

43

45

37

28

11

26

12

14

AM29LV160DB/SST39VF1601

NOR Flash最大可兼容8M

LDATA0

LDATA1

LDATA2

LDATA3

LDATA4

LDATA5

LDATA6

LDATA7

LDATA8

LDATA9

LDATA10

LDATA11

LDATA12

LDATA13

LDATA14

LDATA15

VDD33V

LnOE

LnWE

nGCS0

nRESET

VDD33V

R7

10K

R69

10K

不焊

D

C

B

A

�

D

C

B

A

1

2

3

4

5

6

7

8

VDD33V

NETLINK

NETLINK2

NETLINK3

R82

4.7K

不焊

不焊

R5

0

R8

0

R13

0

1

K

N

I

L

T

E

N

T

C

A

T

E

N

VDD33V

C81

10uF

C79

10uF

C74

0.1uF

C36

0.1uF

GND

VDD33V

nRESET

LDATA15

LDATA14

LDATA13

LDATA12

LDATA11

LDATA10

LDATA9

LDATA8

LADDR2

VDD33V

VDD33V

IRQ_LAN

GND

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

DGND

NC

LINK_O

WACKUP

PW_RST#

DGND

SD15

SD14

SD13

SD12

SD11

SD10

SD9

SD8

DVDD

IO16

CMD

SA4

SA5

SA6

SA7

SA8

SA9

DGND

INT

T

I

A

W

O

I

D

D

V

D

#

R

O

#

W

O

I

I

N

E

A

0

D

S

1

D

S

2

D

S

3

D

S

4

D

S

5

D

S

6

D

S

7

D

S

T

S

R

D

N

G

D

1

T

S

E

T

2

T

S

E

T

3

T

S

E

T

4

T

S

E

T

D

D

V

D

M

5

2

_

2

X

M

5

2

_

1

X

D

N

G

D

D

N

G

A

D

S

1

2

3

4

5

6

7

8

9

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

1

0

2

1

2

2

2

3

2

4

2

5

2

5

7

4

7

3

7

2

7

1

7

0

7

9

6

8

6

7

6

6

6

5

6

4

6

3

6

2

6

1

6

0

6

9

5

8

5

7

5

6

5

5

5

4

5

3

5

2

5

1

5

C

N

C

N

D

D

V

D

D

D

V

D

3

O

I

P

G

2

O

I

P

G

1

O

I

P

G

0

O

I

P

G

S

C

E

E

K

C

E

E

O

D

E

E

I

D

E

E

D

N

G

D

D

N

G

D

C

D

M

I

O

D

M

D

D

V

D

N

E

_

X

T

3

D

X

T

2

D

X

T

1

D

X

T

#

P

U

D

#

D

E

E

P

S

O

M

0

2

K

L

C

#

T

C

A

_

K

N

I

L

DM9000

TXD0

TX_CLK

TEST5

RX_CLK

RX_ER

RX_DV

COL

CRS

DGND

RXD3

RXD2

RXD1

RXD0

LINK_I

DVDD

AVDD

TXO-

TXO+

AGND

AGND

RXI-

RXI+

AVDD

AVDD

BGRES

VDD33V

RD1

50 RD5

50

VDD33V

R16 1K

R39 1K

1

1

C8

0.1uF

2

2

NETACT

NETLINK

C35

0.1uF

RD6

50

RD3

50

CD1

0.1u

1

2

3

4

5

6

7

8

9

10

11

12

A

B

C

D

LAN

TD+

TD-

GND

GND

RD+

RD-

GLEDA

GLEDk

YLEDA

YLEDK

A

B

C

D

HR911103A

TX-

TX+

RX-

RX+

U18

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

VDD33V

TX-

TX+

RX-

RX+

R83

6.8K %1

E

O

n

L

E

W

n

L

T

I

A

W

n

0

A

T

A

D

L

1

A

T

A

D

L

2

A

T

A

D

L

3

A

T

A

D

L

4

A

T

A

D

L

5

A

T

A

D

L

6

A

T

A

D

L

7

A

T

A

D

L

X6

25M

C77

22p

C78

22p

nLAN_CS

VDD33V

1

R76

4.7K

2

1

2

3

4

5

6

Title

Size

A3

Date:

File:

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

7

8

D

C

B

A

�

1

2

3

4

5

6

VDD33V

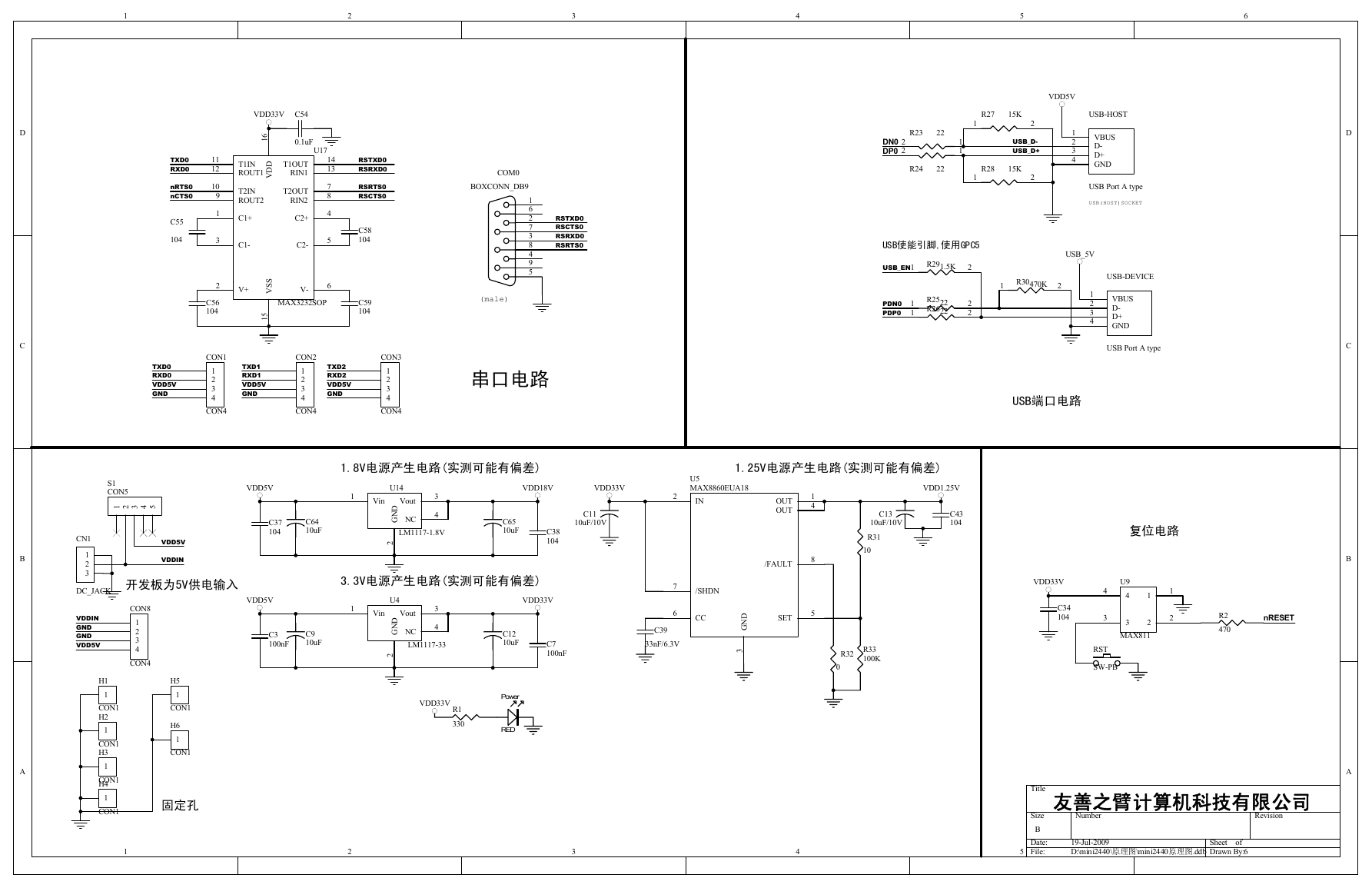

C54

6

1

0.1uF

T1IN

ROUT1

D

D

V

T2IN

ROUT2

T1OUT

RIN1

T2OUT

RIN2

C1+

C1-

C2+

C2-

V+

S

S

V

V-

MAX3232SOP

5

1

U17

14

13

7

8

4

5

6

TXD0

RXD0

nRTS0

nCTS0

C55

104

11

12

10

9

1

3

2

C56

104

RSTXD0

RSRXD0

RSRTS0

RSCTS0

C58

104

C59

104

TXD0

RXD0

VDD5V

GND

CON1

1

2

3

4

CON4

TXD1

RXD1

VDD5V

GND

CON2

CON3

1

2

3

4

TXD2

RXD2

VDD5V

GND

1

2

3

4

CON4

CON4

COM0

BOXCONN_DB9

1

6

2

7

3

8

4

9

5

RSTXD0

RSCTS0

RSRXD0

RSRTS0

(male)

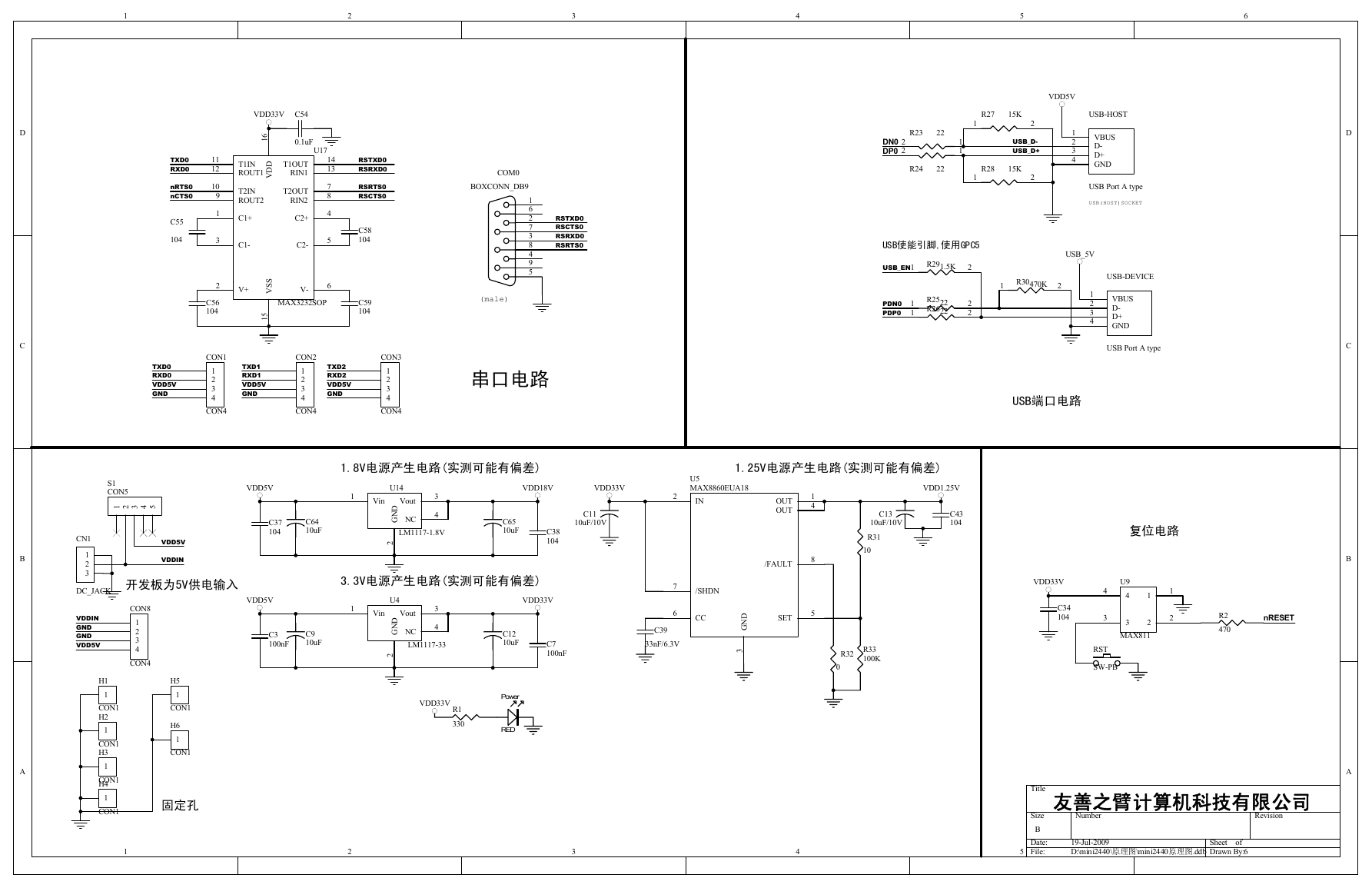

串口电路

DN0

DP0

2

2

R23

22

R24

22

R27

15K

2

USB_D-

USB_D+

R28

15K

2

1

1

1

1

VDD5V

USB-HOST

1

2

3

4

VBUS

D-

D+

GND

USB Port A type

USB(HOST)SOCKET

USB使能引脚,使用GPC5

1

USB_EN

R291.5K

PDN0

PDP0

1

1

R2522

R2622

2

2

2

1

R30470K

2

USB_5V

USB-DEVICE

1

2

3

4

VBUS

D-

D+

GND

USB Port A type

USB端口电路

S1

CON5

12345

CN1

1

2

3

VDD5V

VDDIN

DC_JACK

开发板为5V供电输入

VDDIN

GND

GND

VDD5V

CON8

1

2

3

4

CON4

H5

1

CON1

H6

1

CON1

固定孔

H1

1

CON1

H2

1

CON1

H3

1

CON1

H4

1

CON1

1

1.8V电源产生电路(实测可能有偏差)

VDD5V

C37

104

C64

10uF

1

Vin

U14

Vout

NC

D

N

G

3

4

LM1117-1.8V

2

VDD18V

VDD33V

C11

10uF/10V

C65

10uF

C38

104

3.3V电源产生电路(实测可能有偏差)

VDD5V

C3

100nF

C9

10uF

1

Vin

U4

D

N

G

Vout

3

4

NC

LM1117-33

2

VDD33V

R1

330

VDD33V

C7

100nF

C12

10uF

Power

RED

2

7

6

C39

33nF/6.3V

U5

MAX8860EUA18

IN

/SHDN

CC

D

N

G

3

1.25V电源产生电路(实测可能有偏差)

VDD1.25V

C43

104

C13

10uF/10V

R31

10

OUT

OUT

/FAULT

SET

1

4

8

5

R33

100K

R32

0

复位电路

VDD33V

C34

104

4

3

U9

4

1

3

2

MAX811

1

2

RST

SW-PB

R2

470

nRESET

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

D

C

B

A

D

C

B

A

�

1

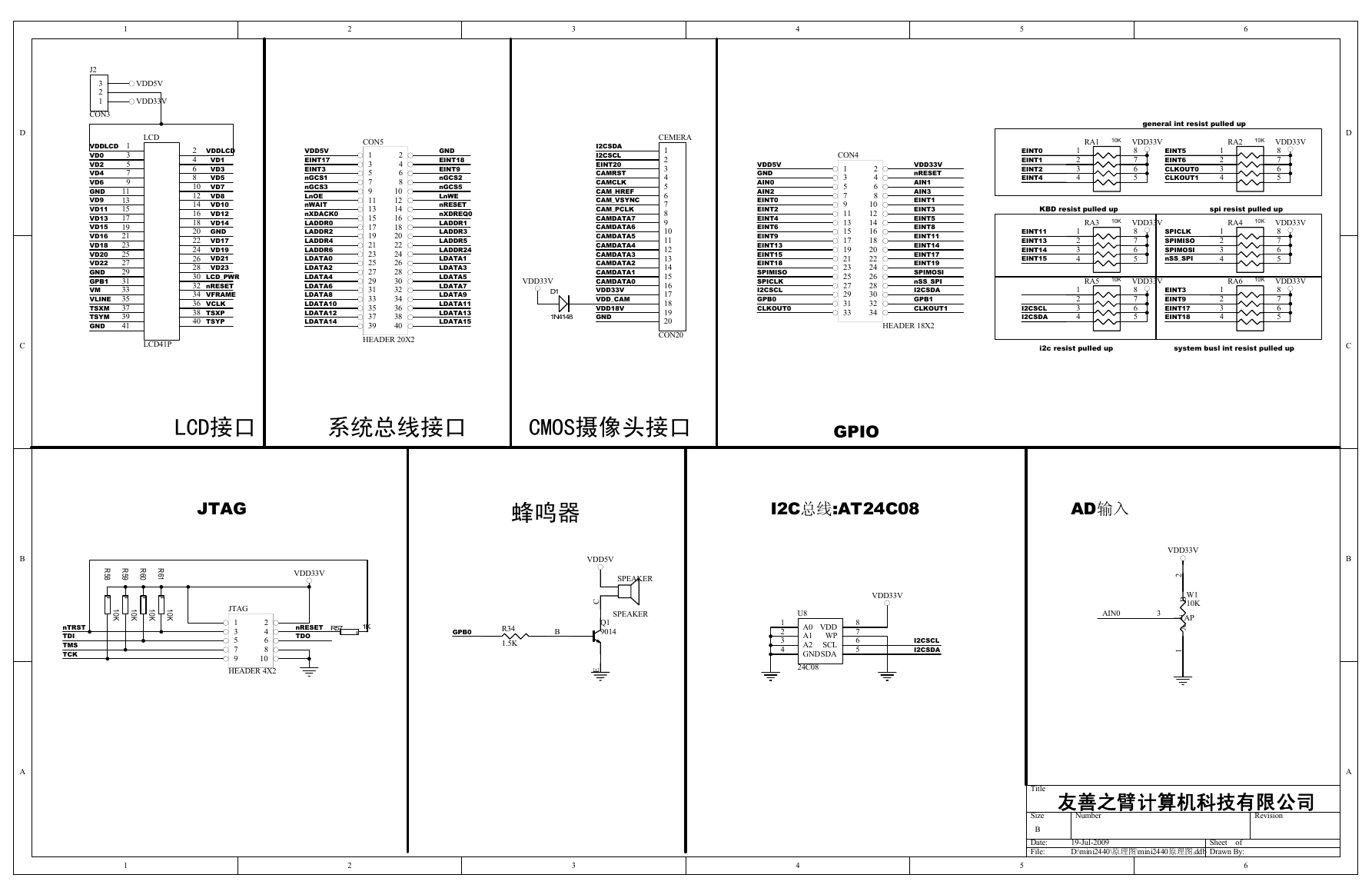

J2

3

2

1

CON3

VDDLCD

VD0

VD2

VD4

VD6

GND

VD9

VD11

VD13

VD15

VD16

VD18

VD20

VD22

GND

GPB1

VM

VLINE

TSXM

TSYM

GND

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

VDD5V

VDD33V

LCD

LCD41P

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

VDDLCD

VD1

VD3

VD5

VD7

VD8

VD10

VD12

VD14

GND

VD17

VD19

VD21

VD23

LCD_PWR

nRESET

VFRAME

VCLK

TSXP

TSYP

2

3

4

5

6

VDD5V

EINT17

EINT3

nGCS1

nGCS3

LnOE

nWAIT

nXDACK0

LADDR0

LADDR2

LADDR4

LADDR6

LDATA0

LDATA2

LDATA4

LDATA6

LDATA8

LDATA10

LDATA12

LDATA14

CON5

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

HEADER 20X2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

GND

EINT18

EINT9

nGCS2

nGCS5

LnWE

nRESET

nXDREQ0

LADDR1

LADDR3

LADDR5

LADDR24

LDATA1

LDATA3

LDATA5

LDATA7

LDATA9

LDATA11

LDATA13

LDATA15

I2CSDA

I2CSCL

EINT20

CAMRST

CAMCLK

CAM_HREF

CAM_VSYNC

CAM_PCLK

CAMDATA7

CAMDATA6

CAMDATA5

CAMDATA4

CAMDATA3

CAMDATA2

CAMDATA1

CAMDATA0

VDD33V

VDD_CAM

VDD18V

GND

CEMERA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

CON20

VDD33V

D1

1N4148

VDD5V

GND

AIN0

AIN2

EINT0

EINT2

EINT4

EINT6

EINT9

EINT13

EINT15

EINT18

SPIMISO

SPICLK

I2CSCL

GPB0

CLKOUT0

CON4

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

VDD33V

nRESET

AIN1

AIN3

EINT1

EINT3

EINT5

EINT8

EINT11

EINT14

EINT17

EINT19

SPIMOSI

nSS_SPI

I2CSDA

GPB1

CLKOUT1

HEADER 18X2

general int resist pulled up

EINT0

EINT1

EINT2

EINT4

RA1

1

2

3

4

10K VDD33V

8

7

6

5

EINT5

EINT6

CLKOUT0

CLKOUT1

RA2

1

2

3

4

10K VDD33V

8

7

6

5

KBD resist pulled up

spi resist pulled up

EINT11

EINT13

EINT14

EINT15

I2CSCL

I2CSDA

RA3

RA5

1

2

3

4

1

2

3

4

10K VDD33V

8

7

6

5

10K VDD33V

8

7

6

5

SPICLK

SPIMISO

SPIMOSI

nSS_SPI

EINT3

EINT9

EINT17

EINT18

RA4

RA6

1

2

3

4

1

2

3

4

10K VDD33V

8

7

6

5

10K VDD33V

8

7

6

5

i2c resist pulled up

system busl int resist pulled up

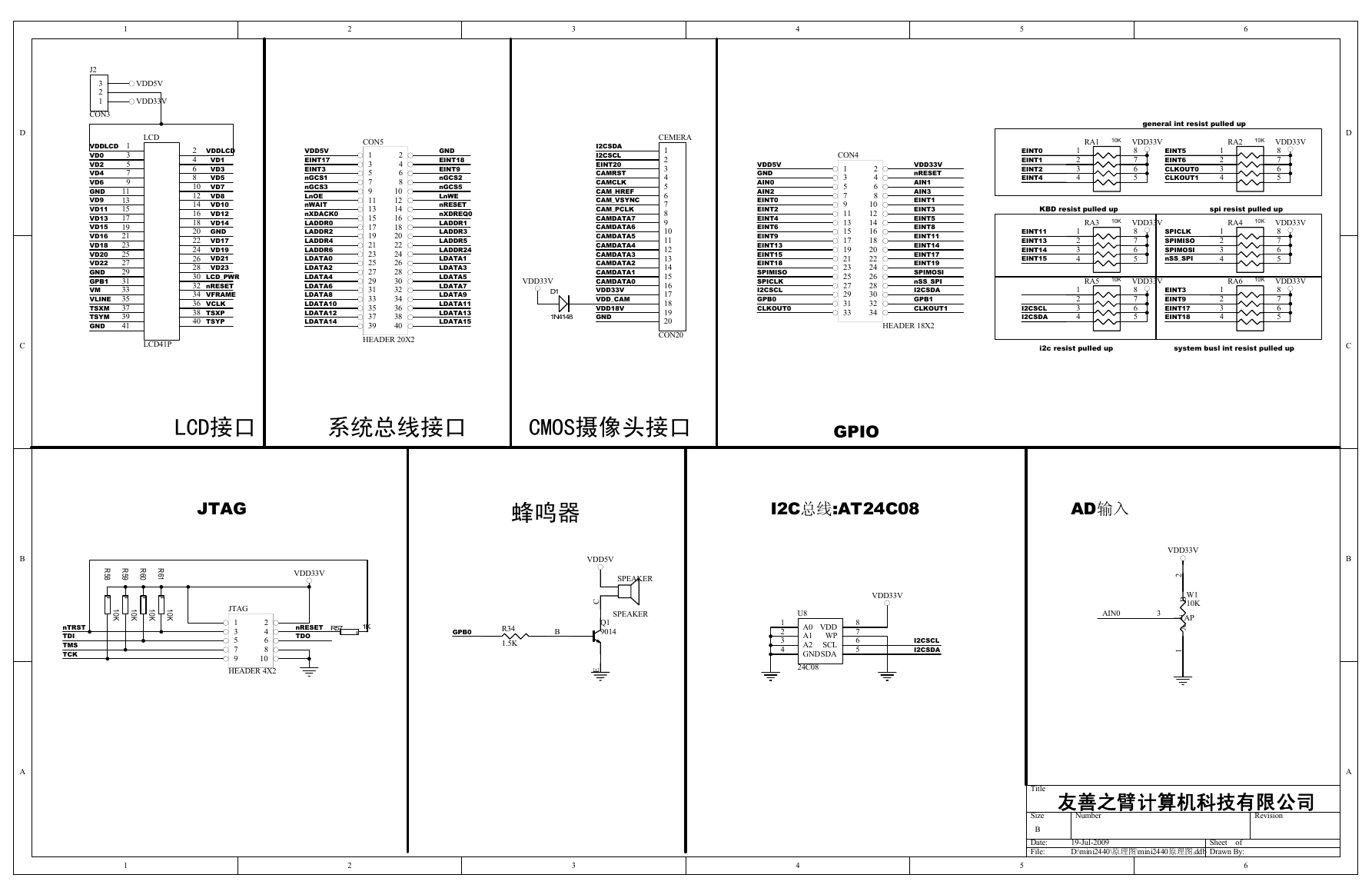

LCD接口

系统总线接口

CMOS摄像头接口

GPIO

JTAG

蜂鸣器

I2C总线:AT24C08

AD输入

R

5

8

R

5

9

R

6

0

R

6

1

VDD33V

1

0

K

1

0

K

1

0

K

1

0

K

nTRST

TDI

TMS

TCK

JTAG

1

3

5

7

9

2

4

6

8

10

HEADER 4X2

nRESET

TDO

R57

1K

GPB0

R34

1.5K

B

VDD5V

SPEAKER

C

SPEAKER

Q1

9014

E

VDD33V

I2CSCL

I2CSDA

1

2

3

4

U8

VDD

WP

SCL

SDA

A0

A1

A2

GND

24C08

8

7

6

5

VDD33V

2

B

W1

10K

TAP

A

1

AIN0

3

D

C

B

A

D

C

B

A

1

2

3

4

Title

Size

B

Date:

File:

5

友善之臂计算机科技有限公司

Number

Revision

19-Jul-2009

Sheet of

D:\mini2440\原理图\mini2440原理图.ddb Drawn By:

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc