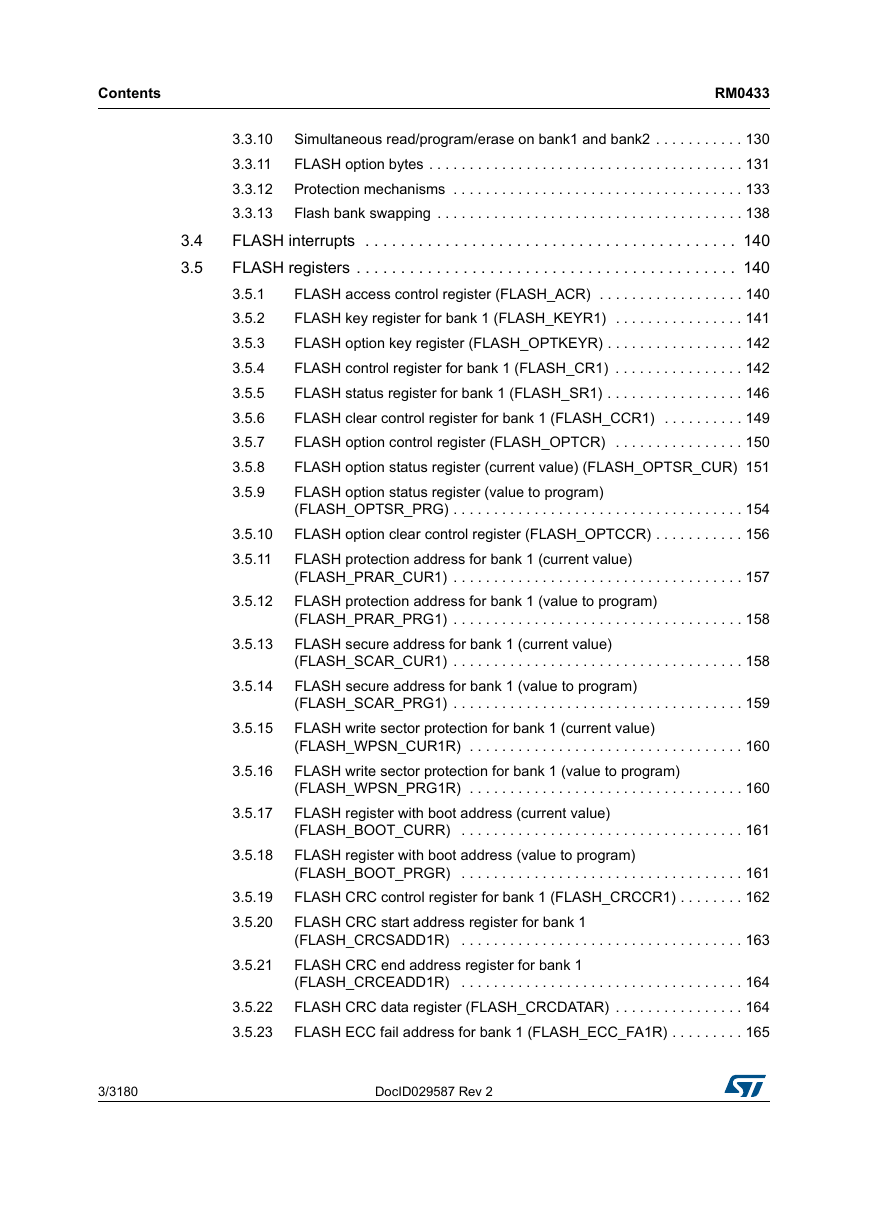

1 Documentation conventions

1.1 List of abbreviations for registers

1.2 Glossary

1.3 Peripheral availability

2 Memory and bus architecture

2.1 System architecture

2.1.1 Bus matrices

2.1.2 Bus-to-bus bridges

2.1.3 Inter-domain buses

2.1.4 CPU buses

2.1.5 Bus master peripherals

2.1.6 Clocks to functional blocks

2.2 Memory organization

2.2.1 Introduction

2.2.2 Memory map and register boundary addresses

2.3 Embedded SRAM

2.4 Flash memory overview

2.5 Boot configuration

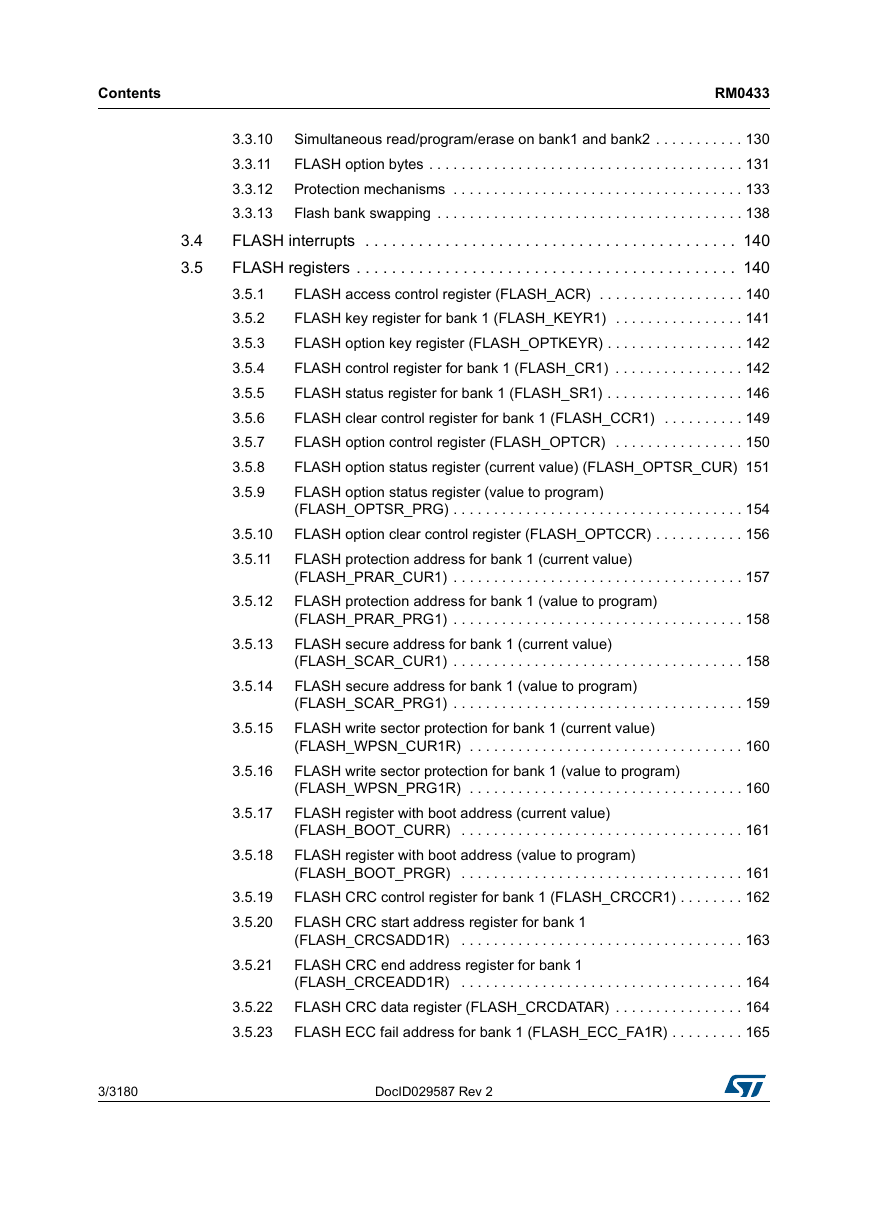

3 Embedded Flash memory (FLASH)

3.1 Introduction

3.2 FLASH main features

3.3 FLASH functional description

3.3.1 Block diagram

3.3.2 Pins and internal signals

3.3.3 Flash memory architecture

3.3.4 Flash read operations

3.3.5 Error code correction (ECC)

3.3.6 Cyclic redundancy check module

3.3.7 Flash program and erase operations

3.3.8 Changing user option bytes

3.3.9 Flash interface error flags

3.3.10 Simultaneous read/program/erase on bank1 and bank2

3.3.11 FLASH option bytes

3.3.12 Protection mechanisms

3.3.13 Flash bank swapping

3.4 FLASH interrupts

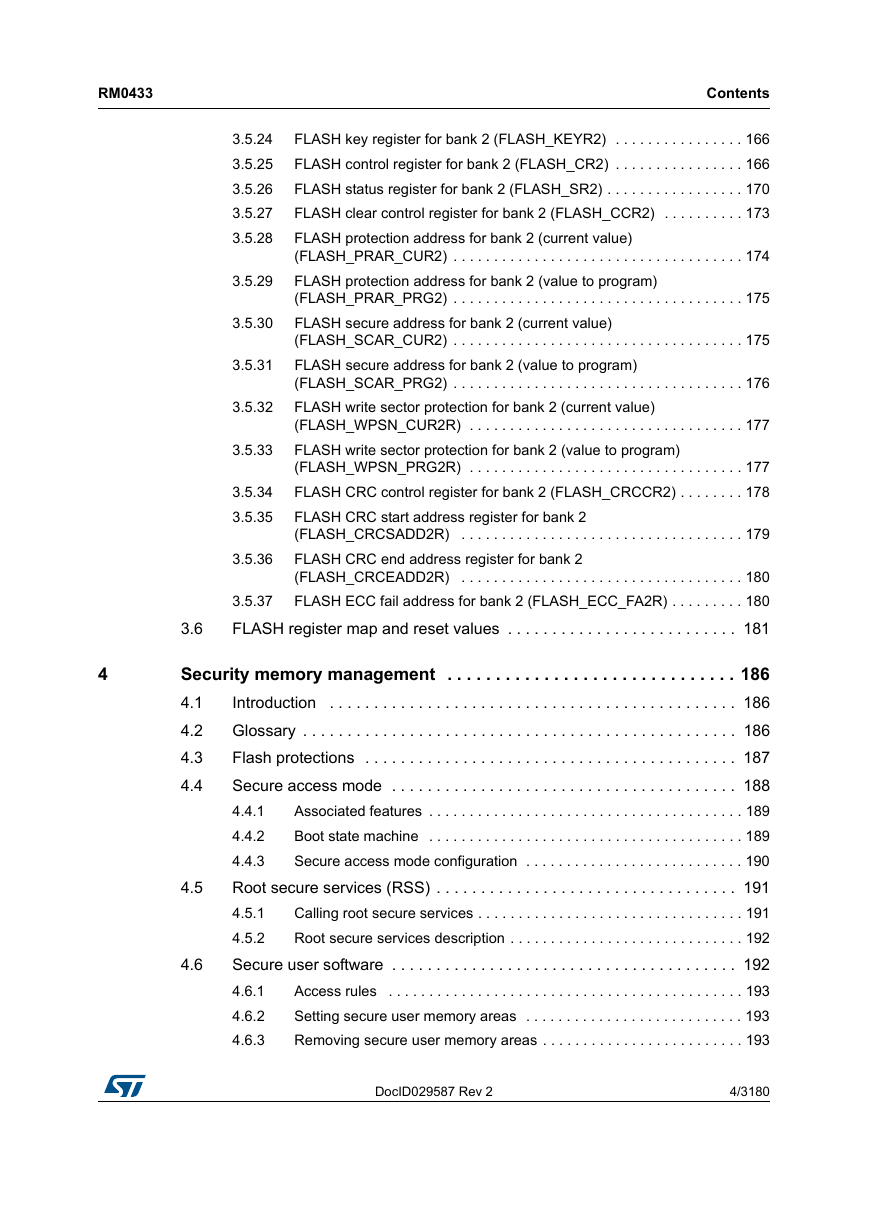

3.5 FLASH registers

3.5.1 FLASH access control register (FLASH_ACR)

3.5.2 FLASH key register for bank 1 (FLASH_KEYR1)

3.5.3 FLASH option key register (FLASH_OPTKEYR)

3.5.4 FLASH control register for bank 1 (FLASH_CR1)

3.5.5 FLASH status register for bank 1 (FLASH_SR1)

3.5.6 FLASH clear control register for bank 1 (FLASH_CCR1)

3.5.7 FLASH option control register (FLASH_OPTCR)

3.5.8 FLASH option status register (current value) (FLASH_OPTSR_CUR)

3.5.9 FLASH option status register (value to program) (FLASH_OPTSR_PRG)

3.5.10 FLASH option clear control register (FLASH_OPTCCR)

3.5.11 FLASH protection address for bank 1 (current value) (FLASH_PRAR_CUR1)

3.5.12 FLASH protection address for bank 1 (value to program) (FLASH_PRAR_PRG1)

3.5.13 FLASH secure address for bank 1 (current value) (FLASH_SCAR_CUR1)

3.5.14 FLASH secure address for bank 1 (value to program) (FLASH_SCAR_PRG1)

3.5.15 FLASH write sector protection for bank 1 (current value) (FLASH_WPSN_CUR1R)

3.5.16 FLASH write sector protection for bank 1 (value to program) (FLASH_WPSN_PRG1R)

3.5.17 FLASH register with boot address (current value) (FLASH_BOOT_CURR)

3.5.18 FLASH register with boot address (value to program) (FLASH_BOOT_PRGR)

3.5.19 FLASH CRC control register for bank 1 (FLASH_CRCCR1)

3.5.20 FLASH CRC start address register for bank 1 (FLASH_CRCSADD1R)

3.5.21 FLASH CRC end address register for bank 1 (FLASH_CRCEADD1R)

3.5.22 FLASH CRC data register (FLASH_CRCDATAR)

3.5.23 FLASH ECC fail address for bank 1 (FLASH_ECC_FA1R)

3.5.24 FLASH key register for bank 2 (FLASH_KEYR2)

3.5.25 FLASH control register for bank 2 (FLASH_CR2)

3.5.26 FLASH status register for bank 2 (FLASH_SR2)

3.5.27 FLASH clear control register for bank 2 (FLASH_CCR2)

3.5.28 FLASH protection address for bank 2 (current value) (FLASH_PRAR_CUR2)

3.5.29 FLASH protection address for bank 2 (value to program) (FLASH_PRAR_PRG2)

3.5.30 FLASH secure address for bank 2 (current value) (FLASH_SCAR_CUR2)

3.5.31 FLASH secure address for bank 2 (value to program) (FLASH_SCAR_PRG2)

3.5.32 FLASH write sector protection for bank 2 (current value) (FLASH_WPSN_CUR2R)

3.5.33 FLASH write sector protection for bank 2 (value to program) (FLASH_WPSN_PRG2R)

3.5.34 FLASH CRC control register for bank 2 (FLASH_CRCCR2)

3.5.35 FLASH CRC start address register for bank 2 (FLASH_CRCSADD2R)

3.5.36 FLASH CRC end address register for bank 2 (FLASH_CRCEADD2R)

3.5.37 FLASH ECC fail address for bank 2 (FLASH_ECC_FA2R)

3.6 FLASH register map and reset values

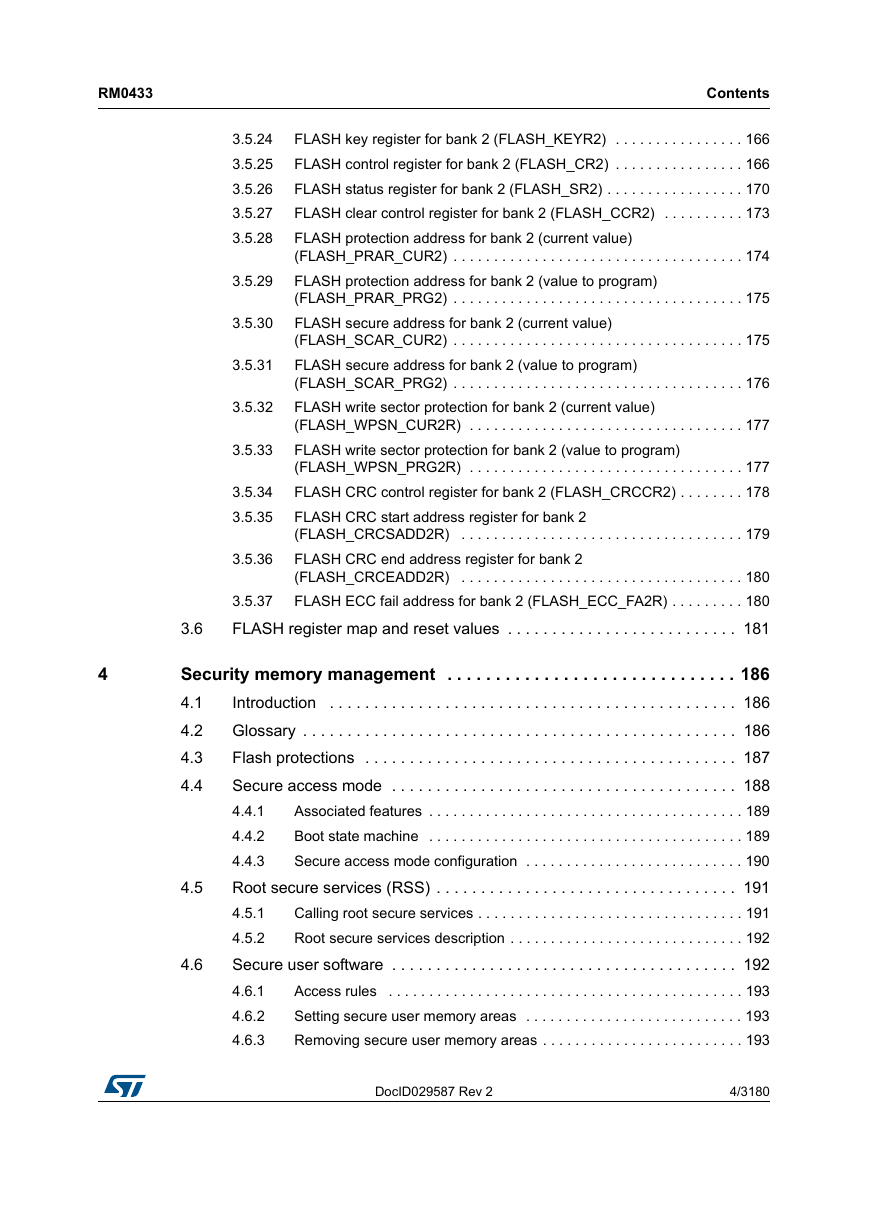

4 Security memory management

4.1 Introduction

4.2 Glossary

4.3 Flash protections

4.4 Secure access mode

4.4.1 Associated features

4.4.2 Boot state machine

4.4.3 Secure access mode configuration

4.5 Root secure services (RSS)

4.5.1 Calling root secure services

4.5.2 Root secure services description

4.6 Secure user software

4.6.1 Access rules

4.6.2 Setting secure user memory areas

4.6.3 Removing secure user memory areas

4.6.4 Selecting secure user software

4.7 Summary of Flash protection mechanisms

5 AXI interconnect

5.1 AXI introduction

5.2 AXI interconnect main features

5.3 AXI interconnect functional description

5.3.1 Block diagram

5.3.2 ASIB configuration

5.3.3 AMIB configuration

5.3.4 Quality of service (QoS)

5.3.5 Global programmer’s view (GPV)

5.4 AXI interconnect registers

5.4.1 AXI interconnect - peripheral ID4 register (AXI_PERIPH_ID_4)

5.4.2 AXI interconnect - peripheral ID0 register (AXI_PERIPH_ID_0)

5.4.3 AXI interconnect - peripheral ID1 register (AXI_PERIPH_ID_1)

5.4.4 AXI interconnect - peripheral ID2 register (AXI_PERIPH_ID_2)

5.4.5 AXI interconnect - peripheral ID3 register (AXI_PERIPH_ID_3)

5.4.6 AXI interconnect - component ID0 register (AXI_COMP_ID_0)

5.4.7 AXI interconnect - component ID1 register (AXI_COMP_ID_1)

5.4.8 AXI interconnect - component ID2 register (AXI_COMP_ID_2)

5.4.9 AXI interconnect - component ID3 register (AXI_COMP_ID_3)

5.4.10 AXI interconnect - TARG x bus matrix issuing functionality register (AXI_TARGx_FN_MOD_ISS_BM)

5.4.11 AXI interconnect - TARG x bus matrix functionality 2 register (AXI_TARGx_FN_MOD2)

5.4.12 AXI interconnect - TARG x long burst functionality modification register (AXI_TARGx_FN_MOD_LB)

5.4.13 AXI interconnect - TARG x issuing functionality modification register (AXI_TARGx_FN_MOD)

5.4.14 AXI interconnect - INI x functionality modification 2 register (AXI_INIx_FN_MOD2)

5.4.15 AXI interconnect - INI x AHB functionality modification register (AXI_INIx_FN_MOD_AHB)

5.4.16 AXI interconnect - INI x read QoS register (AXI_INIx_READ_QOS)

5.4.17 AXI interconnect - INI x write QoS register (AXI_INIx_WRITE_QOS)

5.4.18 AXI interconnect - INI x issuing functionality modification register (AXI_INIx_FN_MOD)

5.5 AXI interconnect register map

6 Power control (PWR)

6.1 Introduction

6.2 PWR main features

6.3 PWR block diagram

6.3.1 PWR pins and internal signals

6.4 Power supplies

6.4.1 System supply startup

6.4.2 Core domain

6.4.3 PWR external supply

6.4.4 Backup domain

6.4.5 VBAT battery charging

6.4.6 Analog supply

6.4.7 USB regulator

6.5 Power supply supervision

6.5.1 Power-on reset (POR)/power-down reset (PDR)

6.5.2 Brownout reset (BOR)

6.5.3 Programmable voltage detector (PVD)

6.5.4 Analog voltage detector (AVD)

6.5.5 Battery voltage thresholds

6.5.6 Temperature thresholds

6.6 Power management

6.6.1 Operating modes

6.6.2 Voltage scaling

6.6.3 Power control modes

6.6.4 Power management examples

6.7 Low-power modes

6.7.1 Slowing down system clocks

6.7.2 Controlling peripheral clocks

6.7.3 Entering low-power modes

6.7.4 Exiting from low-power modes

6.7.5 CSleep mode

6.7.6 CStop mode

6.7.7 DStop mode

6.7.8 Stop mode

6.7.9 DStandby mode

6.7.10 Standby mode

6.8 PWR register description

6.8.1 PWR control register 1 (PWR_CR1)

6.8.2 PWR control status register 1 (PWR_CSR1)

6.8.3 PWR control register 2 (PWR_CR2)

6.8.4 PWR control register 3 (PWR_CR3)

6.8.5 PWR CPU control register (PWR_CPUCR)

6.8.6 PWR D3 domain control register (PWR_D3CR)

6.8.7 PWR wakeup clear register (PWR_WKUPCR)

6.8.8 PWR wakeup flag register (PWR_WKUPFR)

6.8.9 PWR wakeup enable and polarity register (PWR_WKUPEPR)

6.8.10 PWR register map

7 Low-power D3 domain

7.1 Introduction

7.2 EXTI, RCC and PWR interconnections

7.2.1 Interrupts and wakeup

7.2.2 Block interactions

7.2.3 Role of D3 domain DMAMUX2

7.3 Low-power application example based on LPUART1 transmission

7.3.1 Memory retention

7.3.2 Memory-to-peripheral transfer using LPUART1 interface

7.3.3 Overall description of the low-power application example based on LPUART1 transmission

7.3.4 Alternate implementations

7.4 Other low-power applications

8 Reset and Clock Control (RCC)

8.1 RCC main features

8.2 RCC block diagram

8.3 RCC pins and internal signals

8.4 RCC reset block functional description

8.4.1 Power-on/off reset

8.4.2 System reset

8.4.3 Local resets

8.4.4 Reset source identification

8.4.5 Low-power mode security reset (lpwr_rst)

8.4.6 Backup domain reset

8.4.7 Power-on and wakeup sequences

8.5 RCC clock block functional description

8.5.1 Clock naming convention

8.5.2 Oscillators description

8.5.3 Clock Security System (CSS)

8.5.4 Clock output generation (MCO1/MCO2)

8.5.5 PLL description

8.5.6 System clock (sys_ck)

8.5.7 Handling clock generators in Stop and Standby mode

8.5.8 Kernel clock selection

8.5.9 General clock concept overview

8.5.10 Peripheral allocation

8.5.11 Peripheral clock gating control

8.5.12 CPU and bus matrix clock gating control

8.6 RCC Interrupts

8.7 RCC register description

8.7.1 Register mapping overview

8.7.2 RCC Source Control Register (RCC_CR)

8.7.3 RCC Internal Clock Source Calibration Register (RCC_ICSCR)

8.7.4 RCC Clock Recovery RC Register (RCC_CRRCR)

8.7.5 RCC Clock Configuration Register (RCC_CFGR)

8.7.6 RCC Domain 1 Clock Configuration Register (RCC_D1CFGR)

8.7.7 RCC Domain 2 Clock Configuration Register (RCC_D2CFGR)

8.7.8 RCC Domain 3 Clock Configuration Register (RCC_D3CFGR)

8.7.9 RCC PLLs Clock Source Selection Register (RCC_PLLCKSELR)

8.7.10 RCC PLLs Configuration Register (RCC_PLLCFGR)

8.7.11 RCC PLL1 Dividers Configuration Register (RCC_PLL1DIVR)

8.7.12 RCC PLL1 Fractional Divider Register (RCC_PLL1FRACR)

8.7.13 RCC PLL2 Dividers Configuration Register (RCC_PLL2DIVR)

8.7.14 RCC PLL2 Fractional Divider Register (RCC_PLL2FRACR)

8.7.15 RCC PLL3 Dividers Configuration Register (RCC_PLL3DIVR)

8.7.16 RCC PLL3 Fractional Divider Register (RCC_PLL3FRACR)

8.7.17 RCC Domain 1 Kernel Clock Configuration Register (RCC_D1CCIPR)

8.7.18 RCC Domain 2 Kernel Clock Configuration Register (RCC_D2CCIP1R)

8.7.19 RCC Domain 2 Kernel Clock Configuration Register (RCC_D2CCIP2R)

8.7.20 RCC Domain 3 Kernel Clock Configuration Register (RCC_D3CCIPR)

8.7.21 RCC Clock Source Interrupt Enable Register (RCC_CIER)

8.7.22 RCC Clock Source Interrupt Flag Register (RCC_CIFR)

8.7.23 RCC Clock Source Interrupt Clear Register (RCC_CICR)

8.7.24 RCC Backup Domain Control Register (RCC_BDCR)

8.7.25 RCC Clock Control and Status Register (RCC_CSR)

8.7.26 RCC AHB3 Reset Register (RCC_AHB3RSTR)

8.7.27 RCC AHB1 Peripheral Reset Register(RCC_AHB1RSTR)

8.7.28 RCC AHB2 Peripheral Reset Register (RCC_AHB2RSTR)

8.7.29 RCC AHB4 Peripheral Reset Register (RCC_AHB4RSTR)

8.7.30 RCC APB3 Peripheral Reset Register (RCC_APB3RSTR)

8.7.31 RCC APB1 Peripheral Reset Register (RCC_APB1LRSTR)

8.7.32 RCC APB1 Peripheral Reset Register (RCC_APB1HRSTR)

8.7.33 RCC APB2 Peripheral Reset Register (RCC_APB2RSTR)

8.7.34 RCC APB4 Peripheral Reset Register (RCC_APB4RSTR)

8.7.35 RCC Global Control Register (RCC_GCR)

8.7.36 RCC D3 Autonomous mode Register (RCC_D3AMR)

8.7.37 RCC Reset Status Register (RCC_RSR)

8.7.38 RCC AHB3 Clock Register (RCC_AHB3ENR)

8.7.39 RCC AHB1 Clock Register (RCC_AHB1ENR)

8.7.40 RCC AHB2 Clock Register (RCC_AHB2ENR)

8.7.41 RCC AHB4 Clock Register (RCC_AHB4ENR)

8.7.42 RCC APB3 Clock Register (RCC_APB3ENR)

8.7.43 RCC APB1 Clock Register (RCC_APB1LENR)

8.7.44 RCC APB1 Clock Register (RCC_APB1HENR)

8.7.45 RCC APB2 Clock Register (RCC_APB2ENR)

8.7.46 RCC APB4 Clock Register (RCC_APB4ENR)

8.7.47 RCC AHB3 Sleep Clock Register (RCC_AHB3LPENR)

8.7.48 RCC AHB1 Sleep Clock Register (RCC_AHB1LPENR)

8.7.49 RCC AHB2 Sleep Clock Register (RCC_AHB2LPENR)

8.7.50 RCC AHB4 Sleep Clock Register (RCC_AHB4LPENR)

8.7.51 RCC APB3 Sleep Clock Register (RCC_APB3LPENR)

8.7.52 RCC APB1 Low Sleep Clock Register (RCC_APB1LLPENR)

8.7.53 RCC APB1 High Sleep Clock Register (RCC_APB1HLPENR)

8.7.54 RCC APB2 Sleep Clock Register (RCC_APB2LPENR)

8.7.55 RCC APB4 Sleep Clock Register (RCC_APB4LPENR)

8.8 RCC register map

9 Clock recovery system (CRS)

9.1 Introduction

9.2 CRS main features

9.3 CRS functional description

9.3.1 CRS block diagram

9.4 CRS internal signals

9.4.1 Synchronization input

9.4.2 Frequency error measurement

9.4.3 Frequency error evaluation and automatic trimming

9.4.4 CRS initialization and configuration

9.5 CRS low-power modes

9.6 CRS interrupts

9.7 CRS registers

9.7.1 CRS control register (CRS_CR)

9.7.2 CRS configuration register (CRS_CFGR)

9.7.3 CRS interrupt and status register (CRS_ISR)

9.7.4 CRS interrupt flag clear register (CRS_ICR)

9.7.5 CRS register map

10 Hardware semaphore (HSEM)

10.1 Hardware semaphore introduction

10.2 Hardware semaphore main features

10.3 HSEM functional description

10.3.1 HSEM block diagram

10.3.2 HSEM internal signals

10.3.3 HSEM lock procedures

10.3.4 HSEM Write/Read/ReadLock register address

10.3.5 HSEM Clear procedures

10.3.6 HSEM CoreID semaphore clear

10.3.7 HSEM interrupts

10.3.8 AHB bus master ID verification

10.4 HSEM registers

10.4.1 HSEM register (HSEM_R0 - HSEM_R31)

10.4.2 HSEM Read lock register (HSEM_RLR0 - HSEM_RLR31)

10.4.3 HSEM Interrupt enable register (HSEM_CnIER)

10.4.4 HSEM Interrupt clear register (HSEM_CnICR)

10.4.5 HSEM Interrupt status register (HSEM_CnISR)

10.4.6 HSEM Masked interrupt status register (HSEM_CnMISR)

10.4.7 HSEM Clear register (HSEM_CR)

10.4.8 HSEM Interrupt clear register (HSEM_KEYR)

10.4.9 HSEM register map

11 General-purpose I/Os (GPIO)

11.1 Introduction

11.2 GPIO main features

11.3 GPIO functional description

11.3.1 General-purpose I/O (GPIO)

11.3.2 I/O pin alternate function multiplexer and mapping

11.3.3 I/O port control registers

11.3.4 I/O port data registers

11.3.5 I/O data bitwise handling

11.3.6 GPIO locking mechanism

11.3.7 I/O alternate function input/output

11.3.8 External interrupt/wakeup lines

11.3.9 Input configuration

11.3.10 Output configuration

11.3.11 I/O compensation cell

11.3.12 Alternate function configuration

11.3.13 Analog configuration

11.3.14 Using the HSE or LSE oscillator pins as GPIOs

11.3.15 Using the GPIO pins in the backup supply domain

11.4 GPIO registers

11.4.1 GPIO port mode register (GPIOx_MODER) (x =A..K)

11.4.2 GPIO port output type register (GPIOx_OTYPER) (x = A..K)

11.4.3 GPIO port output speed register (GPIOx_OSPEEDR) (x = A..K)

11.4.4 GPIO port pull-up/pull-down register (GPIOx_PUPDR) (x = A..K)

11.4.5 GPIO port input data register (GPIOx_IDR) (x = A..K)

11.4.6 GPIO port output data register (GPIOx_ODR) (x = A..K)

11.4.7 GPIO port bit set/reset register (GPIOx_BSRR) (x = A..K)

11.4.8 GPIO port configuration lock register (GPIOx_LCKR) (x = A..K)

11.4.9 GPIO alternate function low register (GPIOx_AFRL) (x = A..K)

11.4.10 GPIO alternate function high register (GPIOx_AFRH) (x = A..J)

11.4.11 GPIO register map

12 System configuration controller (SYSCFG)

12.1 Introduction

12.2 SYSCFG main features

12.3 SYSCFG register description

12.3.1 SYSCFG peripheral mode configuration register (SYSCFG_PMCR)

12.3.2 SYSCFG external interrupt configuration register 1 (SYSCFG_EXTICR1)

12.3.3 SYSCFG external interrupt configuration register 2 (SYSCFG_EXTICR2)

12.3.4 SYSCFG external interrupt configuration register 3 (SYSCFG_EXTICR3)

12.3.5 SYSCFG external interrupt configuration register 4 (SYSCFG_EXTICR4)

12.3.6 SYSCFG compensation cell control/status register (SYSCFG_CCCSR)

12.3.7 SYSCFG compensation cell value register (SYSCFG_CCVR)

12.3.8 SYSCFG compensation cell code register (SYSCFG_CCCR)

12.3.9 SYSCFG package register (SYSCFG_PKGR)

12.3.10 SYSCFG user register 0 (SYSCFG_UR0)

12.3.11 SYSCFG user register 2 (SYSCFG_UR2)

12.3.12 SYSCFG user register 3 (SYSCFG_UR3)

12.3.13 SYSCFG user register 4 (SYSCFG_UR4)

12.3.14 SYSCFG user register 5 (SYSCFG_UR5)

12.3.15 SYSCFG user register 6 (SYSCFG_UR6)

12.3.16 SYSCFG user register 7 (SYSCFG_UR7)

12.3.17 SYSCFG user register 8 (SYSCFG_UR8)

12.3.18 SYSCFG user register 9 (SYSCFG_UR9)

12.3.19 SYSCFG user register 10 (SYSCFG_UR10)

12.3.20 SYSCFG user register 11 (SYSCFG_UR11)

12.3.21 SYSCFG user register 12 (SYSCFG_UR12)

12.3.22 SYSCFG user register 13 (SYSCFG_UR13)

12.3.23 SYSCFG user register 14 (SYSCFG_UR14)

12.3.24 SYSCFG user register 15 (SYSCFG_UR15)

12.3.25 SYSCFG user register 16 (SYSCFG_UR16)

12.3.26 SYSCFG user register 17 (SYSCFG_UR17)

12.3.27 SYSCFG register maps

13 Block interconnect

13.1 Peripheral interconnect

13.1.1 Introduction

13.1.2 Connection overview

13.2 Wakeup from low power modes

13.3 DMA

13.3.1 MDMA (D1 domain)

13.3.2 DMAMUX1, DMA1 and DMA2 (D2 domain)

13.3.3 DMAMUX2, BDMA (D3 domain)

14 MDMA controller (MDMA)

14.1 MDMA introduction

14.2 MDMA main features

14.3 MDMA functional description

14.3.1 MDMA block diagram

14.3.2 MDMA internal signals

14.3.3 MDMA overview

14.3.4 MDMA channel

14.3.5 Source, destination and transfer modes

14.3.6 Pointer update

14.3.7 MDMA buffer transfer

14.3.8 Request arbitration

14.3.9 FIFO

14.3.10 Block transfer

14.3.11 Block repeat mode

14.3.12 Linked list mode

14.3.13 MDMA transfer completion

14.3.14 MDMA transfer suspension

14.3.15 Error management

14.4 MDMA interrupts

14.5 MDMA registers

14.5.1 MDMA Global Interrupt/Status Register (MDMA_GISR0)

14.5.2 MDMA channel x interrupt/status register (MDMA_CxISR) (x = 0..15)

14.5.3 MDMA channel x interrupt flag clear register (MDMA_CxIFCR) (x = 0..15)

14.5.4 MDMA Channel x error status register (MDMA_CxESR) (x = 0..15)

14.5.5 MDMA channel x control register (MDMA_CxCR) (x = 0..15)

14.5.6 MDMA channel x Transfer Configuration register (MDMA_CxTCR) (x = 0..15)

14.5.7 MDMA Channel x block number of data register (MDMA_CxBNDTR) (x = 0..15)

14.5.8 MDMA channel x source address register (MDMA_CxSAR) (x = 0..15)

14.5.9 MDMA channel x destination address register (MDMA_CxDAR) (x = 0..15)

14.5.10 MDMA channel x Block Repeat address Update register MDMA_CxBRUR (x = 0..15)

14.5.11 MDMA channel x Link Address register (MDMA_CxLAR) (x = 0..15)

14.5.12 MDMA channel x Trigger and Bus selection Register (MDMA_CxTBR) (x = 0..15)

14.5.13 MDMA channel x Mask address register (MDMA_CxMAR) (x = 0..15)

14.5.14 MDMA channel x Mask Data register (MDMA_CxMDR) (x = 0..15)

14.5.15 MDMA register map

15 Direct memory access controller (DMA1, DMA2)

15.1 DMA introduction

15.2 DMA main features

15.3 DMA functional description

15.3.1 DMA block diagram

15.3.2 DMA internal signals

15.3.3 DMA overview

15.3.4 DMA transactions

15.3.5 DMA request mapping

15.3.6 Arbiter

15.3.7 DMA streams

15.3.8 Source, destination and transfer modes

15.3.9 Pointer incrementation

15.3.10 Circular mode

15.3.11 Double buffer mode

15.3.12 Programmable data width, packing/unpacking, endianness

15.3.13 Single and burst transfers

15.3.14 FIFO

15.3.15 DMA transfer completion

15.3.16 DMA transfer suspension

15.3.17 Flow controller

15.3.18 Summary of the possible DMA configurations

15.3.19 Stream configuration procedure

15.3.20 Error management

15.4 DMA interrupts

15.5 DMA registers

15.5.1 DMA low interrupt status register (DMA_LISR)

15.5.2 DMA high interrupt status register (DMA_HISR)

15.5.3 DMA low interrupt flag clear register (DMA_LIFCR)

15.5.4 DMA high interrupt flag clear register (DMA_HIFCR)

15.5.5 DMA stream x configuration register (DMA_SxCR) (x = 0..7)

15.5.6 DMA stream x number of data register (DMA_SxNDTR) (x = 0..7)

15.5.7 DMA stream x peripheral address register (DMA_SxPAR) (x = 0..7)

15.5.8 DMA stream x memory 0 address register (DMA_SxM0AR) (x = 0..7)

15.5.9 DMA stream x memory 1 address register (DMA_SxM1AR) (x = 0..7)

15.5.10 DMA stream x FIFO control register (DMA_SxFCR) (x = 0..7)

15.5.11 DMA register map

16 Basic direct memory access controller (BDMA)

16.1 Introduction

16.2 BDMA main features

16.3 BDMA functional description

16.3.1 BDMA transactions

16.3.2 Arbiter

16.3.3 BDMA channels

16.3.4 Programmable data width, data alignment and endians

16.3.5 Error management

16.3.6 BDMA interrupts

16.4 BDMA registers

16.4.1 DMA interrupt status register (BDMA_ISR)

16.4.2 DMA interrupt flag clear register (BDMA_IFCR)

16.4.3 DMA channel x configuration register (BDMA_CCRx) (x = 1..8, where x = channel number)

16.4.4 DMA channel x number of data register (BDMA_CNDTRx) (x = 1..8, where x = channel number)

16.4.5 DMA channel x peripheral address register (BDMA_CPARx) (x = 1..8, where x = channel number)

16.4.6 DMA channel x memory address register (BDMA_CMARx) (x = 1..8, where x = channel number)

16.4.7 BDMA register map

17 DMA request multiplexer (DMAMUX)

17.1 Introduction

17.2 DMAMUX main features

17.3 DMAMUX implementation

17.3.1 DMAMUX1 and DMAMUX2 instantiation

17.3.2 DMAMUX1 mapping

17.3.3 DMAMUX2 mapping

17.4 DMAMUX functional description

17.4.1 DMAMUX block diagram

17.4.2 DMAMUX signals

17.4.3 DMAMUX channels

17.4.4 DMAMUX request line multiplexer

17.4.5 DMAMUX request generator

17.5 DMAMUX interrupts

17.6 DMAMUX registers

17.6.1 DMAMUX1 request line multiplexer channel x configuration register (DMAMUX1_CxCR)

17.6.2 DMAMUX2 request line multiplexer channel x configuration register (DMAMUX2_CxCR)

17.6.3 DMAMUX1 request line multiplexer interrupt channel status register (DMAMUX1_CSR)

17.6.4 DMAMUX2 request line multiplexer interrupt channel status register (DMAMUX2_CSR)

17.6.5 DMAMUX1 request line multiplexer interrupt clear flag register (DMAMUX1_CFR)

17.6.6 DMAMUX2 request line multiplexer interrupt clear flag register (DMAMUX2_CFR)

17.6.7 DMAMUX1 request generator channel x configuration register (DMAMUX1_RGxCR)

17.6.8 DMAMUX2 request generator channel x configuration register (DMAMUX2_RGxCR)

17.6.9 DMAMUX1 request generator interrupt status register (DMAMUX1_RGSR)

17.6.10 DMAMUX2 request generator interrupt status register (DMAMUX2_RGSR)

17.6.11 DMAMUX1 request generator interrupt clear flag register (DMAMUX1_RGCFR)

17.6.12 DMAMUX2 request generator interrupt clear flag register (DMAMUX2_RGCFR)

17.6.13 DMAMUX register map

18 Chrom-Art Accelerator™ controller (DMA2D)

18.1 DMA2D introduction

18.2 DMA2D main features

18.3 DMA2D functional description

18.3.1 General description

18.4 DMA2D pins and internal signals

18.4.1 DMA2D control

18.4.2 DMA2D foreground and background FIFOs

18.4.3 DMA2D foreground and background pixel format converter (PFC)

18.4.4 DMA2D foreground and background CLUT interface

18.4.5 DMA2D blender

18.4.6 DMA2D output PFC

18.4.7 DMA2D output FIFO

18.4.8 DMA2D AXI master port timer

18.4.9 DMA2D transactions

18.4.10 DMA2D configuration

18.4.11 YCbCr support

18.4.12 DMA2D transfer control (start, suspend, abort and completion)

18.4.13 Watermark

18.4.14 Error management

18.4.15 AXI dead time

18.5 DMA2D interrupts

18.6 DMA2D registers

18.6.1 DMA2D control register (DMA2D_CR)

18.6.2 DMA2D Interrupt Status Register (DMA2D_ISR)

18.6.3 DMA2D interrupt flag clear register (DMA2D_IFCR)

18.6.4 DMA2D foreground memory address register (DMA2D_FGMAR)

18.6.5 DMA2D foreground offset register (DMA2D_FGOR)

18.6.6 DMA2D background memory address register (DMA2D_BGMAR)

18.6.7 DMA2D background offset register (DMA2D_BGOR)

18.6.8 DMA2D foreground PFC control register (DMA2D_FGPFCCR)

18.6.9 DMA2D foreground color register (DMA2D_FGCOLR)

18.6.10 DMA2D background PFC control register (DMA2D_BGPFCCR)

18.6.11 DMA2D background color register (DMA2D_BGCOLR)

18.6.12 DMA2D foreground CLUT memory address register (DMA2D_FGCMAR)

18.6.13 DMA2D background CLUT memory address register (DMA2D_BGCMAR)

18.6.14 DMA2D output PFC control register (DMA2D_OPFCCR)

18.6.15 DMA2D output color register (DMA2D_OCOLR)

18.6.16 DMA2D output memory address register (DMA2D_OMAR)

18.6.17 DMA2D output offset register (DMA2D_OOR)

18.6.18 DMA2D number of line register (DMA2D_NLR)

18.6.19 DMA2D line watermark register (DMA2D_LWR)

18.6.20 DMA2D AXI master timer configuration register (DMA2D_AMTCR)

18.6.21 DMA2D register map

19 Nested Vectored Interrupt Controllers

19.1 NVIC features

19.1.1 SysTick calibration value register

19.1.2 Interrupt and exception vectors

20 Extended interrupt and event controller (EXTI)

20.1 EXTI main features

20.2 EXTI block diagram

20.2.1 EXTI connections between peripherals, CPU, and D3 domain

20.3 EXTI functional description

20.3.1 EXTI Configurable event input CPU wakeup

20.3.2 EXTI configurable event input Any wakeup

20.3.3 EXTI direct event input CPU wakeup

20.3.4 EXTI direct event input Any wakeup

20.3.5 EXTI D3 pending request clear selection

20.4 EXTI event input mapping

20.5 EXTI functional behavior

20.5.1 EXTI CPU interrupt procedure

20.5.2 EXTI CPU event procedure

20.5.3 EXTI CPU wakeup procedure

20.5.4 EXTI D3 domain wakeup for autonomous Run mode procedure

20.5.5 EXTI software interrupt/event trigger procedure

20.6 EXTI register description

20.6.1 EXTI rising trigger selection register (EXTI_RTSR1)

20.6.2 EXTI falling trigger selection register (EXTI_FTSR1)

20.6.3 EXTI software interrupt event register (EXTI_SWIER1)

20.6.4 EXTI D3 pending mask register (EXTI_D3PMR1)

20.6.5 EXTI D3 pending clear selection register low (EXTI_D3PCR1L)

20.6.6 EXTI D3 pending clear selection register high (EXTI_D3PCR1H)

20.6.7 EXTI rising trigger selection register (EXTI_RTSR2)

20.6.8 EXTI falling trigger selection register (EXTI_FTSR2)

20.6.9 EXTI software interrupt event register (EXTI_SWIER2)

20.6.10 EXTI D3 pending mask register (EXTI_D3PMR2)

20.6.11 EXTI D3 pending clear selection register low (EXTI_D3PCR2L)

20.6.12 EXTI D3 pending clear selection register high (EXTI_D3PCR2H)

20.6.13 EXTI rising trigger selection register (EXTI_RTSR3)

20.6.14 EXTI falling trigger selection register (EXTI_FTSR3)

20.6.15 EXTI software interrupt event register (EXTI_SWIER3)

20.6.16 EXTI D3 pending mask register (EXTI_D3PMR3)

20.6.17 EXTI D3 pending clear selection register low (EXTI_D3PCR3L)

20.6.18 EXTI D3 pending clear selection register high (EXTI_D3PCR3H)

20.6.19 EXTI interrupt mask register (EXTI_CPUIMR1)

20.6.20 EXTI event mask register (EXTI_CPUEMR1)

20.6.21 EXTI pending register (EXTI_CPUPR1)

20.6.22 EXTI interrupt mask register (EXTI_CPUIMR2)

20.6.23 EXTI event mask register (EXTI_CPUEMR2)

20.6.24 EXTI pending register (EXTI_CPUPR2)

20.6.25 EXTI interrupt mask register (EXTI_CPUIMR3)

20.6.26 EXTI event mask register (EXTI_CPUEMR3)

20.6.27 EXTI pending register (EXTI_CPUPR3)

20.6.28 EXTI register map

21 Cyclic redundancy check calculation unit (CRC)

21.1 Introduction

21.2 CRC main features

21.3 CRC functional description

21.3.1 CRC block diagram

21.3.2 CRC internal signals

21.3.3 CRC operation

21.4 CRC registers

21.4.1 Data register (CRC_DR)

21.4.2 Independent data register (CRC_IDR)

21.4.3 Control register (CRC_CR)

21.4.4 Initial CRC value (CRC_INIT)

21.4.5 CRC polynomial (CRC_POL)

21.4.6 CRC register map

22 Flexible memory controller (FMC)

22.1 FMC main features

22.2 FMC block diagram

22.3 FMC internal signals

22.4 AHB interface

22.5 AXI interface

22.5.1 Supported memories and transactions

22.6 External device address mapping

22.6.1 NOR/PSRAM address mapping

22.6.2 NAND Flash memory address mapping

22.6.3 SDRAM address mapping

22.7 NOR Flash/PSRAM controller

22.7.1 External memory interface signals

22.7.2 Supported memories and transactions

22.7.3 General timing rules

22.7.4 NOR Flash/PSRAM controller asynchronous transactions

22.7.5 Synchronous transactions

22.7.6 NOR/PSRAM controller registers

22.8 NAND Flash controller

22.8.1 External memory interface signals

22.8.2 NAND Flash supported memories and transactions

22.8.3 Timing diagrams for NAND Flash memories

22.8.4 NAND Flash operations

22.8.5 NAND Flash prewait feature

22.8.6 Computation of the error correction code (ECC) in NAND Flash memory

22.8.7 NAND Flash controller registers

22.9 SDRAM controller

22.9.1 SDRAM controller main features

22.9.2 SDRAM External memory interface signals

22.9.3 SDRAM controller functional description

22.9.4 Low-power modes

22.9.5 SDRAM controller registers

22.10 FMC register map

23 Quad-SPI interface (QUADSPI)

23.1 Introduction

23.2 QUADSPI main features

23.3 QUADSPI functional description

23.3.1 QUADSPI block diagram

23.3.2 QUADSPI pins and internal signals

23.3.3 QUADSPI Command sequence

23.3.4 QUADSPI signal interface protocol modes

23.3.5 QUADSPI indirect mode

23.3.6 QUADSPI status flag polling mode

23.3.7 QUADSPI memory-mapped mode

23.3.8 QUADSPI Free running clock mode

23.3.9 QUADSPI Flash memory configuration

23.3.10 QUADSPI delayed data sampling

23.3.11 QUADSPI configuration

23.3.12 QUADSPI usage

23.3.13 Sending the instruction only once

23.3.14 QUADSPI error management

23.3.15 QUADSPI busy bit and abort functionality

23.3.16 nCS behavior

23.4 QUADSPI interrupts

23.5 QUADSPI registers

23.5.1 QUADSPI control register (QUADSPI_CR)

23.5.2 QUADSPI device configuration register (QUADSPI_DCR)

23.5.3 QUADSPI status register (QUADSPI_SR)

23.5.4 QUADSPI flag clear register (QUADSPI_FCR)

23.5.5 QUADSPI data length register (QUADSPI_DLR)

23.5.6 QUADSPI communication configuration register (QUADSPI_CCR)

23.5.7 QUADSPI address register (QUADSPI_AR)

23.5.8 QUADSPI alternate bytes registers (QUADSPI_ABR)

23.5.9 QUADSPI data register (QUADSPI_DR)

23.5.10 QUADSPI polling status mask register (QUADSPI _PSMKR)

23.5.11 QUADSPI polling status match register (QUADSPI _PSMAR)

23.5.12 QUADSPI polling interval register (QUADSPI _PIR)

23.5.13 QUADSPI low-power timeout register (QUADSPI_LPTR)

23.5.14 QUADSPI register map

24 Delay block (DLYB)

24.1 Introduction

24.2 DLYB main features

24.3 DLYB functional description

24.3.1 DLYB diagram

24.3.2 DLYB pins and internal signals

24.3.3 General description

24.3.4 Delay line length configuration procedure

24.3.5 Output clock phase configuration procedure

24.4 DLYB registers

24.4.1 DLYB control register (DLYB_CR)

24.4.2 DLYB configuration register (DLYB_CFGR)

24.4.3 DLYB register map

25 Analog-to-digital converters (ADC)

25.1 Introduction

25.2 ADC main features

25.3 ADC functional description

25.3.1 ADC block diagram

25.3.2 ADC pins and internal signals

25.3.3 Clocks

25.3.4 ADC1/2/3 connectivity

25.3.5 Slave AHB interface

25.3.6 ADC Deep-Power-Down Mode (DEEPPWD) & ADC Voltage Regulator (ADVREGEN)

25.3.7 Single-ended and differential input channels

25.3.8 Calibration (ADCAL, ADCALDIF, ADCALLIN, ADCx_CALFACT)

25.3.9 ADC on-off control (ADEN, ADDIS, ADRDY)

25.3.10 Constraints when writing the ADC control bits

25.3.11 Channel selection (SQRx, JSQRx)

25.3.12 Prechannel selection register (ADCx_PCSEL)

25.3.13 Channel-wise programmable sampling time (SMPR1, SMPR2)

25.3.14 Single conversion mode (CONT=0)

25.3.15 Continuous conversion mode (CONT=1)

25.3.16 Starting conversions (ADSTART, JADSTART)

25.3.17 Timing

25.3.18 Stopping an ongoing conversion (ADSTP, JADSTP)

25.3.19 Conversion on external trigger and trigger polarity (EXTSEL, EXTEN, JEXTSEL, JEXTEN)

25.3.20 Injected channel management

25.3.21 Discontinuous mode (DISCEN, DISCNUM, JDISCEN)

25.3.22 Queue of context for injected conversions

25.3.23 Programmable resolution (RES) - fast conversion mode

25.3.24 End of conversion, end of sampling phase (EOC, JEOC, EOSMP)

25.3.25 End of conversion sequence (EOS, JEOS)

25.3.26 Timing diagrams example (single/continuous modes, hardware/software triggers)

25.3.27 Data management

25.3.28 Managing conversions using the DFSDM

25.3.29 Dynamic low-power features

25.3.30 Analog window watchdog (AWD1EN, JAWD1EN, AWD1SGL, AWD1CH, AWD2CH, AWD3CH, AWD_HTRy, AWD_LTRy, AWDy)

25.3.31 Oversampler

25.3.32 Dual ADC modes

25.3.33 Temperature sensor

25.3.34 VBAT supply monitoring

25.3.35 Monitoring the internal voltage reference

25.4 ADC interrupts

25.5 ADC registers (for each ADC)

25.5.1 ADC interrupt and status register (ADCx_ISR, x=1..3)

25.5.2 ADC interrupt enable register (ADCx_IER, x=1..3)

25.5.3 ADC control register (ADCx_CR, x=1..3)

25.5.4 ADC configuration register (ADCx_CFGR, x=1..3)

25.5.5 ADC configuration register 2 (ADCx_CFGR2, x=1..3)

25.5.6 ADC sample time register 1 (ADCx_SMPR1, x=1..3)

25.5.7 ADC sample time register 2 (ADCx_SMPR2, x=1..3)

25.5.8 ADC pre channel selection register (ADCx_PCSEL, x=1..3)

25.5.9 ADC watchdog threshold register 1 (ADCx_LTR1, x=1..3)

25.5.10 ADC watchdog threshold register 1 (ADCx_LHTR1, x=1..3)

25.5.11 ADC regular sequence register 1 (ADCx_SQR1, x=1..3)

25.5.12 ADC regular sequence register 2 (ADCx_SQR2, x=1..3)

25.5.13 ADC regular sequence register 3 (ADCx_SQR3, x=1..3)

25.5.14 ADC regular sequence register 4 (ADCx_SQR4, x=1..3)

25.5.15 ADC regular Data Register (ADCx_DR, x=1..3)

25.5.16 ADC injected sequence register (ADCx_JSQR, x=1..3)

25.5.17 ADC offset register (ADCx_OFRy, x=1..3) (y=1..4)

25.5.18 ADC injected data register (ADCx_JDRy, x=1..3, y= 1..4)

25.5.19 ADC Analog Watchdog 2 Configuration Register (ADCx_AWD2CR, x=1..3)

25.5.20 ADC Analog Watchdog 3 Configuration Register (ADCx_AWD3CR, x=1..3)

25.5.21 ADC watchdog lower threshold register 2 (ADCx_LTR2, x=1..3)

25.5.22 ADC watchdog higher threshold register 2 (ADCx_HTR2, x=1..3)

25.5.23 ADC watchdog lower threshold register 3 (ADCx_LTR3, x=1..3)

25.5.24 ADC watchdog higher threshold register 3 (ADCx_HTR3, x=1..3)

25.5.25 ADC Differential Mode Selection register (ADCx_DIFSEL, x=1..3)

25.5.26 ADC Calibration Factors register (ADCx_CALFACT, x=1..3)

25.5.27 ADC Calibration Factor register 2 (ADCx_CALFACT2, x=1..3)

25.5.28 ADC Option register (ADCx_OR, x=1..3)

25.6 ADC common registers

25.6.1 ADC Common status register (ADCx_CSR, x=12 or 3)

25.6.2 ADC common control register (ADCx_CCR, x=12 or 3)

25.6.3 ADC common regular data register for dual mode (ADCx_CDR, x=12 or 3)

25.6.4 ADC common regular data register for 32-bit dual mode (ADCx_CDR2, x=12 or 3)

25.6.5 ADC register map

26 Digital-to-analog converter (DAC)

26.1 Introduction

26.2 DAC main features

26.3 DAC functional description

26.3.1 DAC block diagram

26.3.2 DAC pins and internal signals

26.3.3 DAC channel enable

26.3.4 DAC data format

26.3.5 DAC conversion

26.3.6 DAC output voltage

26.3.7 DAC trigger selection

26.3.8 DMA request

26.3.9 Noise generation

26.3.10 Triangle-wave generation

26.3.11 DAC channel modes

26.3.12 DAC channel buffer calibration

26.3.13 Dual DAC channel conversion (if available)

26.4 DAC low-power modes

26.5 DAC registers

26.5.1 DAC control register (DAC_CR)

26.5.2 DAC software trigger register (DAC_SWTRGR)

26.5.3 DAC channel1 12-bit right-aligned data holding register (DAC_DHR12R1)

26.5.4 DAC channel1 12-bit left aligned data holding register (DAC_DHR12L1)

26.5.5 DAC channel1 8-bit right aligned data holding register (DAC_DHR8R1)

26.5.6 DAC channel2 12-bit right aligned data holding register (DAC_DHR12R2)

26.5.7 DAC channel2 12-bit left aligned data holding register (DAC_DHR12L2)

26.5.8 DAC channel2 8-bit right-aligned data holding register (DAC_DHR8R2)

26.5.9 Dual DAC 12-bit right-aligned data holding register (DAC_DHR12RD)

26.5.10 DUAL DAC 12-bit left aligned data holding register (DAC_DHR12LD)

26.5.11 DUAL DAC 8-bit right aligned data holding register (DAC_DHR8RD)

26.5.12 DAC channel1 data output register (DAC_DOR1)

26.5.13 DAC channel2 data output register (DAC_DOR2)

26.5.14 DAC status register (DAC_SR)

26.5.15 DAC calibration control register (DAC_CCR)

26.5.16 DAC mode control register (DAC_MCR)

26.5.17 DAC Sample and Hold sample time register 1 (DAC_SHSR1)

26.5.18 DAC Sample and Hold sample time register 2 (DAC_SHSR2)

26.5.19 DAC Sample and Hold hold time register (DAC_SHHR)

26.5.20 DAC Sample and Hold refresh time register (DAC_SHRR)

26.5.21 DAC option register (DAC_OR)

26.5.22 DAC register map

27 Voltage reference buffer (VREFBUF)

27.1 Introduction

27.2 VREFBUF functional description

27.3 VREFBUF registers

27.3.1 VREFBUF control and status register (VREFBUF_CSR)

27.3.2 VREFBUF calibration control register (VREFBUF_CCR)

27.3.3 VREFBUF register map

28 Comparator (COMP)

28.1 Introduction

28.2 COMP main features

28.3 COMP functional description

28.3.1 COMP block diagram

28.3.2 COMP pins and internal signals

28.3.3 COMP reset and clocks

28.3.4 Comparator LOCK mechanism

28.3.5 Window comparator

28.3.6 Hysteresis

28.3.7 Comparator output blanking function

28.3.8 Comparator output on GPIOs

28.3.9 Comparator output redirection

28.3.10 COMP power and speed modes

28.4 COMP low-power modes

28.5 COMP interrupts

28.5.1 Interrupt through EXTI block

28.5.2 Interrupt through NVIC of the CPU

28.6 SCALER function

28.7 COMP registers

28.7.1 Comparator status register (COMP_SR)

28.7.2 Comparator interrupt clear flag register (COMP_ICFR)

28.7.3 Comparator option register (COMP_OR)

28.7.4 Comparator configuration register 1 (COMP_CFGR1)

28.7.5 Comparator configuration register 2 (COMP_CFGR2)

28.7.6 COMP register map

29 Operational amplifiers (OPAMP)

29.1 Introduction

29.2 OPAMP main features

29.3 OPAMP functional description

29.3.1 OPAMP reset and clocks

29.3.2 Initial configuration

29.3.3 Signal routing

29.3.4 OPAMP modes

29.3.5 Calibration

29.4 OPAMP low-power modes

29.5 OPAMP PGA gain

29.6 OPAMP registers

29.6.1 OPAMP1 control/status register (OPAMP1_CSR)

29.6.2 OPAMP1 trimming register in normal mode (OPAMP1_OTR)

29.6.3 OPAMP1 trimming register in high-speed mode (OPAMP1_HSOTR)

29.6.4 OPAMP option register (OPAMP_OR)

29.6.5 OPAMP2 control/status register (OPAMP2_CSR)

29.6.6 OPAMP2 trimming register in normal mode (OPAMP2_OTR)

29.6.7 OPAMP2 trimming register in high-speed mode (OPAMP2_HSOTR)

29.6.8 OPAMP register map

30 Digital filter for sigma delta modulators (DFSDM)

30.1 Introduction

30.2 DFSDM main features

30.3 DFSDM implementation

30.4 DFSDM functional description

30.4.1 DFSDM block diagram

30.4.2 DFSDM pins and internal signals

30.4.3 DFSDM reset and clocks

30.4.4 Serial channel transceivers

30.4.5 Configuring the input serial interface

30.4.6 Parallel data inputs

30.4.7 Channel selection

30.4.8 Digital filter configuration

30.4.9 Integrator unit

30.4.10 Analog watchdog

30.4.11 Short-circuit detector

30.4.12 Extreme detector

30.4.13 Data unit block

30.4.14 Signed data format

30.4.15 Launching conversions

30.4.16 Continuous and fast continuous modes

30.4.17 Request precedence

30.4.18 Power optimization in run mode

30.5 DFSDM interrupts

30.6 DFSDM DMA transfer

30.7 DFSDM channel y registers (y=0..7)

30.7.1 DFSDM channel configuration y register (DFSDM_CHyCFGR1) (y=0..7)

30.7.2 DFSDM channel configuration y register (DFSDM_CHyCFGR2) (y=0..7)

30.7.3 DFSDM channel analog watchdog and short-circuit detector register (DFSDM_CHyAWSCDR) (y=0..7)

30.7.4 DFSDM channel watchdog filter data register (DFSDM_CHyWDATR) (y=0..7)

30.7.5 DFSDM channel data input register (DFSDM_CHyDATINR) (y=0..7)

30.8 DFSDM filter x module registers (x=0..3)

30.8.1 DFSDM control register 1 (DFSDM_FLTxCR1)

30.8.2 DFSDM control register 2 (DFSDM_FLTxCR2)

30.8.3 DFSDM interrupt and status register (DFSDM_FLTxISR)

30.8.4 DFSDM interrupt flag clear register (DFSDM_FLTxICR)

30.8.5 DFSDM injected channel group selection register (DFSDM_FLTxJCHGR)

30.8.6 DFSDM filter control register (DFSDM_FLTxFCR)

30.8.7 DFSDM data register for injected group (DFSDM_FLTxJDATAR)

30.8.8 DFSDM data register for the regular channel (DFSDM_FLTxRDATAR)

30.8.9 DFSDM analog watchdog high threshold register (DFSDM_FLTxAWHTR)

30.8.10 DFSDM analog watchdog low threshold register (DFSDM_FLTxAWLTR)

30.8.11 DFSDM analog watchdog status register (DFSDM_FLTxAWSR)

30.8.12 DFSDM analog watchdog clear flag register (DFSDM_FLTxAWCFR)

30.8.13 DFSDM Extremes detector maximum register (DFSDM_FLTxEXMAX)

30.8.14 DFSDM Extremes detector minimum register (DFSDM_FLTxEXMIN)

30.8.15 DFSDM conversion timer register (DFSDM_FLTxCNVTIMR)

30.8.16 DFSDM register map

31 Digital camera interface (DCMI)

31.1 DCMI introduction

31.2 DCMI main features

31.3 DCMI clocks

31.4 DCMI functional overview

31.4.1 DCMI block diagram

31.4.2 DCMI internal signals

31.4.3 DMA interface

31.4.4 DCMI physical interface

31.4.5 Synchronization

31.4.6 Capture modes

31.4.7 Crop feature

31.4.8 JPEG format

31.4.9 FIFO

31.5 Data format description

31.5.1 Data formats

31.5.2 Monochrome format

31.5.3 RGB format

31.5.4 YCbCr format

31.5.5 YCbCr format - Y only

31.5.6 Half resolution image extraction

31.6 DCMI interrupts

31.7 DCMI register description

31.7.1 DCMI control register (DCMI_CR)

31.7.2 DCMI status register (DCMI_SR)

31.7.3 DCMI raw interrupt status register (DCMI_RIS)

31.7.4 DCMI interrupt enable register (DCMI_IER)

31.7.5 DCMI masked interrupt status register (DCMI_MIS)

31.7.6 DCMI interrupt clear register (DCMI_ICR)

31.7.7 DCMI embedded synchronization code register (DCMI_ESCR)

31.7.8 DCMI embedded synchronization unmask register (DCMI_ESUR)

31.7.9 DCMI crop window start (DCMI_CWSTRT)

31.7.10 DCMI crop window size (DCMI_CWSIZE)

31.7.11 DCMI data register (DCMI_DR)

31.7.12 DCMI register map

32 LCD-TFT Display Controller (LTDC)

32.1 Introduction

32.2 LTDC main features

32.3 LTDC functional description

32.3.1 LTDC block diagram

32.3.2 LCD-TFT internal signals

32.3.3 LCD-TFT pins and external signal interface

32.3.4 LTDC reset and clocks

32.4 LTDC programmable parameters

32.4.1 LTDC Global configuration parameters

32.4.2 Layer programmable parameters

32.5 LTDC interrupts

32.6 LTDC programming procedure

32.7 LTDC registers

32.7.1 LTDC Synchronization Size Configuration Register (LTDC_SSCR)

32.7.2 LTDC Back Porch Configuration Register (LTDC_BPCR)

32.7.3 LTDC Active Width Configuration Register (LTDC_AWCR)

32.7.4 LTDC Total Width Configuration Register (LTDC_TWCR)

32.7.5 LTDC Global Control Register (LTDC_GCR)

32.7.6 LTDC Shadow Reload Configuration Register (LTDC_SRCR)

32.7.7 LTDC Background Color Configuration Register (LTDC_BCCR)

32.7.8 LTDC Interrupt Enable Register (LTDC_IER)

32.7.9 LTDC Interrupt Status Register (LTDC_ISR)

32.7.10 LTDC Interrupt Clear Register (LTDC_ICR)

32.7.11 LTDC Line Interrupt Position Configuration Register (LTDC_LIPCR)

32.7.12 LTDC Current Position Status Register (LTDC_CPSR)

32.7.13 LTDC Current Display Status Register (LTDC_CDSR)

32.7.14 LTDC Layerx Control Register (LTDC_LxCR) (where x=1..2)

32.7.15 LTDC Layerx Window Horizontal Position Configuration Register (LTDC_LxWHPCR) (where x=1..2)

32.7.16 LTDC Layerx Window Vertical Position Configuration Register (LTDC_LxWVPCR) (where x=1..2)

32.7.17 LTDC Layerx Color Keying Configuration Register (LTDC_LxCKCR) (where x=1..2)

32.7.18 LTDC Layerx Pixel Format Configuration Register (LTDC_LxPFCR) (where x=1..2)

32.7.19 LTDC Layerx Constant Alpha Configuration Register (LTDC_LxCACR) (where x=1..2)

32.7.20 LTDC Layerx Default Color Configuration Register (LTDC_LxDCCR) (where x=1..2)

32.7.21 LTDC Layerx Blending Factors Configuration Register (LTDC_LxBFCR) (where x=1..2)

32.7.22 LTDC Layerx Color Frame Buffer Address Register (LTDC_LxCFBAR) (where x=1..2)

32.7.23 LTDC Layerx Color Frame Buffer Length Register (LTDC_LxCFBLR) (where x=1..2)

32.7.24 LTDC Layerx ColorFrame Buffer Line Number Register (LTDC_LxCFBLNR) (where x=1..2)

32.7.25 LTDC Layerx CLUT Write Register (LTDC_LxCLUTWR) (where x=1..2)

32.7.26 LTDC register map

33 JPEG codec (JPEG)

33.1 Introduction

33.2 JPEG codec main features

33.3 JPEG codec block functional description

33.3.1 General description

33.3.2 JPEG internal signals

33.3.3 JPEG decoding procedure

33.3.4 JPEG encoding procedure

33.4 JPEG codec interrupts

33.5 JPEG codec registers

33.5.1 JPEG codec control register (JPEG_CONFR0)

33.5.2 JPEG codec configuration register 1 (JPEG_CONFR1)

33.5.3 JPEG codec configuration register 2 (JPEG_CONFR2)

33.5.4 JPEG codec configuration register 3 (JPEG_CONFR3)

33.5.5 JPEG codec configuration register 4-7 (JPEG_CONFR4-7)

33.5.6 JPEG control register (JPEG_CR)

33.5.7 JPEG status register (JPEG_SR)

33.5.8 JPEG clear flag register (JPEG_CFR)

33.5.9 JPEG data input register (JPEG_DIR)

33.5.10 JPEG data output register (JPEG_DOR)

33.5.11 JPEG codec register map

34 True Random Number Generator (RNG)

34.1 Introduction

34.2 RNG main features

34.3 RNG functional description

34.3.1 RNG block diagram

34.3.2 RNG internal signals

34.3.3 Random number generation

34.3.4 RNG initialization

34.3.5 RNG operation

34.3.6 RNG clocking

34.3.7 Error management

34.4 RNG low-power usage

34.5 RNG interrupts

34.6 RNG processing time

34.7 Entropy source validation

34.7.1 Introduction

34.7.2 Validation conditions

34.7.3 Data collection

34.8 RNG registers

34.8.1 RNG control register (RNG_CR)

34.8.2 RNG status register (RNG_SR)

34.8.3 RNG data register (RNG_DR)

34.8.4 RNG register map

35 Cryptographic processor (CRYP)

35.1 Introduction

35.2 CRYP main features

35.3 CRYP functional description

35.3.1 CRYP block diagram

35.3.2 CRYP internal signals

35.3.3 CRYP DES/TDES cryptographic core

35.3.4 CRYP AES cryptographic core

35.3.5 CRYP procedure to perform a cipher operation

35.3.6 CRYP busy state

35.3.7 Preparing the CRYP AES key for decryption

35.3.8 CRYP stealing and data padding

35.3.9 CRYP suspend/resume operations

35.3.10 CRYP DES/TDES basic chaining modes (ECB, CBC)

35.3.11 CRYP AES basic chaining modes (ECB, CBC)

35.3.12 CRYP AES counter mode (AES-CTR)

35.3.13 CRYP AES Galois/counter mode (GCM)

35.3.14 CRYP AES Galois message authentication code (GMAC)

35.3.15 CRYP AES Counter with CBC-MAC (CCM)

35.3.16 CRYP data registers and data swapping

35.3.17 CRYP key registers

35.3.18 CRYP initialization vector registers

35.3.19 CRYP DMA interface

35.3.20 CRYP error management

35.4 CRYP interrupts

35.5 CRYP processing time

35.6 CRYP registers

35.6.1 CRYP control register (CRYP_CR)

35.6.2 CRYP status register (CRYP_SR)

35.6.3 CRYP data input register (CRYP_DIN)

35.6.4 CRYP data output register (CRYP_DOUT)

35.6.5 CRYP DMA control register (CRYP_DMACR)

35.6.6 CRYP interrupt mask set/clear register (CRYP_IMSCR)

35.6.7 CRYP raw interrupt status register (CRYP_RISR)

35.6.8 CRYP masked interrupt status register (CRYP_MISR)

35.6.9 CRYP key register 0L (CRYP_K0LR)

35.6.10 CRYP key register 0R (CRYP_K0RR)

35.6.11 CRYP key register 1L (CRYP_K1LR)

35.6.12 CRYP key register 1R (CRYP_K1RR)

35.6.13 CRYP key register 2L (CRYP_K2LR)

35.6.14 CRYP key register 2R (CRYP_K2RR)

35.6.15 CRYP key register 3L (CRYP_K3LR)

35.6.16 CRYP key register 3R (CRYP_K3RR)

35.6.17 CRYP initialization vector register 0L (CRYP_IV0LR)

35.6.18 CRYP initialization vector register 0R (CRYP_IV0RR)

35.6.19 CRYP initialization vector register 1L (CRYP_IV1LR)

35.6.20 CRYP initialization vector register 1R (CRYP_IV1RR)

35.6.21 CRYP context swap GCM-CCM registers (CRYP_CSGCMCCMxR)

35.6.22 CRYP context swap GCM registers (CRYP_CSGCMxR)

35.6.23 CRYP register map

36 Hash processor (HASH)

36.1 Introduction

36.2 HASH main features

36.3 HASH functional description

36.3.1 HASH block diagram

36.3.2 HASH internal signals

36.3.3 About secure hash algorithms

36.3.4 Message data feeding

36.3.5 Message digest computing

36.3.6 Message padding

36.3.7 HMAC operation

36.3.8 Context swapping

36.3.9 HASH DMA interface

36.3.10 HASH error management

36.4 HASH interrupts

36.5 HASH processing time

36.6 HASH registers

36.6.1 HASH control register (HASH_CR)

36.6.2 HASH data input register (HASH_DIN)

36.6.3 HASH start register (HASH_STR)

36.6.4 HASH digest registers (HASH_HR0..7)

36.6.5 HASH interrupt enable register (HASH_IMR)

36.6.6 HASH status register (HASH_SR)

36.6.7 HASH context swap registers (HASH_CSRx)

36.6.8 HASH register map

37 High-Resolution Timer (HRTIM)

37.1 Introduction

37.2 Main features

37.3 Functional description

37.3.1 General description

37.3.2 HRTIM pins and internal signals

37.3.3 Clocks

37.3.4 Timer A..E timing units

37.3.5 Master timer

37.3.6 Set/reset events priorities and narrow pulses management

37.3.7 External events global conditioning

37.3.8 External event filtering in timing units

37.3.9 Delayed Protection

37.3.10 Register preload and update management

37.3.11 Events propagation within or across multiple timers

37.3.12 Output management

37.3.13 Burst mode controller

37.3.14 Chopper

37.3.15 Fault protection

37.3.16 Auxiliary outputs

37.3.17 Synchronizing the HRTIM with other timers or HRTIM instances

37.3.18 ADC triggers

37.3.19 DAC triggers

37.3.20 HRTIM Interrupts

37.3.21 DMA

37.3.22 HRTIM initialization

37.3.23 Debug

37.4 Application use cases

37.4.1 Buck converter

37.4.2 Buck converter with synchronous rectification

37.4.3 Multiphase converters

37.4.4 Transition mode Power Factor Correction

37.5 HRTIM registers

37.5.1 HRTIM Master Timer Control Register (HRTIM_MCR)

37.5.2 HRTIM Master Timer Interrupt Status Register (HRTIM_MISR)

37.5.3 HRTIM Master Timer Interrupt Clear Register (HRTIM_MICR)

37.5.4 HRTIM Master Timer DMA / Interrupt Enable Register (HRTIM_MDIER)

37.5.5 HRTIM Master Timer Counter Register (HRTIM_MCNTR)

37.5.6 HRTIM Master Timer Period Register (HRTIM_MPER)

37.5.7 HRTIM Master Timer Repetition Register (HRTIM_MREP)

37.5.8 HRTIM Master Timer Compare 1 Register (HRTIM_MCMP1R)

37.5.9 HRTIM Master Timer Compare 2 Register (HRTIM_MCMP2R)

37.5.10 HRTIM Master Timer Compare 3 Register (HRTIM_MCMP3R)

37.5.11 HRTIM Master Timer Compare 4 Register (HRTIM_MCMP4R)

37.5.12 HRTIM Timerx Control Register (HRTIM_TIMxCR)

37.5.13 HRTIM Timerx Interrupt Status Register (HRTIM_TIMxISR)

37.5.14 HRTIM Timerx Interrupt Clear Register (HRTIM_TIMxICR)

37.5.15 HRTIM Timerx DMA / Interrupt Enable Register (HRTIM_TIMxDIER)

37.5.16 HRTIM Timerx Counter Register (HRTIM_CNTxR)

37.5.17 HRTIM Timerx Period Register (HRTIM_PERxR)

37.5.18 HRTIM Timerx Repetition Register (HRTIM_REPxR)

37.5.19 HRTIM Timerx Compare 1 Register (HRTIM_CMP1xR)

37.5.20 HRTIM Timerx Compare 1 Compound Register (HRTIM_CMP1CxR)

37.5.21 HRTIM Timerx Compare 2 Register (HRTIM_CMP2xR)

37.5.22 HRTIM Timerx Compare 3 Register (HRTIM_CMP3xR)

37.5.23 HRTIM Timerx Compare 4 Register (HRTIM_CMP4xR)

37.5.24 HRTIM Timerx Capture 1 Register (HRTIM_CPT1xR)

37.5.25 HRTIM Timerx Capture 2 Register (HRTIM_CPT2xR)

37.5.26 HRTIM Timerx Deadtime Register (HRTIM_DTxR)

37.5.27 HRTIM Timerx Output1 Set Register (HRTIM_SETx1R)

37.5.28 HRTIM Timerx Output1 Reset Register (HRTIM_RSTx1R)

37.5.29 HRTIM Timerx Output2 Set Register (HRTIM_SETx2R)

37.5.30 HRTIM Timerx Output2 Reset Register (HRTIM_RSTx2R)

37.5.31 HRTIM Timerx External Event Filtering Register 1 (HRTIM_EEFxR1)

37.5.32 HRTIM Timerx External Event Filtering Register 2 (HRTIM_EEFxR2)

37.5.33 HRTIM Timerx Reset Register (HRTIM_RSTxR)

37.5.34 HRTIM Timerx Chopper Register (HRTIM_CHPxR)

37.5.35 HRTIM Timerx Capture 1 Control Register (HRTIM_CPT1xCR)

37.5.36 HRTIM Timerx Capture 2 Control Register (HRTIM_CPT2xCR)

37.5.37 HRTIM Timerx Output Register (HRTIM_OUTxR)

37.5.38 HRTIM Timerx Fault Register (HRTIM_FLTxR)

37.5.39 HRTIM Control Register 1 (HRTIM_CR1)

37.5.40 HRTIM Control Register 2 (HRTIM_CR2)

37.5.41 HRTIM Interrupt Status Register (HRTIM_ISR)

37.5.42 HRTIM Interrupt Clear Register (HRTIM_ICR)

37.5.43 HRTIM Interrupt Enable Register (HRTIM_IER)

37.5.44 HRTIM Output Enable Register (HRTIM_OENR)

37.5.45 HRTIM Output Disable Register (HRTIM_ODISR)

37.5.46 HRTIM Output Disable Status Register (HRTIM_ODSR)

37.5.47 HRTIM Burst Mode Control Register (HRTIM_BMCR)

37.5.48 HRTIM Burst Mode Trigger Register (HRTIM_BMTRGR)

37.5.49 HRTIM Burst Mode Compare Register (HRTIM_BMCMPR)

37.5.50 HRTIM Burst Mode Period Register (HRTIM_BMPER)

37.5.51 HRTIM Timer External Event Control Register 1 (HRTIM_EECR1)

37.5.52 HRTIM Timer External Event Control Register 2 (HRTIM_EECR2)

37.5.53 HRTIM Timer External Event Control Register 3 (HRTIM_EECR3)

37.5.54 HRTIM ADC Trigger 1 Register (HRTIM_ADC1R)

37.5.55 HRTIM ADC Trigger 2 Register (HRTIM_ADC2R)

37.5.56 HRTIM ADC Trigger 3 Register (HRTIM_ADC3R)

37.5.57 HRTIM ADC Trigger 4 Register (HRTIM_ADC4R)

37.5.58 HRTIM Fault Input Register 1 (HRTIM_FLTINR1)

37.5.59 HRTIM Fault Input Register 2 (HRTIM_FLTINR2)

37.5.60 HRTIM Burst DMA Master timer update Register (HRTIM_BDMUPR)

37.5.61 HRTIM Burst DMA Timerx update Register (HRTIM_BDTxUPR)

37.5.62 HRTIM Burst DMA Data Register (HRTIM_BDMADR)

37.5.63 HRTIM register map

38 Advanced-control timers (TIM1/TIM8)

38.1 TIM1/TIM8 introduction

38.2 TIM1/TIM8 main features

38.3 TIM1/TIM8 functional description

38.3.1 Time-base unit

38.3.2 Counter modes

38.3.3 Repetition counter

38.3.4 External trigger input

38.3.5 Clock selection

38.3.6 Capture/compare channels

38.3.7 Input capture mode

38.3.8 PWM input mode

38.3.9 Forced output mode

38.3.10 Output compare mode

38.3.11 PWM mode

38.3.12 Asymmetric PWM mode

38.3.13 Combined PWM mode

38.3.14 Combined 3-phase PWM mode

38.3.15 Complementary outputs and dead-time insertion

38.3.16 Using the break function

38.3.17 Bidirectional break inputs

38.3.18 Clearing the OCxREF signal on an external event

38.3.19 6-step PWM generation

38.3.20 One-pulse mode

38.3.21 Retriggerable one pulse mode (OPM)

38.3.22 Encoder interface mode

38.3.23 UIF bit remapping

38.3.24 Timer input XOR function

38.3.25 Interfacing with Hall sensors

38.3.26 Timer synchronization

38.3.27 ADC synchronization

38.3.28 DMA burst mode

38.3.29 Debug mode

38.4 TIM1/TIM8 registers

38.4.1 TIM1/TIM8 control register 1 (TIMx_CR1)

38.4.2 TIM1/TIM8 control register 2 (TIMx_CR2)

38.4.3 TIM1/TIM8 slave mode control register (TIMx_SMCR)

38.4.4 TIM1/TIM8 DMA/interrupt enable register (TIMx_DIER)

38.4.5 TIM1/TIM8 status register (TIMx_SR)

38.4.6 TIM1/TIM8 event generation register (TIMx_EGR)

38.4.7 TIM1/TIM8 capture/compare mode register 1 (TIMx_CCMR1)

38.4.8 TIM1/TIM8 capture/compare mode register 2 (TIMx_CCMR2)

38.4.9 TIM1/TIM8 capture/compare enable register (TIMx_CCER)

38.4.10 TIM1/TIM8 counter (TIMx_CNT)

38.4.11 TIM1/TIM8 prescaler (TIMx_PSC)

38.4.12 TIM1/TIM8 auto-reload register (TIMx_ARR)

38.4.13 TIM1/TIM8 repetition counter register (TIMx_RCR)

38.4.14 TIM1/TIM8 capture/compare register 1 (TIMx_CCR1)

38.4.15 TIM1/TIM8 capture/compare register 2 (TIMx_CCR2)

38.4.16 TIM1/TIM8 capture/compare register 3 (TIMx_CCR3)

38.4.17 TIM1/TIM8 capture/compare register 4 (TIMx_CCR4)

38.4.18 TIM1/TIM8 break and dead-time register (TIMx_BDTR)

38.4.19 TIM1/TIM8 DMA control register (TIMx_DCR)

38.4.20 TIM1/TIM8 DMA address for full transfer (TIMx_DMAR)

38.4.21 TIM1/TIM8 capture/compare mode register 3 (TIMx_CCMR3)

38.4.22 TIM1/TIM8 capture/compare register 5 (TIMx_CCR5)

38.4.23 TIM1/TIM8 capture/compare register 6 (TIMx_CCR6)

38.4.24 TIM1 alternate function option register 1 (TIM1_AF1)

38.4.25 TIM1 Alternate function register 2 (TIM1_AF2)

38.4.26 TIM8 Alternate function option register 1 (TIM8_AF1)

38.4.27 TIM8 Alternate function option register 2 (TIM8_AF2)

38.4.28 TIM1 timer input selection register (TIM1_TISEL)

38.4.29 TIM8 timer input selection register (TIM8_TISEL)

38.4.30 TIM1 register map

38.4.31 TIM8 register map

39 General-purpose timers (TIM2/TIM3/TIM4/TIM5)

39.1 TIM2/TIM3/TIM4/TIM5 introduction

39.2 TIM2/TIM3/TIM4/TIM5 main features

39.3 TIM2/TIM3/TIM4/TIM5 functional description

39.3.1 Time-base unit

39.3.2 Counter modes

39.3.3 Clock selection

39.3.4 Capture/compare channels

39.3.5 Input capture mode

39.3.6 PWM input mode

39.3.7 Forced output mode

39.3.8 Output compare mode

39.3.9 PWM mode

39.3.10 Asymmetric PWM mode

39.3.11 Combined PWM mode

39.3.12 Clearing the OCxREF signal on an external event

39.3.13 One-pulse mode

39.3.14 Retriggerable one pulse mode (OPM)

39.3.15 Encoder interface mode

39.3.16 UIF bit remapping

39.3.17 Timer input XOR function

39.3.18 Timers and external trigger synchronization

39.3.19 Timer synchronization

39.3.20 DMA burst mode

39.3.21 Debug mode

39.4 TIM2/TIM3/TIM4/TIM5 registers

39.4.1 TIMx control register 1 (TIMx_CR1)

39.4.2 TIMx control register 2 (TIMx_CR2)

39.4.3 TIMx slave mode control register (TIMx_SMCR)

39.4.4 TIMx DMA/Interrupt enable register (TIMx_DIER)

39.4.5 TIMx status register (TIMx_SR)

39.4.6 TIMx event generation register (TIMx_EGR)

39.4.7 TIMx capture/compare mode register 1 (TIMx_CCMR1)

39.4.8 TIMx capture/compare mode register 2 (TIMx_CCMR2)

39.4.9 TIMx capture/compare enable register (TIMx_CCER)

39.4.10 TIMx counter (TIMx_CNT)

39.4.11 TIMx prescaler (TIMx_PSC)

39.4.12 TIMx auto-reload register (TIMx_ARR)

39.4.13 TIMx capture/compare register 1 (TIMx_CCR1)

39.4.14 TIMx capture/compare register 2 (TIMx_CCR2)

39.4.15 TIMx capture/compare register 3 (TIMx_CCR3)

39.4.16 TIMx capture/compare register 4 (TIMx_CCR4)

39.4.17 TIMx DMA control register (TIMx_DCR)

39.4.18 TIMx DMA address for full transfer (TIMx_DMAR)

39.4.19 TIM2 alternate function option register 1 (TIM2_AF1)

39.4.20 TIM3 alternate function option register 1 (TIM3_AF1)

39.4.21 TIM5 alternate function option register 1 (TIM5_AF1)

39.4.22 TIM2 timer input selection register (TIM2_TISEL)

39.4.23 TIM3 timer input selection register (TIM3_TISEL)

39.4.24 TIM5 timer input selection register (TIM5_TISEL)

39.4.25 TIMx register map

40 General-purpose timers (TIM12/TIM13/TIM14)

40.1 TIM12/TIM13/TIM14 introduction

40.2 TIM12/TIM13/TIM14 main features

40.2.1 TIM12 main features

40.2.2 TIM13/TIM14 main features

40.3 TIM12/TIM13/TIM14 functional description

40.3.1 Time-base unit

40.3.2 Counter modes

40.3.3 Clock selection

40.3.4 Capture/compare channels

40.3.5 Input capture mode

40.3.6 PWM input mode (only for TIM12)

40.3.7 Forced output mode

40.3.8 Output compare mode

40.3.9 PWM mode

40.3.10 Combined PWM mode (TIM12 only)

40.3.11 One-pulse mode

40.3.12 Retriggerable one pulse mode (OPM) (TIM12 only)

40.3.13 UIF bit remapping

40.3.14 Timer input XOR function

40.3.15 TIM12 external trigger synchronization

40.3.16 Slave mode – combined reset + trigger mode

40.3.17 Timer synchronization (TIM12)

40.3.18 Debug mode

40.4 TIM12 registers

40.4.1 TIM12 control register 1 (TIMx_CR1)

40.4.2 TIM12 slave mode control register (TIMx_SMCR)

40.4.3 TIM12 Interrupt enable register (TIMx_DIER)

40.4.4 TIM12 status register (TIMx_SR)

40.4.5 TIM12 event generation register (TIMx_EGR)

40.4.6 TIM12 capture/compare mode register 1 (TIMx_CCMR1)

40.4.7 TIM12 capture/compare enable register (TIMx_CCER)

40.4.8 TIM12 counter (TIMx_CNT)

40.4.9 TIM12 prescaler (TIMx_PSC)

40.4.10 TIM12 auto-reload register (TIMx_ARR)

40.4.11 TIM12 capture/compare register 1 (TIMx_CCR1)

40.4.12 TIM12 capture/compare register 2 (TIMx_CCR2)

40.4.13 TIM12 timer input selection register (TIM12_TISEL)

40.4.14 TIM12 register map

40.5 TIM13/TIM14 registers

40.5.1 TIM13/TIM14 control register 1 (TIMx_CR1)

40.5.2 TIM13/TIM14 Interrupt enable register (TIMx_DIER)

40.5.3 TIM13/TIM14 status register (TIMx_SR)

40.5.4 TIM13/TIM14 event generation register (TIMx_EGR)

40.5.5 TIM13/TIM14 capture/compare mode register 1 (TIMx_CCMR1)

40.5.6 TIM13/TIM14 capture/compare enable register (TIMx_CCER)

40.5.7 TIM13/TIM14 counter (TIMx_CNT)

40.5.8 TIM13/TIM14 prescaler (TIMx_PSC)

40.5.9 TIM13/TIM14 auto-reload register (TIMx_ARR)

40.5.10 TIM13/TIM14 capture/compare register 1 (TIMx_CCR1)

40.5.11 TIM13 timer input selection register (TIM13_TISEL)

40.5.12 TIM14 timer input selection register (TIM14_TISEL)

40.5.13 TIM13/TIM14 register map

41 General-purpose timers (TIM15/TIM16/TIM17)

41.1 TIM15/TIM16/TIM17 introduction

41.2 TIM15 main features

41.3 TIM16/TIM17 main features

41.4 TIM15/TIM16/TIM17 functional description

41.4.1 Time-base unit

41.4.2 Counter modes

41.4.3 Repetition counter

41.4.4 Clock selection

41.4.5 Capture/compare channels

41.4.6 Input capture mode

41.4.7 PWM input mode (only for TIM15)

41.4.8 Forced output mode

41.4.9 Output compare mode

41.4.10 PWM mode

41.4.11 Combined PWM mode (TIM15 only)

41.4.12 Complementary outputs and dead-time insertion

41.4.13 Using the break function

41.4.14 One-pulse mode

41.4.15 UIF bit remapping

41.4.16 Timer input XOR function (TIM15 only)

41.4.17 External trigger synchronization (TIM15 only)

41.4.18 Slave mode – combined reset + trigger mode

41.4.19 DMA burst mode

41.4.20 Timer synchronization (TIM15)

41.4.21 Debug mode

41.5 TIM15 registers

41.5.1 TIM15 control register 1 (TIM15_CR1)

41.5.2 TIM15 control register 2 (TIM15_CR2)

41.5.3 TIM15 slave mode control register (TIM15_SMCR)

41.5.4 TIM15 DMA/interrupt enable register (TIM15_DIER)

41.5.5 TIM15 status register (TIM15_SR)

41.5.6 TIM15 event generation register (TIM15_EGR)

41.5.7 TIM15 capture/compare mode register 1 (TIM15_CCMR1)

41.5.8 TIM15 capture/compare enable register (TIM15_CCER)

41.5.9 TIM15 counter (TIM15_CNT)

41.5.10 TIM15 prescaler (TIM15_PSC)

41.5.11 TIM15 auto-reload register (TIM15_ARR)

41.5.12 TIM15 repetition counter register (TIM15_RCR)

41.5.13 TIM15 capture/compare register 1 (TIM15_CCR1)

41.5.14 TIM15 capture/compare register 2 (TIM15_CCR2)

41.5.15 TIM15 break and dead-time register (TIM15_BDTR)

41.5.16 TIM15 DMA control register (TIM15_DCR)

41.5.17 TIM15 DMA address for full transfer (TIM15_DMAR)

41.5.18 TIM15 alternate register 1 (TIM15_AF1)

41.5.19 TIM15 input selection register (TIM15_TISEL)

41.5.20 TIM15 register map

41.6 TIM16/TIM17 registers

41.6.1 TIM16/TIM17 control register 1 (TIMx_CR1)

41.6.2 TIM16/TIM17 control register 2 (TIMx_CR2)

41.6.3 TIM16/TIM17 DMA/interrupt enable register (TIMx_DIER)

41.6.4 TIM16/TIM17 status register (TIMx_SR)

41.6.5 TIM16/TIM17 event generation register (TIMx_EGR)

41.6.6 TIM16/TIM17 capture/compare mode register 1 (TIMx_CCMR1)

41.6.7 TIM16/TIM17 capture/compare enable register (TIMx_CCER)

41.6.8 TIM16/TIM17 counter (TIMx_CNT)

41.6.9 TIM16/TIM17 prescaler (TIMx_PSC)

41.6.10 TIM16/TIM17 auto-reload register (TIMx_ARR)

41.6.11 TIM16/TIM17 repetition counter register (TIMx_RCR)

41.6.12 TIM16/TIM17 capture/compare register 1 (TIMx_CCR1)

41.6.13 TIM16/TIM17 break and dead-time register (TIMx_BDTR)

41.6.14 TIM16/TIM17 DMA control register (TIMx_DCR)

41.6.15 TIM16/TIM17 DMA address for full transfer (TIMx_DMAR)

41.6.16 TIM16 alternate function register 1 (TIM16_AF1)

41.6.17 TIM16 input selection register (TIM16_TISEL)

41.6.18 TIM17 alternate function register 1 (TIM17_AF1)

41.6.19 TIM17 input selection register (TIM17_TISEL)

41.6.20 TIM16/TIM17 register map

42 Basic timers (TIM6/TIM7)

42.1 TIM6/TIM7 introduction

42.2 TIM6/TIM7 main features

42.3 TIM6/TIM7 functional description

42.3.1 Time-base unit

42.3.2 Counting mode

42.3.3 UIF bit remapping

42.3.4 Clock source

42.3.5 Debug mode

42.4 TIM6/TIM7 registers

42.4.1 TIM6/TIM7 control register 1 (TIMx_CR1)

42.4.2 TIM6/TIM7 control register 2 (TIMx_CR2)

42.4.3 TIM6/TIM7 DMA/Interrupt enable register (TIMx_DIER)

42.4.4 TIM6/TIM7 status register (TIMx_SR)

42.4.5 TIM6/TIM7 event generation register (TIMx_EGR)

42.4.6 TIM6/TIM7 counter (TIMx_CNT)

42.4.7 TIM6/TIM7 prescaler (TIMx_PSC)

42.4.8 TIM6/TIM7 auto-reload register (TIMx_ARR)

42.4.9 TIM6/TIM7 register map

43 Low-power timer (LPTIM)

43.1 Introduction

43.2 LPTIM main features

43.3 LPTIM implementation

43.4 LPTIM functional description

43.4.1 LPTIM block diagram

43.4.2 LPTIM pins and internal signals

43.4.3 LPTIM input and trigger mapping

43.4.4 LPTIM reset and clocks

43.4.5 Glitch filter

43.4.6 Prescaler

43.4.7 Trigger multiplexer

43.4.8 Operating mode

43.4.9 Timeout function

43.4.10 Waveform generation

43.4.11 Register update

43.4.12 Counter mode

43.4.13 Timer enable

43.4.14 Timer counter reset

43.4.15 Encoder mode

43.5 LPTIM interrupts

43.6 LPTIM registers

43.6.1 LPTIM interrupt and status register (LPTIM_ISR)

43.6.2 LPTIM interrupt clear register (LPTIM_ICR)

43.6.3 LPTIM interrupt enable register (LPTIM_IER)

43.6.4 LPTIM configuration register (LPTIM_CFGR)

43.6.5 LPTIM control register (LPTIM_CR)

43.6.6 LPTIM compare register (LPTIM_CMP)

43.6.7 LPTIM autoreload register (LPTIM_ARR)

43.6.8 LPTIM counter register (LPTIM_CNT)

43.6.9 LPTIM configuration register 2 (LPTIMx_CFGR2, x=1,2)

43.6.10 LPTIM3 configuration register 2 (LPTIM3_CFGR2)

43.6.11 LPTIM register map

44 System window watchdog (WWDG)

44.1 Introduction

44.2 WWDG main features

44.3 WWDG functional description

44.3.1 WWDG block diagram

44.3.2 WWDG internal signals

44.3.3 Enabling the watchdog

44.3.4 Controlling the downcounter

44.3.5 Advanced watchdog interrupt feature

44.3.6 How to program the watchdog timeout

44.3.7 Debug mode

44.4 .WWDG registers

44.4.1 Control register (WWDG_CR)

44.4.2 Configuration register (WWDG_CFR)

44.4.3 Status register (WWDG_SR)

44.4.4 WWDG register map

45 Independent watchdog (IWDG)

45.1 Introduction

45.2 IWDG main features

45.3 IWDG functional description

45.3.1 IWDG block diagram

45.3.2 IWDG internal signals

45.3.3 Window option

45.3.4 Hardware watchdog

45.3.5 Low-power freeze

45.3.6 Behavior in Stop and Standby modes

45.3.7 Register access protection

45.3.8 Debug mode

45.4 IWDG registers

45.4.1 Key register (IWDG_KR)

45.4.2 Prescaler register (IWDG_PR)

45.4.3 Reload register (IWDG_RLR)

45.4.4 Status register (IWDG_SR)

45.4.5 Window register (IWDG_WINR)

45.4.6 IWDG register map

46 Real-time clock (RTC)

46.1 Introduction

46.2 RTC main features

46.3 RTC functional description

46.3.1 RTC block diagram

46.3.2 RTC pins and internal signals

46.3.3 GPIOs controlled by the RTC

46.3.4 Clock and prescalers

46.3.5 Real-time clock and calendar

46.3.6 Programmable alarms

46.3.7 Periodic auto-wakeup

46.3.8 RTC initialization and configuration

46.3.9 Reading the calendar

46.3.10 Resetting the RTC

46.3.11 RTC synchronization

46.3.12 RTC reference clock detection

46.3.13 RTC smooth digital calibration

46.3.14 Time-stamp function

46.3.15 Tamper detection

46.3.16 Calibration clock output

46.3.17 Alarm output

46.4 RTC low-power modes

46.5 RTC interrupts

46.6 RTC registers

46.6.1 RTC time register (RTC_TR)

46.6.2 RTC date register (RTC_DR)

46.6.3 RTC control register (RTC_CR)

46.6.4 RTC initialization and status register (RTC_ISR)

46.6.5 RTC prescaler register (RTC_PRER)

46.6.6 RTC wakeup timer register (RTC_WUTR)

46.6.7 RTC alarm A register (RTC_ALRMAR)

46.6.8 RTC alarm B register (RTC_ALRMBR)

46.6.9 RTC write protection register (RTC_WPR)

46.6.10 RTC sub second register (RTC_SSR)

46.6.11 RTC shift control register (RTC_SHIFTR)

46.6.12 RTC timestamp time register (RTC_TSTR)

46.6.13 RTC timestamp date register (RTC_TSDR)

46.6.14 RTC time-stamp sub second register (RTC_TSSSR)

46.6.15 RTC calibration register (RTC_CALR)

46.6.16 RTC tamper configuration register (RTC_TAMPCR)

46.6.17 RTC alarm A sub second register (RTC_ALRMASSR)

46.6.18 RTC alarm B sub second register (RTC_ALRMBSSR)

46.6.19 RTC option register (RTC_OR)

46.6.20 RTC backup registers (RTC_BKPxR)

46.6.21 RTC register map

47 Inter-integrated circuit (I2C) interface

47.1 Introduction

47.2 I2C main features

47.3 I2C implementation

47.4 I2C functional description

47.4.1 I2C block diagram

47.4.2 I2C clock requirements

47.4.3 Mode selection

47.4.4 I2C initialization

47.4.5 Software reset

47.4.6 Data transfer

47.4.7 I2C slave mode

47.4.8 I2C master mode

47.4.9 I2C_TIMINGR register configuration examples

47.4.10 SMBus specific features

47.4.11 SMBus initialization

47.4.12 SMBus: I2C_TIMEOUTR register configuration examples

47.4.13 SMBus slave mode

47.4.14 Wakeup from Stop mode on address match

47.4.15 Error conditions

47.4.16 DMA requests

47.4.17 Debug mode

47.5 I2C low-power modes

47.6 I2C interrupts

47.7 I2C registers

47.7.1 Control register 1 (I2C_CR1)

47.7.2 Control register 2 (I2C_CR2)

47.7.3 Own address 1 register (I2C_OAR1)

47.7.4 Own address 2 register (I2C_OAR2)

47.7.5 Timing register (I2C_TIMINGR)

47.7.6 Timeout register (I2C_TIMEOUTR)

47.7.7 Interrupt and status register (I2C_ISR)

47.7.8 Interrupt clear register (I2C_ICR)

47.7.9 PEC register (I2C_PECR)

47.7.10 Receive data register (I2C_RXDR)

47.7.11 Transmit data register (I2C_TXDR)

47.7.12 I2C register map

48 Universal synchronous asynchronous receiver transmitter (USART)

48.1 USART introduction

48.2 USART main features

48.3 USART extended features

48.4 USART implementation

48.5 USART functional description

48.5.1 USART block diagram

48.5.2 USART signals

48.5.3 USART character description

48.5.4 USART FIFOs and thresholds

48.5.5 USART transmitter

48.5.6 USART receiver

48.5.7 USART baud rate generation

48.5.8 Tolerance of the USART receiver to clock deviation

48.5.9 USART Auto baud rate detection

48.5.10 USART multiprocessor communication

48.5.11 USART Modbus communication

48.5.12 USART parity control

48.5.13 USART LIN (local interconnection network) mode

48.5.14 USART synchronous mode

48.5.15 USART single-wire Half-duplex communication

48.5.16 USART receiver timeout

48.5.17 USART Smartcard mode

48.5.18 USART IrDA SIR ENDEC block

48.5.19 Continuous communication using USART and DMA

48.5.20 RS232 Hardware flow control and RS485 Driver Enable

48.5.21 USART low-power management

48.6 USART interrupts

48.7 USART registers

48.7.1 USART control register 1 (USART_CR1)

48.7.2 USART control register 2 (USART_CR2)

48.7.3 USART control register 3 (USART_CR3)

48.7.4 USART baud rate register (USART_BRR)

48.7.5 USART guard time and prescaler register (USART_GTPR)

48.7.6 USART receiver timeout register (USART_RTOR)

48.7.7 USART request register (USART_RQR)

48.7.8 USART interrupt and status register (USART _ISR)

48.7.9 USART interrupt flag clear register (USART_ICR)

48.7.10 USART receive data register (USART_RDR)

48.7.11 USART transmit data register (USART_TDR)

48.7.12 USART prescaler register (USART_PRESC)

48.7.13 USART register map

49 Low-power universal asynchronous receiver transmitter (LPUART)

49.1 LPUART introduction

49.2 LPUART main features

49.3 LPUART functional description

49.3.1 LPUART block diagram

49.3.2 LPUART signals

49.3.3 LPUART character description

49.3.4 LPUART FIFOs and thresholds

49.3.5 LPUART transmitter

49.3.6 LPUART receiver

49.3.7 LPUART baud rate generation

49.3.8 Tolerance of the LPUART receiver to clock deviation

49.3.9 LPUART multiprocessor communication

49.3.10 LPUART parity control

49.3.11 LPUART single-wire Half-duplex communication

49.3.12 Continuous communication using DMA and LPUART

49.3.13 RS232 Hardware flow control and RS485 Driver Enable

49.3.14 LPUART low-power management

49.4 LPUART interrupts

49.5 LPUART registers

49.5.1 Control register 1 (LPUART_CR1)

49.5.2 Control register 2 (LPUART_CR2)

49.5.3 Control register 3 (LPUART_CR3)

49.5.4 Baud rate register (LPUART_BRR)

49.5.5 Request register (LPUART_RQR)

49.5.6 Interrupt & status register (LPUART_ISR)

49.5.7 Interrupt flag clear register (LPUART_ICR)

49.5.8 Receive data register (LPUART_RDR)

49.5.9 Transmit data register (LPUART_TDR)

49.5.10 Prescaler register (LPUART_PRESC)

49.5.11 LPUART register map

50 Serial peripheral interface (SPI)

50.1 Introduction

50.2 SPI main features

50.3 SPI implementation

50.4 SPI functional description

50.4.1 SPI block diagram