微机原理课程设计

学院:

姓名:

学号:

时间:2010.4—2010.6

�

一、设计目的:

通过课程设计加深对所学《微型计算机原理与应用》这门课的理解,理解

CPU 8088 的基本系统的功能和它最小系统的工作方式,掌握 8255、8259、8254、

8279、0809、0832 等芯片的功能和应用。在课程设计中培养我们分析问题、解

决问题的方法,培养较强的动手能力和一定的微机应用系统的设计和调试能力。

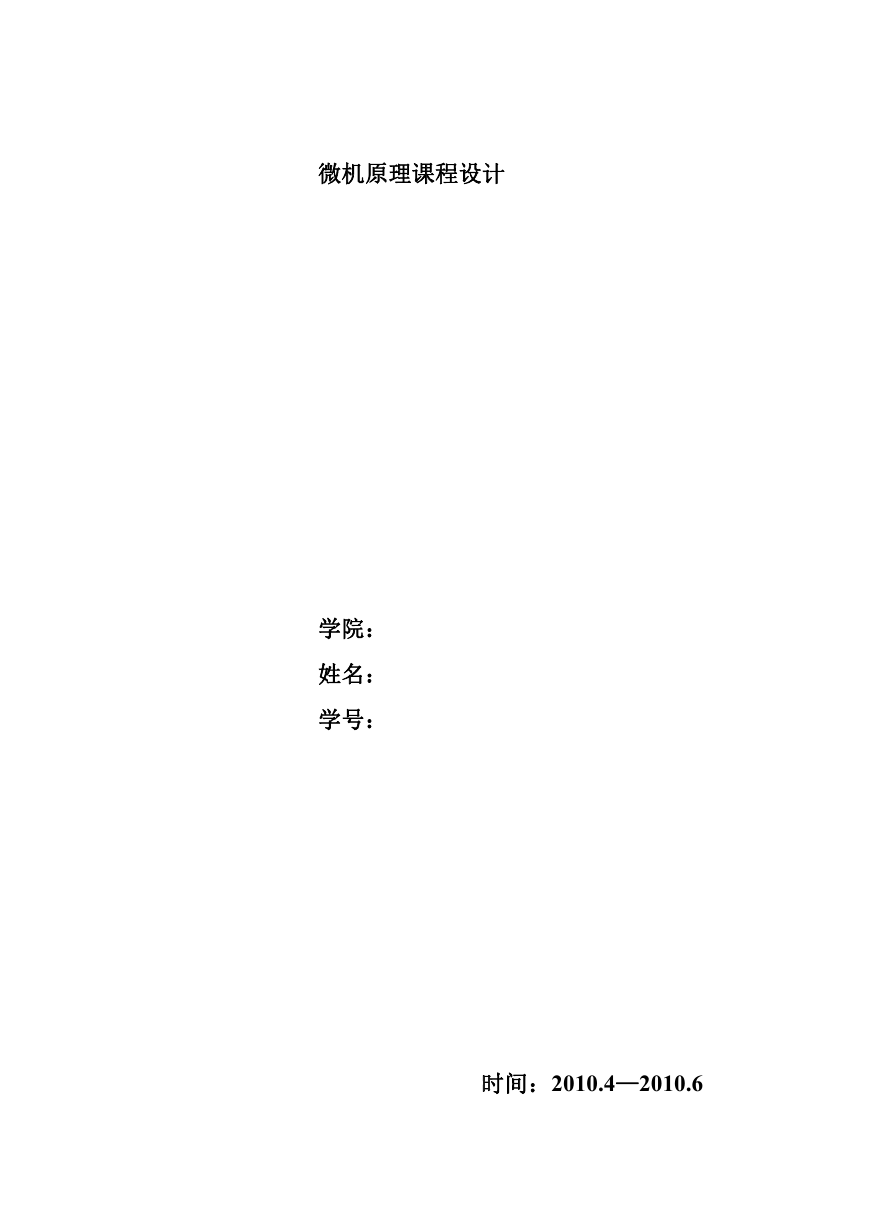

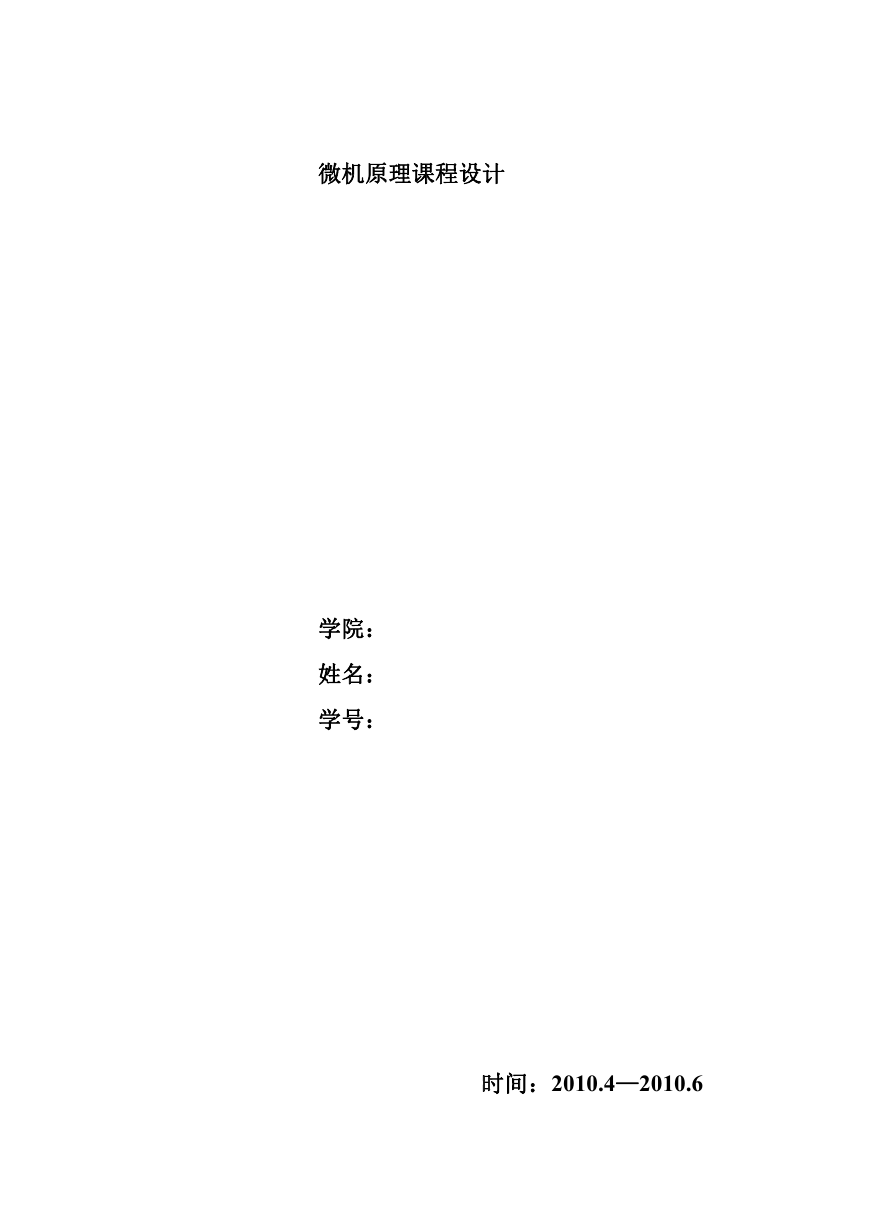

二、设计要求:

选用 8088 为 CPU,用 2 片 2764 组成最小系统的 ROM,2 片 6264 组成最

小系统的 RAM,采用 8284 芯片组成系统的时钟电路,利用 74LS138 为译码电

路;用 8255,0809、0832、8253 以及 8259 等芯片最小系统的的控制系统。

系统的总框图如下:

三、设计过程:

2

�

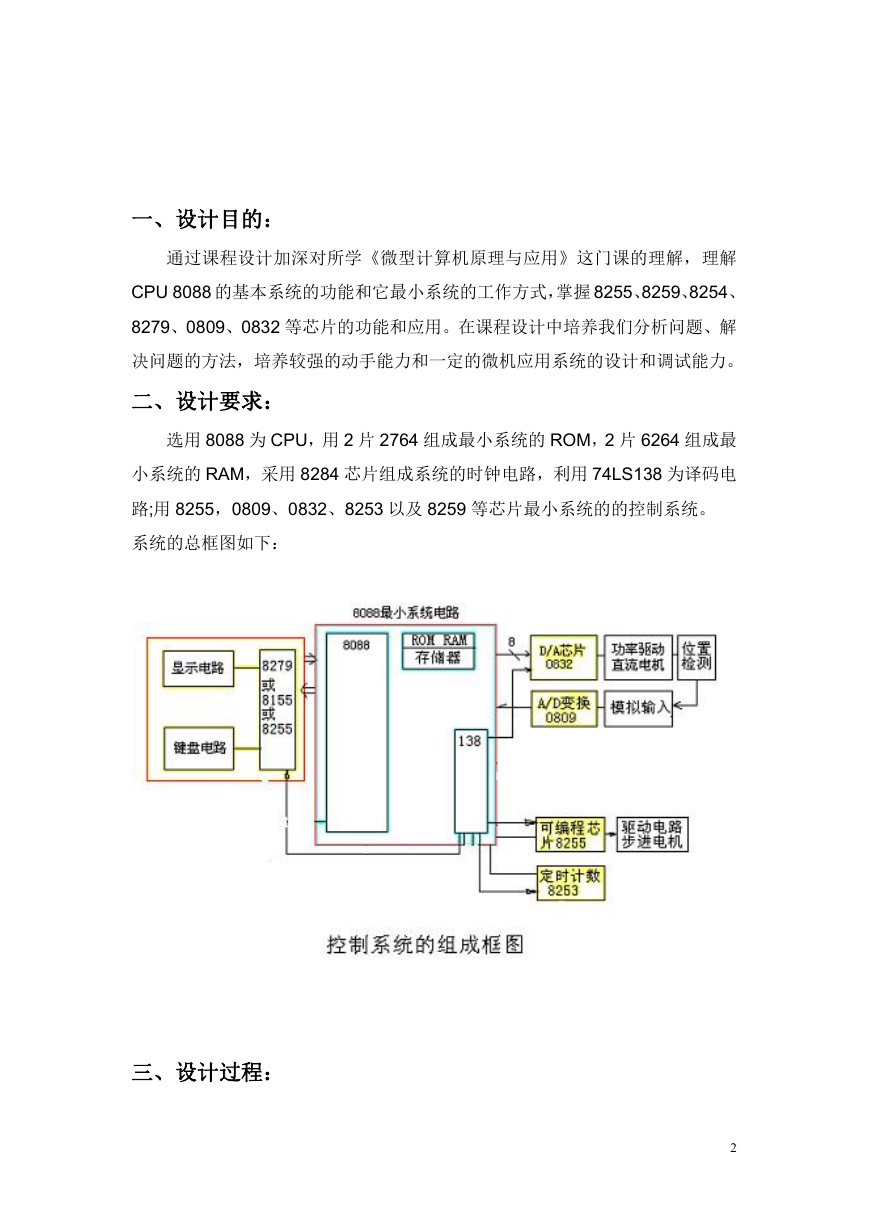

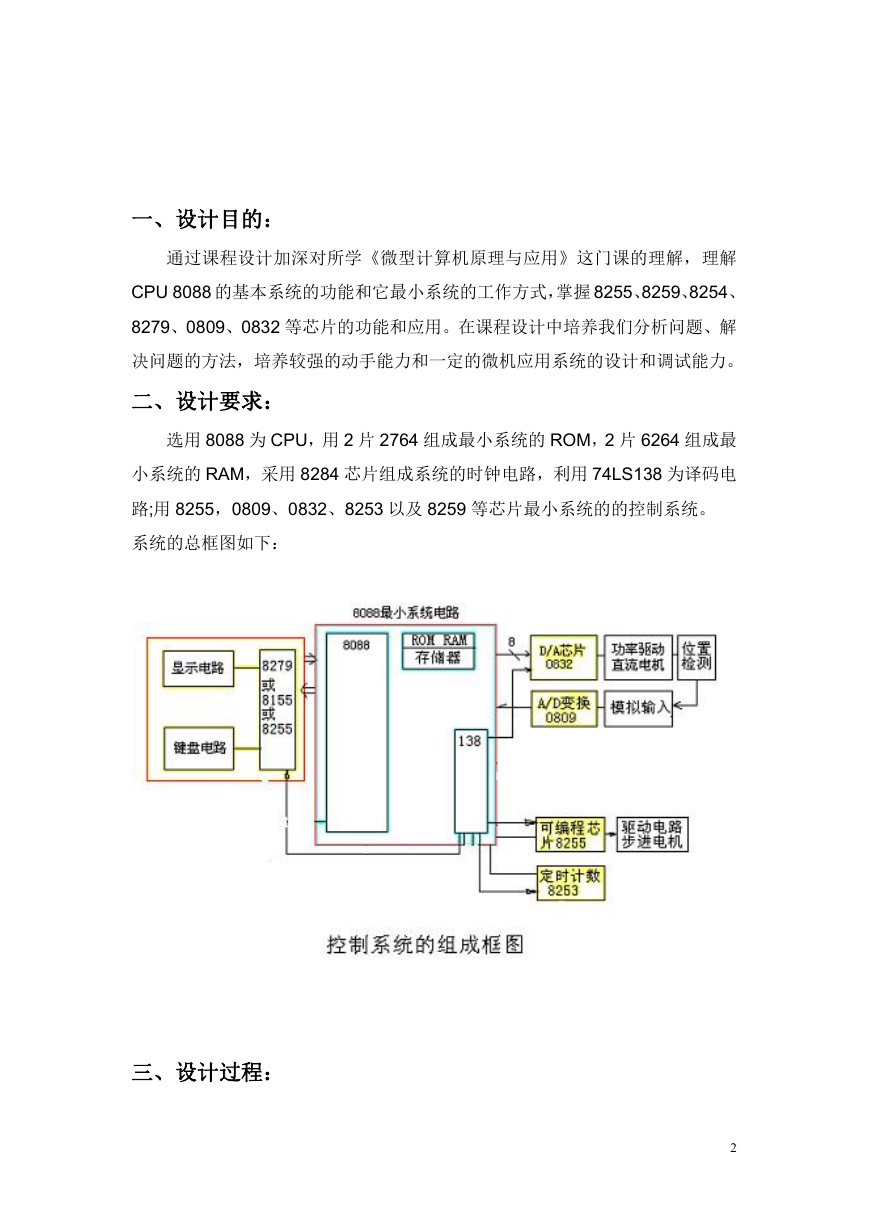

1、8088 最小系统电路的设计

A:选用 8088 为 CPU 其芯片如图:

其内部结构为:

8088 最小模式是指构成的系统规模比较小,只含 8088 一个微处理器,三大总线连接比

较简单。系统的地址总线除了 A19~A16,AD7~AD0 通过地址锁存器 8282 提供,系统的数

据总线可由 CPU 的 AD7~AD0 直接提供,提供也可通过收发器接口芯片 8286 提供,一增

大数据的驱动能力,这是负载情况而定。而系统的控制总线直接由 CPU 的控制总线提供。

这样系统中与总线控制有关的逻辑电路减到了最小的程度。如下图所示

3

�

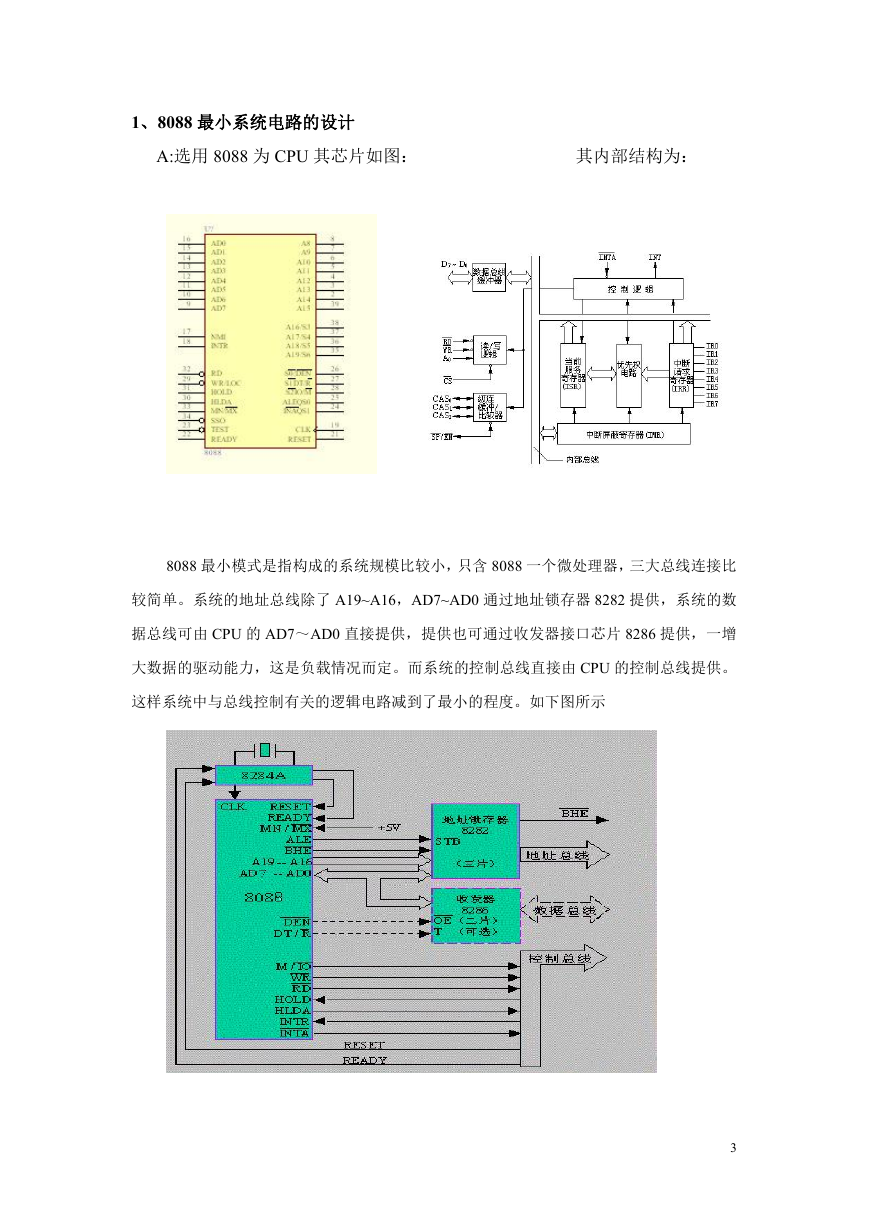

图 8284A 为时钟发生器,它除了给 CPU 提供频率恒定的时钟信号 CLK 外,

还对外部来的准备好信号 RDY 及复位信号 RESET 进行同步。引外部对这两个

信号的发出是随机的,经 8284 内部逻辑电路在时钟脉冲下同步,被同步的准备

好信号 RESET 和复位信号 RESET 从 8284A 输出。送至 8088CPU。

对于图所示系统,存储器可空间为 1MB,数据总线为 8BIT 宽,若某校系统

内存只需 64K,则用 16 根地址线就够了。

1. 与工作模式无关的引脚

⑴AD7~AD0(双向。三态)

为低 8 位地址/数据的复用引脚线。采用分时的多路转换方法来实现对地址线和数据线

的复用。在总线坐骑的 T1 状态。这些银线表示为这些银线用作株距总线。可见对复用信号

使用时间来加以划分的。它要求在 T1 状态线出现低 8 位地址时,用地址锁存器加以锁存。

这样在随后的 T 状态,即使这些线用作数据线,而第 8 位地址线的地址在个体却被记录保

存下来,并送到地址总线上。在 DMA 方式时,这些银线被浮置为高阻状态。

⑵A15~A8(输出,三态)

为 8 位地址线。在读写存储器或外设端口色中个总线周期内,都作为地址线输出高 8

位地址。

在 DMA 方式时,这些引线被浮置为高阻。

⑶A19/S6~A16/S3(输出、三态)

为地址/状态服用引脚线,在总线周期的 T1 状态,这些银线表示为最高 4 位的地址线,

在总线周期的其他 T 状态,这些银胶用作提供状态信息,同样需要地址锁存器对 T1 状态出

现的最高 4 位地址加以锁存。

状态信息 S6 总是为低电平,S5 反映当前允许中断标志的状态。S4 与 S3 一起指示当前

那一个段寄存器被使用。

在 DMA 方式时,这些引线被浮置为高阻。

⑷RD(输出、三态)

读信号,当其有效时表示正在对存储器或 I/O 端口进行读操作。若 IO/M 为低电平,

表示读取存储器的数据,若 IO/M 为高电平,表示读取 I/O 端口的数据。

在 DMA 方式时,这些引线被浮置为高阻。

⑸READY(输入)

4

�

为准备就绪信号。低电平有效。本信号由等待指令 WAIT 来检查。我们知道当 CPU 执

行 WAIT 指令时,CPU 处于等待状态,一旦检测到 TEST 号为低,则结束等待状态,继续

执行 WAIT 指令下面的指令。

⑹TEST(输入)

为检测信号,低电平有效。本信号由低呢古代指令 WAIT 来检查。我们知道当 CPU 执

行 WAIT 指令时,CPU 处于等待状态,一旦检测到 TEST 号为低,则结束等待状态,继续

执行 WAIT 指令下面的指令。

⑺INTR(输入)

可屏蔽中断请求信号,高电平有效。CPU 在执行每条指令的最后一个 T 状态时,去采

样 INTR 信号,若发现有效,而中断允许标志 IF 有为 1,则 CPU 在结束当前指令周期后相

应中断请求,赚取执行中断处理程序。

(8)NMI(输入)

非屏幕中断请求信号,为一个边缘触发信号,不能有软件加以屏蔽。只要在 NMI 线上

出现由低到高的变化信号,则 CPU 就会在当前指令中,赚取之行给屏蔽中断处理程序。

⑼RESET(输入)

复位信号,高电平有效,复位时该信号要求维持高电平值到 4 个时钟周期,若使初次加

电,则高电平信号至少要保持 50us,复位信号的到来,将立即结束 CPU 的当前操作,内部

寄存器恢复到初始状态。

当 RESET 信号从高电平回到低电平时,及复位后进入重新启动时,变质型从内存

FFFF0H 处带式的指令,通常在 FFFF0H 存放一条无条件转移指令,转移到系统程序的实际

入口处。这样只要系统被复位启动,就自动进入系统程序。

⑽CLK(输入)

时钟信号,它为 CPU 和总线控制电路提供基准时钟,对时钟信号要求:1/3 周期为高

电平,2/3 周期为低电平。8088 的标准时钟频率为 5MZ。

⑾电源和地

VCC 为电源引线,单一的为+5V 电源。引脚为 1 和 20 为两条 GND 线,要求均要接地

⑿MN/MX(输入)

为最小/最大模式信号,它决定 8088 的工作模式。将此引线接电源 5V,则 8088 工作

与最小模式,若此引线接地,则 8088 工作在最大模式。

引脚 24~31 在不同模式下有不同的功能含义。下面分别加以介绍。

5

�

2. 最小模式下的引脚

把 MN/MX 引脚连至电源,8088 处与最小模式,此时引脚 24~31 的功能含义如下:

⑴INTA

CPU 向外输出的中断响应信号,用于对外部中断与发出中断请求的响应。中断响应周

期由连个连续的总线周期组成,在每个响应周期的 T2,T3 和 TW 状态,INTA 均为有效,

在第二个中断响应周期,外设端口网数据总线上发送中断类型号,CPU 根据中断向量而转

向中断处理程序。

⑵ALE

地址锁存允许信号,高电平有效。在总线州的 T1 状态,当地质/数据复用点 AD3~AD0

和地质/状态服用线 A19/A6~A16/S3 上出现地址信号时,CPU 提供 ALE 有效电平,将

地址信息锁存到地址锁存器中。

⑶DEN

数据允许信号。在使用 8286/8287 数据树发起的最小模式系统中,在存储器访问周期,

I/O 访问周期或中断响应周期,此信号有效,用来作为 8286/8287 数据收发器的输出允许

信号,即允许收发器和系统数据总线进行数据传送。

在 DMA 方式时,此线被浮置为高阻。

⑷DT

数据发送/接收控制信号。在使用 8286/8287 数据收发器的最小模式系统中,用 DT

/R 来控制数据传送方向。DT/R 为高电平,进行数据发送,及收发器把数据送系统数据

总线,而当 DT/R 为低电平,进行数据接收,及收发器把系统数据总线上的数据读进来了

当 CPU 处与 DMA 方式时,此线浮空。

⑸IO/M

访问存储器或 I/O 端口的控制信号。若 IO/M 为高电平,则访问的是 I/O 端口;若

IO/M 为低电平,则访问的是存储器。

⑹WR

写信号。当其有效时表示 CPU 正在对存储器或 I/O 端口进行写操作,具体对水进行写

操作,有 IO/M 信号决定。本信号在总线周期的 T2,T3。TW 状态有效。

在 DMA 方式时,此线被浮置为高阻。

⑺HOLD

总线保持请求信号。当系统中 CPU 之外的总线主设备要求占用总线时,通过 HOLD 引

6

�

县向 CPU 发出高电平的请求信号,如果 CPU 允许让出总线,则在当前周期的 T1 状态,向

HLDA 银线输出一高电平信号作为相应。同时使地址总线,数据总线和相应的控制线处于负

控状态,则总线请求主设备取得了对总线的控制权。一旦总线使用完毕,总线请求主设备让

HOLD 变为低电平。CPU 检测到 HOLD 为低后,把 HLDA 也只为低电平,CPU 有多的了对

总线的控制权。

⑻HLDA

总线保持相应信号。当 HLDA 有效时,表示 CPU 对总线请求主设备作出相应,用移让

出总线,与 CPU 相连的三态银线都被估值为高阻态。

⑼SSO

系统状态信号,它与 IO/M,DT/R 共同组合放映当前总线周期执行的是什么操作。

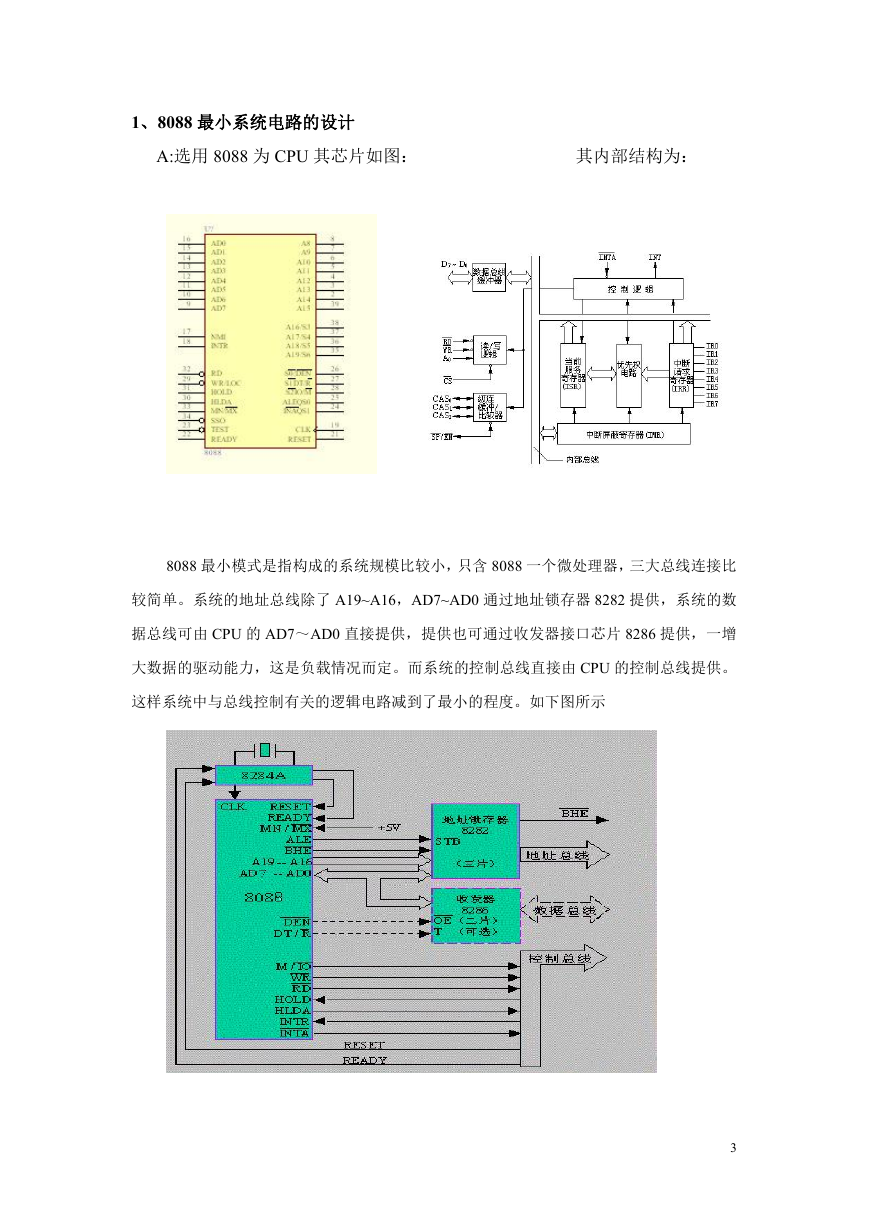

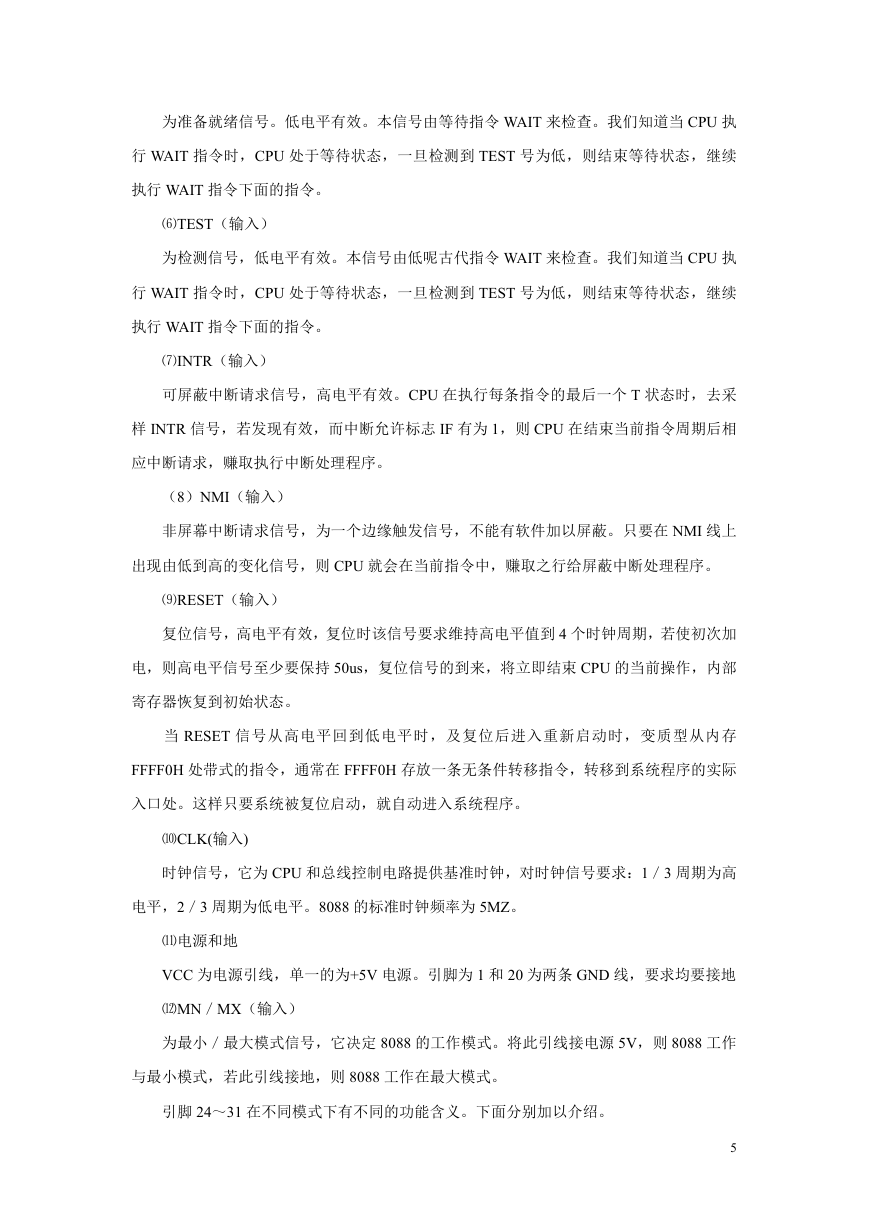

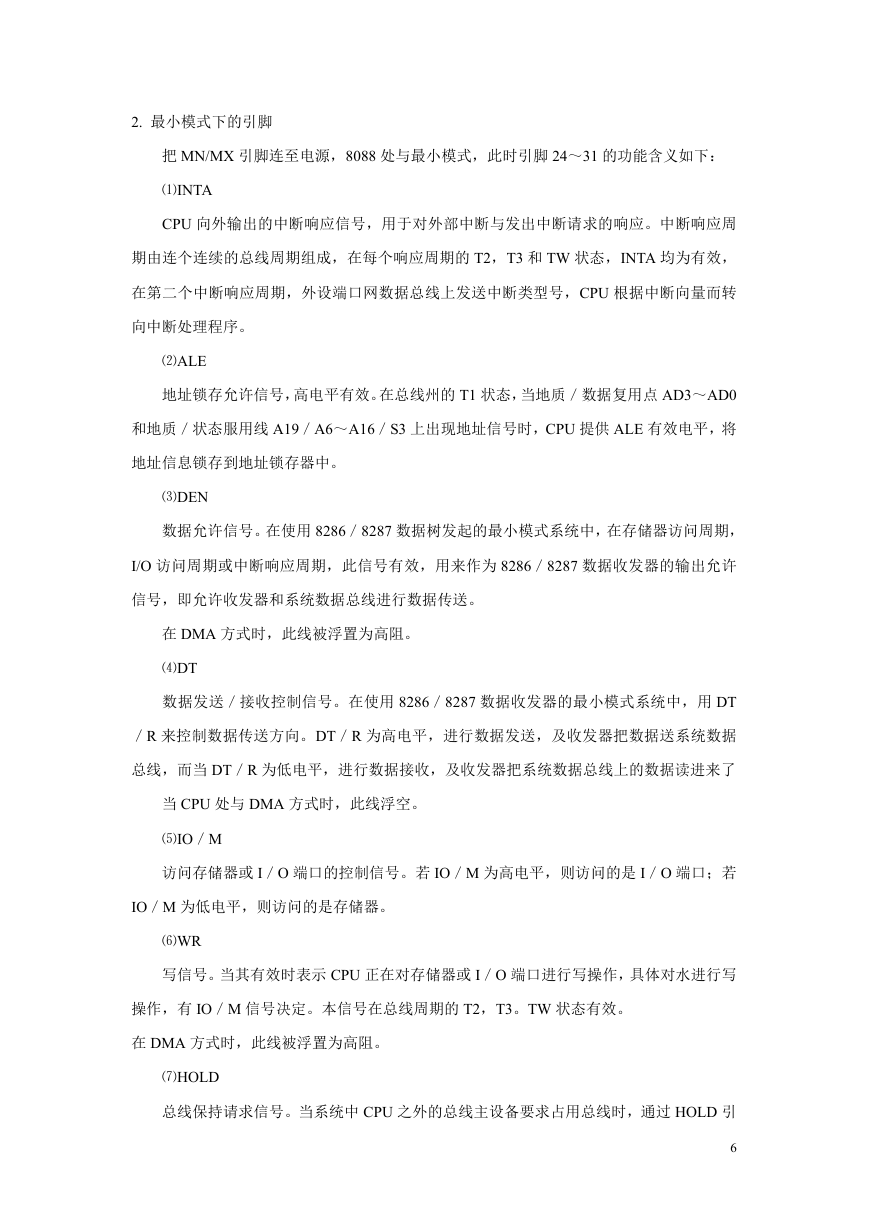

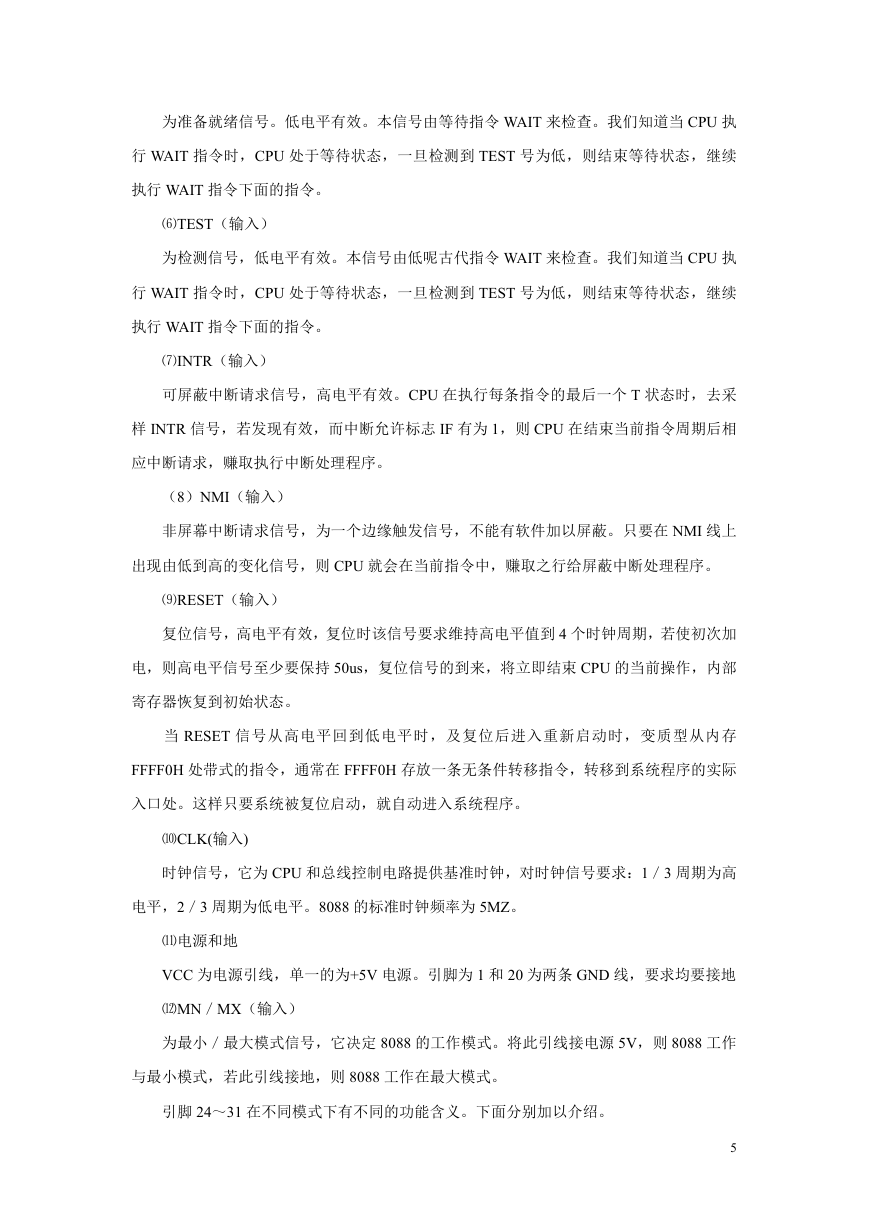

B:选用 3 片 8282 为地址锁存器,如图:

将 8088 的 20 位地址和 BHE#信号分为 3 组,和 3 片 8282 的 DI7~DI0 连接,

CPU 的地址锁存使能 ALE 与 8282 的 STB 端相连。在 ALE 的下降沿时,对地址

信号进行锁存。地址锁存器 8282 相当于 8 个 D 触发器。 从真值表可以看出,

当 OE#为高,DO7~DO0 为高阻状态。当 OE#为低 STB 为高时,8282 的输出等

于输入, 8282 的输出信号 DO7~DO0 与输入信号 DI7~DI0 相等。当 STB 由 高

变低,信号被锁存。OE#为高电平时,8282 的输出为高阻态,OE#为低,DO7~

DO0 有效。具体细节可以参见图 4.2.5 的真值表。

7

�

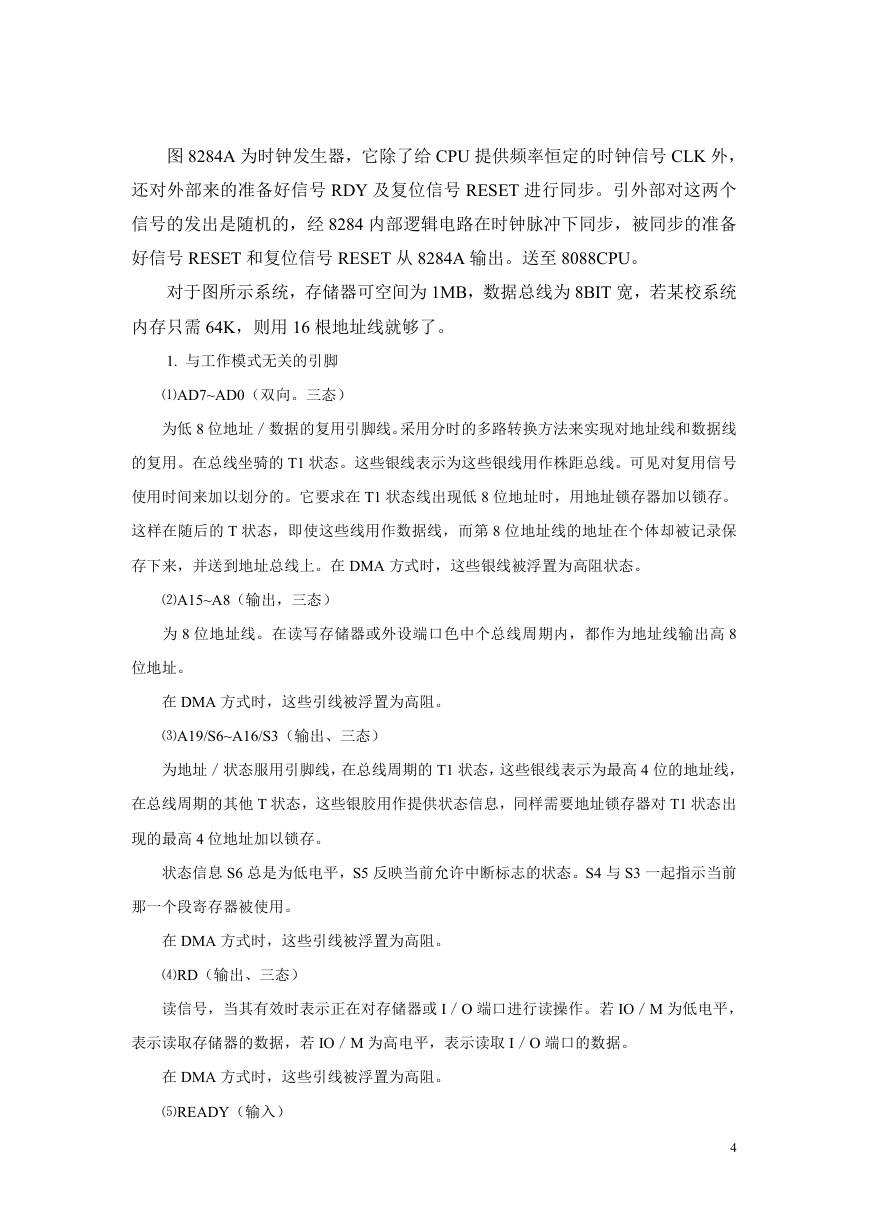

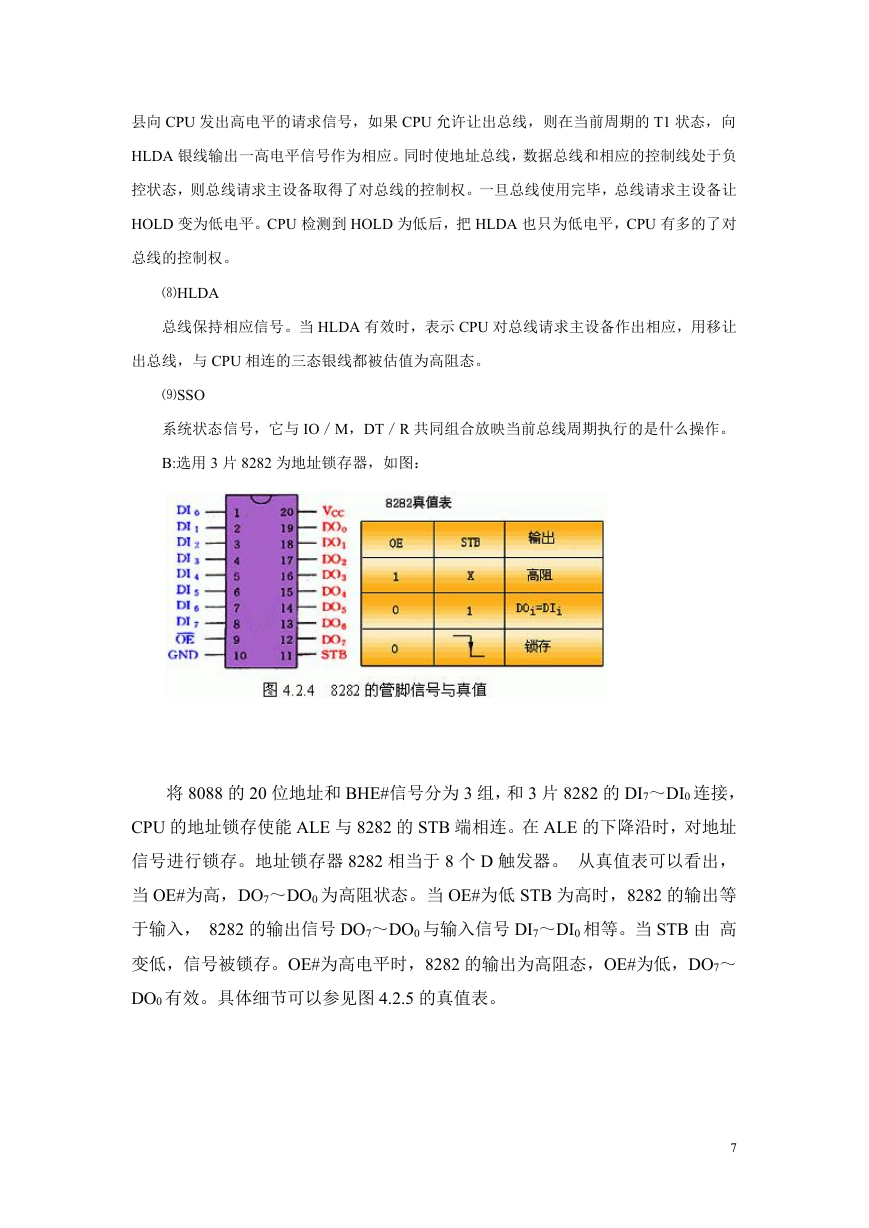

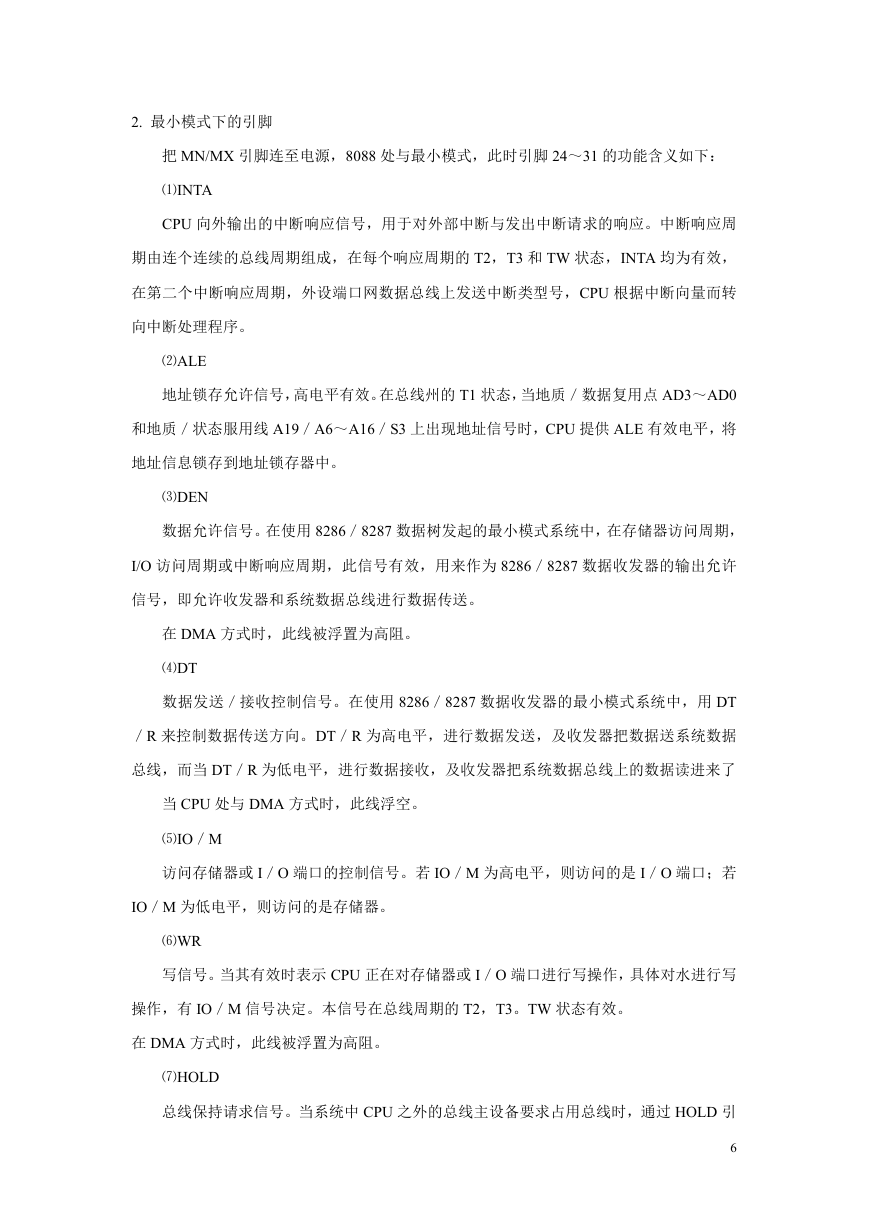

C:选用 2 片 2764 和 2 片 6264 构成最小系统的存储器,如图:

8088 CPU 的地址总线为 A0~A15,数据总线为 D0~D7,RD 为读信号,低电

平有效,有效时表示 CPU 正在执行从存储器输入操作。WR 为写信号,低电平有

效,有效时表示 CPU 正在执行向存储器输出操作。选用的 ROM 模块芯片为

EPROM2764,容量为 8K*8。该芯片引脚说明如下:A0~A12 为地址线,O0~O7 为

数据线,CE 为片选信号,OE 为数据输出允许信号。PGM 为编程控制信号,Vpp

为编程电压,正常输出时 PGM 和 Vpp 均接+5V,工作电压 Vcc 为+5V。选用的

RAM 模块芯片为 SRAM6264,容量为 8K*8。该芯片引脚说明如下:A0~A12 为地址

线,O0~O7 为数据线,CS1 为第一片选信号,低电平有效,CS2 为第二片选信

号,高电平有效,只有 CS1 和 CS2 同时有效时,芯片才被选中。ROM 模块的地

址为 000H~3FFFH,RAM 模块的地址为 8000H~BFFFH,时钟频率为 2MHz。

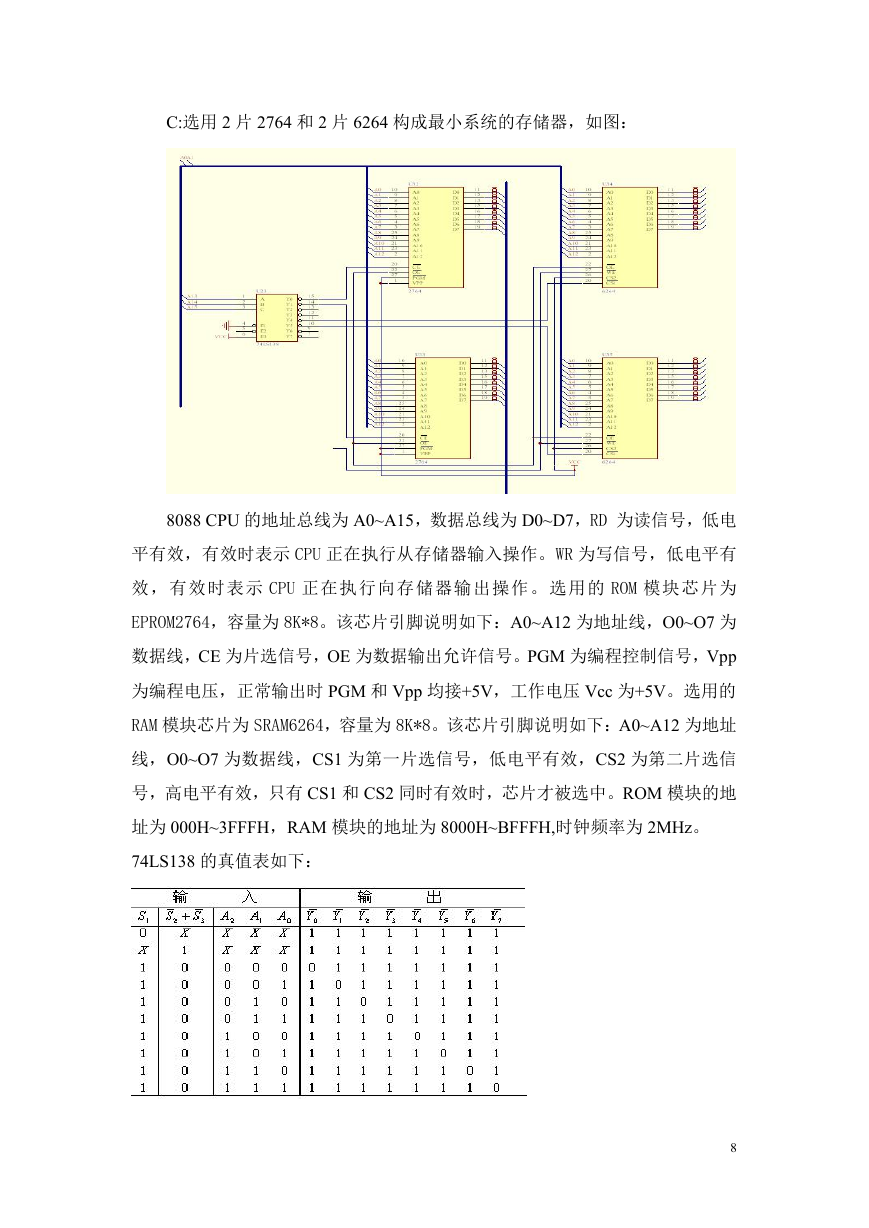

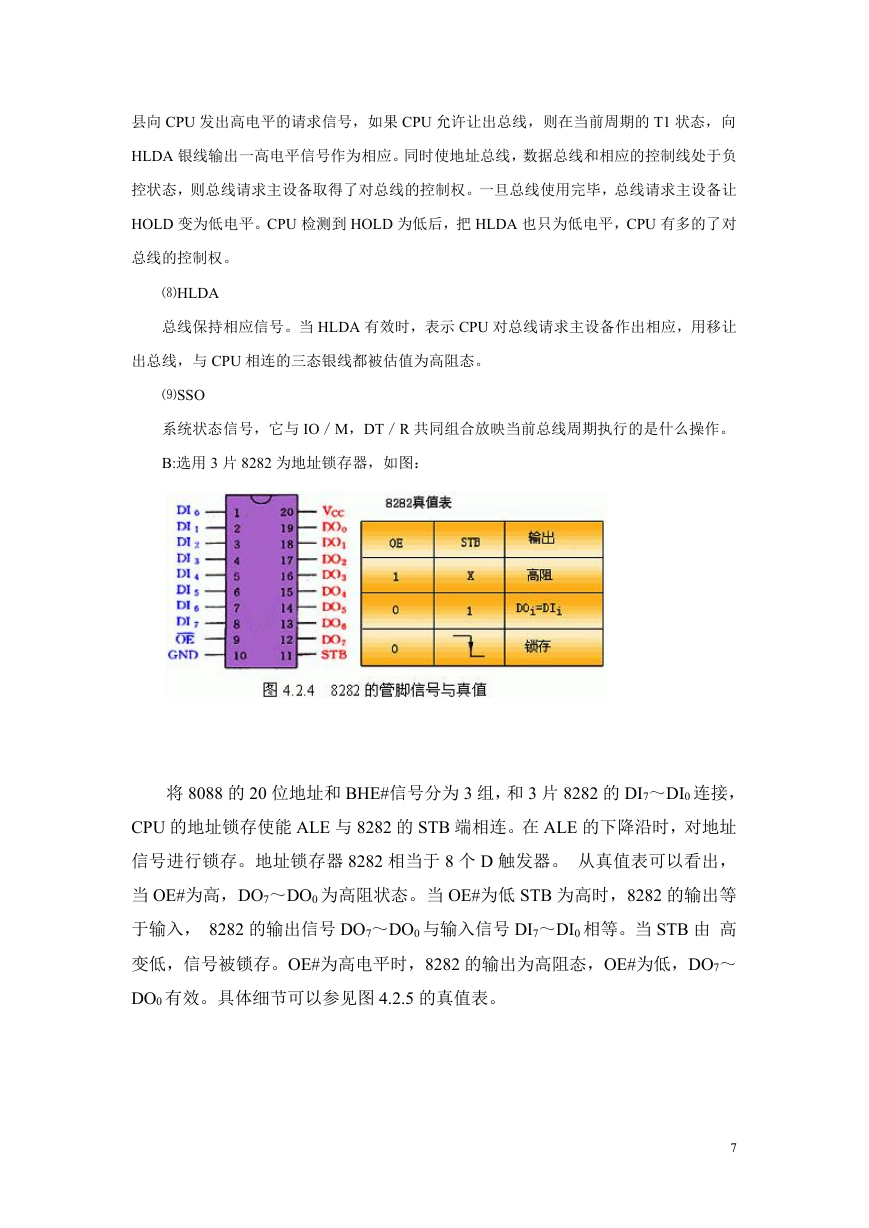

74LS138 的真值表如下:

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc