1. Introduction

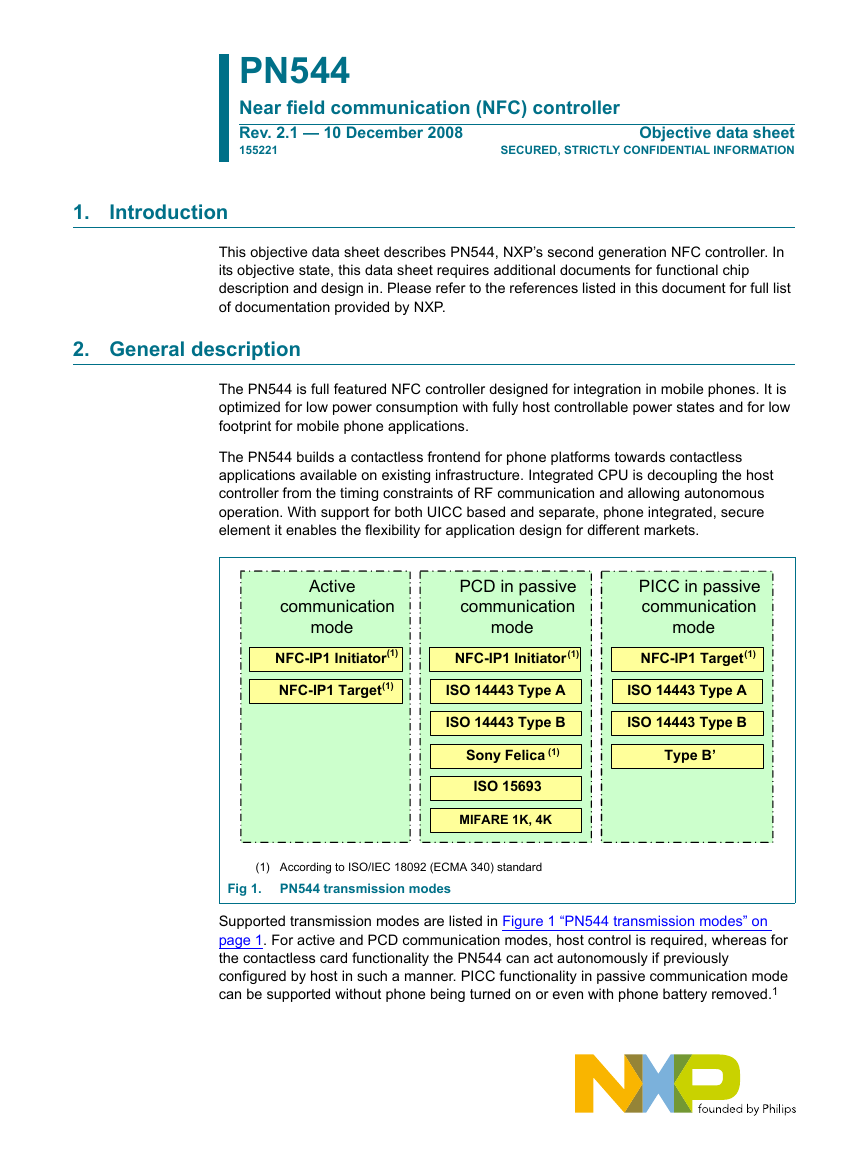

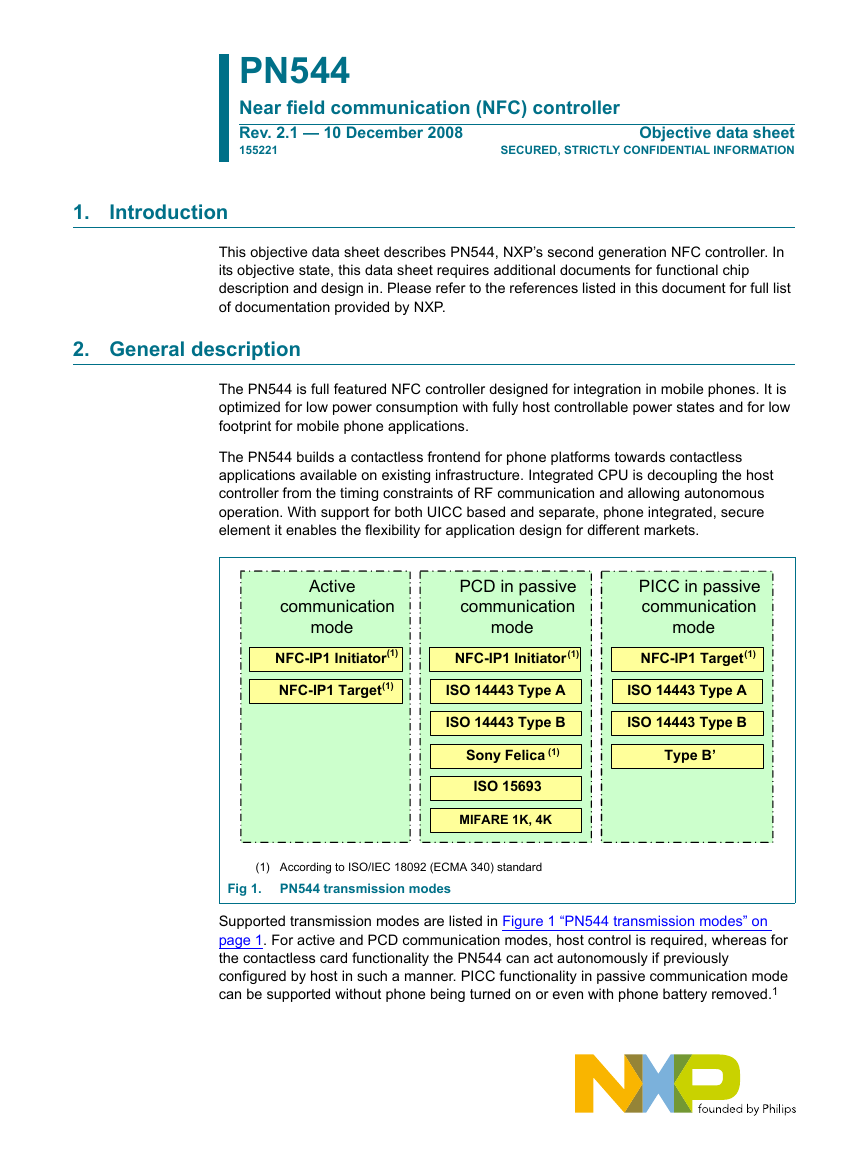

2. General description

3. Features

4. Applications

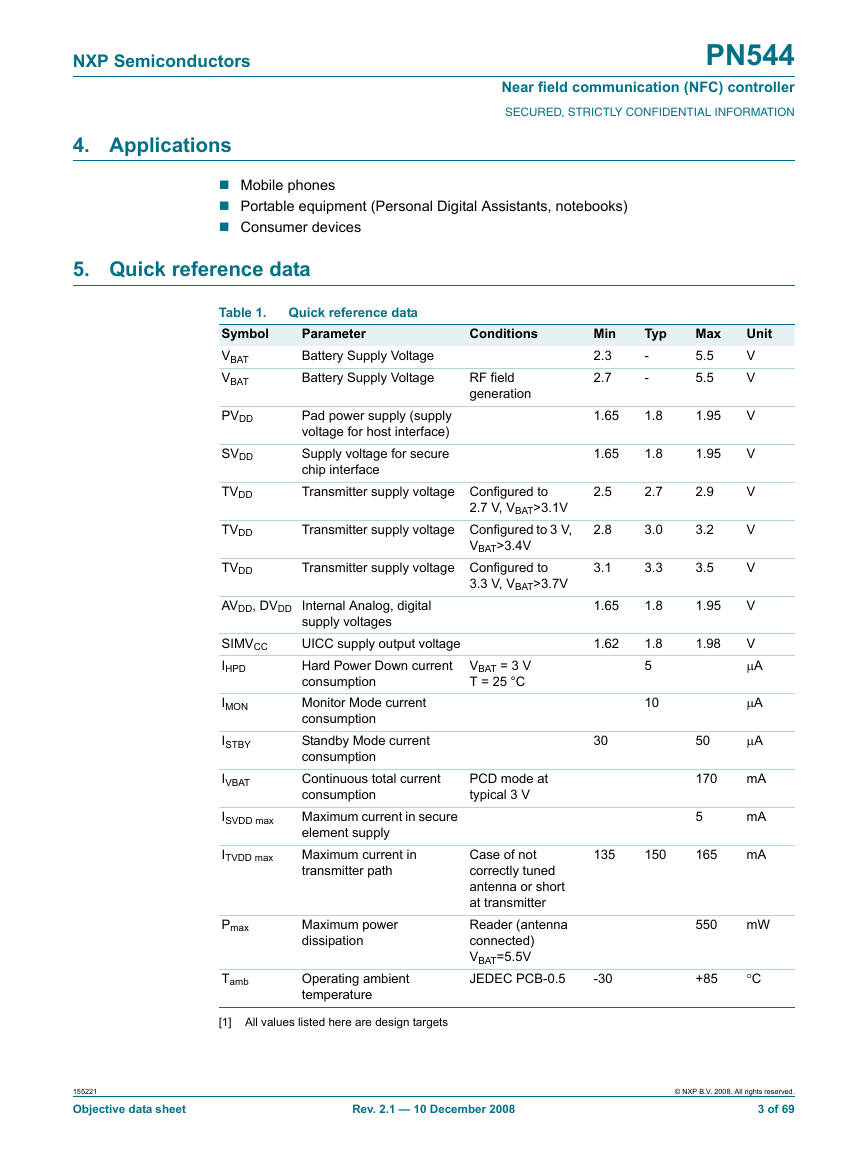

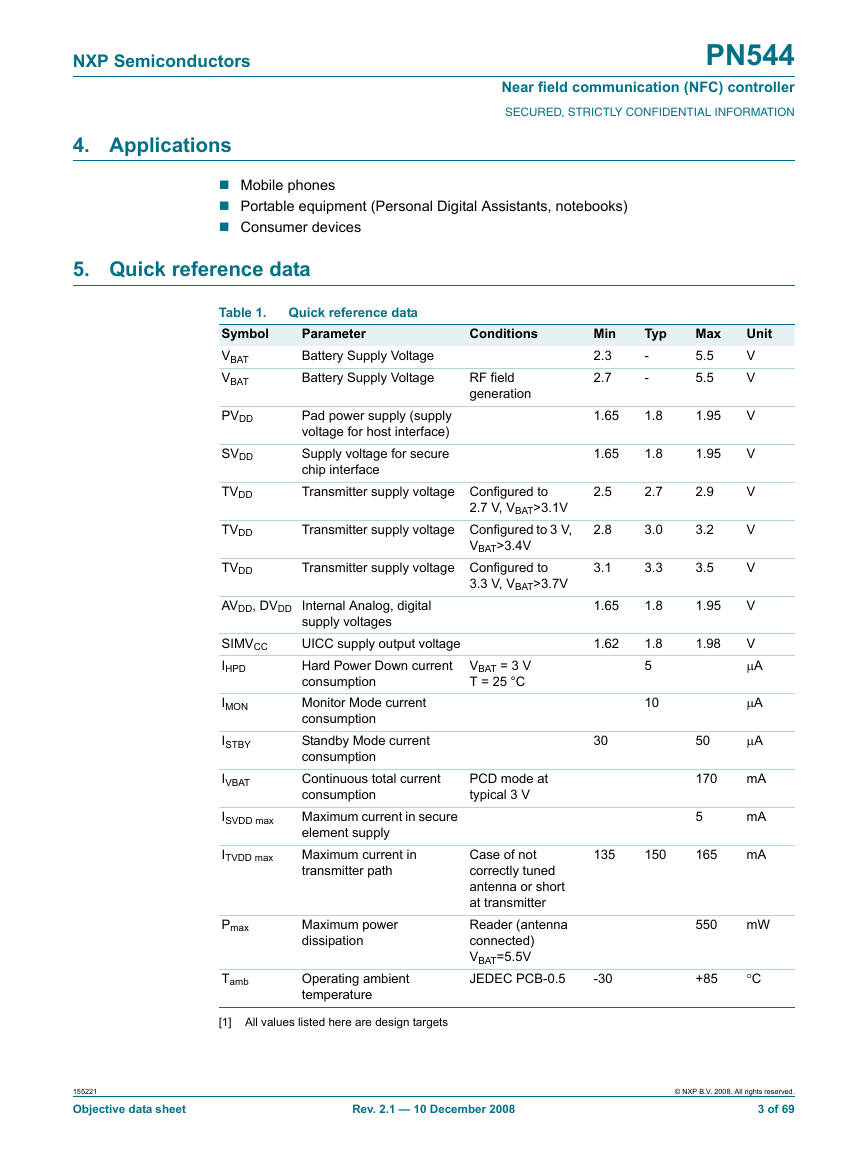

5. Quick reference data

6. Ordering information

7. Marking

8. Block diagram

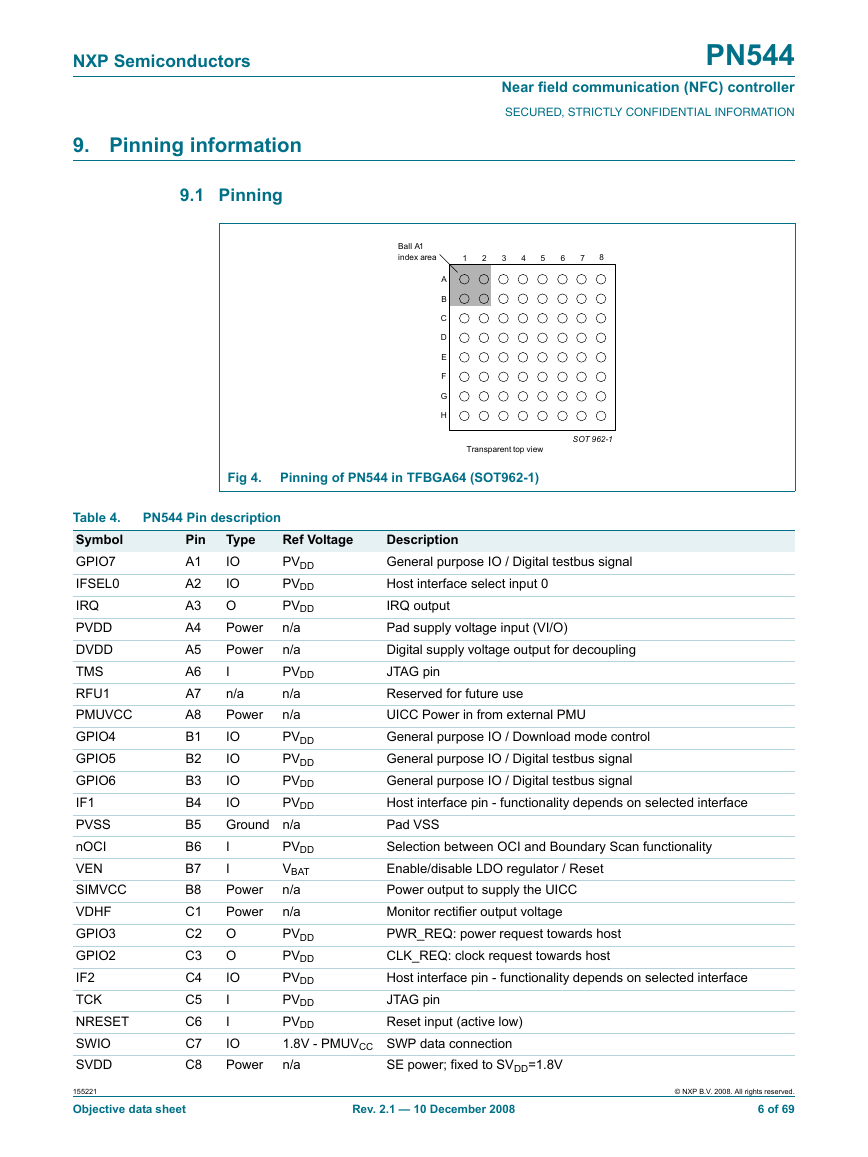

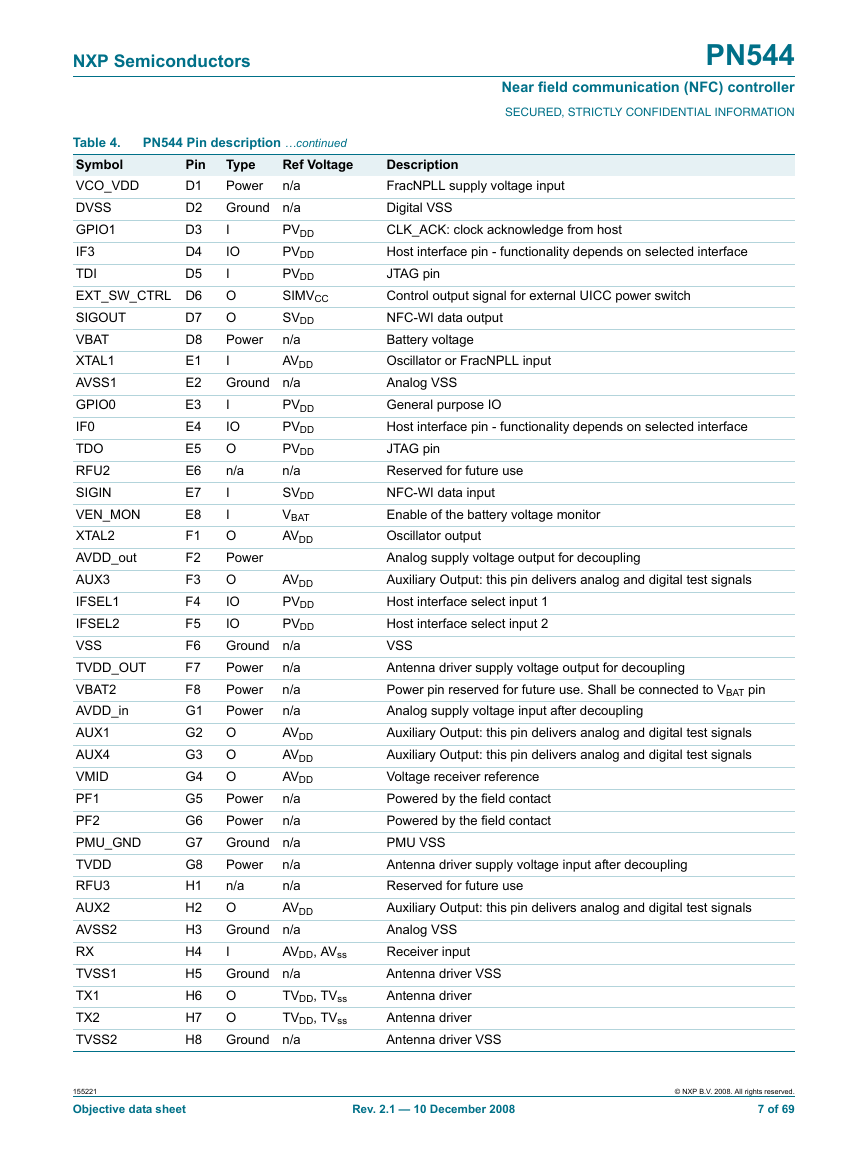

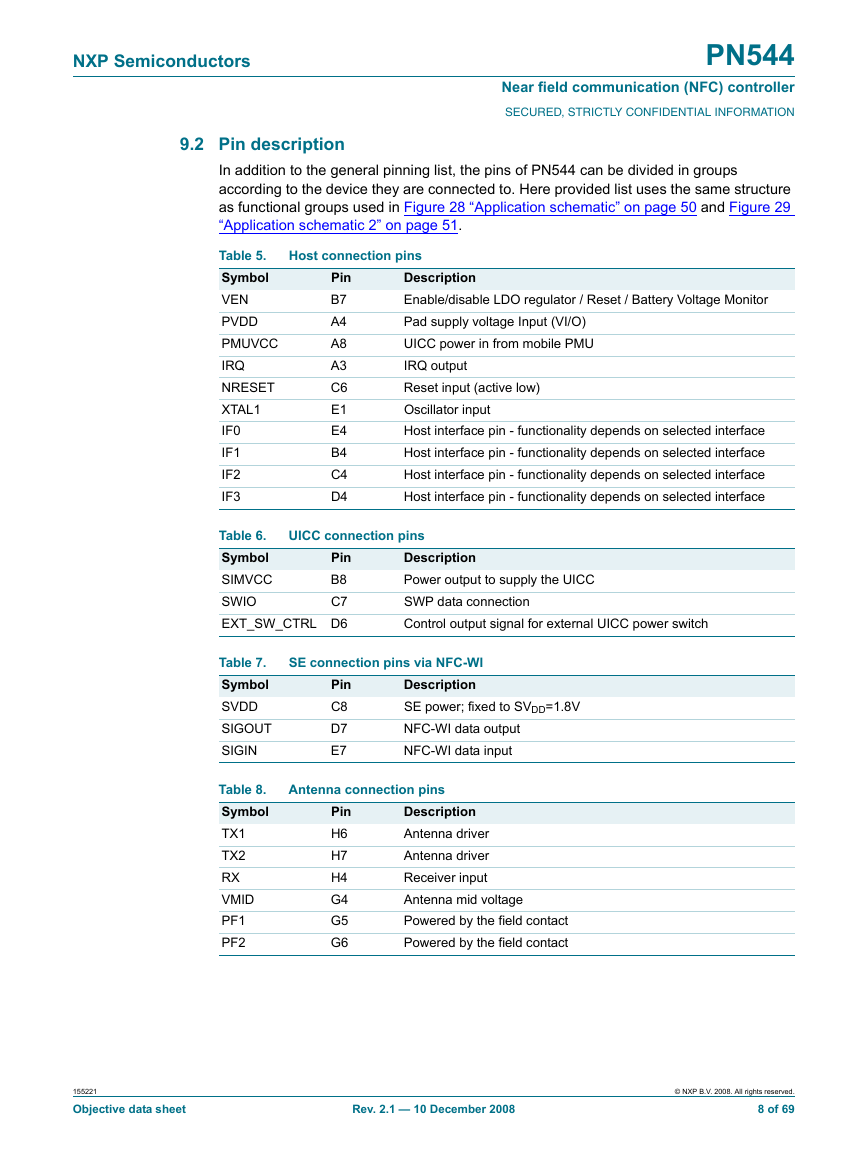

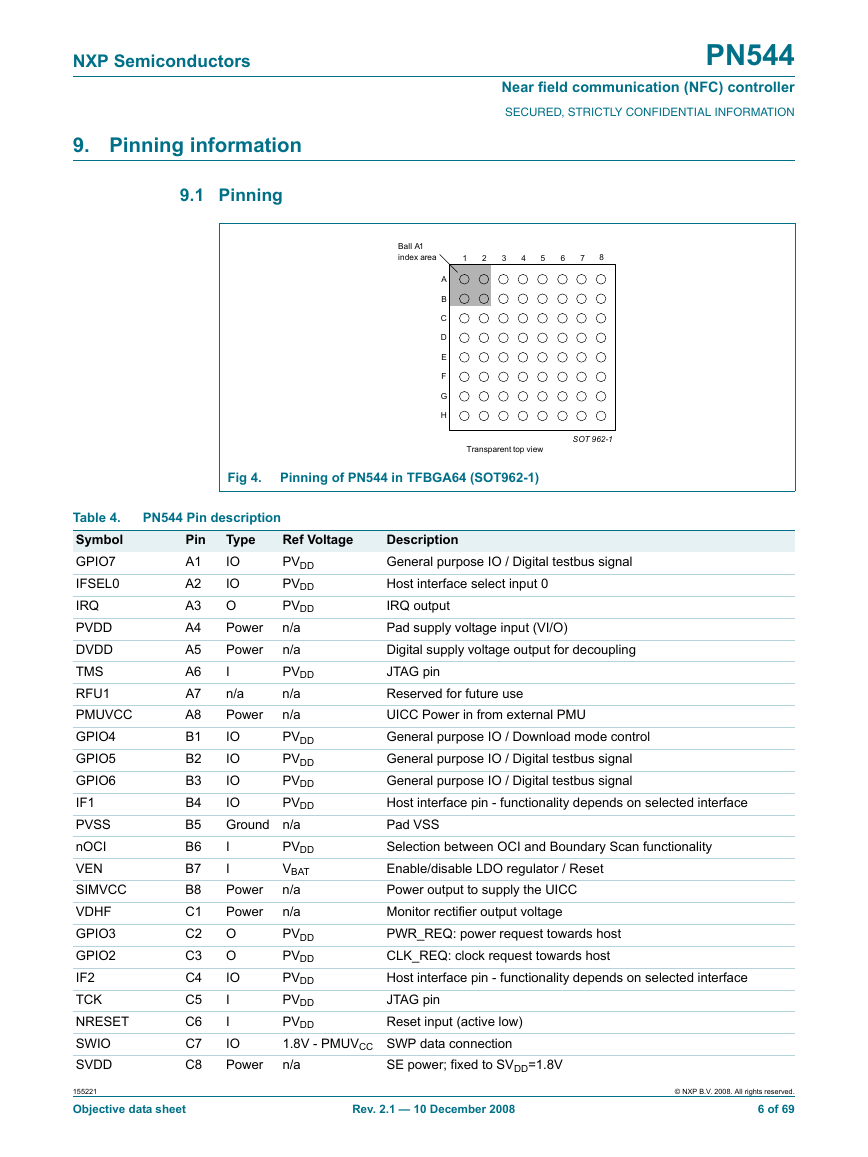

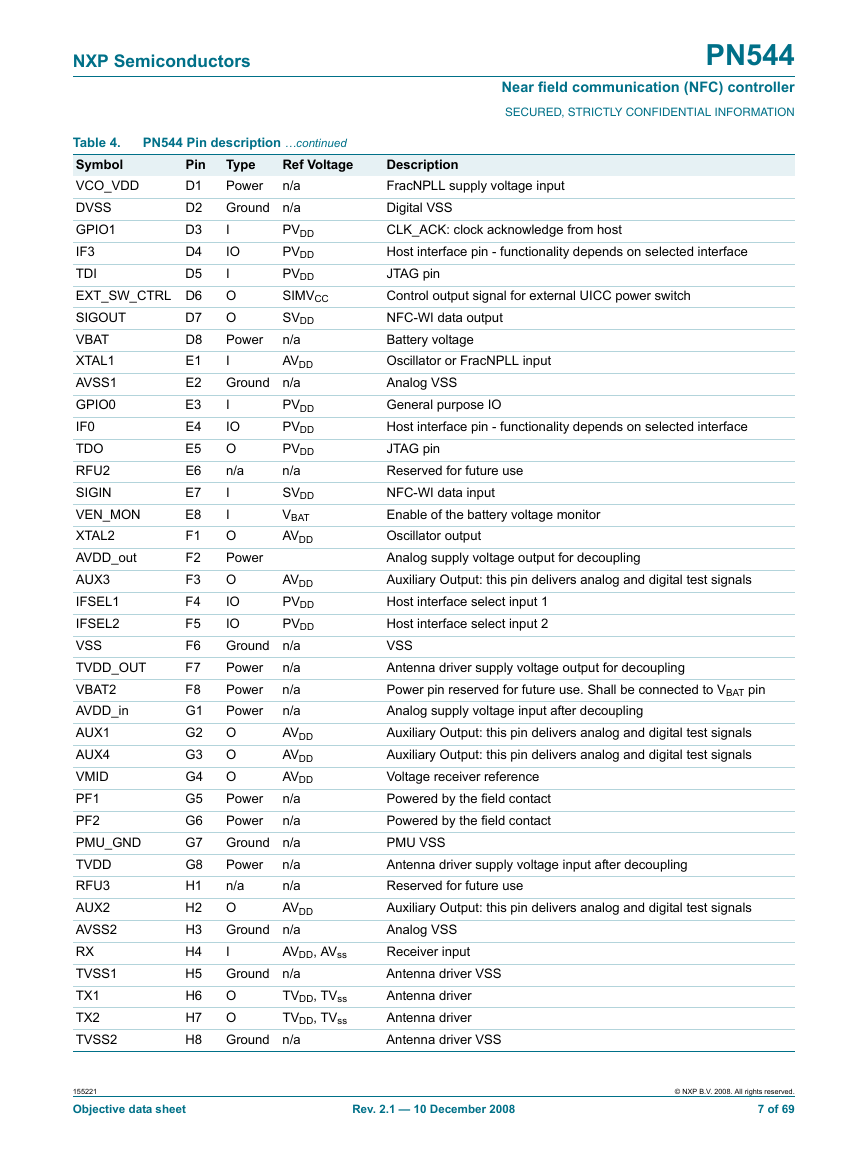

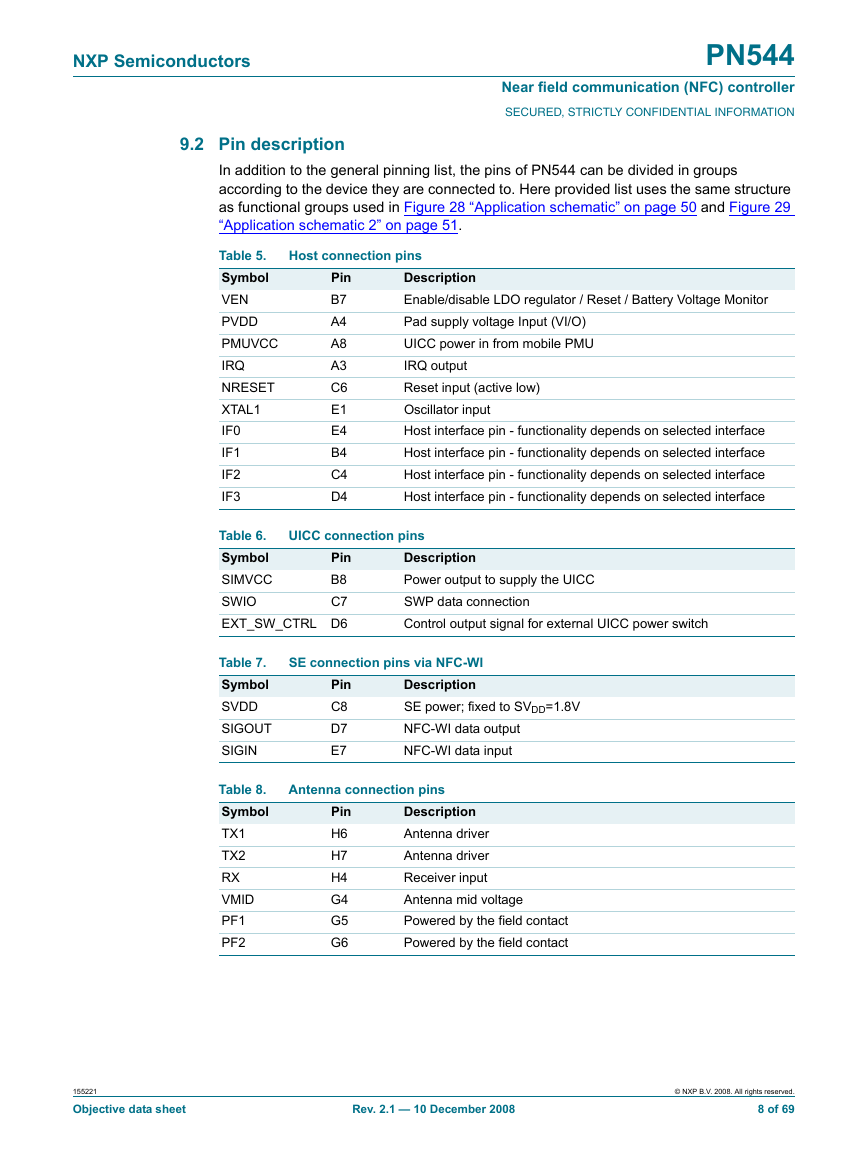

9. Pinning information

9.1 Pinning

9.2 Pin description

10. Functional description

10.1 Functional / Power states of PN544

10.1.1 Standby mode

10.1.2 Active R/W mode

10.1.3 Active battery mode

10.1.4 Polling loop

10.1.5 Hard power down (HPD) mode

10.1.6 Monitor mode

10.1.7 Active antenna mode (Powered-by-field)

10.2 Microcontroller HT80C51MX

10.2.1 PN544 memory management

10.2.2 Timer0/1 description

10.2.3 Interrupts management

10.2.4 FW architecture

10.3 Host interfaces

10.3.1 High Speed UART (HSU) Interface

10.3.1.1 HSU configuration options

10.3.2 I2C interface

10.3.2.1 I2C configuration options

10.3.2.2 I2C functional description

10.3.3 Serial Peripheral Interface

10.3.3.1 Features

10.3.3.2 SPI configuration options

10.3.3.3 SPI functional description

10.3.4 IOs configuration

10.3.4.1 Pad configuration description

10.4 Secure element interfaces

10.4.1 SWP interface

10.4.2 NFC-WI interface support

10.5 PN544 clock concept

10.5.1 27.12 MHz crystal oscillator

10.5.2 Integrated FracNpll to make use of cellular clock

10.5.3 Low power 20 MHz oscillator

10.5.4 Low power 333 kHz oscillator

10.6 Supply concept

10.6.1 PN544 supply sources

10.6.2 PMU functional description

10.6.3 Secure element supply

10.6.4 UICC supply

10.6.5 Battery voltage monitor

10.7 Contactless interface Unit

10.7.1 Reader/Writer modes

10.7.1.1 ISO/IEC 14443-A/MIFARE PCD mode

10.7.1.2 FeliCa PCD mode

10.7.1.3 ISO/IEC 14443B PCD mode

10.7.1.4 ISO/IEC 15693 VCD mode

10.7.2 ISO/IEC 18092, ECMA 340 NFCIP-1 operating mode

10.7.2.1 ACTIVE Communication mode

10.7.2.2 PASSIVE Communication mode

10.7.2.3 NFCIP-1 framing and coding

10.7.2.4 NFCIP-1 protocol support

10.7.3 Card Operation mode

10.7.3.1 ISO/IEC 14443-A / MIFARE Card Operation mode

10.7.3.2 ISO/IEC 14443 B and B’ Card Operation mode

11. Application design-in information

12. Limiting values

13. Recommended operating conditions

14. Thermal characteristics

15. Characteristics

15.1 Current consumption characteristics

15.2 Functional block electrical characteristics

15.2.1 Battery voltage monitor characteristics

15.3 Pin characteristics

15.3.1 XTAL pin characteristics (XTAL1, XAL2)

15.3.2 VEN and VEN_MON input pin characteristics

15.3.3 NRESET input pin characteristics

15.3.4 Output pin characteristics for IRQ

15.3.5 Pin characteristics for GPIOs, IF0 and IF1

15.3.6 Pin characteristics for IF2, IF3

15.3.7 SWIO pin characteristics

15.3.8 Output pin characteristics for EXT_SW_CTRL

15.3.9 Input pin characteristics for SIGIN

15.3.10 Output pin characteristics for SIGOUT

15.3.11 Output pin characteristics for AUX1/AUX2/AUX3/AUX4

15.3.12 Input pin characteristics for RX

15.3.13 Output pin characteristics for TX1/TX2

16. Package outline

17. Abbreviations

18. References

19. Revision history

20. Legal information

20.1 Data sheet status

20.2 Definitions

20.3 Disclaimers

20.4 Licenses

20.5 Trademarks

21. Contact information

22. Tables

23. Figures

24. Contents

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc