VGA 接口控制设计

何习华 2008136206

一、设计目的

1、 掌握时序电路设计及 VGA 接口时序

2、 了解 VGA 显示原理

3、 了解有限状态机设计

二、设计原理

2.1 VGA 时序原理

常见的 VGA 显示器主要是 CRT (阴极射线管)显示器,彩色是由 R、G、B(红、绿、

蓝)三基色组成。CRT 用逐行扫描或隔行扫描的方式实现图像显示,由 VGA 控制模块产生

的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏

上,产生 R、G、B 三基色,合成一个彩色像素。扫描从屏幕的左上方开始,由左至右,由

上到下,逐行进行扫描,每扫完一行,电子束回到屏幕下一行的起始位置,在回扫期间,CRT

对电子束进行消隐,每行结束时用行同步信号 HS 进行行同步;扫描完所有行,再由场同步

信号 VS 进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

行同步信号 HS 和场同步信号 VS 是两个重要的信号。对于 VGA 显示器的这五种信号的时

序驱动要严格遵循“VGA 工业标准”,本设计中采用 VGA 显示模式为:640×480×60Hz,该

模式下像素频率为 25MHz(实际为 25.125MHz)。

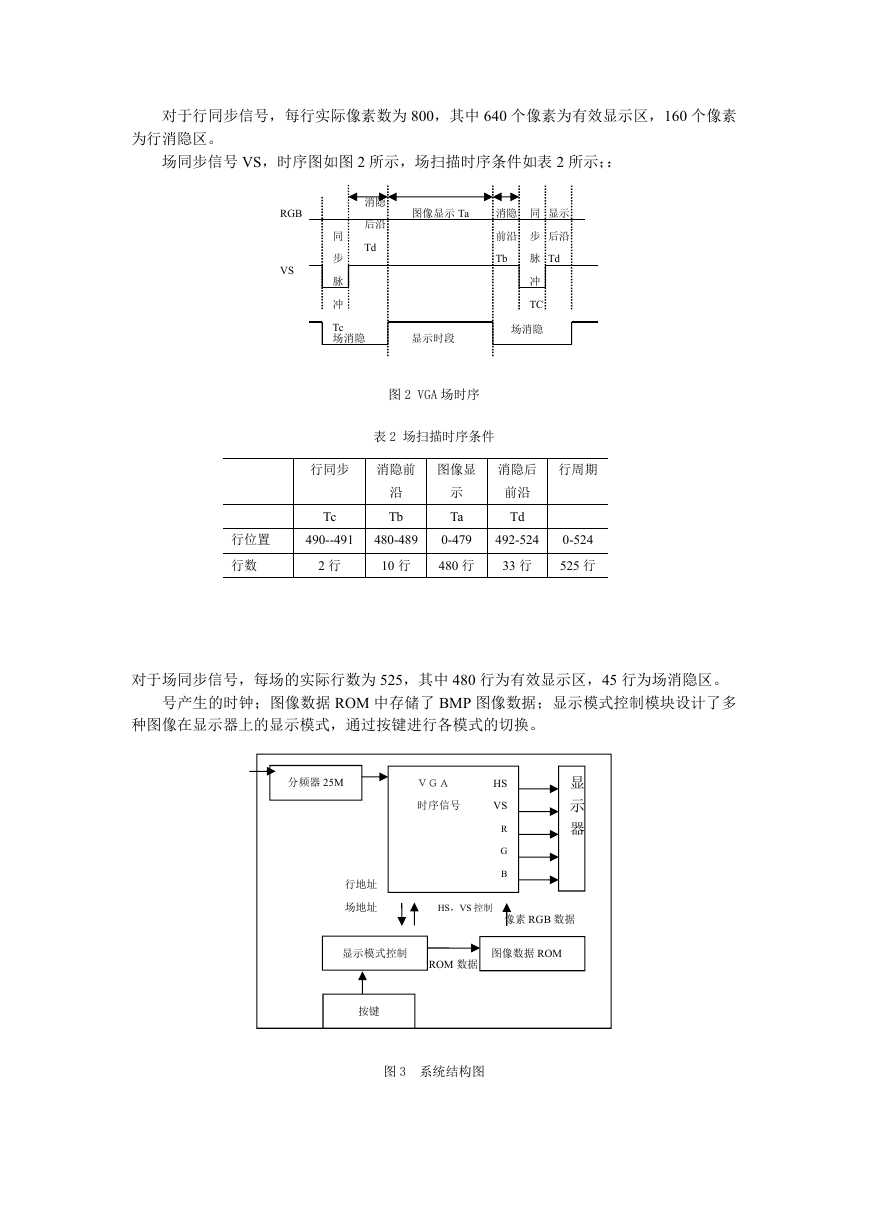

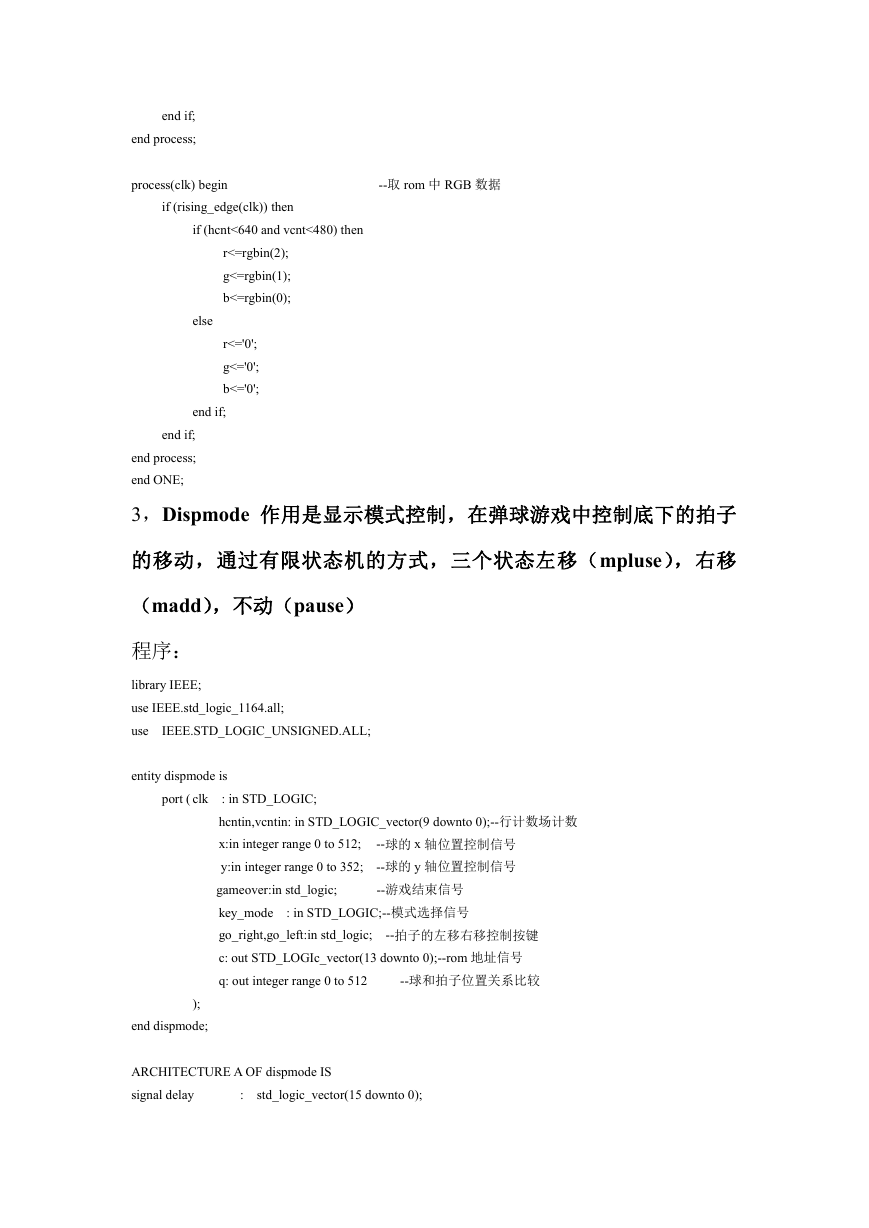

行同步信号 HS,时序图如图 1 所示,行扫描时序条件如表 1 所示;

图像显示 Ta

消隐

消隐

前沿

同

后沿

Td

Tb

步

脉

冲

Tc

行消隐

RGB

HS

消隐

后沿

Td

同

步

脉

冲

Tc

行消隐

显示时段

图 1 VGA 行时序

表 1 行扫描时序条件

行同步

消隐前沿

图像显示

消隐后沿

行周期

Tc

Tb

像素位置 656-751

640-655

像素个数 96 个

16 个

Ta

0-639

640 个

Td

751-799

48 个

0-799

800 个

�

对于行同步信号,每行实际像素数为 800,其中 640 个像素为有效显示区,160 个像素

为行消隐区。

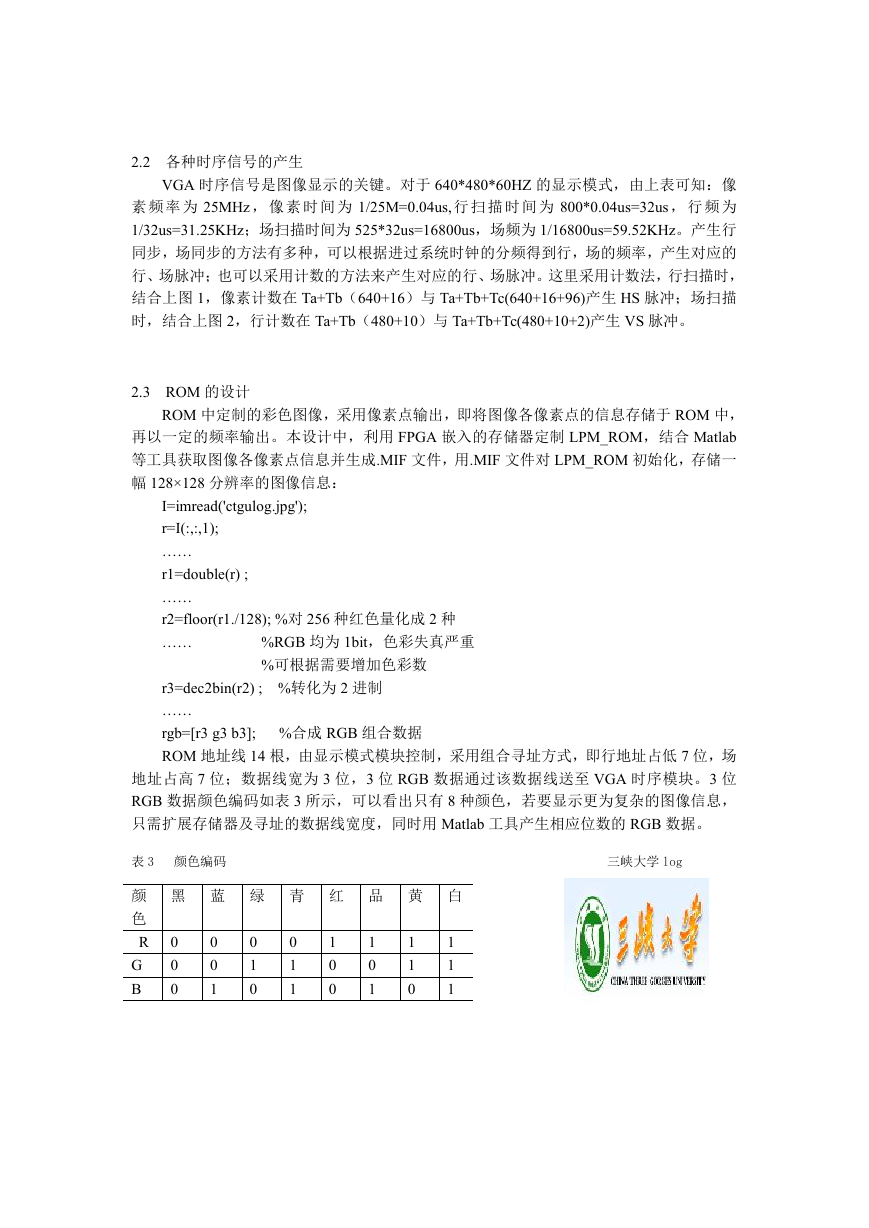

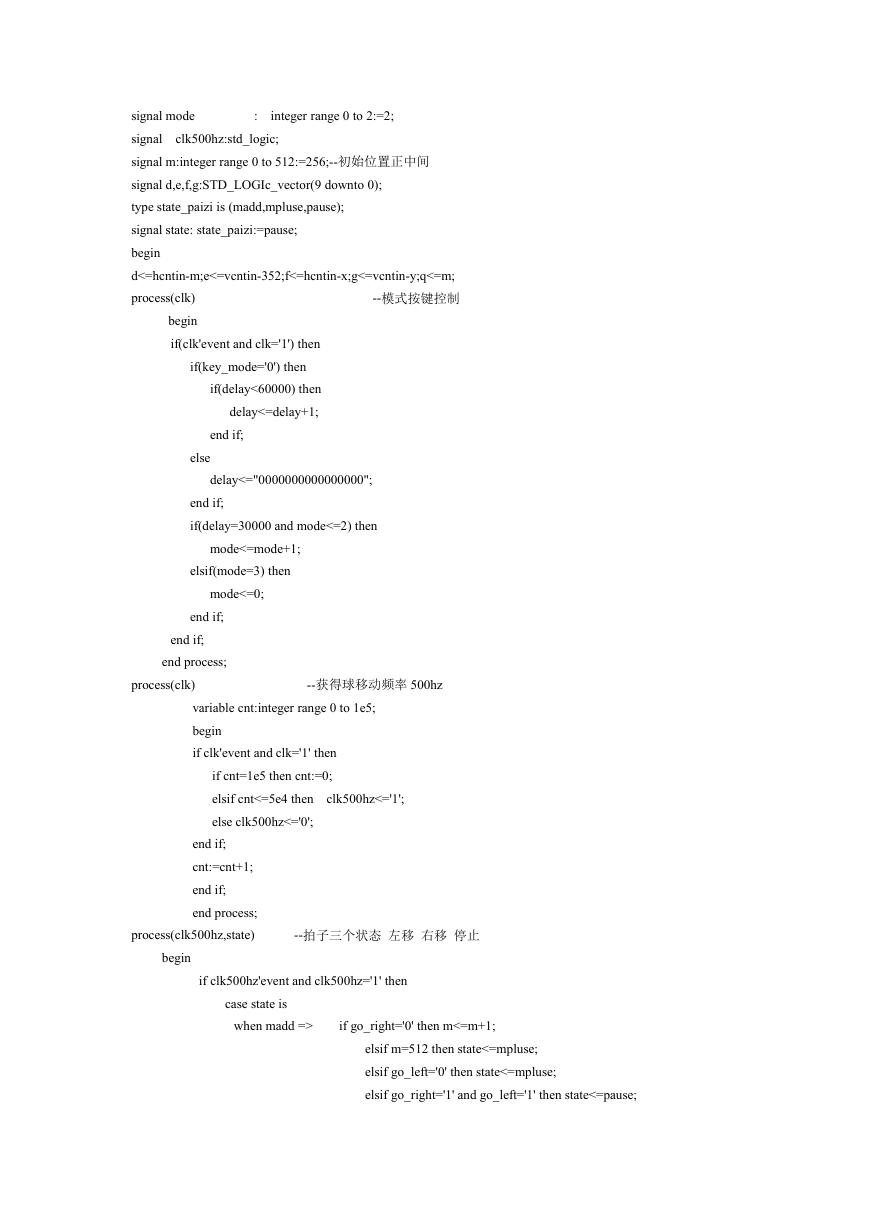

场同步信号 VS,时序图如图 2 所示,场扫描时序条件如表 2 所示;:

RGB

VS

消隐

后沿

Td

同

步

脉

冲

图像显示 Ta

消隐

同

显示

前沿

步

后沿

Tb

Td

脉

冲

TC

Tc

场消隐

显示时段

场消隐

图 2 VGA 场时序

表 2 场扫描时序条件

行同步

消隐前

图像显

消隐后

行周期

Tc

沿

Tb

行位置

行数

490--491

2 行

480-489

10 行

示

Ta

0-479

480 行

前沿

Td

492-524

33 行

0-524

525 行

对于场同步信号,每场的实际行数为 525,其中 480 行为有效显示区,45 行为场消隐区。

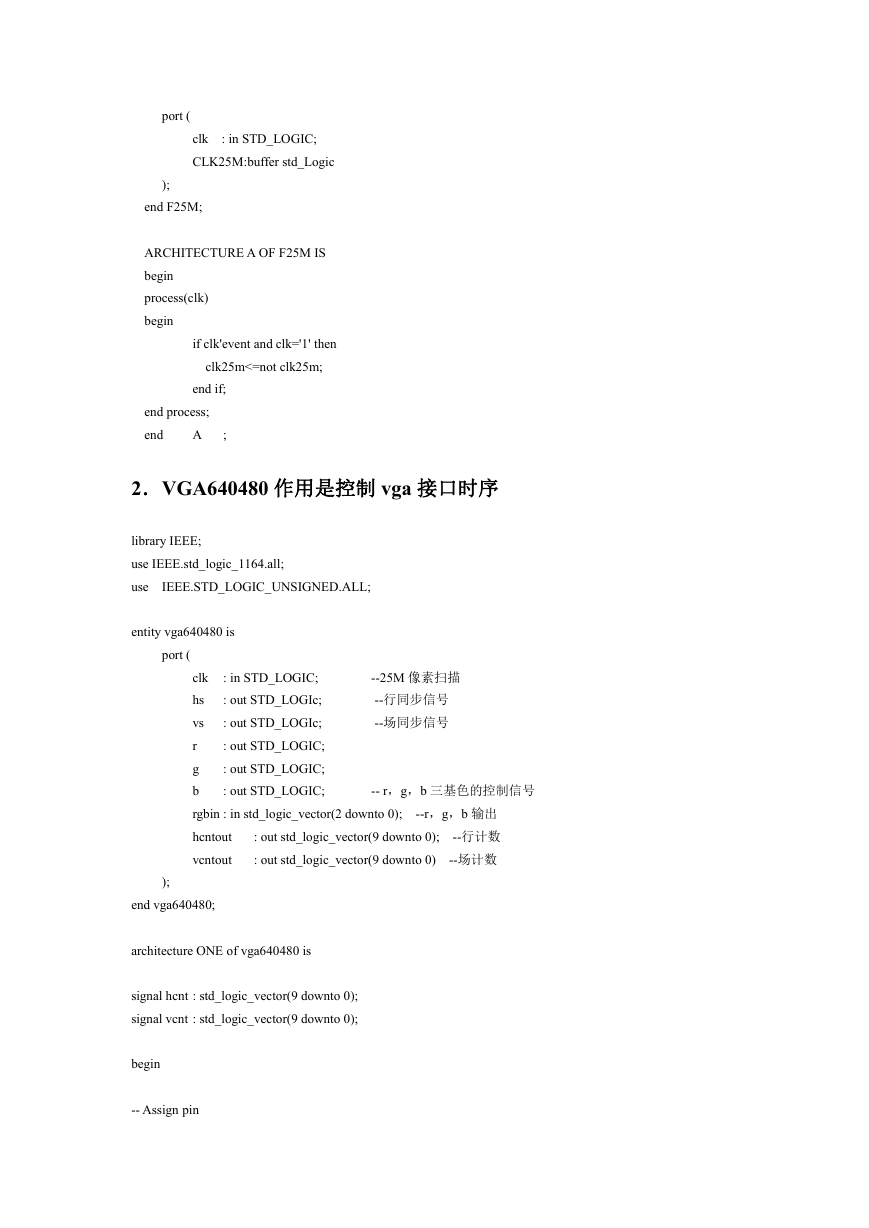

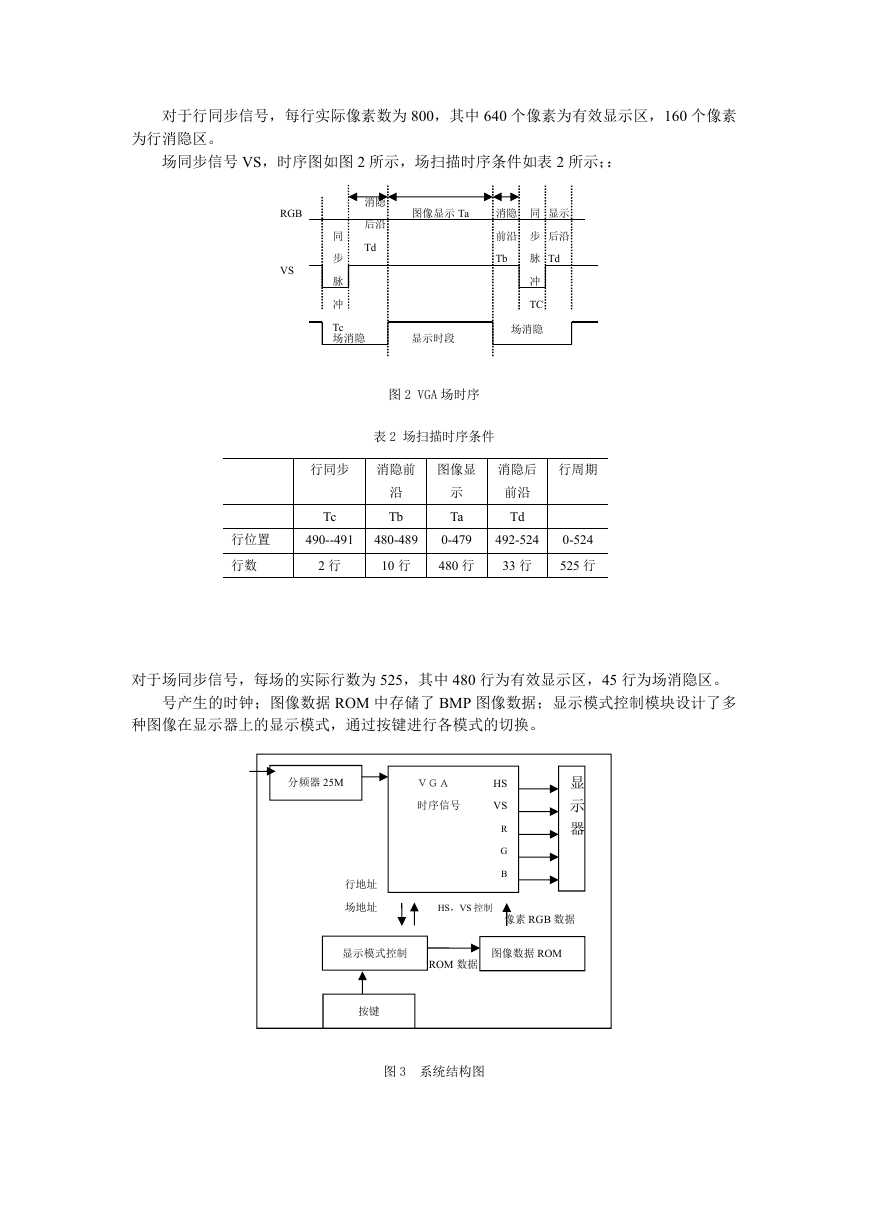

号产生的时钟;图像数据 ROM 中存储了 BMP 图像数据;显示模式控制模块设计了多

种图像在显示器上的显示模式,通过按键进行各模式的切换。

分频器 25M

VGA

时序信号

显

示

器

HS

VS

R

G

B

行地址

场地址

HS,VS 控制

像素 RGB 数据

显示模式控制

图像数据 ROM

ROM 数据

地址

按键

图 3 系统结构图

�

2.2 各种时序信号的产生

VGA 时序信号是图像显示的关键。对于 640*480*60HZ 的显示模式,由上表可知:像

素 频 率 为 25MHz , 像 素 时 间 为 1/25M=0.04us, 行 扫 描 时 间 为 800*0.04us=32us , 行 频 为

1/32us=31.25KHz;场扫描时间为 525*32us=16800us,场频为 1/16800us=59.52KHz。产生行

同步,场同步的方法有多种,可以根据进过系统时钟的分频得到行,场的频率,产生对应的

行、场脉冲;也可以采用计数的方法来产生对应的行、场脉冲。这里采用计数法,行扫描时,

结合上图 1,像素计数在 Ta+Tb(640+16)与 Ta+Tb+Tc(640+16+96)产生 HS 脉冲;场扫描

时,结合上图 2,行计数在 Ta+Tb(480+10)与 Ta+Tb+Tc(480+10+2)产生 VS 脉冲。

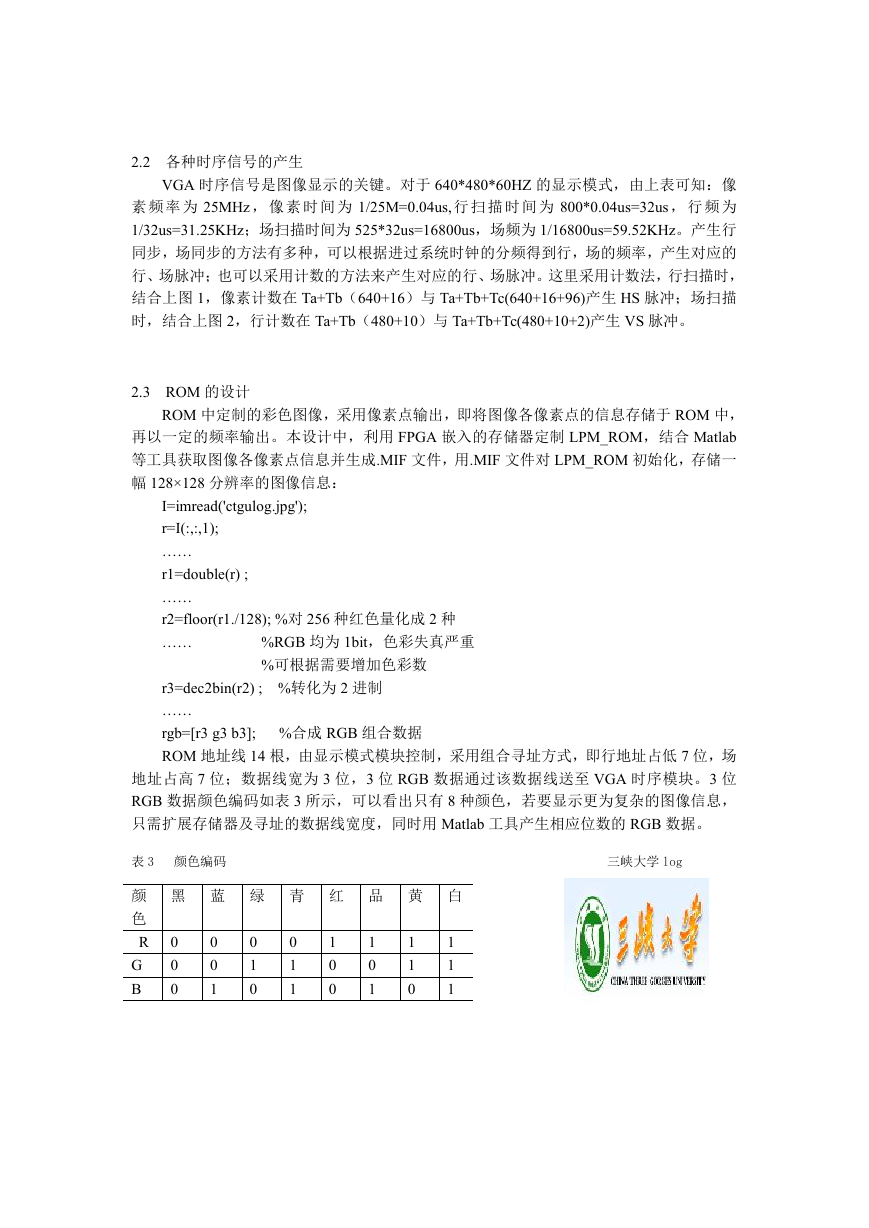

2.3 ROM 的设计

ROM 中定制的彩色图像,采用像素点输出,即将图像各像素点的信息存储于 ROM 中,

再以一定的频率输出。本设计中,利用 FPGA 嵌入的存储器定制 LPM_ROM,结合 Matlab

等工具获取图像各像素点信息并生成.MIF 文件,用.MIF 文件对 LPM_ROM 初始化,存储一

幅 128×128 分辨率的图像信息:

I=imread('ctgulog.jpg');

r=I(:,:,1);

……

r1=double(r) ;

……

r2=floor(r1./128); %对 256 种红色量化成 2 种

……

%RGB 均为 1bit,色彩失真严重

%可根据需要增加色彩数

r3=dec2bin(r2) ; %转化为 2 进制

……

rgb=[r3 g3 b3]; %合成 RGB 组合数据

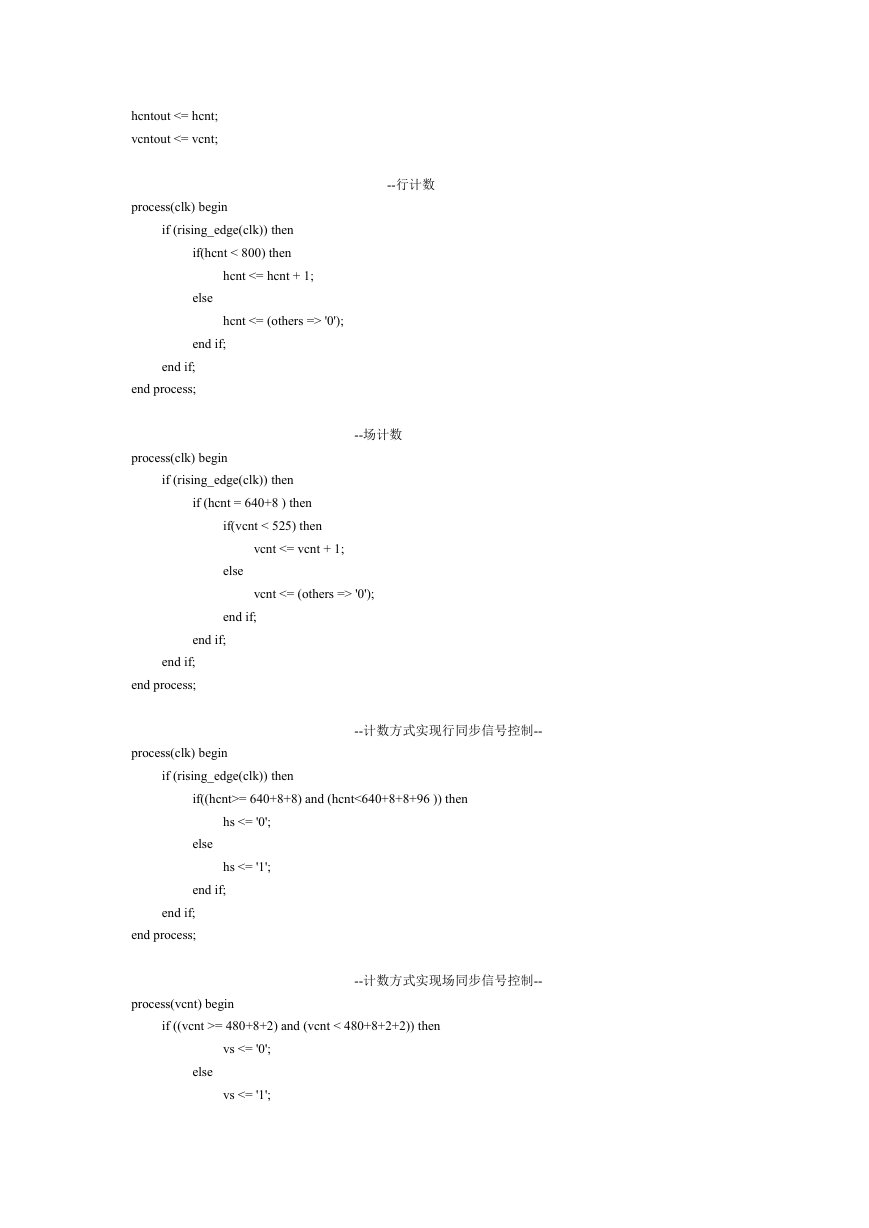

ROM 地址线 14 根,由显示模式模块控制,采用组合寻址方式,即行地址占低 7 位,场

地址占高 7 位;数据线宽为 3 位,3 位 RGB 数据通过该数据线送至 VGA 时序模块。3 位

RGB 数据颜色编码如表 3 所示,可以看出只有 8 种颜色,若要显示更为复杂的图像信息,

只需扩展存储器及寻址的数据线宽度,同时用 Matlab 工具产生相应位数的 RGB 数据。

表 3 颜色编码

三峡大学 log

颜

色

R

G

B

黑 蓝 绿 青 红 品 黄 白

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

�

三、设计内容及电路图

总原理图如下

菱角分配如下

5 个模块 F25M, VGA640480, Dispmode ,XY, C rom

程序清单如下:

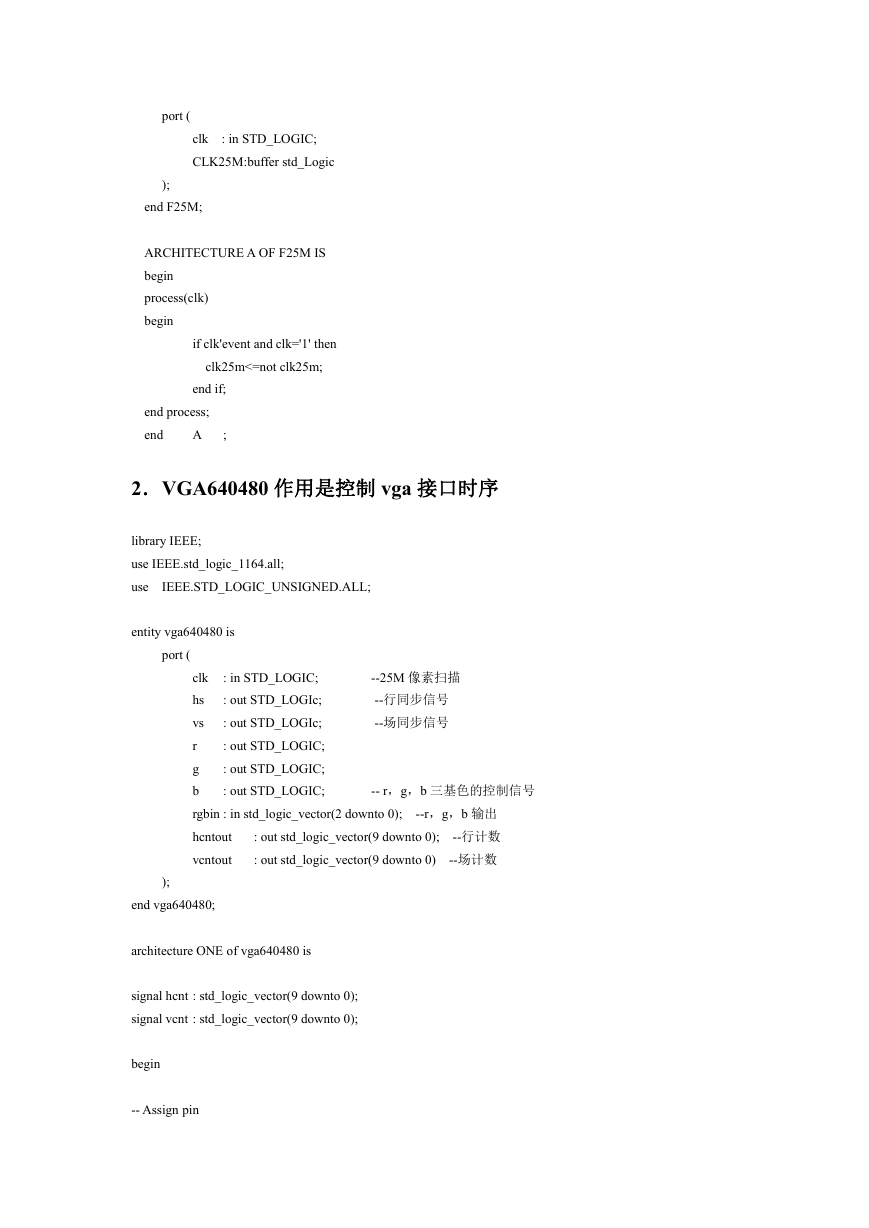

1,F25M 作用是得到 25M 的像素扫描频率;

library IEEE;

use IEEE.std_logic_1164.all;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entity F25M is

�

port (

clk : in STD_LOGIC;

CLK25M:buffer std_Logic

);

end F25M;

ARCHITECTURE A OF F25M IS

begin

process(clk)

begin

if clk'event and clk='1' then

clk25m<=not clk25m;

end if;

end process;

A

end

;

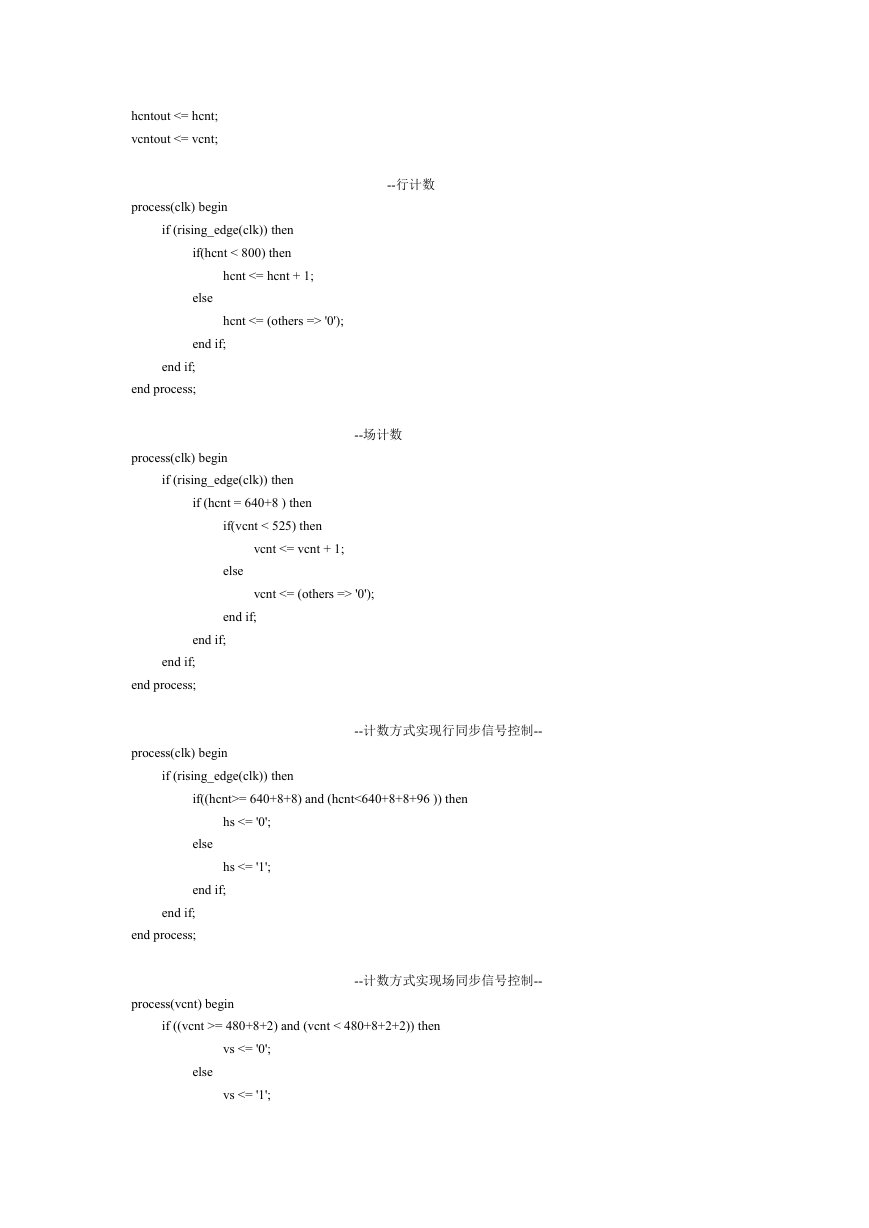

2.VGA640480 作用是控制 vga 接口时序

library IEEE;

use IEEE.std_logic_1164.all;

use

IEEE.STD_LOGIC_UNSIGNED.ALL;

entity vga640480 is

port (

--25M 像素扫描

--行同步信号

--场同步信号

: in STD_LOGIC;

: out STD_LOGIc;

: out STD_LOGIc;

: out STD_LOGIC;

: out STD_LOGIC;

: out STD_LOGIC;

clk

hs

vs

r

g

b

rgbin : in std_logic_vector(2 downto 0);

hcntout

vcntout

-- r,g,b 三基色的控制信号

: out std_logic_vector(9 downto 0);

: out std_logic_vector(9 downto 0)

--r,g,b 输出

--行计数

--场计数

);

end vga640480;

architecture ONE of vga640480 is

signal hcnt : std_logic_vector(9 downto 0);

signal vcnt : std_logic_vector(9 downto 0);

begin

-- Assign pin

�

--行计数

hcntout <= hcnt;

vcntout <= vcnt;

process(clk) begin

if (rising_edge(clk)) then

if(hcnt < 800) then

hcnt <= hcnt + 1;

else

hcnt <= (others => '0');

end if;

end if;

end process;

process(clk) begin

if (rising_edge(clk)) then

--场计数

if (hcnt = 640+8 ) then

if(vcnt < 525) then

vcnt <= vcnt + 1;

else

vcnt <= (others => '0');

end if;

end if;

end if;

end process;

--计数方式实现行同步信号控制--

process(clk) begin

if (rising_edge(clk)) then

if((hcnt>= 640+8+8) and (hcnt<640+8+8+96 )) then

else

hs <= '0';

hs <= '1';

end if;

end if;

end process;

process(vcnt) begin

if ((vcnt >= 480+8+2) and (vcnt < 480+8+2+2)) then

--计数方式实现场同步信号控制--

else

vs <= '0';

vs <= '1';

�

end if;

end process;

process(clk) begin

if (rising_edge(clk)) then

if (hcnt<640 and vcnt<480) then

--取 rom 中 RGB 数据

r<=rgbin(2);

g<=rgbin(1);

b<=rgbin(0);

else

r<='0';

g<='0';

b<='0';

end if;

end if;

end process;

end ONE;

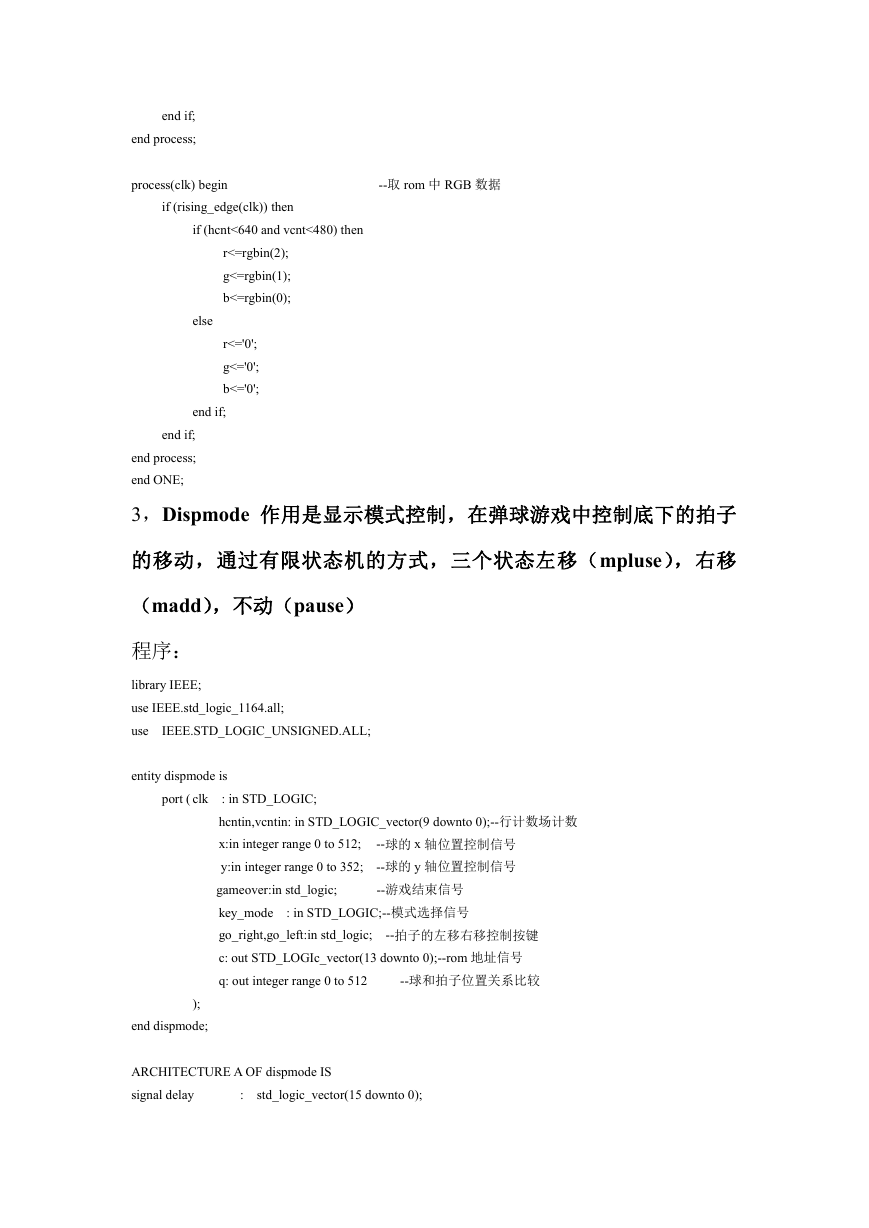

3,Dispmode 作用是显示模式控制,在弹球游戏中控制底下的拍子

的移动,通过有限状态机的方式,三个状态左移(mpluse),右移

(madd),不动(pause)

程序:

library IEEE;

use IEEE.std_logic_1164.all;

use

IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dispmode is

port ( clk : in STD_LOGIC;

--球的 x 轴位置控制信号

--球的 y 轴位置控制信号

--游戏结束信号

: in STD_LOGIC;--模式选择信号

hcntin,vcntin: in STD_LOGIC_vector(9 downto 0);--行计数场计数

x:in integer range 0 to 512;

y:in integer range 0 to 352;

gameover:in std_logic;

key_mode

go_right,go_left:in std_logic;

c: out STD_LOGIc_vector(13 downto 0);--rom 地址信号

q: out integer range 0 to 512

--拍子的左移右移控制按键

--球和拍子位置关系比较

);

end dispmode;

ARCHITECTURE A OF dispmode IS

signal delay

:

std_logic_vector(15 downto 0);

�

:

clk500hz:std_logic;

integer range 0 to 2:=2;

signal mode

signal

signal m:integer range 0 to 512:=256;--初始位置正中间

signal d,e,f,g:STD_LOGIc_vector(9 downto 0);

type state_paizi is (madd,mpluse,pause);

signal state: state_paizi:=pause;

begin

d<=hcntin-m;e<=vcntin-352;f<=hcntin-x;g<=vcntin-y;q<=m;

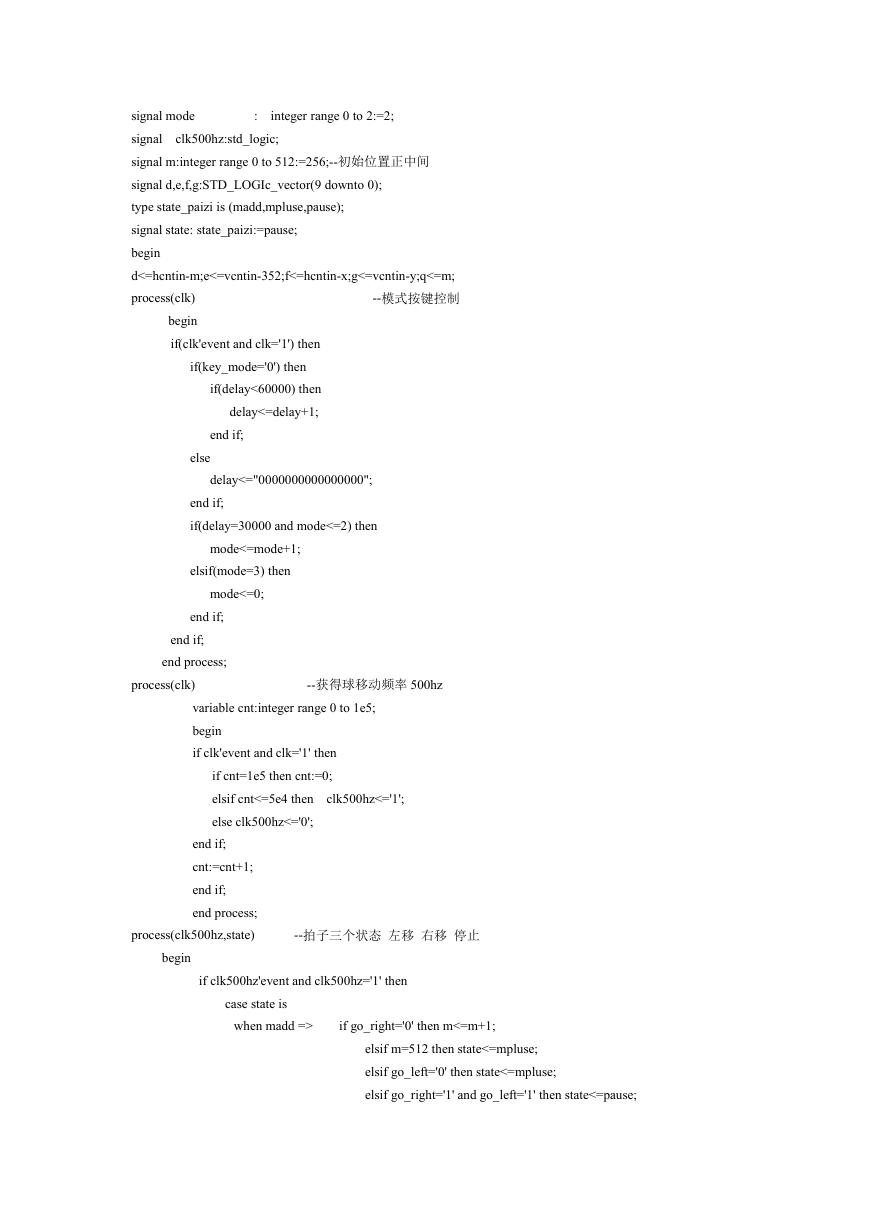

process(clk)

--模式按键控制

begin

if(clk'event and clk='1') then

if(key_mode='0') then

if(delay<60000) then

delay<=delay+1;

end if;

else

delay<="0000000000000000";

end if;

if(delay=30000 and mode<=2) then

mode<=mode+1;

elsif(mode=3) then

mode<=0;

end if;

end if;

end process;

process(clk)

--获得球移动频率 500hz

variable cnt:integer range 0 to 1e5;

begin

if clk'event and clk='1' then

if cnt=1e5 then cnt:=0;

elsif cnt<=5e4 then clk500hz<='1';

else clk500hz<='0';

end if;

cnt:=cnt+1;

end if;

end process;

process(clk500hz,state)

begin

--拍子三个状态 左移 右移 停止

if clk500hz'event and clk500hz='1' then

case state is

when madd =>

if go_right='0' then m<=m+1;

elsif m=512 then state<=mpluse;

elsif go_left='0' then state<=mpluse;

elsif go_right='1' and go_left='1' then state<=pause;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc