Lontium Semiconductor

LT8918_Datasheet_R1.3

LONTIUM SEMICONDUCTOR CORPORATION

ClearedEdge Technology

LT8918

MIPI DSI/CSI-2 Transmitter

Datasheet

We produce mixed-signal products for a better digital world!

Confidential

1

�

Lontium Semiconductor

LT8918_Datashet_R1.3

TABLE OF CONTENTS

1. REVISION HISTORY ............................................................................................................. 3

2. GENERAL DESCRIPTION .................................................................................................... 4

2.1 APPLICATION .................................................................................................................................................................... 4

2.2 FEATURES ......................................................................................................................................................................... 5

2.3 FUNCTIONAL DIAGRAM ..................................................................................................................................................... 5

3. PINNING INFORMATION ...................................................................................................... 6

3.1 QFN64 PIN DIAGRAM ...................................................................................................................................................... 6

3.2 QFN64 PIN DEFINITION .................................................................................................................................................... 7

3.3 BGA81 BALL MAP ......................................................................................................................................................... 11

3.4 BGA81 BALL DEFINITION .............................................................................................................................................. 12

4. ELECTRICAL CHARACTERISTICS ................................................................................... 15

4.1 ABSOLUTE MAXIMUM CONDITIONS ................................................................................................................................ 15

4.2 NORMAL OPERATING CONDITIONS ................................................................................................................................ 15

4.3 DC CHARACTERISTICS ................................................................................................................................................... 15

4.4 AC CHARACTERISTICS ................................................................................................................................................... 15

5. PACKAGE INFORMATION ................................................................................................. 17

5.1 QFN64 7.5MM X 7.5MM PACKAGE ................................................................................................................................ 17

5.2 BGA81 5MM X 5MM PACKAGE ...................................................................................................................................... 18

Confidential

2

�

Lontium Semiconductor

1. REVISION HISTORY

LT8918_Datashet_R1.3

Version

R1.0

Owner

C.Tao

R1.1

R1.2

R1.3

C.Tao

C.Tao

N.Wang

Content

Initial Release

1. Update QFN64 7.5mm x 7.5mm EPAD size from 5.6x5.6 to 6.2x6.2

2. Add BGA81 5mm x 5mm ball map, ball definition and package information

3. Remove CSI-2 YUV 422 10bit and RAW8 video format support

4. Add CCI module in block diagram

1. Update pin information

Change package information

Date

2016/06/14

2016/06/15

2016/08/16

2016/8/18

Confidential

3

�

Lontium Semiconductor

LT8918_Datashet_R1.3

2. GENERAL DESCRIPTION

The Lontium LT8918 is a high performance MIPIDSI/CSI-2 transmitter for mobile display panel or camera application.

The TTL input of LT8918 supports both 24-bit RGB and BT656/1120 video format under either SDR or DDR sampling. The

maximum input pixel clock frequency is SDR 148.5MHz or DDR 74.25MHz for 1080P@60Hz high-end mobile display or

video capture application.

For MIPI DSI/CSI-2 output, LT8918 features a single port MIPI DSI or CSI-2 transmitter with 1 high-speed clock lane and

1~4 configurable high-speed data lanes operating at maximum 1.5Gb/s/lane, which can support a total bandwidth of up to

6Gb/s. LT8918 supports both Non-Burst and Burst DSI video data transferring, as well as Command Mode through Lane-0.

The LT8918 is fabricated in advanced CMOS process and implemented in a small outline 7.5mm x 7.5mm QFN64

package. This package is RoHS compliant and specified to operate from -40°C to +85°C.

2.1 Application

Mobile systems

Cellular handsets

Digital video cameras

Digital still cameras

Car Display and Camera System

Tablet PC, Notebook PC

Fig2.1 Typical Application and System Diagrams

Confidential

4

�

Lontium Semiconductor

2.2 Features

RGB Input

Support 24-bit RGB and BT656/BT1120 Input

Support both SDR and DDR Data Sampling

Programmable Rising/Falling Edge Clock Input

Support up to 74.25MHz DDR or 148.5MHz SDR

Clock Input

Support both 1.8V and 3.3V Input Voltage Level

Single-Port MIPI DSI Transmitter

Compliant with DCS1.02, D-PHY1.1 & DSI1.02

1 Clock Lane and 1~4 Configurable Data Lanes

80Mb/s~1.5Gb/s per Data Lane

Resolution Up to 1080P 60Hz

Data Lane and Polarity Swapping

Both Non-Burst and Burst Video Mode Supported

Command Mode through Lane-0 Supported

Support RGB666, Loosely RGB666, RGB888,

RGB565, 16-bit YCbCr4:2:2, 24-bit YCbCr 4:2:2

Video Format

2.3 Functional Diagram

LT8918_Datashet_R1.3

Single-Port MIPI CSI-2 Transmitter

Compliant with D-PHY1.1 & CSI-2 1.0

1 Clock Lane and 1~4 Configurable Data Lanes

80Mb/s~1.5Gb/s per Data Lane

Resolution Up to 1080P 60Hz

Data Lane and Polarity Swapping

Support RGB565, RGB666, RGB888, 8-bit YUV422

Video Format

Miscellaneous

1.8V Single Supply Power

Support 100KHz and 400KHz I2C slave

Support SPI slave

External 25MHz Crystal Reference Clock

Temperature Range: -400C ~ +850C

Packaged in QFN64 7.5mm x 7.5mm and BGA81

5mm x 5mm

Fig2.2 MIPI DSI/CSI-2 Transmitter Functional Diagrams

Confidential

5

�

LT8918_Datashet_R1.3

Lontium Semiconductor

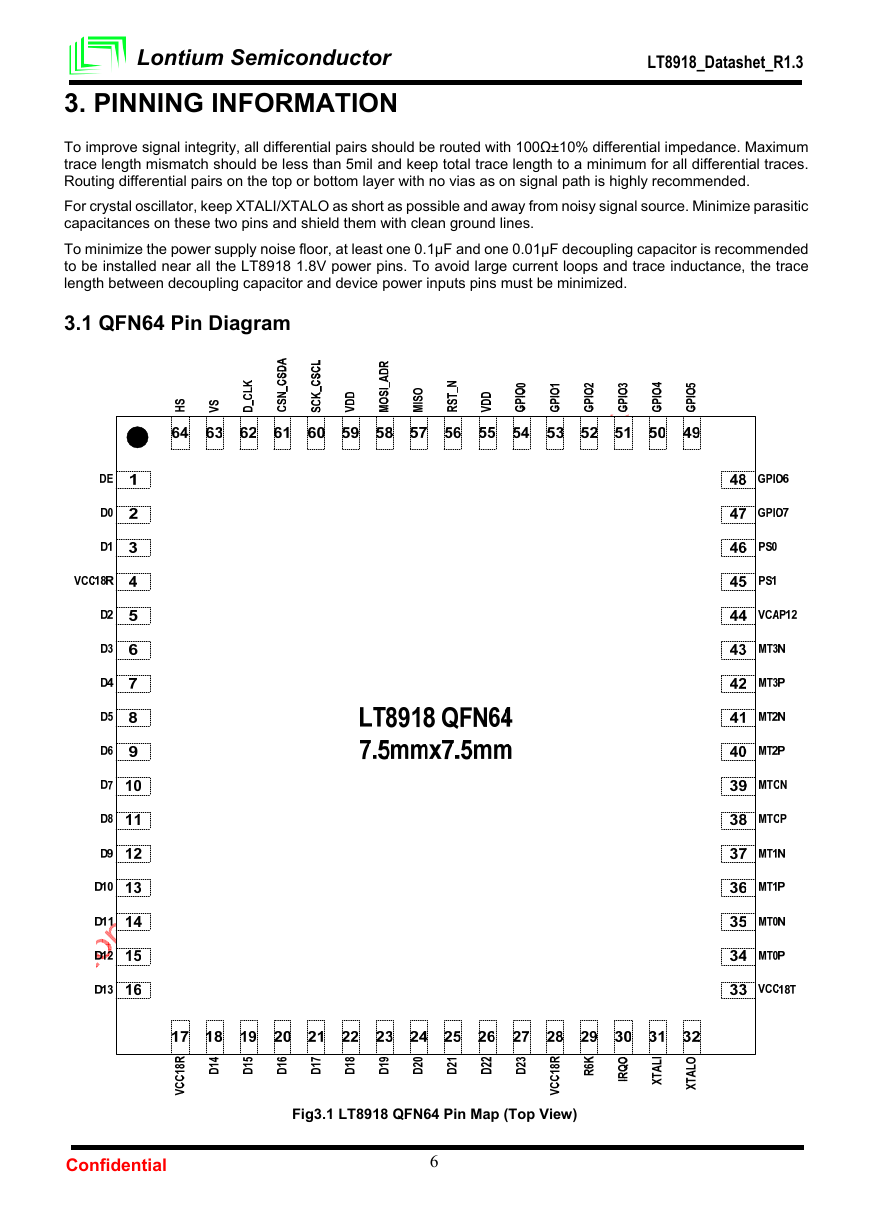

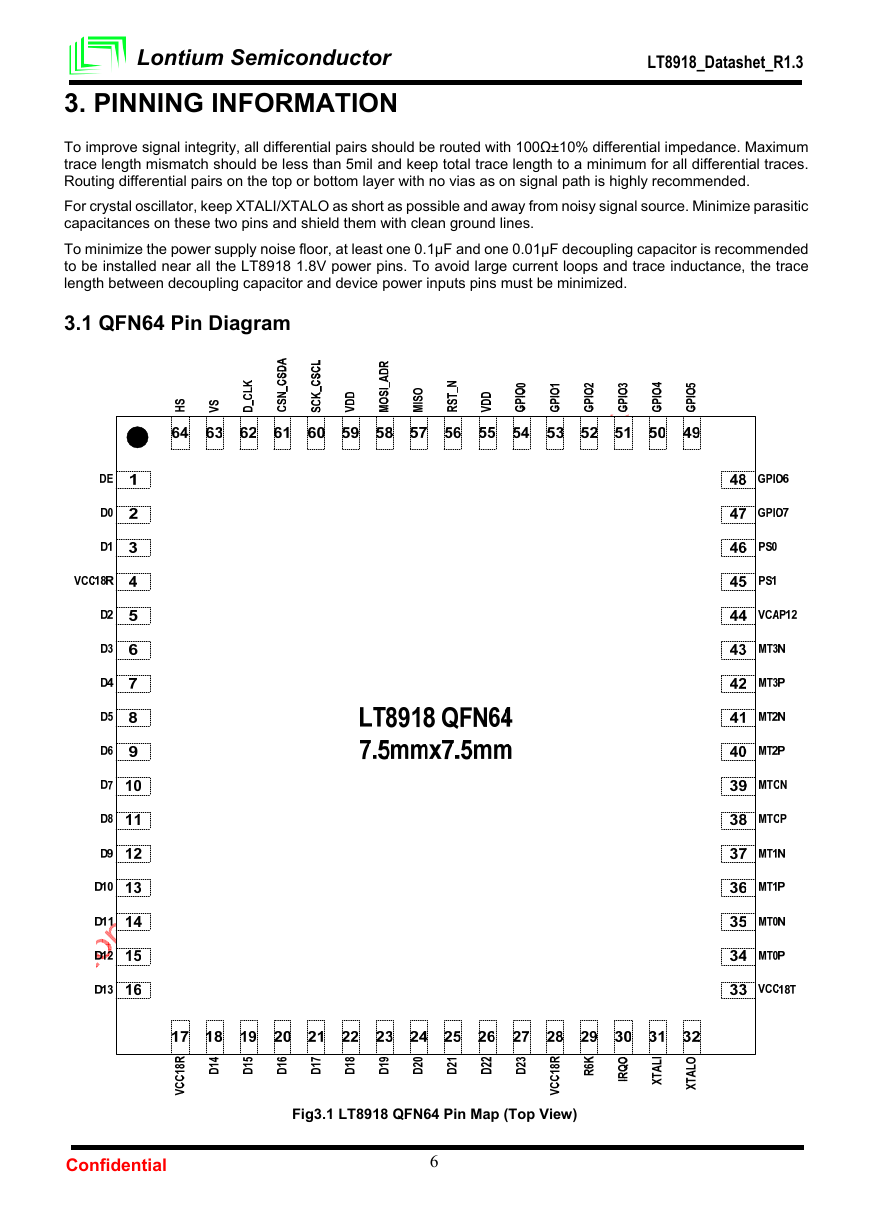

3. PINNING INFORMATION

To improve signal integrity, all differential pairs should be routed with 100Ω±10% differential impedance. Maximum

trace length mismatch should be less than 5mil and keep total trace length to a minimum for all differential traces.

Routing differential pairs on the top or bottom layer with no vias as on signal path is highly recommended.

For crystal oscillator, keep XTALI/XTALO as short as possible and away from noisy signal source. Minimize parasitic

capacitances on these two pins and shield them with clean ground lines.

To minimize the power supply noise floor, at least one 0.1μF and one 0.01μF decoupling capacitor is recommended

to be installed near all the LT8918 1.8V power pins. To avoid large current loops and trace inductance, the trace

length between decoupling capacitor and device power inputs pins must be minimized.

3.1 QFN64 Pin Diagram

Fig3.1 LT8918 QFN64 Pin Map (Top View)

Confidential

6

�

Lontium Semiconductor

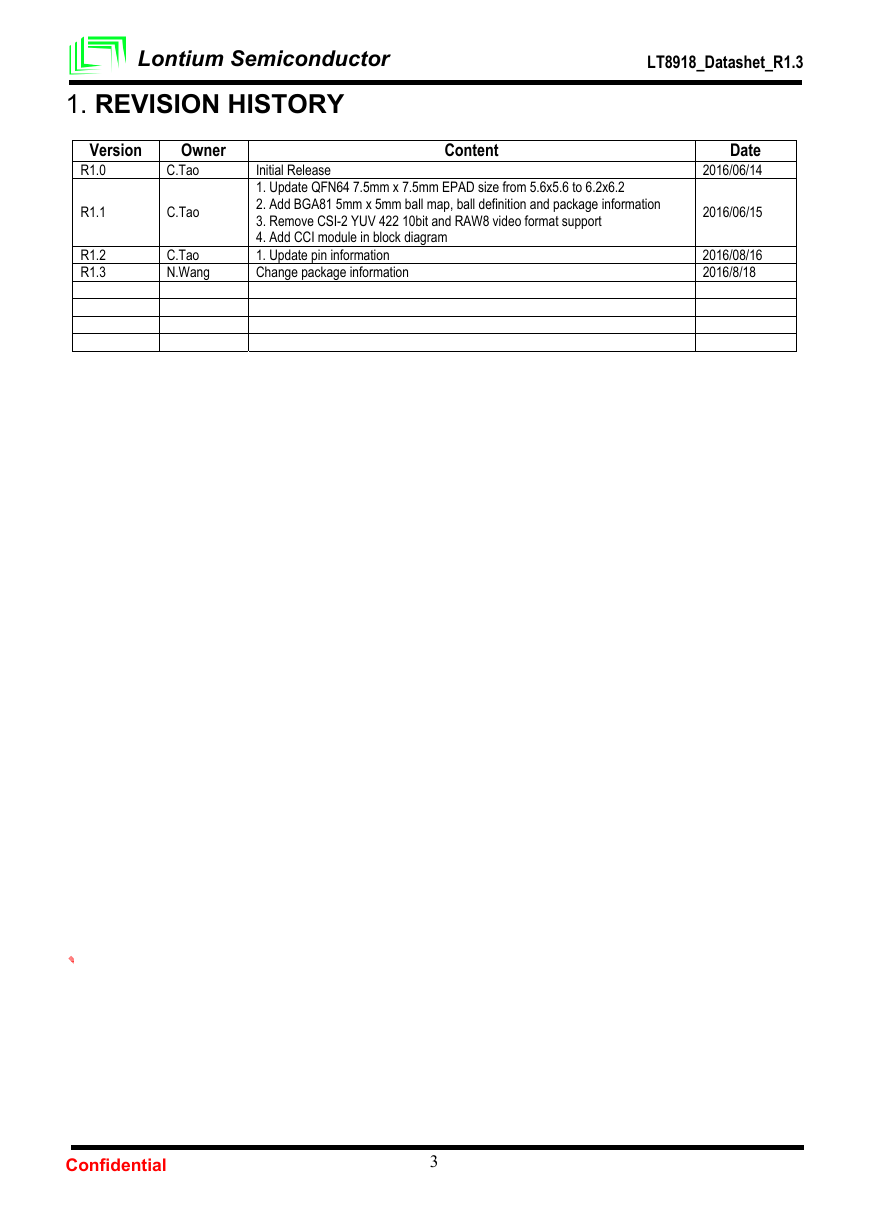

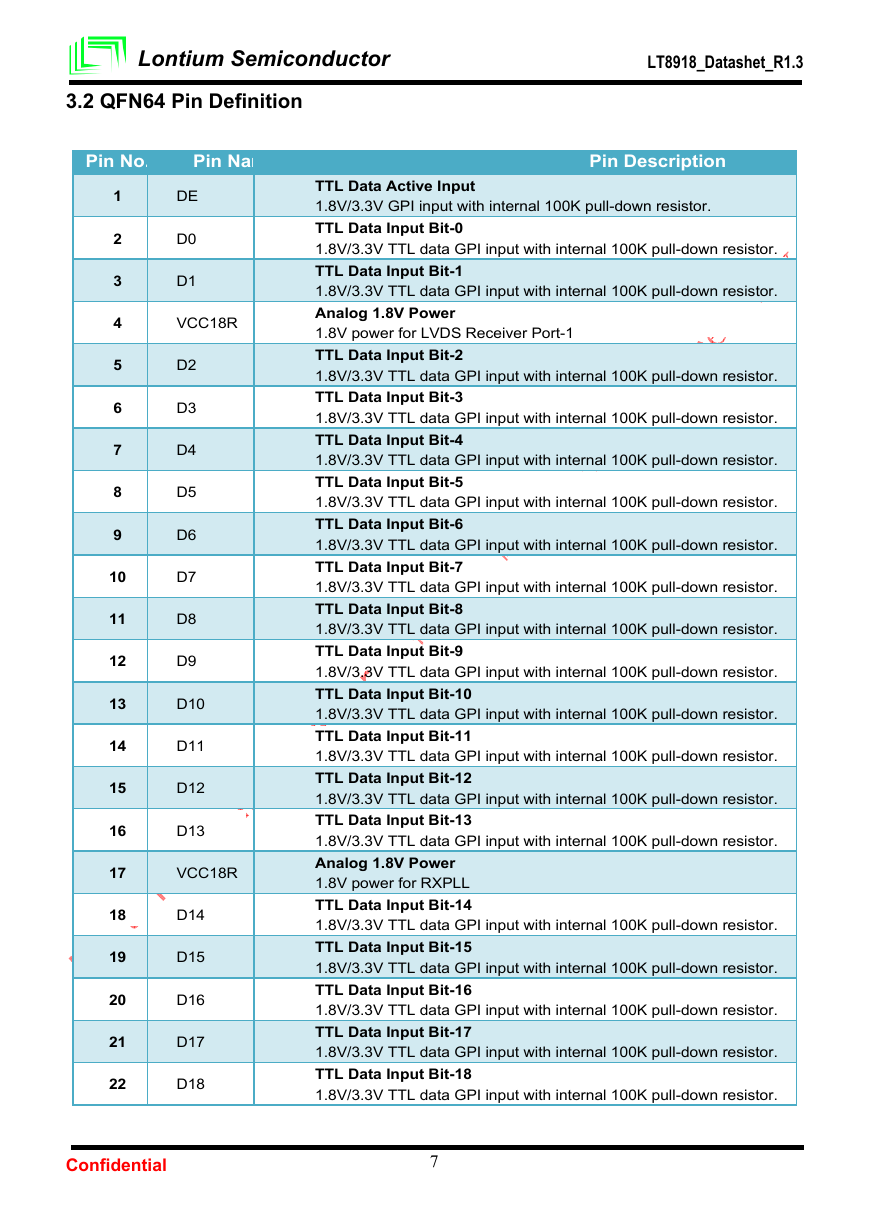

3.2 QFN64 Pin Definition

LT8918_Datashet_R1.3

Pin No.

Pin Name

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

DE

D0

D1

VCC18R

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

VCC18R

D14

D15

D16

D17

D18

Pin Description

TTL Data Active Input

1.8V/3.3V GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-0

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-1

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

Analog 1.8V Power

1.8V power for LVDS Receiver Port-1

TTL Data Input Bit-2

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-3

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-4

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-5

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-6

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-7

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-8

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-9

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-10

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-11

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-12

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-13

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

Analog 1.8V Power

1.8V power for RXPLL

TTL Data Input Bit-14

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-15

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-16

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-17

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-18

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

Confidential

7

�

Lontium Semiconductor

LT8918_Datashet_R1.3

Pin No.

Pin Name

Pin Description

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

D19

D20

D21

D22

D23

VCC18R

R6K

IRQO

XTALI

XTALO

VCC18T

MT0P

MT0N

MT1P

MT1N

MTCP

MTCN

MT2P

MT2N

MT3P

MT3N

TTL Data Input Bit-19

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-20

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-21

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-22

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

TTL Data Input Bit-23

1.8V/3.3V TTL data GPI input with internal 100K pull-down resistor.

Analog 1.8V Power

1.8V power for LVDS Receiver Port-2 and Bandgap

BandGap External Resistor

External 6K resistor for setting internal reference current.

Interrupt Request Output

In default, this pin is configured as interrupt request (IRQ) output.

Analog Test Signal Output

When this pin is configured as Hi-Z, it serves as analog test signal output.

Crystal Clock Input

A crystal oscillator should be attached between this pin and XTALO. However, a CMOS 1.8V

compatible clock signal can also be connected to this pin as reference clock of LT8918

Crystal Clock Output

A crystal oscillator should be attached between this pin and XTALI. If XTALI is used as reference

clock input, this pin must be floating.

Analog 1.8V Power

1.8V power for MIPI Transmitter

MIPI Data Lane-0 Positive Output

MIPITX Positive output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-0 Negative Output

MIPITX Negative output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-1 Positive Output

MIPITX Positive output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-1 Negative Output

MIPITX Negative output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-C Positive Output

MIPITX Positive output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-C Negative Output

MIPITX Negative output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-2 Positive Output

MIPITX Positive output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-2 Negative Output

MIPITX Negative output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-3 Positive Output

MIPITX Positive output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

MIPI Data Lane-3 Negative Output

MIPITX Negative output of Bi-directional polarity swappable differential pairs up to 2.5Gb/s.

Confidential

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc