SW 众核处理器

一 研发背景

2015 年 4 月份美国政府以中国的超算涉嫌用于核爆试验为由宣布制裁中国四家

超算中心以及国防科技大学,并禁止英特尔等美国公司向中国出口高性能计算芯

片。当时中国的“天河二号”使用的是 Intel Xeon E5 处理器及 Xeon Phi 加速

卡,美国的禁令使中国无法继续获得英特尔高性能芯片。

当然这并没有阻止中国研发超算的决心,在被禁售之前,无锡江南计算技术研究

就已经预料到美国会阻止中国超算的发展,所以开始自研处理器。早在 2010 年

无锡研究所曾利用 DEC ALPHA 21164A EV-56 架构成功研发了申威 SW1600 处理器,

使用 65nm 工艺,16 个 RISC 64 位核心,频率在 975MHz 到 1200MHz 之间,1.1GHz

频率下浮点性能 140.88GFLOPS。而搭载申威 SW1600 处理器的神威蓝光计算机成

为国内首个全部采用国产中央处理器(CPU)和系统软件构建的千万亿次计算机

系统使中国成为继美国日本之后成为第三个采用自主 CPU 构建千万亿次级超级

计算机的国家。但神威蓝光与美国还有很大的距离,所以在被美国禁售之后,无

锡研究所加紧研制,不再使用 Alpha 架构,而是自己研发指令集,这是专为高性

能计算研发的指令集。在自研指令集上终于研发成功了申威 SW26010。但 sw1600

已不再能够符合新一代超级计算机的要求,因此急需一款自主可控的新一代 cpu,

sw26010 就此问世。配备中国本土生产的申威 SW26010 多核处理器的 Sunway

TaihuLight 超级计算机,在 2018 年 3 月至 6 月之间成为了 TOP500 项目排名中

世界上最快的超级计算机。

二 芯片架构

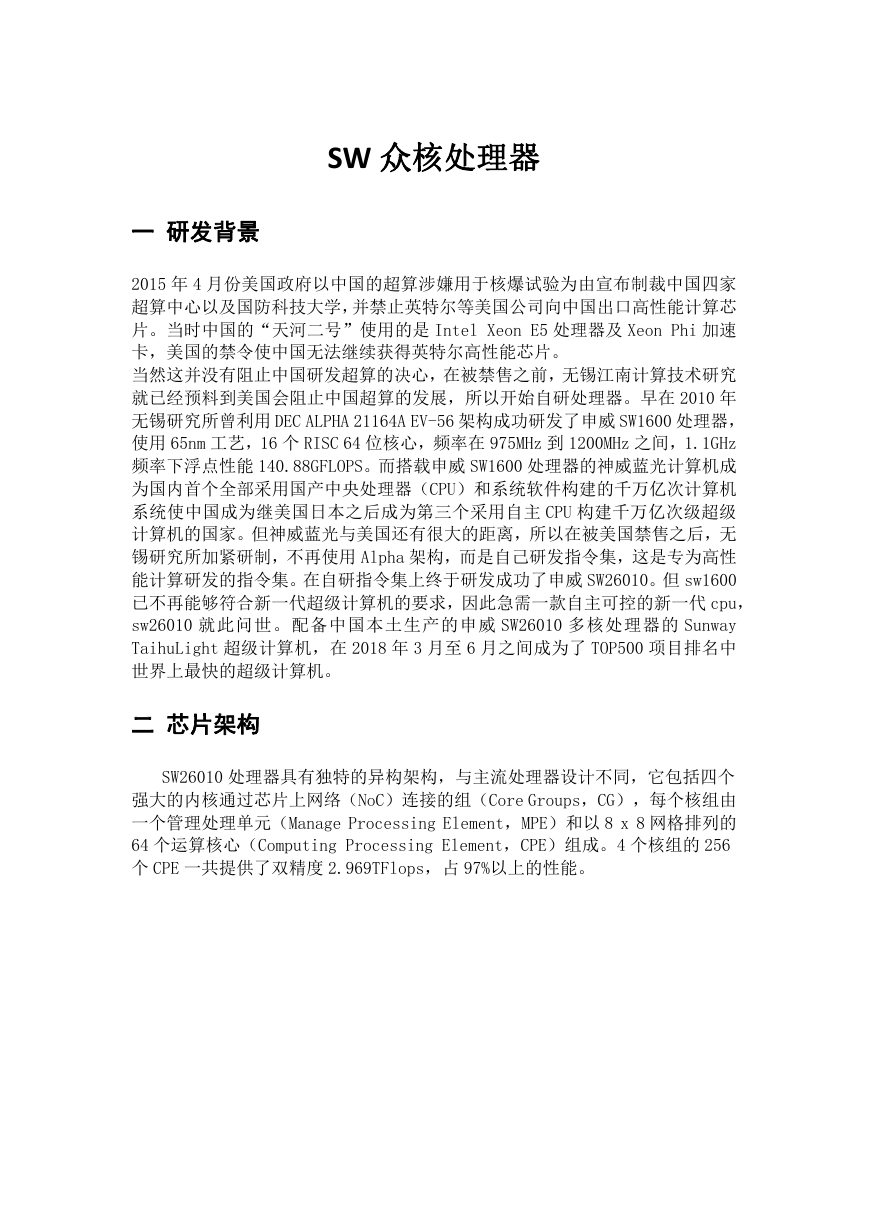

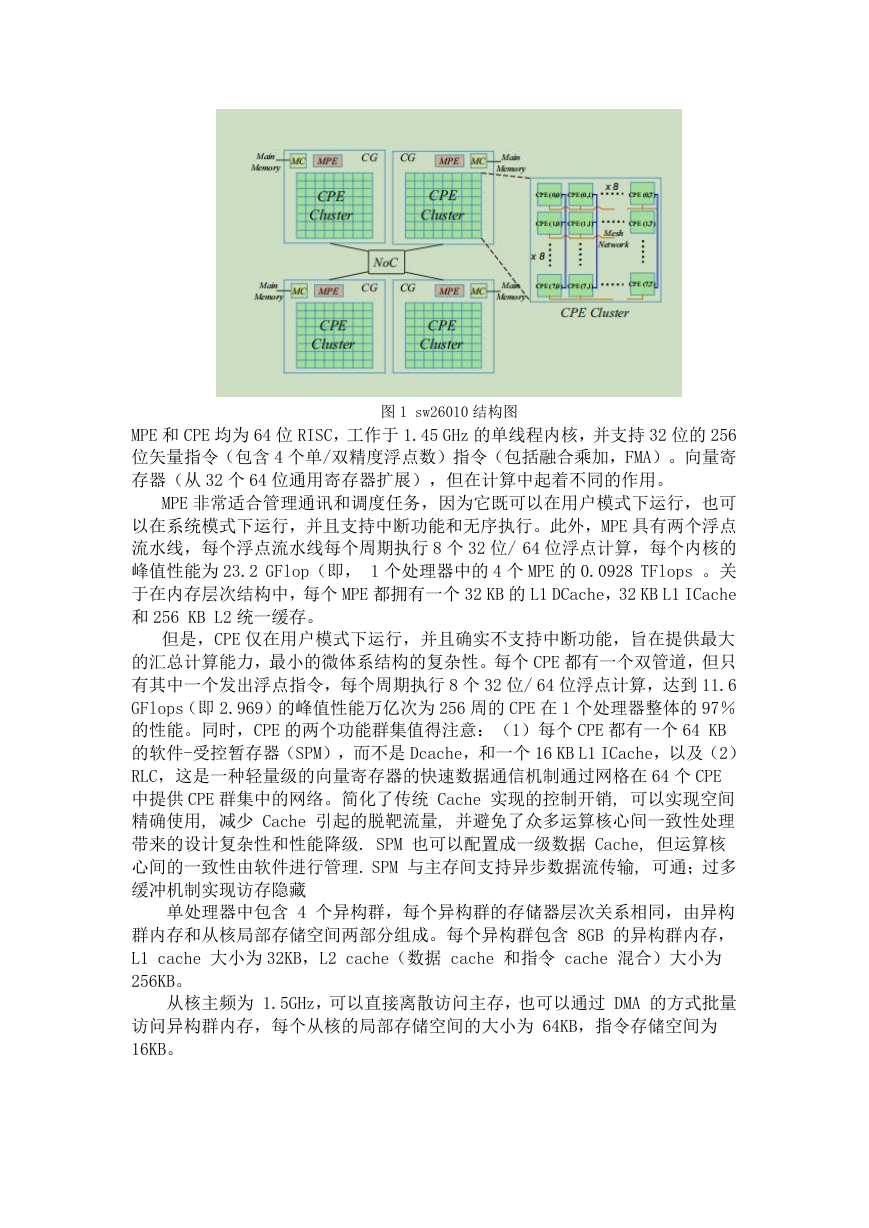

SW26010 处理器具有独特的异构架构,与主流处理器设计不同,它包括四个

强大的内核通过芯片上网络(NoC)连接的组(Core Groups,CG),每个核组由

一个管理处理单元(Manage Processing Element,MPE)和以 8 x 8 网格排列的

64 个运算核心(Computing Processing Element,CPE)组成。4 个核组的 256

个 CPE 一共提供了双精度 2.969TFlops,占 97%以上的性能。

�

图 1 sw26010 结构图

MPE 和 CPE 均为 64 位 RISC,工作于 1.45 GHz 的单线程内核,并支持 32 位的 256

位矢量指令(包含 4 个单/双精度浮点数)指令(包括融合乘加,FMA)。向量寄

存器(从 32 个 64 位通用寄存器扩展),但在计算中起着不同的作用。

MPE 非常适合管理通讯和调度任务,因为它既可以在用户模式下运行,也可

以在系统模式下运行,并且支持中断功能和无序执行。此外,MPE 具有两个浮点

流水线,每个浮点流水线每个周期执行 8 个 32 位/ 64 位浮点计算,每个内核的

峰值性能为 23.2 GFlop(即, 1 个处理器中的 4 个 MPE 的 0.0928 TFlops 。关

于在内存层次结构中,每个 MPE 都拥有一个 32 KB 的 L1 DCache,32 KB L1 ICache

和 256 KB L2 统一缓存。

但是,CPE 仅在用户模式下运行,并且确实不支持中断功能,旨在提供最大

的汇总计算能力,最小的微体系结构的复杂性。每个 CPE 都有一个双管道,但只

有其中一个发出浮点指令,每个周期执行 8 个 32 位/ 64 位浮点计算,达到 11.6

GFlops(即 2.969)的峰值性能万亿次为 256 周的 CPE 在 1 个处理器整体的 97%

的性能。同时,CPE 的两个功能群集值得注意:(1)每个 CPE 都有一个 64 KB

的软件-受控暂存器(SPM),而不是 Dcache,和一个 16 KB L1 ICache,以及(2)

RLC,这是一种轻量级的向量寄存器的快速数据通信机制通过网格在 64 个 CPE

中提供 CPE 群集中的网络。简化了传统 Cache 实现的控制开销, 可以实现空间

精确使用, 减少 Cache 引起的脱靶流量, 并避免了众多运算核心间一致性处理

带来的设计复杂性和性能降级. SPM 也可以配置成一级数据 Cache, 但运算核

心间的一致性由软件进行管理. SPM 与主存间支持异步数据流传输, 可通;过多

缓冲机制实现访存隐藏

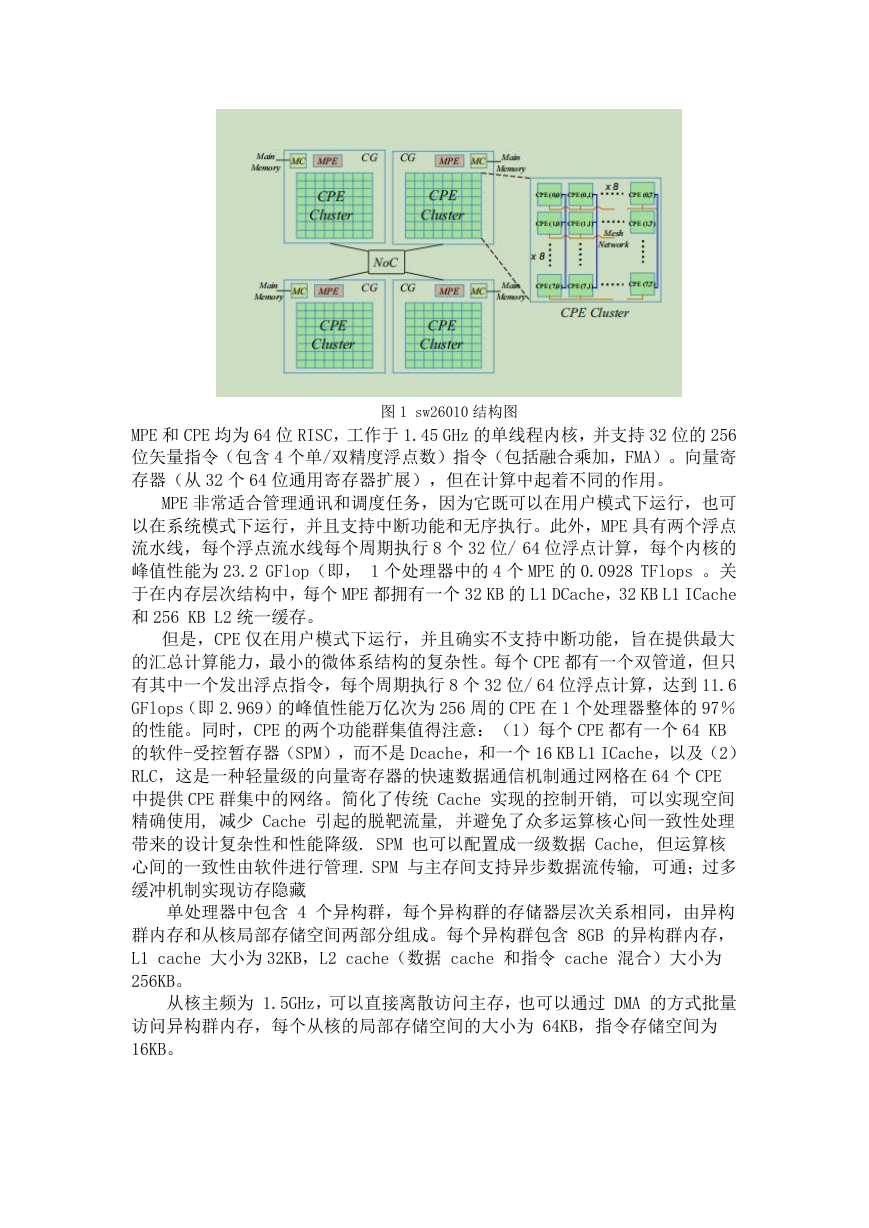

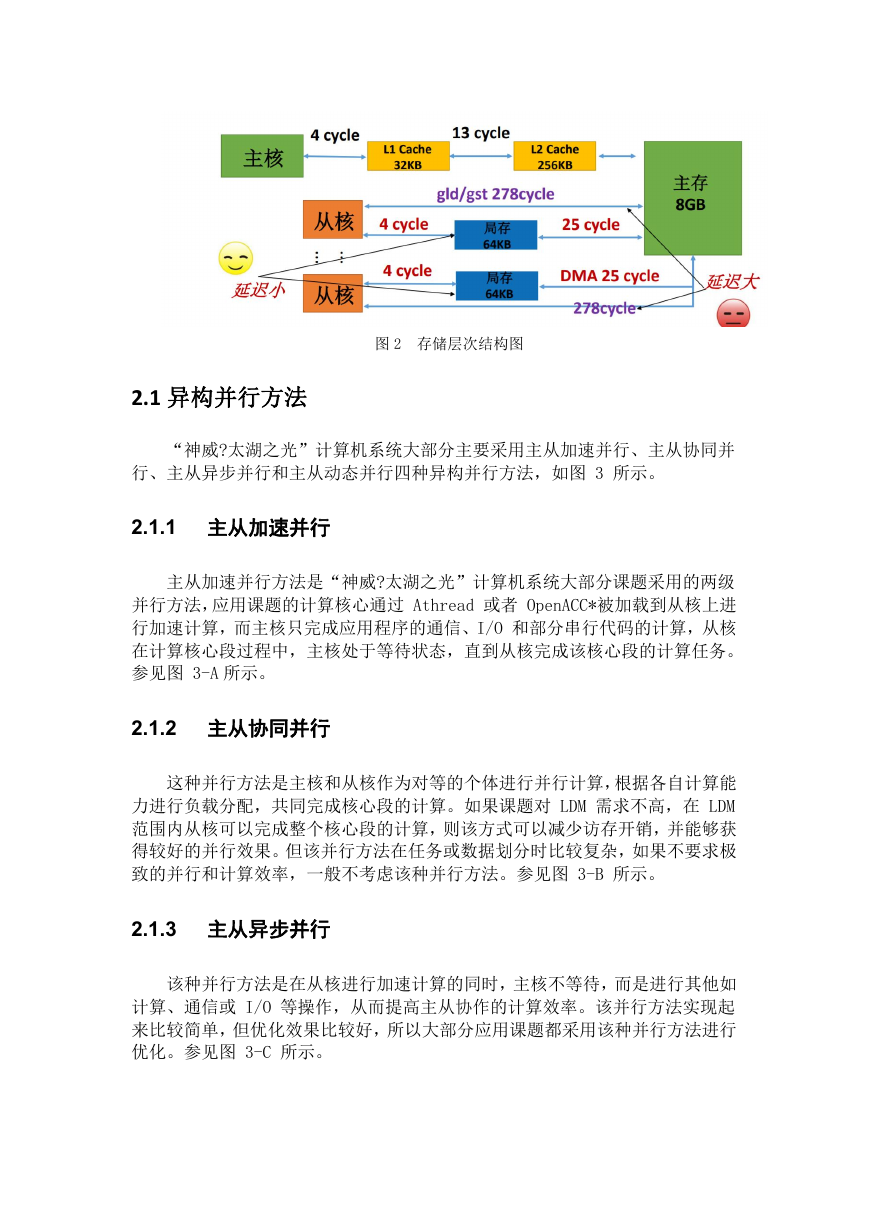

单处理器中包含 4 个异构群,每个异构群的存储器层次关系相同,由异构

群内存和从核局部存储空间两部分组成。每个异构群包含 8GB 的异构群内存,

L1 cache 大小为 32KB,L2 cache(数据 cache 和指令 cache 混合)大小为

256KB。

从核主频为 1.5GHz,可以直接离散访问主存,也可以通过 DMA 的方式批量

访问异构群内存,每个从核的局部存储空间的大小为 64KB,指令存储空间为

16KB。

�

图 2 存储层次结构图

2.1 异构并行方法

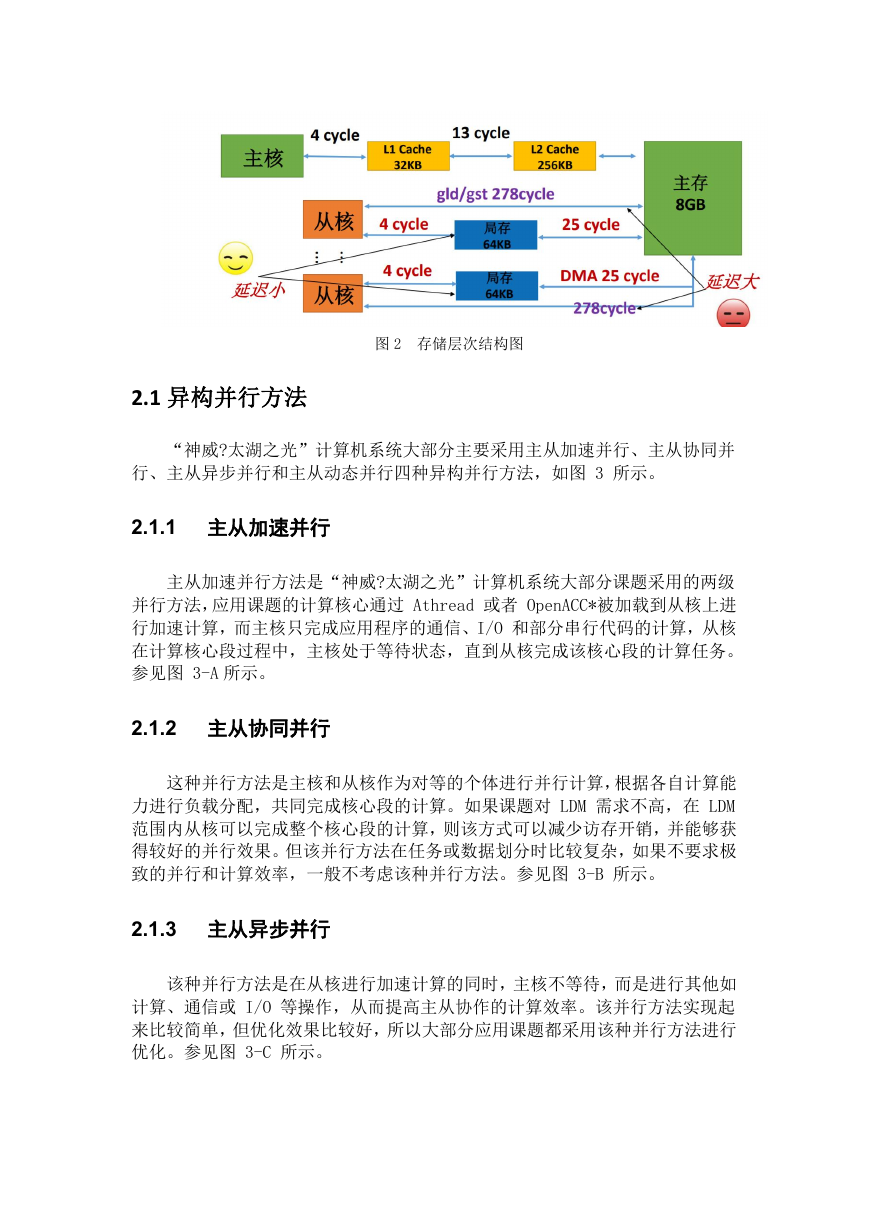

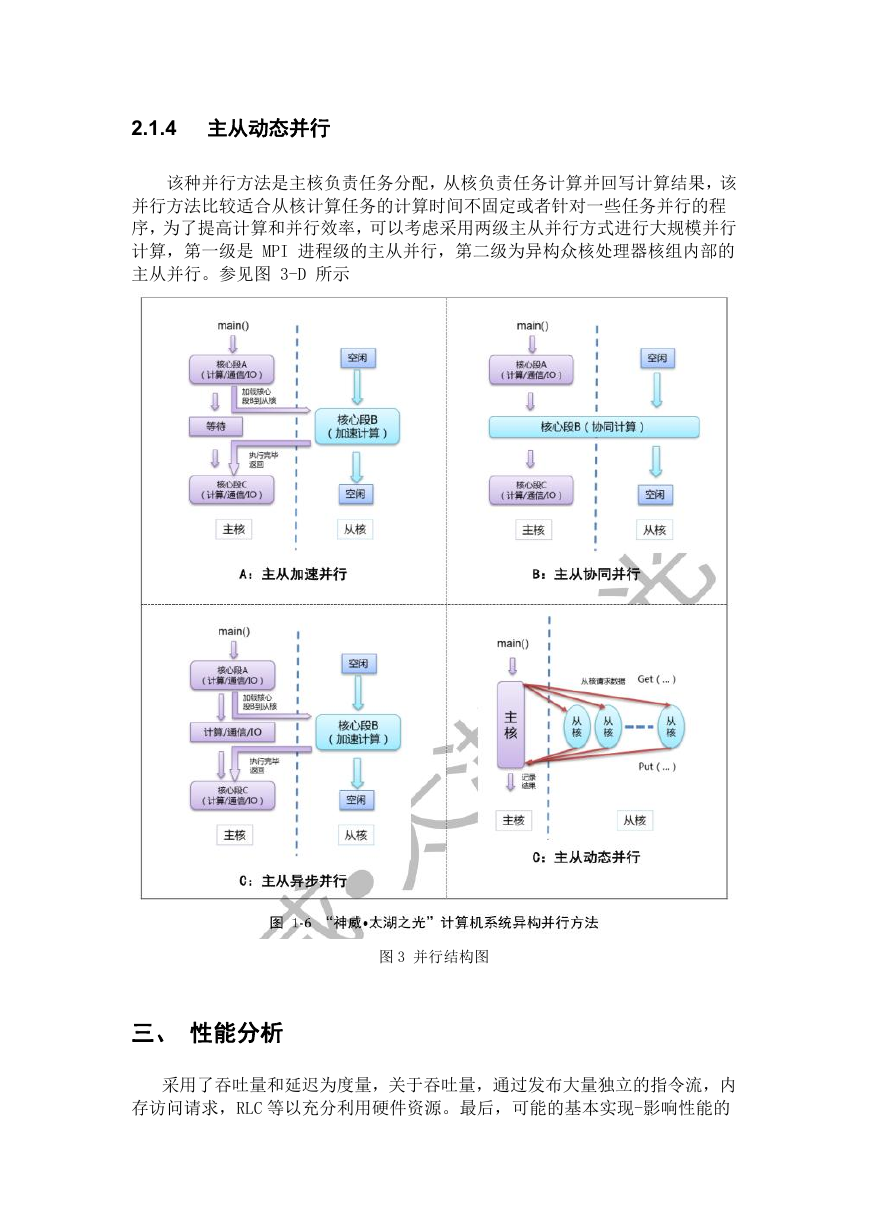

“神威?太湖之光”计算机系统大部分主要采用主从加速并行、主从协同并

行、主从异步并行和主从动态并行四种异构并行方法,如图 3 所示。

2.1.1 主从加速并行

主从加速并行方法是“神威?太湖之光”计算机系统大部分课题采用的两级

并行方法,应用课题的计算核心通过 Athread 或者 OpenACC*被加载到从核上进

行加速计算,而主核只完成应用程序的通信、I/O 和部分串行代码的计算,从核

在计算核心段过程中,主核处于等待状态,直到从核完成该核心段的计算任务。

参见图 3-A 所示。

2.1.2 主从协同并行

这种并行方法是主核和从核作为对等的个体进行并行计算,根据各自计算能

力进行负载分配,共同完成核心段的计算。如果课题对 LDM 需求不高,在 LDM

范围内从核可以完成整个核心段的计算,则该方式可以减少访存开销,并能够获

得较好的并行效果。但该并行方法在任务或数据划分时比较复杂,如果不要求极

致的并行和计算效率,一般不考虑该种并行方法。参见图 3-B 所示。

2.1.3 主从异步并行

该种并行方法是在从核进行加速计算的同时,主核不等待,而是进行其他如

计算、通信或 I/O 等操作,从而提高主从协作的计算效率。该并行方法实现起

来比较简单,但优化效果比较好,所以大部分应用课题都采用该种并行方法进行

优化。参见图 3-C 所示。

�

2.1.4 主从动态并行

该种并行方法是主核负责任务分配,从核负责任务计算并回写计算结果,该

并行方法比较适合从核计算任务的计算时间不固定或者针对一些任务并行的程

序,为了提高计算和并行效率,可以考虑采用两级主从并行方式进行大规模并行

计算,第一级是 MPI 进程级的主从并行,第二级为异构众核处理器核组内部的

主从并行。参见图 3-D 所示

图 3 并行结构图

三、 性能分析

采用了吞吐量和延迟为度量,关于吞吐量,通过发布大量独立的指令流,内

存访问请求,RLC 等以充分利用硬件资源。最后,可能的基本实现-影响性能的

�

关键架构组件的设置通过对数值的分析得出推论结果以及专用装配体的行为基

准。

(1)CPE 双流水线分析

尽管 CPE 可以支持双重发射,但是只有一个流水线设计用于浮点运算,而其

他管道主要处理内存访问操作。我们在两个方面评估了 CPE 流水线的性能方面:

两种延迟方面的向量指令和吞吐量

以及指令发布顺序。

1. 向量指令延迟

对于算术和置换指令,序列由相同的指令组成:$

va←op

va, $

vb,...),其中$

va 和$

vb 是向量寄存器和运算表示被测量

va 同时充当源和目标指令中的操作数。• 对于 SPM 访问说明,

($

的指令。注意$

在采取以下措施之前-我们首先通过以下方式初始化 RAW 依赖项存储驻留在寄存

a 中的 SPM 地址地址到 addr 指向的 SPM 位置,然后从 SPM 将地址 addr 的

器$

数据加载到$

a)))。这样,当前负载必须

停顿,直到前一个取回地址。结果表明,大多数向量算术指令需要花费 7 个周期

(昂贵的除外)平方根(sqrt)和除法(div)指令。

a←反复加载(0($

a(即,$

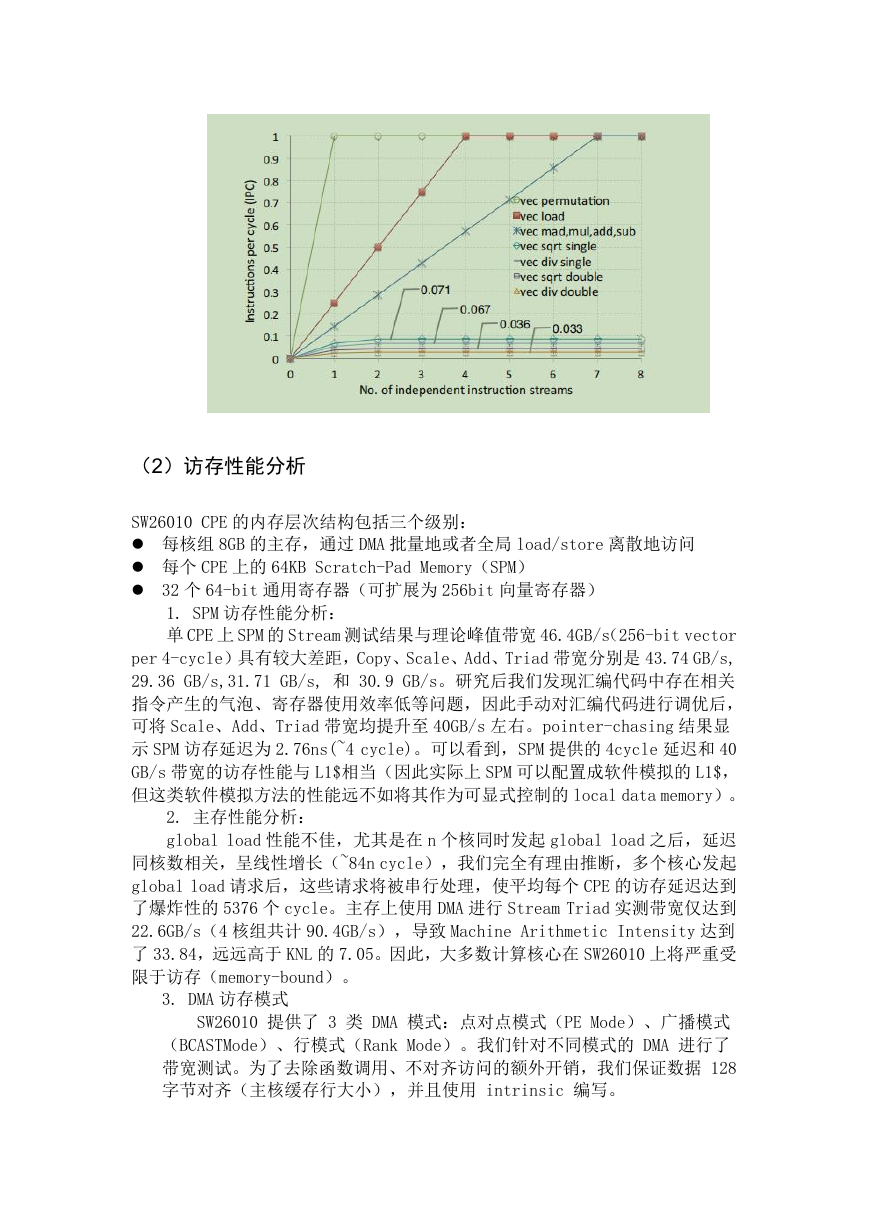

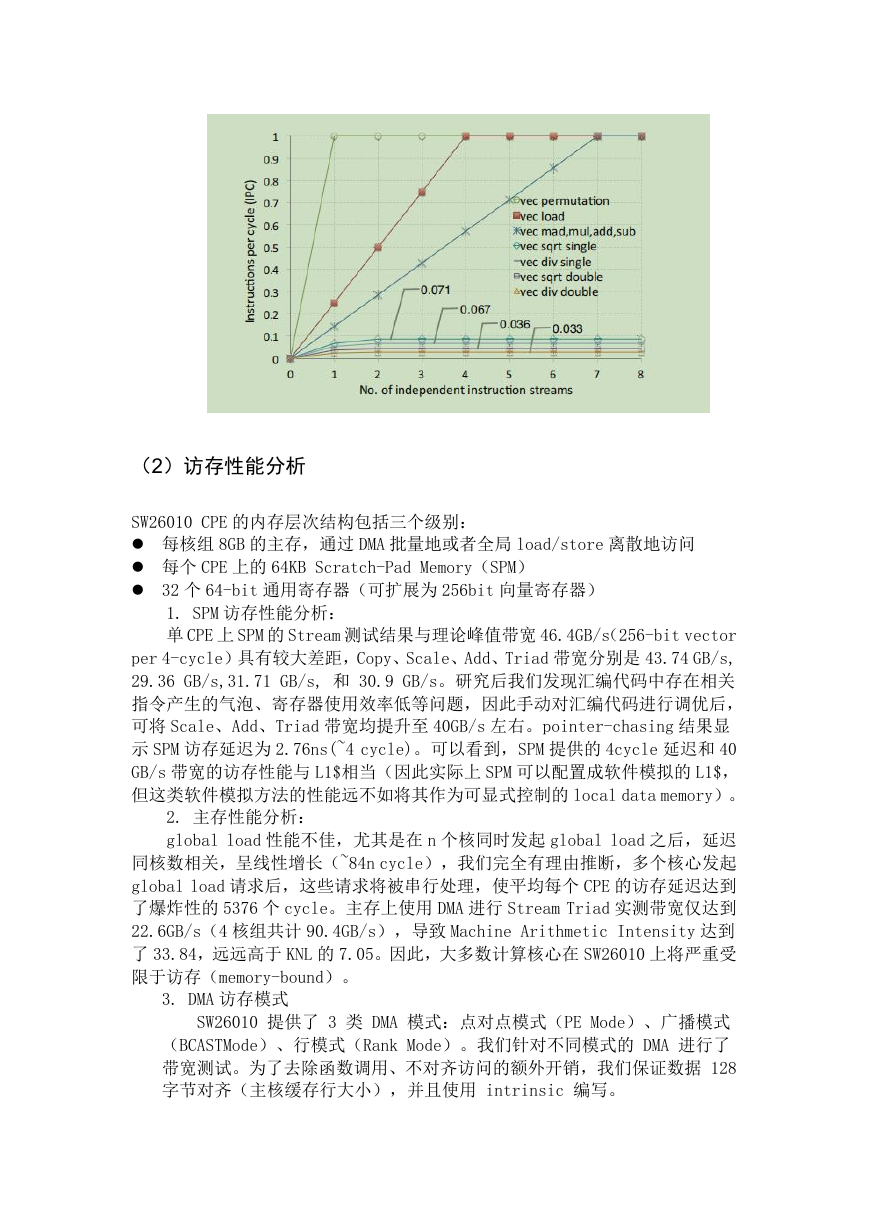

2.向量指令吞吐量

向量指令吞吐量是通过长期的相关指令使用不同的寄存器。鉴于 CPE 是单

线程的,我们按照周期(IPC)指标,并逐渐增加独立的指令流,探索条件达到

最佳性能。据此,我们对各类算术指令进行了测算,所得结果如图所示。可以发

现,对于大多数算术指令,需要 7 个独立指令流才能达到最高吞吐。另外,除法

和开方指令不仅延迟高,而且只能部分流水,例如双精度除法需要间隔 30 个

cycle 才能发射下一个除法。因此,软件模拟的除法、开方、倒数开方结合 loop

unrolling 是提升包含这类操作的应用性能的重要途径。

�

(2)访存性能分析

SW26010 CPE 的内存层次结构包括三个级别:

每核组 8GB 的主存,通过 DMA 批量地或者全局 load/store 离散地访问

每个 CPE 上的 64KB Scratch-Pad Memory(SPM)

32 个 64-bit 通用寄存器(可扩展为 256bit 向量寄存器)

1. SPM 访存性能分析:

单 CPE 上 SPM 的 Stream 测试结果与理论峰值带宽 46.4GB/s(256-bit vector

per 4-cycle)具有较大差距,Copy、Scale、Add、Triad 带宽分别是 43.74 GB/s,

29.36 GB/s,31.71 GB/s, 和 30.9 GB/s。研究后我们发现汇编代码中存在相关

指令产生的气泡、寄存器使用效率低等问题,因此手动对汇编代码进行调优后,

可将 Scale、Add、Triad 带宽均提升至 40GB/s 左右。pointer-chasing 结果显

示 SPM 访存延迟为 2.76ns(~4 cycle)。可以看到,SPM 提供的 4cycle 延迟和 40

GB/s 带宽的访存性能与 L1$相当(因此实际上 SPM 可以配置成软件模拟的 L1$,

但这类软件模拟方法的性能远不如将其作为可显式控制的 local data memory)。

2. 主存性能分析:

global load 性能不佳,尤其是在 n 个核同时发起 global load 之后,延迟

同核数相关,呈线性增长(~84n cycle),我们完全有理由推断,多个核心发起

global load 请求后,这些请求将被串行处理,使平均每个 CPE 的访存延迟达到

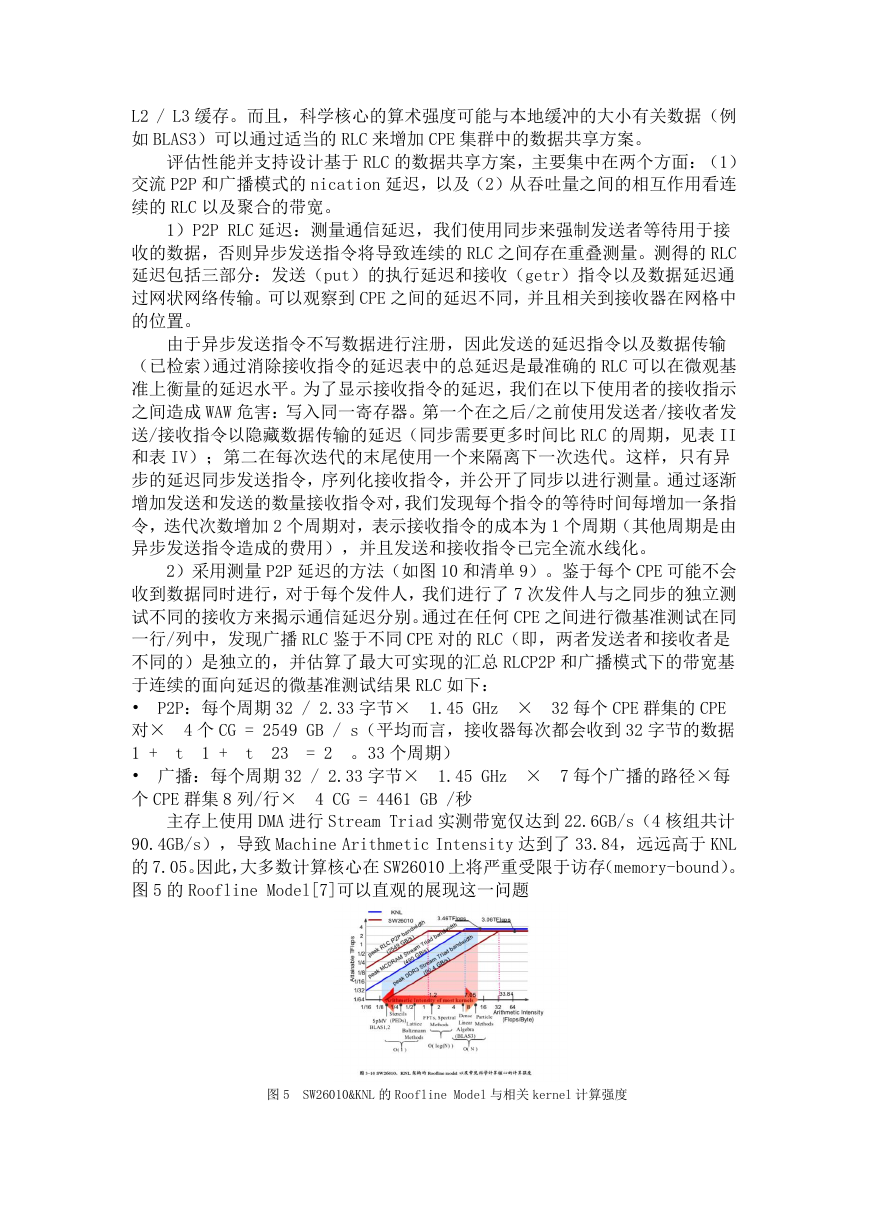

了爆炸性的 5376 个 cycle。主存上使用 DMA 进行 Stream Triad 实测带宽仅达到

22.6GB/s(4 核组共计 90.4GB/s),导致 Machine Arithmetic Intensity 达到

了 33.84,远远高于 KNL 的 7.05。因此,大多数计算核心在 SW26010 上将严重受

限于访存(memory-bound)。

3. DMA 访存模式

SW26010 提供了 3 类 DMA 模式:点对点模式(PE Mode)、广播模式

(BCASTMode)、行模式(Rank Mode)。我们针对不同模式的 DMA 进行了

带宽测试。为了去除函数调用、不对齐访问的额外开销,我们保证数据 128

字节对齐(主核缓存行大小),并且使用 intrinsic 编写。

�

点对点模式适用于任何数据传输场景。每个从核读写各自所需的主存数

据。因此我们全面地测试了在从核数量不同、传输单位数据块大小不同的情

况下 DMA 的读写带宽,并且使用 stream 基准测试集进行了实际带宽测试。

结果如图 3–2 所示。我们发现:

• 读带宽最高为 27.9 GB/s,并且需要 64 个从核完全参与数据传输才

能达到最大带宽;

• 写带宽峰值为 24.1 GB/s;

• 读写混合时,带宽峰值为 23.4 GB/s;

• Stream Traid 带宽测试峰值为 22.6 GB/s;

广播模式适用于主存向从核广播数据,因此是单向传输。与点对点模式

不同的是,广播模式下任意一个从核发起广播请求后,数据会从主存传输到

从核阵列上,然后再通过从核阵列网络将数据传输到所有从核上。因此,与

点对点模式相比,广播模式下数据无需进行多次重复传输。实测发现广播模

式带宽为 6.97GB/s,考虑到广播模式避免了 63 次重复的数据传输,因此有

效带宽为 446.1 GB/s(6.97 × 64)。

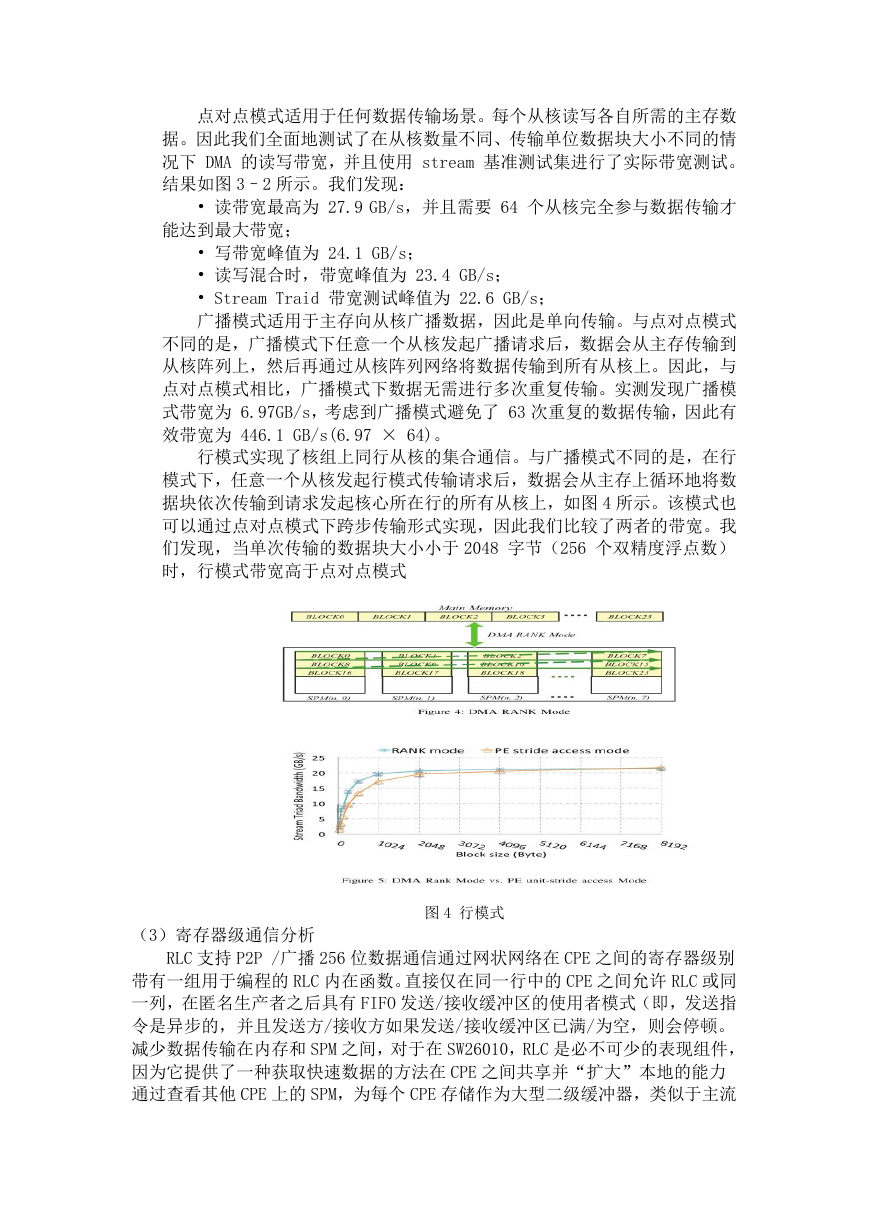

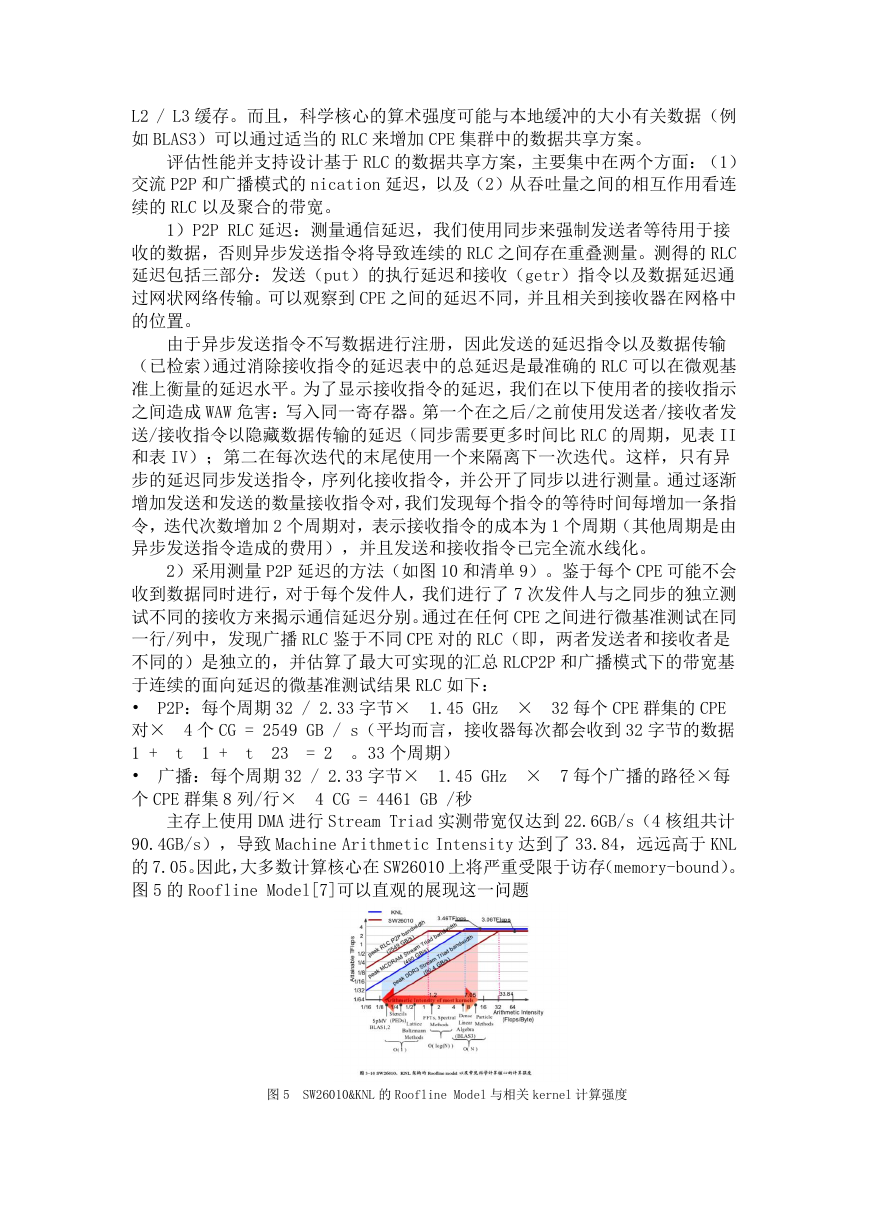

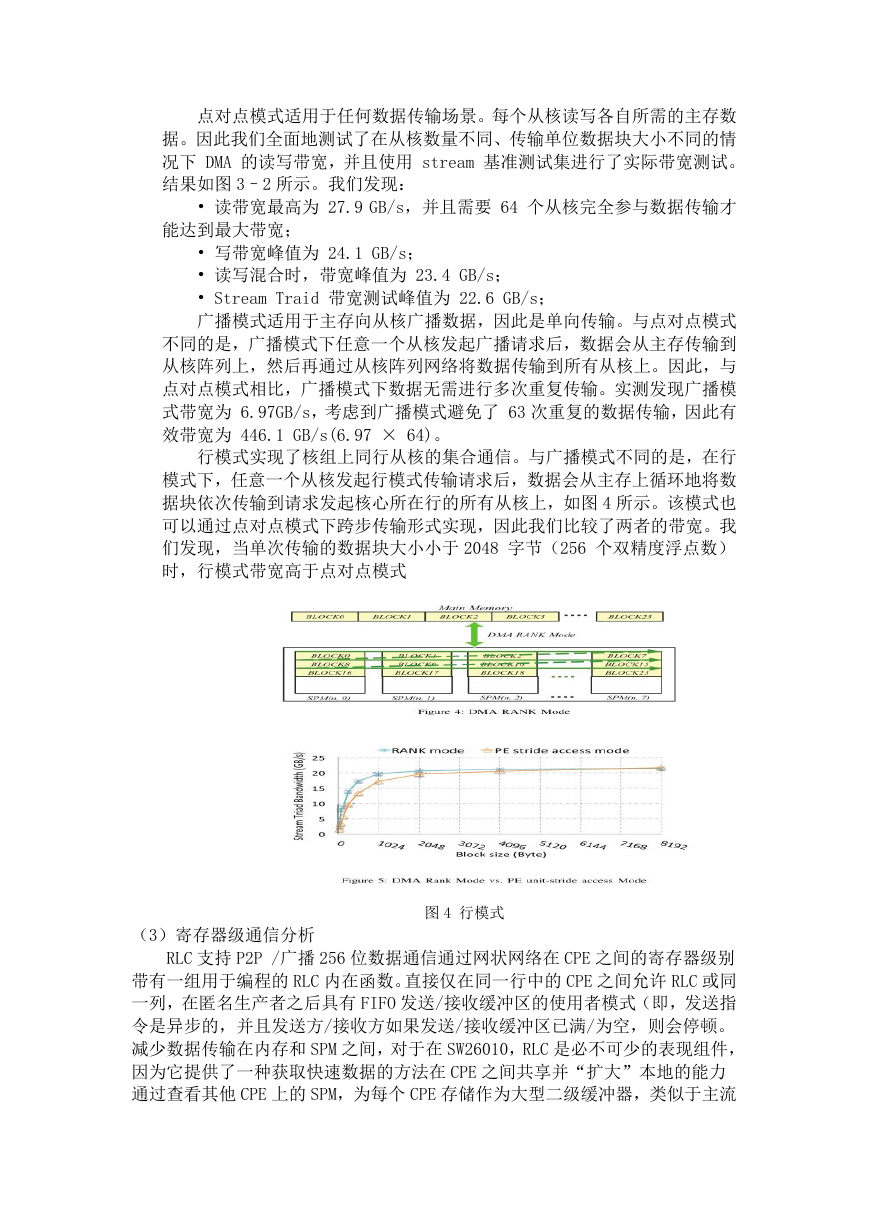

行模式实现了核组上同行从核的集合通信。与广播模式不同的是,在行

模式下,任意一个从核发起行模式传输请求后,数据会从主存上循环地将数

据块依次传输到请求发起核心所在行的所有从核上,如图 4 所示。该模式也

可以通过点对点模式下跨步传输形式实现,因此我们比较了两者的带宽。我

们发现,当单次传输的数据块大小小于 2048 字节(256 个双精度浮点数)

时,行模式带宽高于点对点模式

(3)寄存器级通信分析

图 4 行模式

RLC 支持 P2P /广播 256 位数据通信通过网状网络在 CPE 之间的寄存器级别

带有一组用于编程的 RLC 内在函数。直接仅在同一行中的 CPE 之间允许 RLC 或同

一列,在匿名生产者之后具有 FIFO 发送/接收缓冲区的使用者模式(即,发送指

令是异步的,并且发送方/接收方如果发送/接收缓冲区已满/为空,则会停顿。

减少数据传输在内存和 SPM 之间,对于在 SW26010,RLC 是必不可少的表现组件,

因为它提供了一种获取快速数据的方法在 CPE 之间共享并“扩大”本地的能力

通过查看其他 CPE 上的 SPM,为每个 CPE 存储作为大型二级缓冲器,类似于主流

�

L2 / L3 缓存。而且,科学核心的算术强度可能与本地缓冲的大小有关数据(例

如 BLAS3)可以通过适当的 RLC 来增加 CPE 集群中的数据共享方案。

评估性能并支持设计基于 RLC 的数据共享方案,主要集中在两个方面:(1)

交流 P2P 和广播模式的 nication 延迟,以及(2)从吞吐量之间的相互作用看连

续的 RLC 以及聚合的带宽。

1)P2P RLC 延迟:测量通信延迟,我们使用同步来强制发送者等待用于接

收的数据,否则异步发送指令将导致连续的 RLC 之间存在重叠测量。测得的 RLC

延迟包括三部分:发送(put)的执行延迟和接收(getr)指令以及数据延迟通

过网状网络传输。可以观察到 CPE 之间的延迟不同,并且相关到接收器在网格中

的位置。

由于异步发送指令不写数据进行注册,因此发送的延迟指令以及数据传输

(已检索)通过消除接收指令的延迟表中的总延迟是最准确的 RLC 可以在微观基

准上衡量的延迟水平。为了显示接收指令的延迟,我们在以下使用者的接收指示

之间造成 WAW 危害:写入同一寄存器。第一个在之后/之前使用发送者/接收者发

送/接收指令以隐藏数据传输的延迟(同步需要更多时间比 RLC 的周期,见表 II

和表 IV);第二在每次迭代的末尾使用一个来隔离下一次迭代。这样,只有异

步的延迟同步发送指令,序列化接收指令,并公开了同步以进行测量。通过逐渐

增加发送和发送的数量接收指令对,我们发现每个指令的等待时间每增加一条指

令,迭代次数增加 2 个周期对,表示接收指令的成本为 1 个周期(其他周期是由

异步发送指令造成的费用),并且发送和接收指令已完全流水线化。

2)采用测量 P2P 延迟的方法(如图 10 和清单 9)。鉴于每个 CPE 可能不会

收到数据同时进行,对于每个发件人,我们进行了 7 次发件人与之同步的独立测

试不同的接收方来揭示通信延迟分别。通过在任何 CPE 之间进行微基准测试在同

一行/列中,发现广播 RLC 鉴于不同 CPE 对的 RLC(即,两者发送者和接收者是

不同的)是独立的,并估算了最大可实现的汇总 RLCP2P 和广播模式下的带宽基

于连续的面向延迟的微基准测试结果 RLC 如下:

•

对× 4 个 CG = 2549 GB / s(平均而言,接收器每次都会收到 32 字节的数据

1 +

• 广播:每个周期 32 / 2.33 字节× 1.45 GHz × 7 每个广播的路径×每

个 CPE 群集 8 列/行× 4 CG = 4461 GB /秒

P2P:每个周期 32 / 2.33 字节× 1.45 GHz × 32 每个 CPE 群集的 CPE

= 2 。33 个周期)

t

1 +

t

23

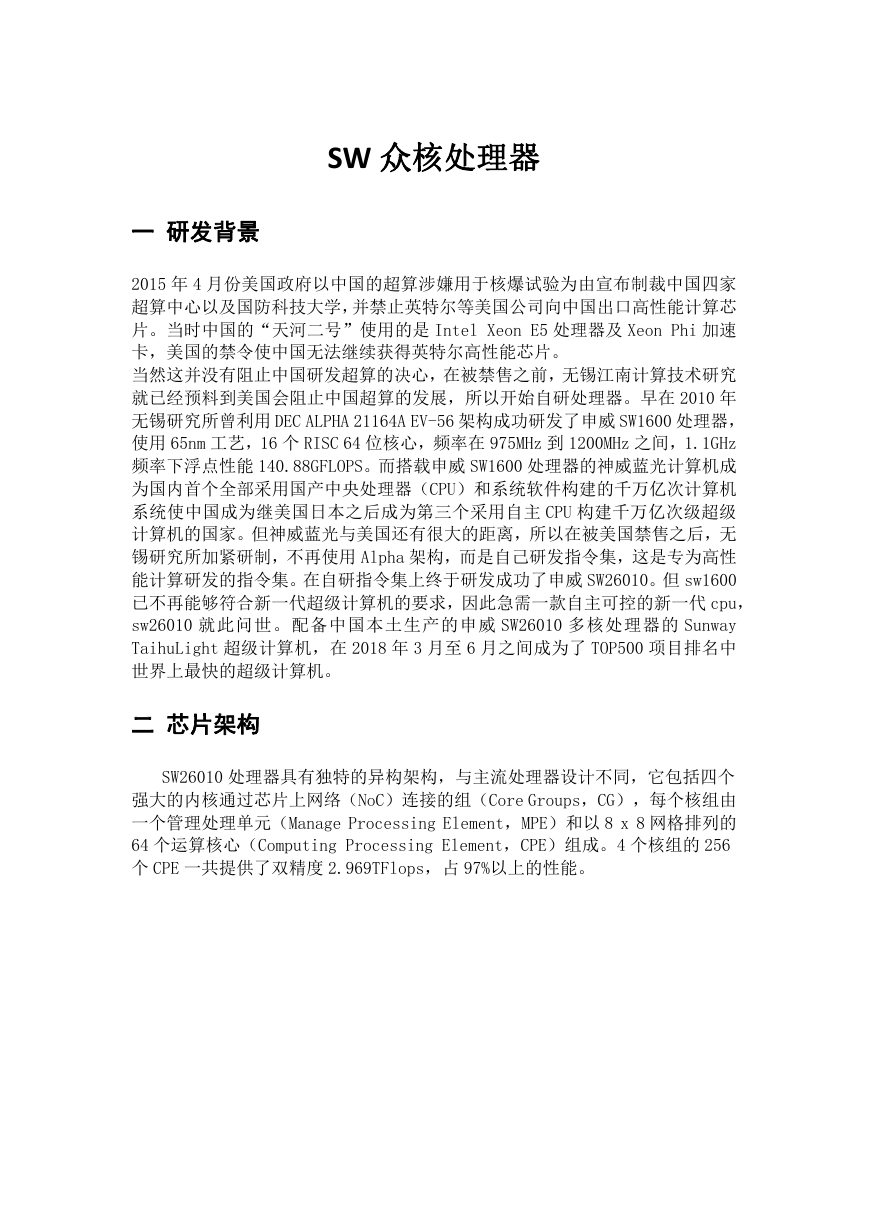

主存上使用 DMA 进行 Stream Triad 实测带宽仅达到 22.6GB/s(4 核组共计

90.4GB/s),导致 Machine Arithmetic Intensity 达到了 33.84,远远高于 KNL

的 7.05。因此,大多数计算核心在 SW26010 上将严重受限于访存(memory-bound)。

图 5 的 Roofline Model[7]可以直观的展现这一问题

图 5 SW26010&KNL 的 Roofline Model 与相关 kernel 计算强度

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc