Quartus II 系列学习教程三

Quartus II 调用 PLL 模块

SJTU 2017 年 5 月

�

目录

一、

PLL 简介与应用背景 ..................................................................................... 1

1) PLL 锁相环简介 .......................................................................................... 1

2) 应用背景 ...................................................................................................... 1

二、 Quartus II 设置 PLL 的调用 ........................................................................... 2

1) 生成 PLL 的 IP 核例化文件 ....................................................................... 2

2) 调用 PLL 的 IP 核例化文件 ........................................................................ 8

3) Modelsim_Altera 仿真结果 ......................................................................... 9

I

�

一、 PLL 简介与应用背景

1) PLL 锁相环简介

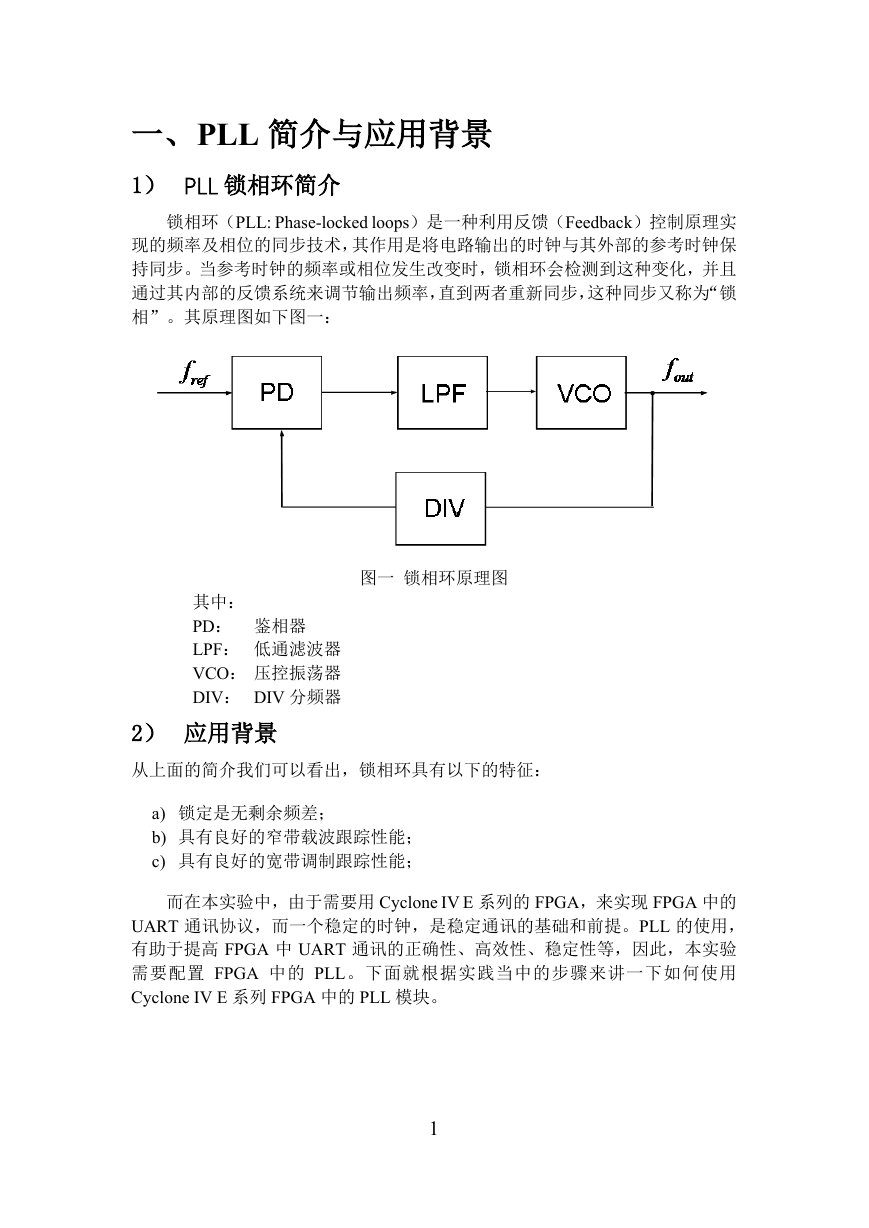

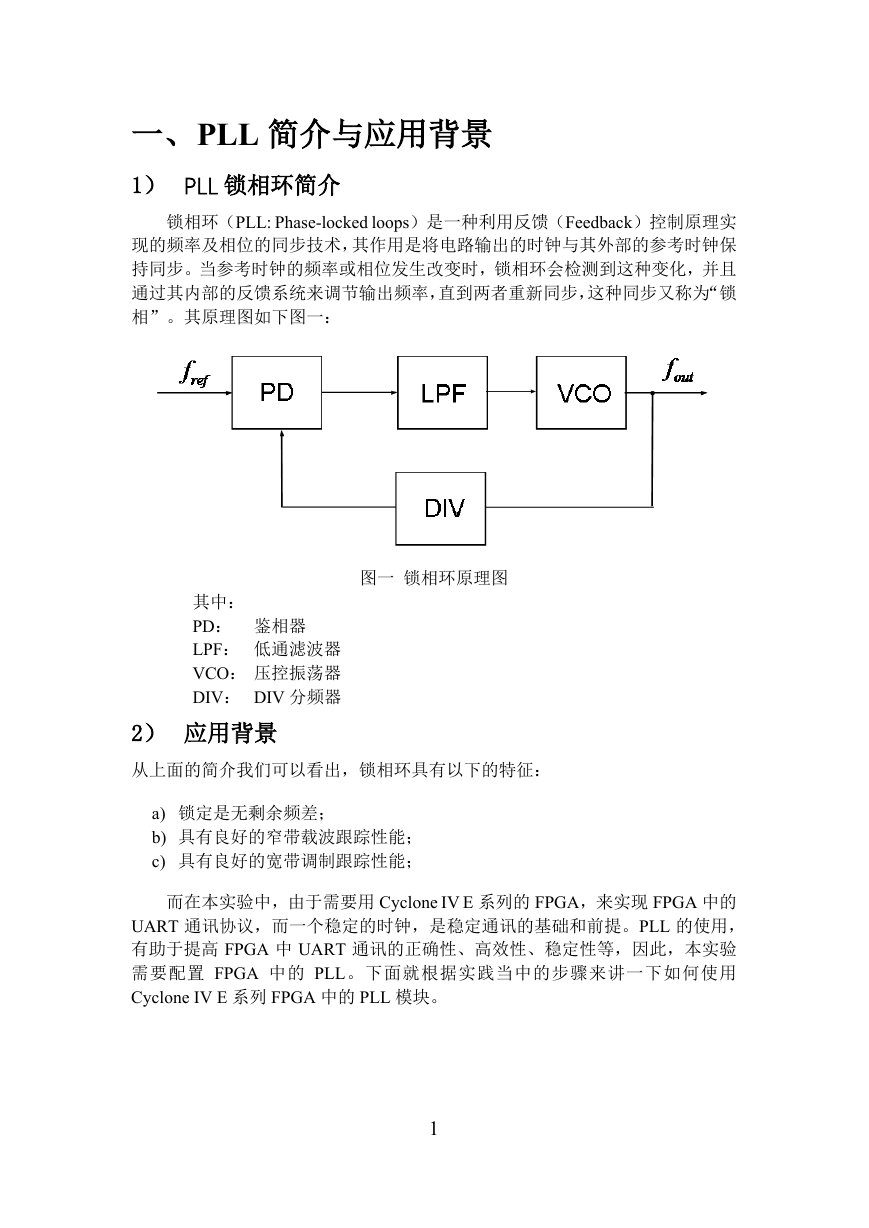

锁相环(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制原理实

现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保

持同步。当参考时钟的频率或相位发生改变时,锁相环会检测到这种变化,并且

通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“锁

相”。其原理图如下图一:

图一 锁相环原理图

其中:

PD: 鉴相器

LPF: 低通滤波器

VCO: 压控振荡器

DIV: DIV 分频器

2) 应用背景

从上面的简介我们可以看出,锁相环具有以下的特征:

a) 锁定是无剩余频差;

b) 具有良好的窄带载波跟踪性能;

c) 具有良好的宽带调制跟踪性能;

而在本实验中,由于需要用 Cyclone IV E 系列的 FPGA,来实现 FPGA 中的

UART 通讯协议,而一个稳定的时钟,是稳定通讯的基础和前提。PLL 的使用,

有助于提高 FPGA 中 UART 通讯的正确性、高效性、稳定性等,因此,本实验

需要配置 FPGA 中的 PLL。下面就根据实践当中的步骤来讲一下如何使用

Cyclone IV E 系列 FPGA 中的 PLL 模块。

1

�

二、 Quartus II 设置 PLL 的调用

本 例 程 的 操 作 环 境 是 Quartus II 13 , 安 装 Cyclone IV 器 件 库 和

Modelsim_Altera 的 EDA 仿真工具。

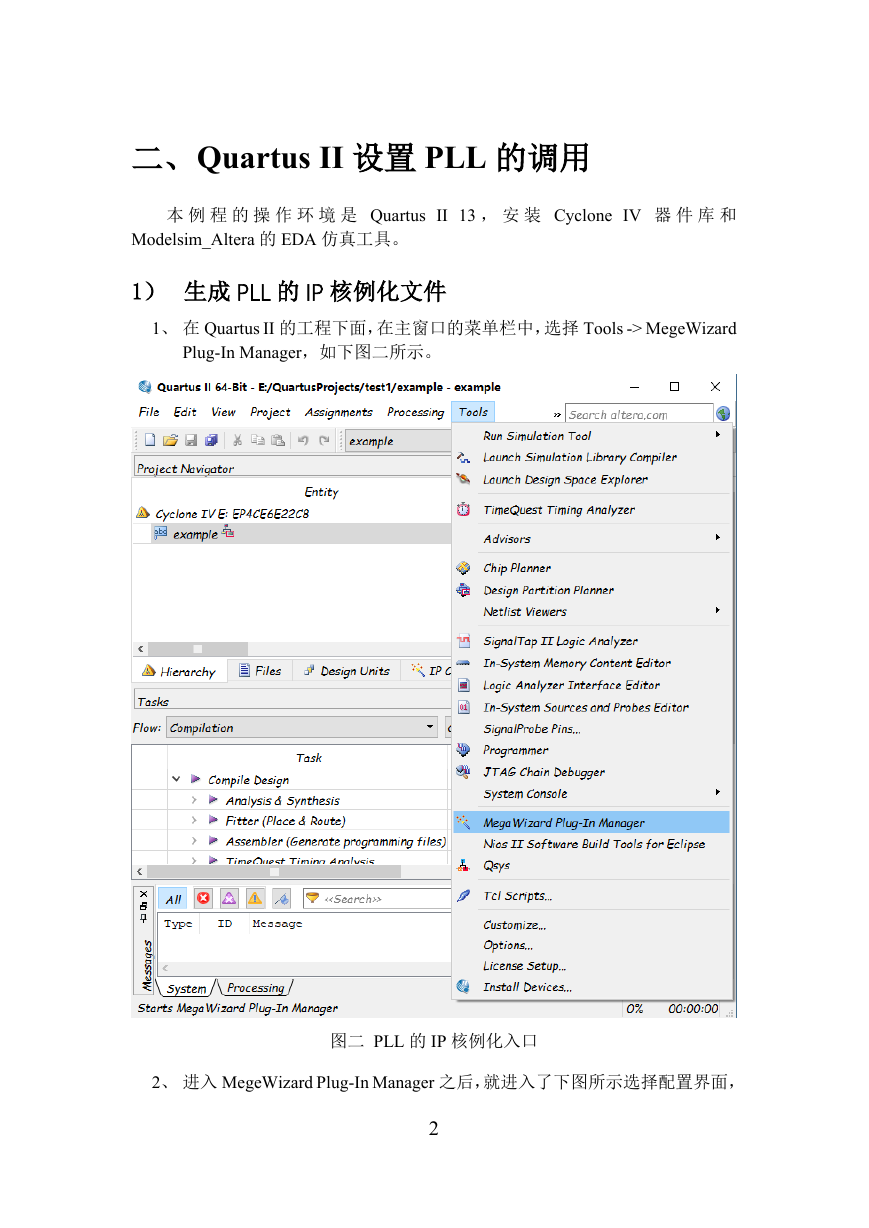

1) 生成 PLL 的 IP 核例化文件

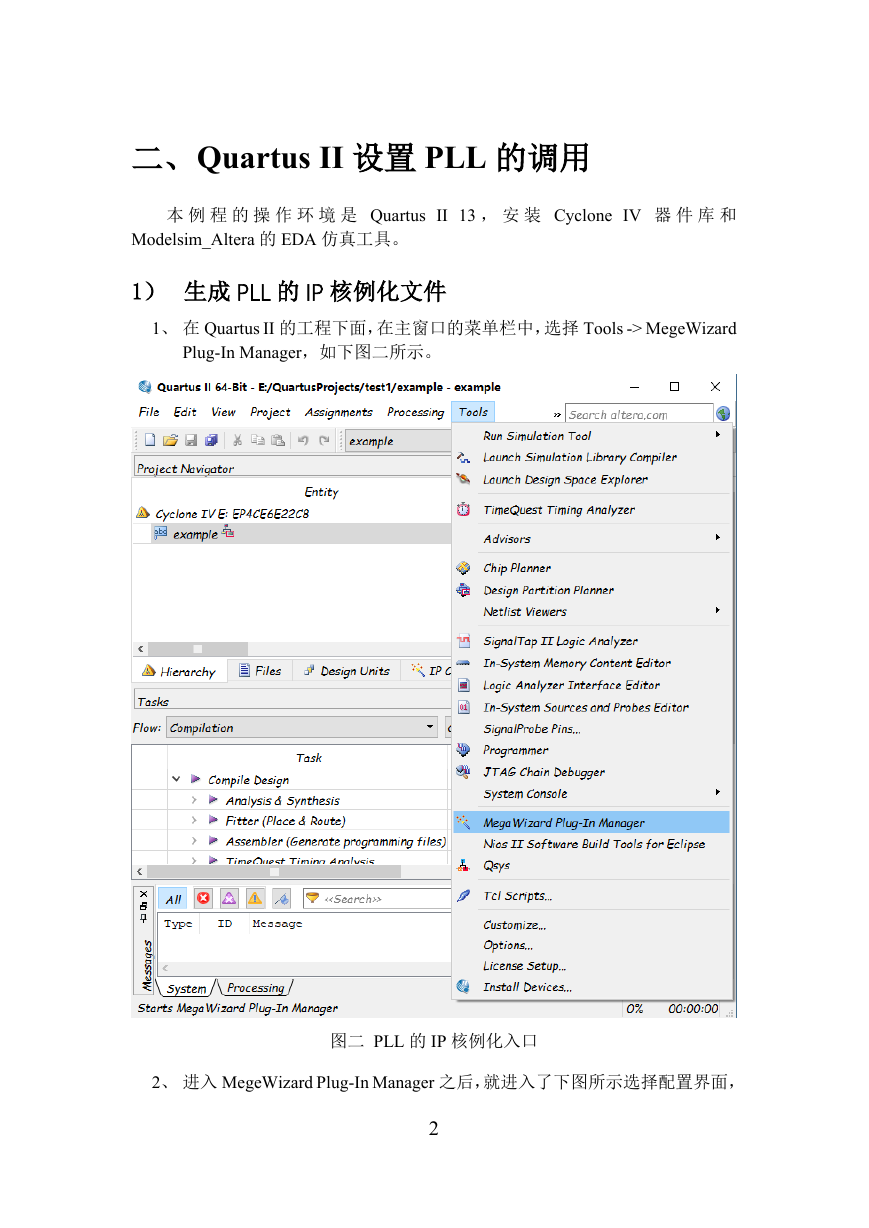

1、 在 Quartus II 的工程下面,在主窗口的菜单栏中,选择 Tools -> MegeWizard

Plug-In Manager,如下图二所示。

图二 PLL 的 IP 核例化入口

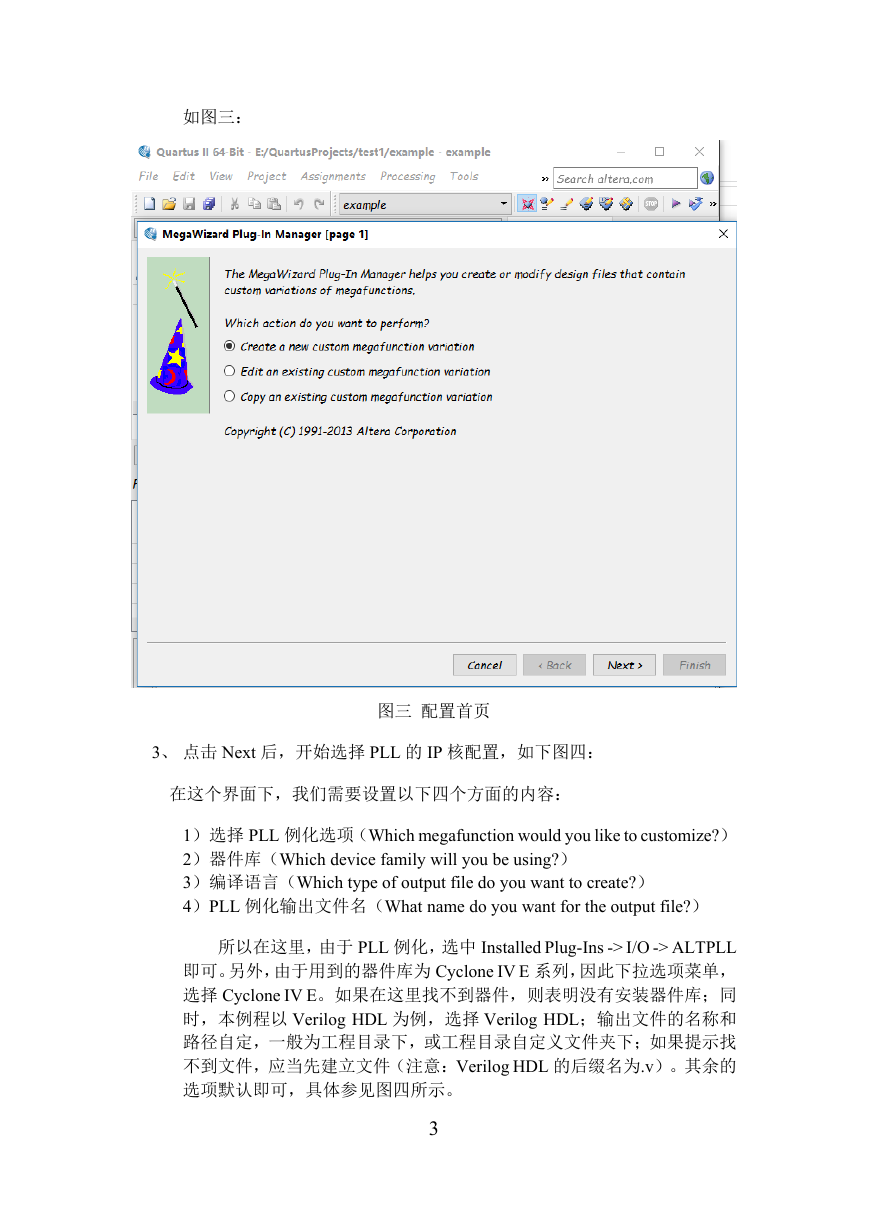

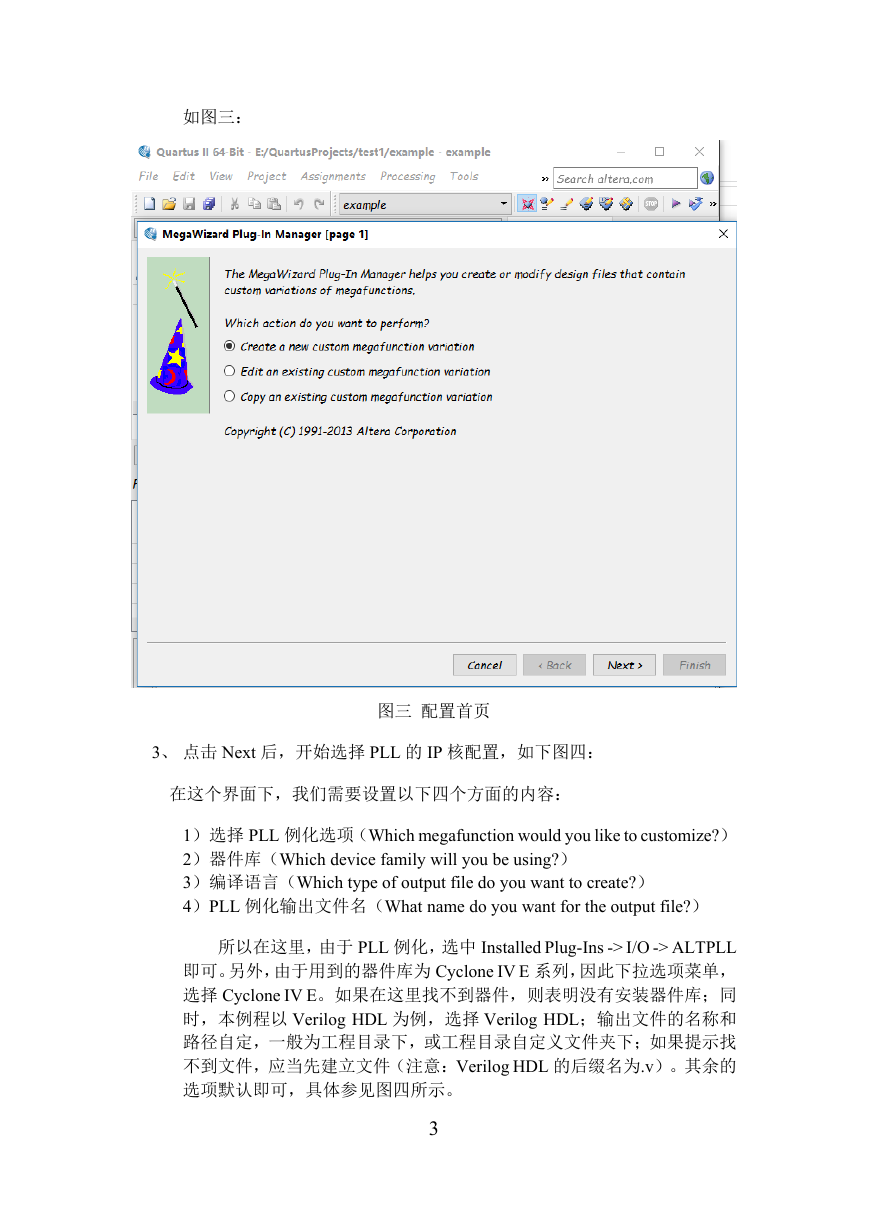

2、 进入 MegeWizard Plug-In Manager 之后,就进入了下图所示选择配置界面,

2

�

如图三:

图三 配置首页

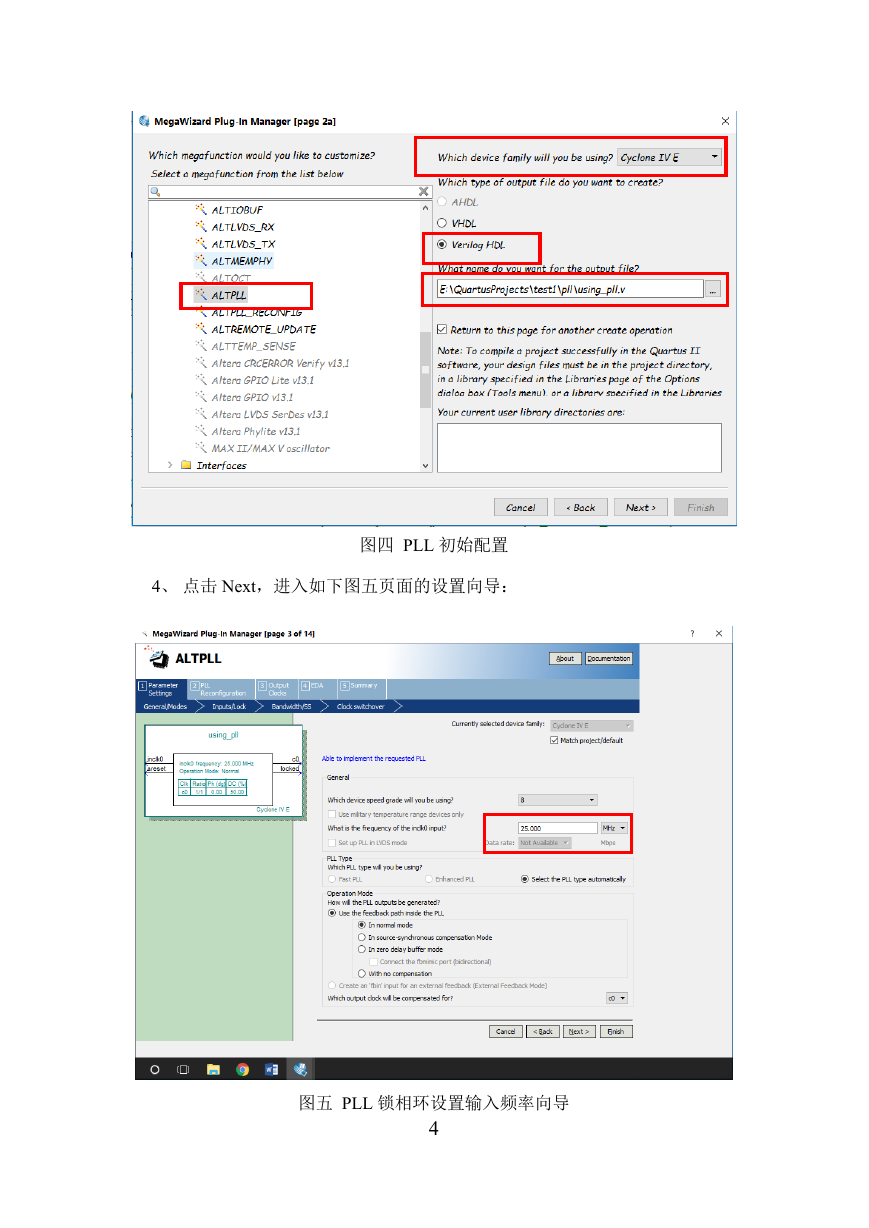

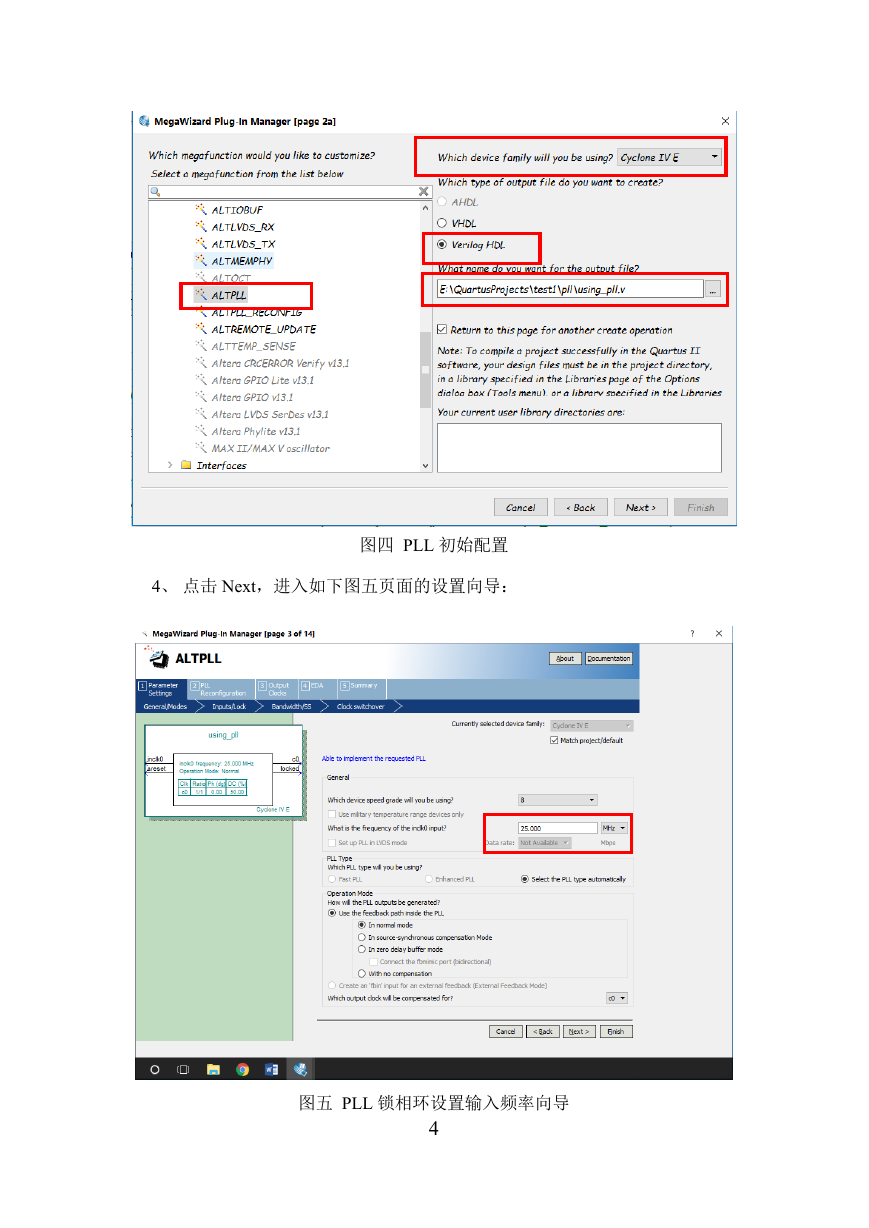

3、 点击 Next 后,开始选择 PLL 的 IP 核配置,如下图四:

在这个界面下,我们需要设置以下四个方面的内容:

1)选择 PLL 例化选项(Which megafunction would you like to customize?)

2)器件库(Which device family will you be using?)

3)编译语言(Which type of output file do you want to create?)

4)PLL 例化输出文件名(What name do you want for the output file?)

所以在这里,由于 PLL 例化,选中 Installed Plug-Ins -> I/O -> ALTPLL

即可。另外,由于用到的器件库为 Cyclone IV E 系列,因此下拉选项菜单,

选择 Cyclone IV E。如果在这里找不到器件,则表明没有安装器件库;同

时,本例程以 Verilog HDL 为例,选择 Verilog HDL;输出文件的名称和

路径自定,一般为工程目录下,或工程目录自定义文件夹下;如果提示找

不到文件,应当先建立文件(注意:Verilog HDL 的后缀名为.v)。其余的

选项默认即可,具体参见图四所示。

3

�

图四 PLL 初始配置

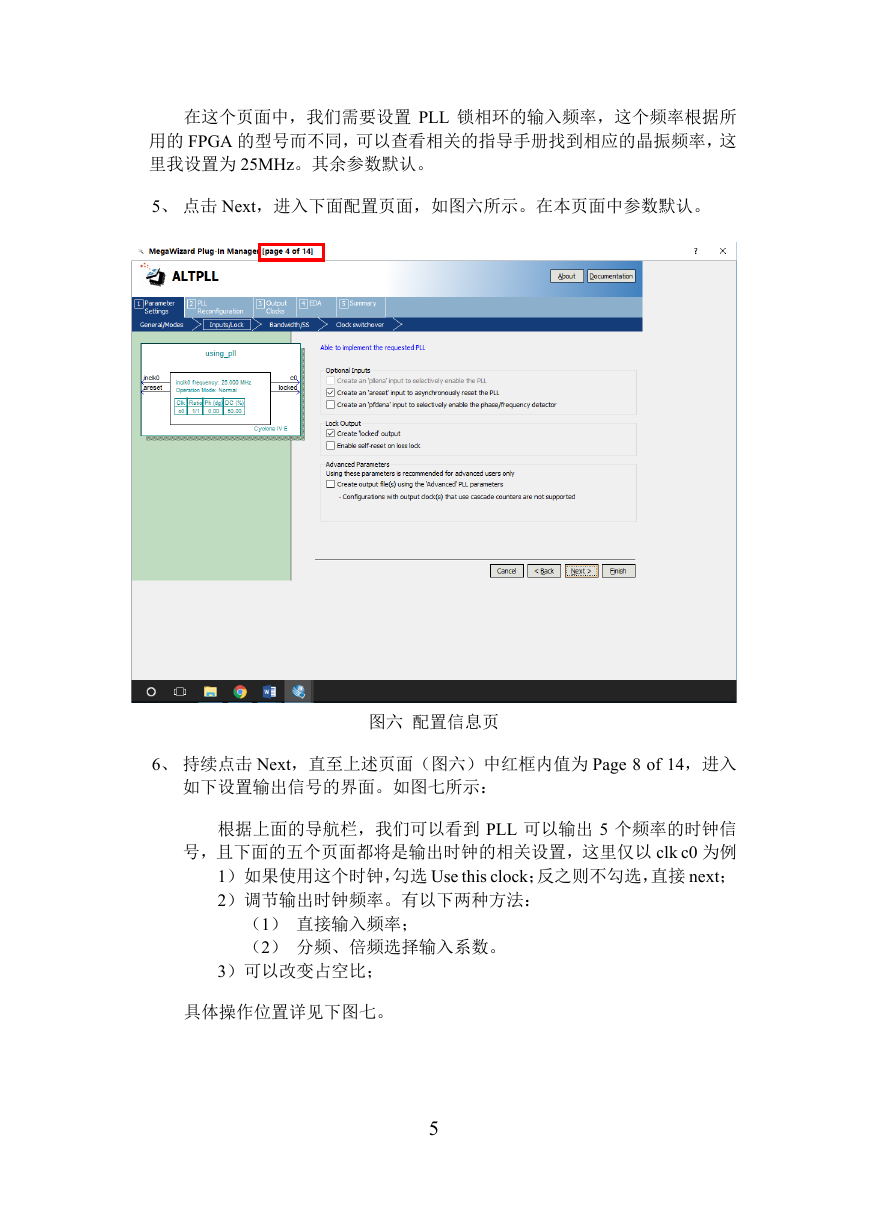

4、 点击 Next,进入如下图五页面的设置向导:

图五 PLL 锁相环设置输入频率向导

4

�

在这个页面中,我们需要设置 PLL 锁相环的输入频率,这个频率根据所

用的 FPGA 的型号而不同,可以查看相关的指导手册找到相应的晶振频率,这

里我设置为 25MHz。其余参数默认。

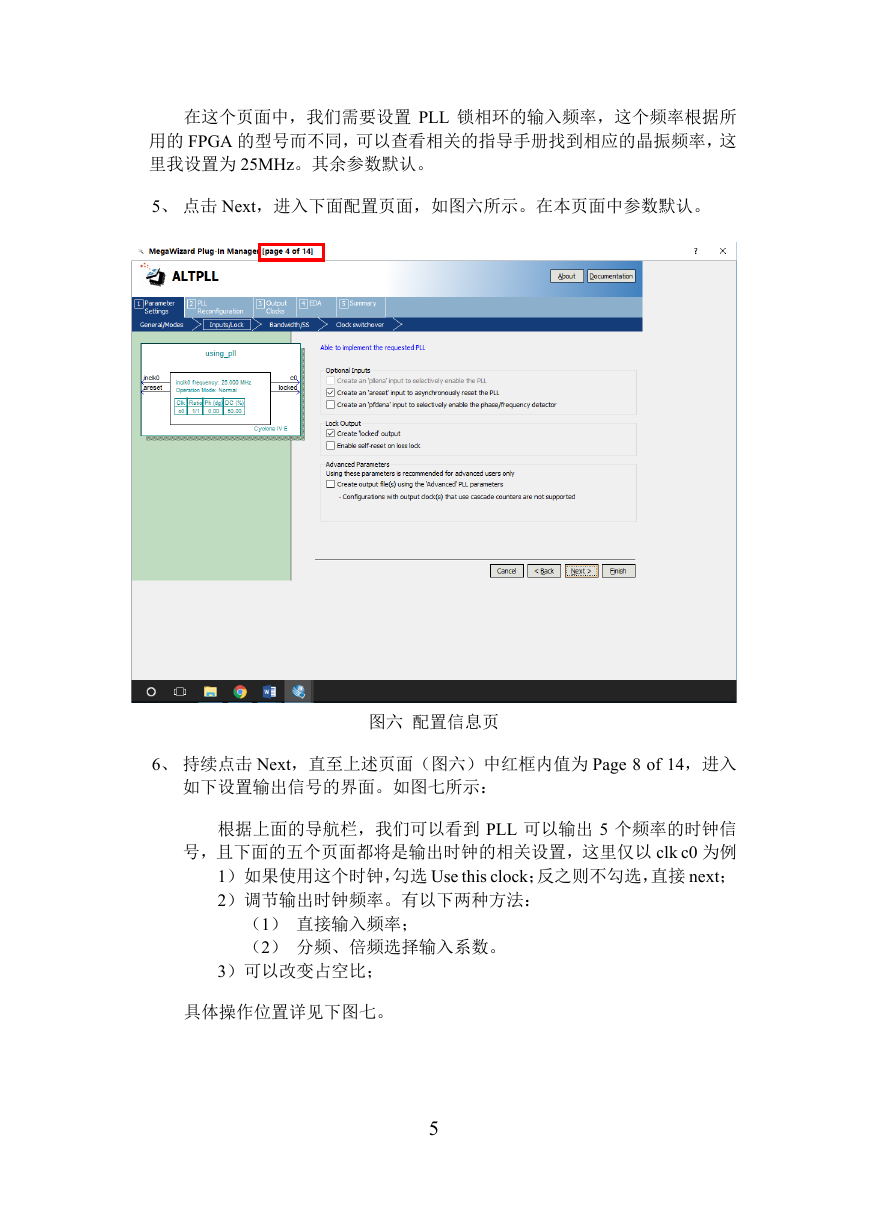

5、 点击 Next,进入下面配置页面,如图六所示。在本页面中参数默认。

图六 配置信息页

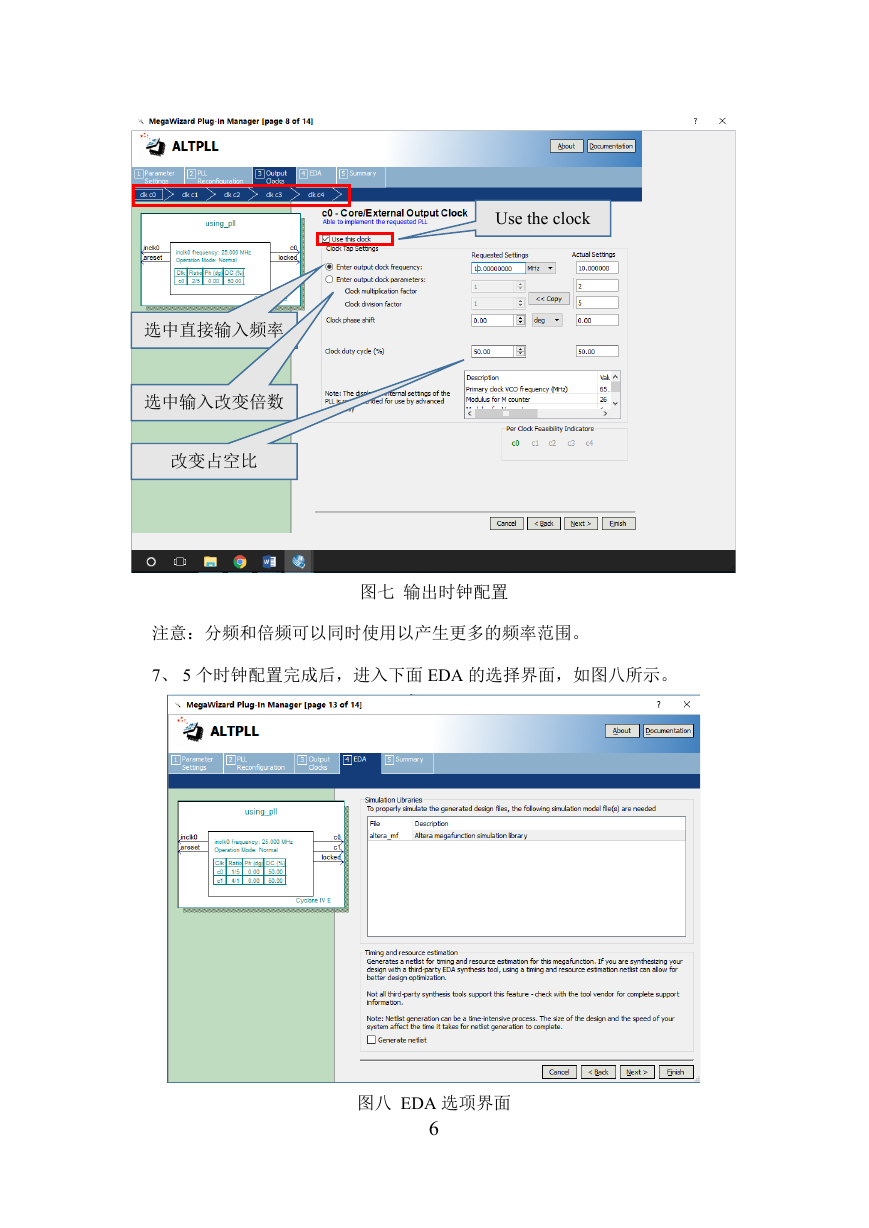

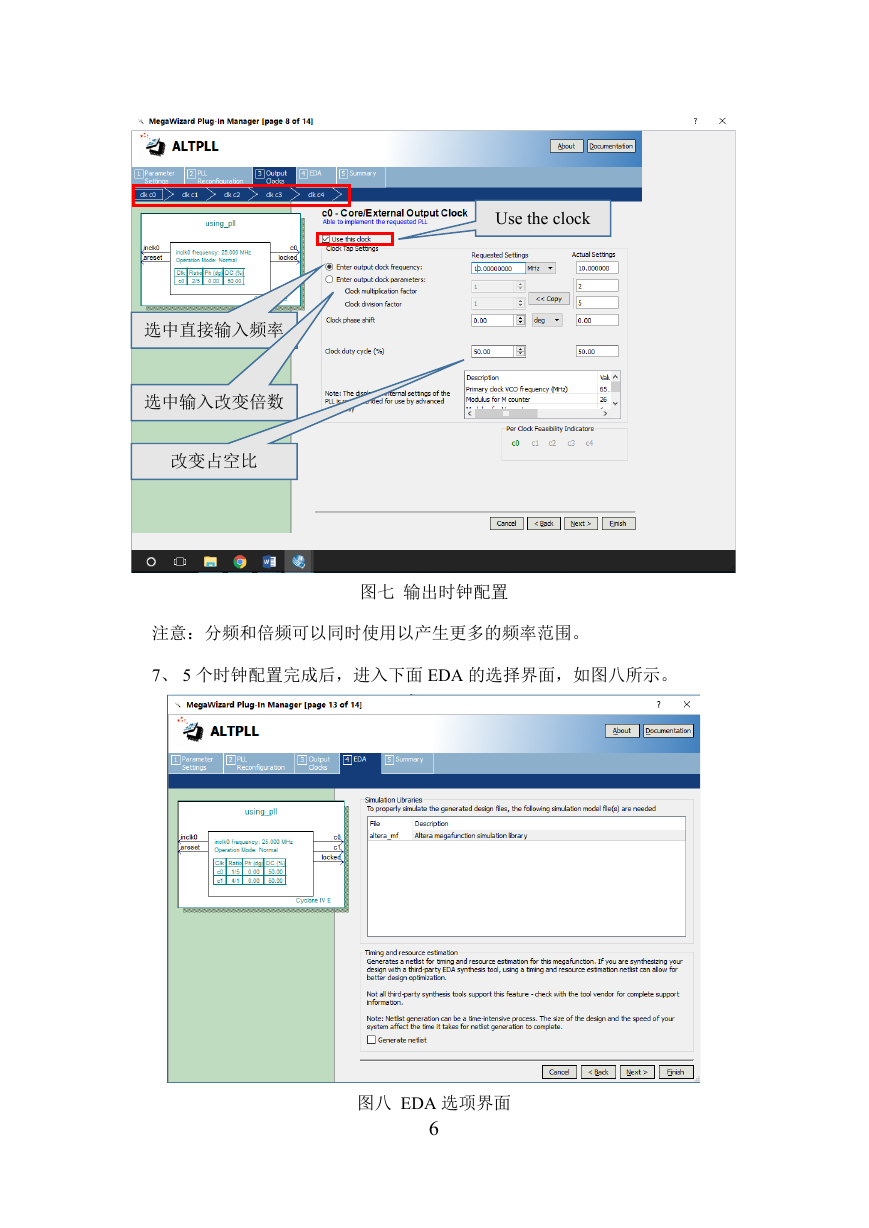

6、 持续点击 Next,直至上述页面(图六)中红框内值为 Page 8 of 14,进入

如下设置输出信号的界面。如图七所示:

根据上面的导航栏,我们可以看到 PLL 可以输出 5 个频率的时钟信

号,且下面的五个页面都将是输出时钟的相关设置,这里仅以 clk c0 为例

1)如果使用这个时钟,勾选 Use this clock;反之则不勾选,直接 next;

2)调节输出时钟频率。有以下两种方法:

(1) 直接输入频率;

(2) 分频、倍频选择输入系数。

3)可以改变占空比;

具体操作位置详见下图七。

5

�

Use the clock

选中直接输入频率

选中输入改变倍数

改变占空比

图七 输出时钟配置

注意:分频和倍频可以同时使用以产生更多的频率范围。

7、 5 个时钟配置完成后,进入下面 EDA 的选择界面,如图八所示。

图八 EDA 选项界面

6

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc