总第 46 卷 第 522 期

2009 年 第 06 期

电测与仪表

Electrical Measurement &Instrumentation

Vol.46 No.522

Jun. 2009

基于 FPGA 的随机等效采样模块设计

金星,黄伟

(中国地质大学 机电学院,武汉 430074)

摘要:随着电子技术的不断发展,各种仪表对高频模拟信号处理能力的要求越来越高。针对目前高速率数模转

换芯片的需求与实际的芯片制造工艺及其成本之间的矛盾,本文介绍了随机等效采样的原理,并利用 FPGA 的

内部资源和自下而上的设计方法,实现了实时采样速率 50M、等效采样速率 1.6G 的模块。该模块包括采样触发

模块、采样时钟产生模块、短时间测量模块、采样数据暂存模块,并给出了通用兼容的接口。该设计的各个子模

块以及顶层模块通过仿真验证,整个模块能够集成到各种信号采集系统中,具有一定的参考价值。

关键词:FPGA;随机等效采样;锁相环;模数转换

中图分类号:TM923;TP274+.2

文章编号:1001-1390(2009)06-0017-04

文献标识码:B

The Design of Random Equivalent Sampling Module Based on FPGA

(Faculty of Mechanical & Electronic Information, China University of Geosciences, Wuhan 430074, China)

JIN Xing, HUANG Wei

Abstract:With the constant development of electronic technology, the capability of processing high frequency analog

signals has become increasingly important. According to the contradiction between the demand of high speed AD

convert chip and chip manufacture techniques and cost, this paper introduces the principle of random equivalent

sampling. A module has been designed based on the interior resource in Field Programmable Gate Arrays. Its real

time sampling is up to 50Msps and equivalent sampling is up to 1.6Gsps. This module which has common and

compatible interface includes sampling trigger module, sampling clock generation module, little time measurement

module and sampling data temporarily storage module. Each sub-module and the top module have been validated

through the simulation. This solution is useful in various signal acquisition system.

Key words:FPGA,random equivalent sampling,phase-locked loop,analog digit convert(ADC)

0 引 言

随着数字化技术的迅速发展,对高频信号的采集

逐渐增多,由于受现有元器件的限制,低速的模数转

换器很难对高频信号实时采集,而取而代之的是欠采

样技术[1],它利用信号的周期性,以增加采集时间为代

价,降低对高速采样电路的压力,通过重组恢复原始

信号,可以实现周期信号或者重复信号的数字化。

1 等效采样的原理

早期的等效采样采用的是顺序等效时间采样。其

基本原理就是:每一次触发启动一次采样,得到一个

采样值,这个值对应着信号在一个周期内某一点的幅

度值。在多次采样之后,把采样得到的一组数据进行

重组,从而再现原信号波形。顺序等效时间采样的缺

点是仅能在触发点后采样,因而具有一定的局限性。

为了克服顺序等效时间采样的缺点,目前最常用

的等效采样方法是随机等效采样,其原理如图 1 所

示。随机等效采样实际上是以触发点为时间参考基准

对周期快变信号进行采样、存储和重构的技术。随机

等效采样的关键在于精确测量触发点与下一个采样

时钟间的时间间隔,以及通过等效采样算法确定各次

采样数据在信号重建的位置[2]。在随机等效采样的方

式下,首先让 ADC 在最高转换率下连续工作,等触发

信号到来时,通过一个门检测电路获取从触发信号到

触发后 ADC 的第一个采样时钟的时间差。这个时间

差表明了触发后的初始数据采样时刻。以这个时间差

作为起点,随后而来的每次采样,对应的时间位置构

成了一个递增序列,这个序列的间隔由 ADC 的采样

速率决定[3]。因此,完成一轮采样之后,就可以得到一

17-

-

�

总第 46 卷 第 522 期

2009 年 第 06 期

电测与仪表

Electrical Measurement &Instrumentation

Vol.46 No.522

Jun. 2009

组数据。这组数据在存储器中的位置就由这次采样数

据对应的时间序列决定。经过多轮的随机采样,得到

多组采样数据序列,在重复输入周期性波形的前提

下,就可以用这多组采样数据序列重建出信号波形,

每轮采样的起始时刻是不确定的,前一轮采样的起始

点可能在后一轮采样起始点的后面。因此,为了存储

器中按顺序存储波形,就必须对每轮采样得到的数据

序列进行重新分配,按照一定的算法写入存储器的对

应地址空间[4]。

�

�

�

�

�

�

�

�

�

�

�

�

�

�

�

�

�

�

�

3 等效采样模块中子模块的实现方法

3.1 短时间测量的方法及原理

该方法主要是利用了游标卡尺的原理,同样也借

助 FPGA 内部的锁相环来实现。主要的原理图如图 3。

系统时钟和采样时钟就好像游标卡尺上的两个刻度,

系统时钟就相当于主尺,采样时钟就相当于标尺。不过

在这里不是对长度的测量而是对时间的测量。

����

����

图 1 等效采样原理

Fig.1 Equivalent sampling module principle diagram

对于等效采样模块的实现,不仅要实现其逻辑功

������

��

�

�

�

2 基于 FPGA 的随机等效采样模块整体结构

��������� �

��

��

������

��

�������������

�� �

��

����

��

���������

����������������

������

���������������

���������

Altera 公司的 cyclone I 系列中的 EP1C6Q240C6

内部带有 2 个锁相环,本设计用其中一个锁相环来完

成采样时钟和系统时钟的频率关系的功能[5]。当系统

进入等效采样时,采样时钟始终保持一个固定的频率

(50MHz)。当输入信号满足触发条件时,触发信号立刻

驱动触发振荡器起振,利用监控器检测触发振荡器产

出触发事件到与下一个采样时钟的时间间隔,从而计

算出触发点与第一个采样点之间的短时间间隔[6]。

3.2 短时间测量的FPGA实现

能的完整性,还需考虑到采样数据的进一步处理,设

计其与 SOPC 系统兼容的接口。因此,等效采样模块

的内部结构如图 2 所示。

生的时钟是否和采样时钟同相位,同时利用计数器对

这个两个时钟进行计数。当相位检测模块检测到振荡

时钟和采样时钟同相位时,根据计数器的计数值推算

��

? �

Δ

图 3 短时间 T 测量原理

Fig.3 Principle of short time T measurement

在 FPGA 中,使用其内部的 PLL 宏模块。通过设

置输入时钟为 50MHz,输出时钟端选择 c0 为内部时

钟网络输出,输入与输出的频率关系设置为 31/30,

输出时钟频率为 51.66667MHz,即为采样频率。根据

上面介绍的游标卡尺的原理,当采样的外部触发信

号为高电平时,采样时钟开始有效,其与系统时钟之

间的相位差可以通过对系统时钟记数,系统时钟在

经过 0~31 个时钟后必定与采样时钟出现等相位点,

通过检测系统时钟与采样时钟的等相位点,等相位时

停止记数,可以知道第一个采样点相对于触发时刻的

时间,其计算公式为:

T=(20/31)·(N-1 )

(1)

式中 N 为触发开始点到等相位点所经过的时间计数

器的数值。按此设计的最小精度为 0.667ns。因此短时

间的测量只需要将触发信号有效后对系统时钟计数,

当采样时钟和系统时钟同相位时停止计数,得到的计

数器的值就是上面公式中的 N 的值,就可以计算出

图 2 等效采样模块的内部结构

Fig.2 Equivalent sampling module structure diagram

对于该等效采样模块,通过 FPGA 内部逻辑资源

实现等效采样功能,其对于 SOPC 系统相当于一个

SRAM,当外部触发采样完成一次完整的信号采集过

程后,也就是 RAM2 寄存器满后通过 R/S 控制信号让

系统读取 RAM2 内部暂存的数据,同时屏蔽外部触

发信号,当系统读取数据完成后,让采集模块重新开

始采集数据,对于该模块的访问就如同访问 SRAM

一样简单。SOPC 系统读取数据后再实现数据转存至

其他大容量存储设备中或者是在 LCD 外设中显示信

号的波形。

18-

-

�

总第 46 卷 第 522 期

2009 年 第 06 期

电测与仪表

Electrical Measurement &Instrumentation

Vol.46 No.522

Jun. 2009

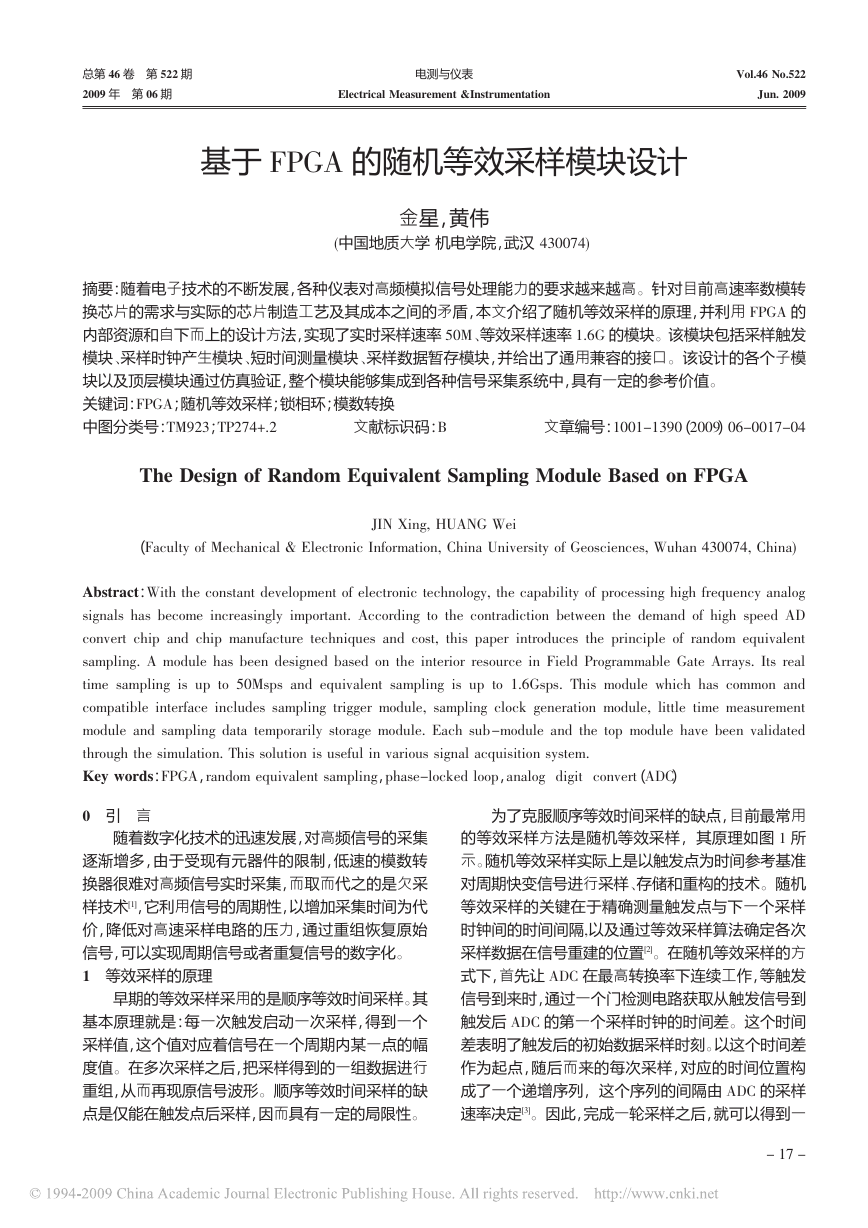

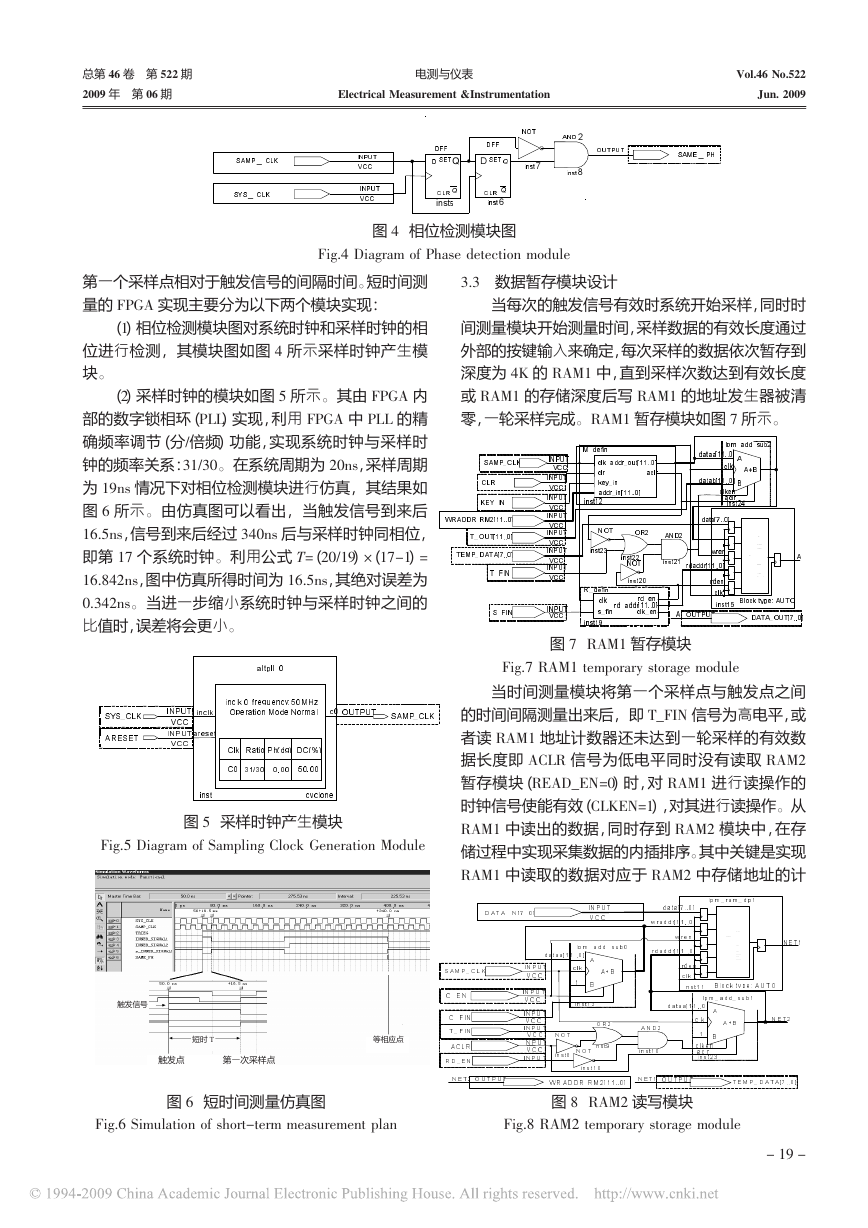

图 4 相位检测模块图

Fig.4 Diagram of Phase detection module

当每次的触发信号有效时系统开始采样,同时时

间测量模块开始测量时间,采样数据的有效长度通过

第一个采样点相对于触发信号的间隔时间。短时间测

量的 FPGA 实现主要分为以下两个模块实现:

(1)相位检测模块图对系统时钟和采样时钟的相

位进行检测,其模块图如图 4 所示采样时钟产生模

块。

�

���������������� ��

����������������������

���������

���������

�����������Q�������

���������

���������

����

�������������������

������������ �����

��������������������������������������

��� � ������������������������������������������ !�"#$%%��"#�������$%%��&'(�������$���)�*"#�%� #�%�$%%������������ #���"#)(�+���"#)(����� ���"#)(��"#)(����� , -,��������

��

��"#)(�.,�&��/(!0 /1/ ����02�$%%�)'3�"#)(�4

�% *"#"#)(����% *"#"#)(�5��� #$������%$($$�������%$($3�������%$($������6� #�%$%%���������% #��� ������� � ����������

����������� �

��

��

����

�������

������

���

�

����������������

���� ��

�

�������� !!"#"$!%& !!'()")�������"'��$!%&�����!�*+,*��-����-���./�012!/31(����!�

��������� �

����

����������

��

����������� ��

��� � �����������

�����������

��� � �����������

����������� ����������������

������

� � ��

���� ���

������

�����

!!

"#$����

!!

"#$����

% �

!��&'"(����)*+,(-�.,/, ���&'"(�0��&'"(�0&'"(1���&'"(2��� ���&'"(��&'"(�����*�+.' *�%*�+! ( ���

��! ( ��

��3% !!%���

��3%.'%! !!%���

��%!.'*�+! ( ���

��*�+����������������������

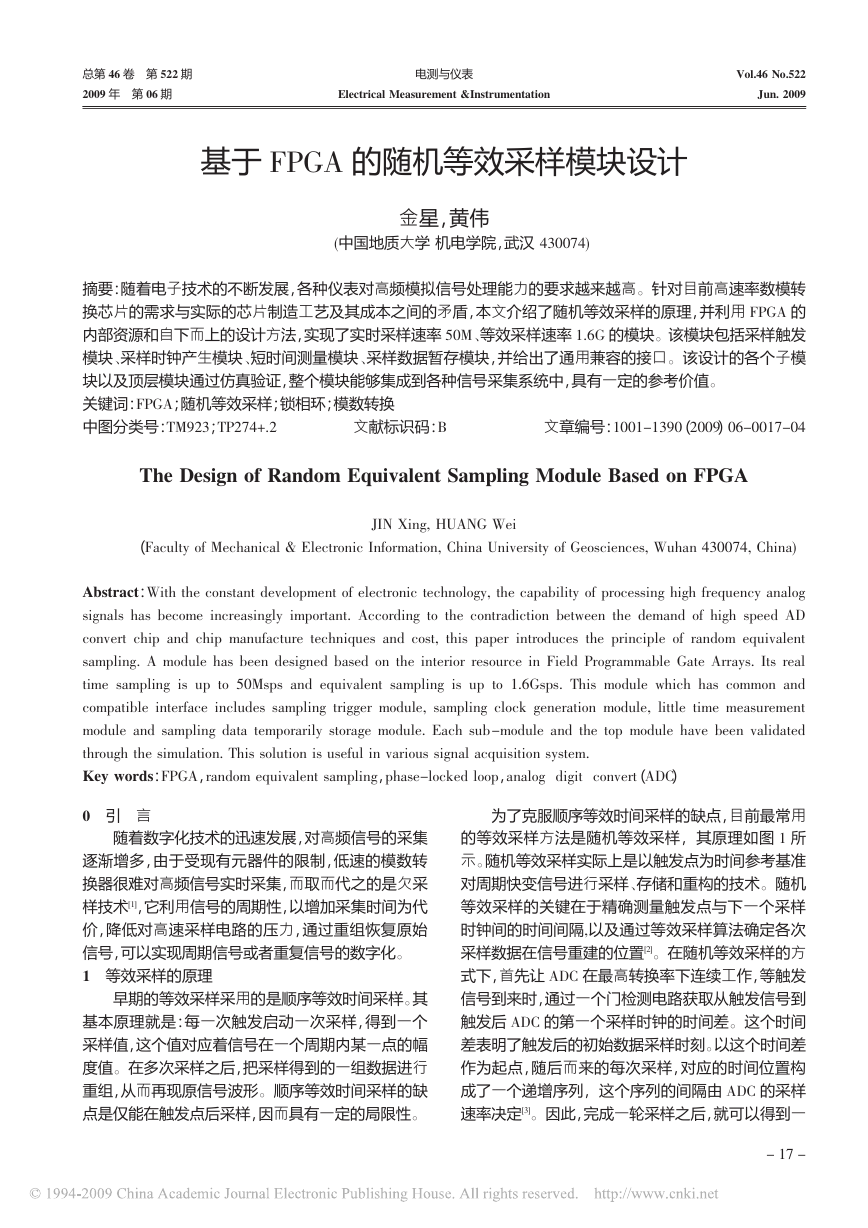

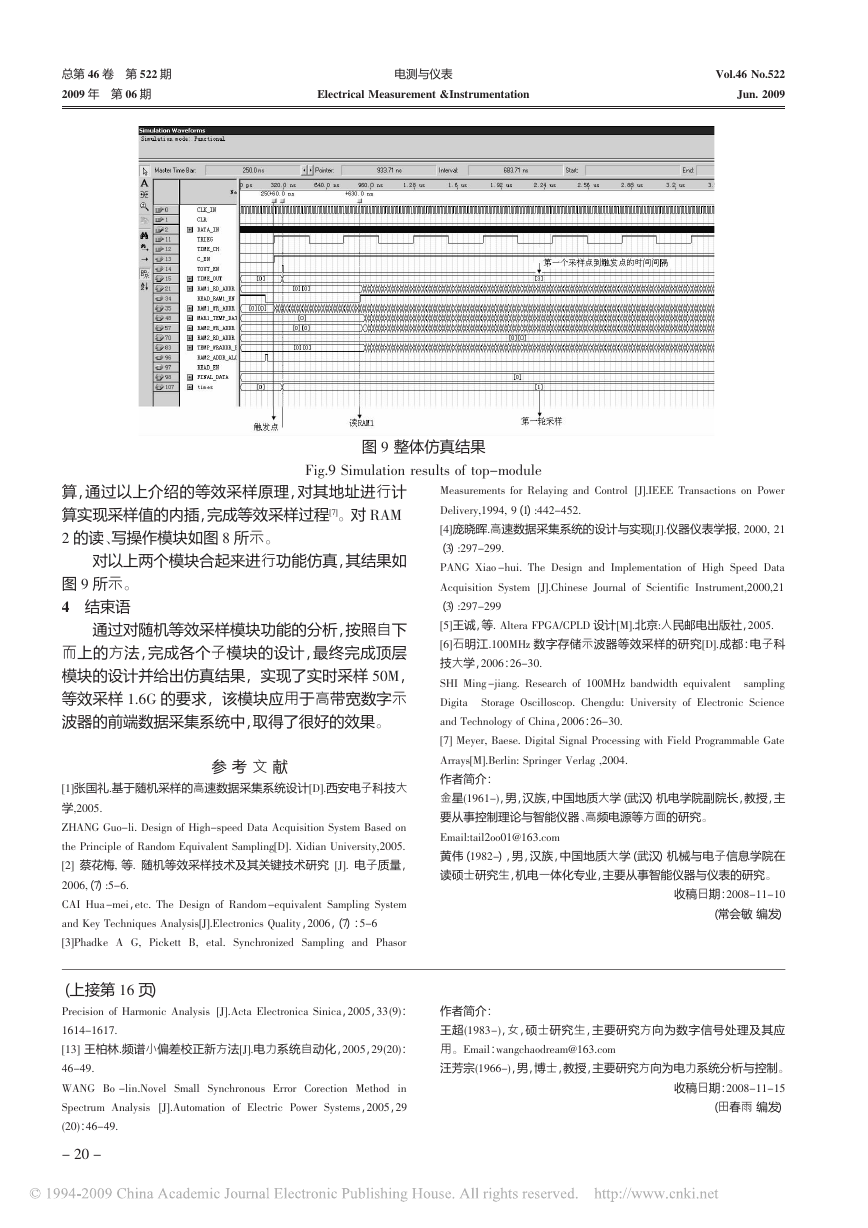

当时间测量模块将第一个采样点与触发点之间

的时间间隔测量出来后,即 T_FIN 信号为高电平,或

者读 RAM1 地址计数器还未达到一轮采样的有效数

据长度即 ACLR 信号为低电平同时没有读取 RAM2

暂存模块(READ_EN=0)时,对 RAM1 进行读操作的

时钟信号使能有效(CLKEN=1),对其进行读操作。从

RAM1 中读出的数据,同时存到 RAM2 模块中,在存

储过程中实现采集数据的内插排序。其中关键是实现

RAM1 中读取的数据对应于 RAM2 中存储地址的计

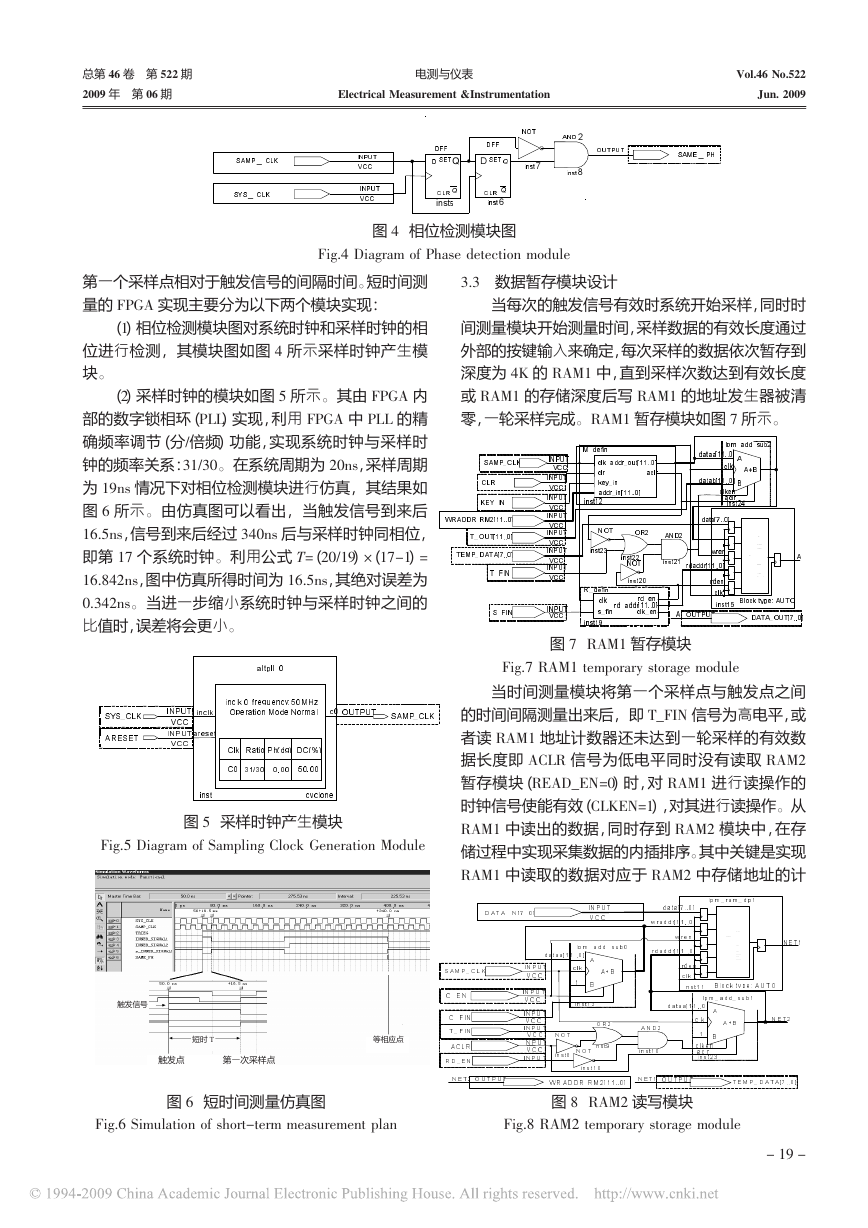

(2)采样时钟的模块如图 5 所示。其由 FPGA 内

部的数字锁相环(PLL)实现,利用 FPGA 中 PLL 的精

确频率调节(分/倍频)功能,实现系统时钟与采样时

钟的频率关系:31/30。在系统周期为 20ns,采样周期

为 19ns 情况下对相位检测模块进行仿真,其结果如

图 6 所示。由仿真图可以看出,当触发信号到来后

16.5ns,信号到来后经过 340ns 后与采样时钟同相位,

即第 17 个系统时钟。利用公式 T=(20/19)×(17-1)=

16.842ns,图中仿真所得时间为 16.5ns,其绝对误差为

0.342ns。当进一步缩小系统时钟与采样时钟之间的

比值时,误差将会更小。

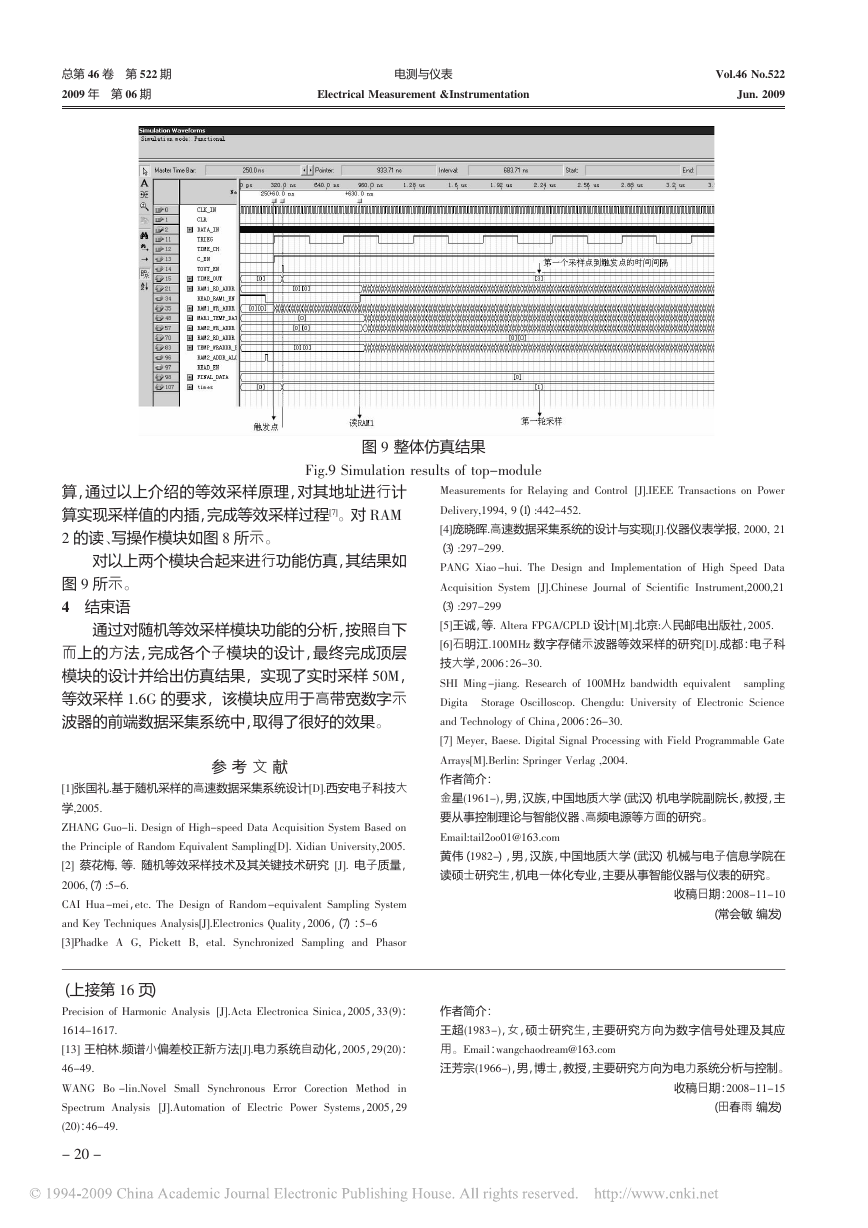

外部的按键输入来确定,每次采样的数据依次暂存到

深度为 4K 的 RAM1 中,直到采样次数达到有效长度

或 RAM1 的存储深度后写 RAM1 的地址发生器被清

零,一轮采样完成。RAM1 暂存模块如图 7 所示。

短时 T

等相应点

触发点

第一次采样点

图 7 RAM1 暂存模块

Fig.7 RAM1 temporary storage module

Fig.5 Diagram of Sampling Clock Generation Module

图 5 采样时钟产生模块

3.3 数据暂存模块设计

触发信号

图 6 短时间测量仿真图

图 8 RAM2 读写模块

Fig.6 Simulation of short-term measurement plan

Fig.8 RAM2 temporary storage module

19-

-

�

总第 46 卷 第 522 期

2009 年 第 06 期

电测与仪表

Electrical Measurement &Instrumentation

Vol.46 No.522

Jun. 2009

图 9 整体仿真结果

Fig.9 Simulation results of top-module

算,通过以上介绍的等效采样原理,对其地址进行计

算实现采样值的内插,完成等效采样过程[7]。对 RAM

2 的读、写操作模块如图 8 所示。

对以上两个模块合起来进行功能仿真,其结果如

图 9 所示。

4 结束语

通过对随机等效采样模块功能的分析,按照自下

而上的方法,完成各个子模块的设计,最终完成顶层

模块的设计并给出仿真结果,实现了实时采样 50M,

等效采样 1.6G 的要求,该模块应用于高带宽数字示

波器的前端数据采集系统中,取得了很好的效果。

参 考 文 献

[1]张国礼.基于随机采样的高速数据采集系统设计[D].西安电子科技大

学,2005.

ZHANG Guo-li. Design of High-speed Data Acquisition System Based on

the Principle of Random Equivalent Sampling[D]. Xidian University,2005.

[2] 蔡花梅, 等. 随机等效采样技术及其关键技术研究 [J]. 电子质量,

2006,(7):5-6.

CAI Hua -mei,etc. The Design of Random -equivalent Sampling System

and Key Techniques Analysis[J].Electronics Quality,2006,(7):5-6

[3]Phadke A G, Pickett B, etal. Synchronized Sampling and Phasor

(上接第 16 页)

Precision of Harmonic Analysis [J].Acta Electronica Sinica,2005,33(9):

1614-1617.

[13] 王柏林.频谱小偏差校正新方法[J].电力系统自动化,2005,29(20):

46-49.

WANG Bo -lin.Novel Small Synchronous Error Corection Method in

Spectrum Analysis [J].Automation of Electric Power Systems,2005,29

(20):46-49.

20-

-

Measurements for Relaying and Control

Delivery,1994, 9(1):442-452.

[4]庞晓晖.高速数据采集系统的设计与实现[J].仪器仪表学报, 2000, 21

(3):297-299.

[J].IEEE Transactions on Power

PANG Xiao -hui. The Design and Implementation of High Speed Data

Acquisition System [J].Chinese Journal of Scientific Instrument,2000,21

(3):297-299

[5]王诚,等. Altera FPGA/CPLD 设计[M].北京:人民邮电出版社,2005.

[6]石明江.100MHz 数字存储示波器等效采样的研究[D].成都:电子科

技大学,2006:26-30.

SHI Ming -jiang. Research of 100MHz bandwidth equivalent

sampling

Storage Oscilloscop. Chengdu: University of Electronic Science

Digita

and Technology of China,2006:26-30.

[7] Meyer, Baese. Digital Signal Processing with Field Programmable Gate

Arrays[M].Berlin: Springer Verlag ,2004.

作者简介:

金星(1961-),男,汉族,中国地质大学(武汉)机电学院副院长,教授,主

要从事控制理论与智能仪器、高频电源等方面的研究。

Email:tail2oo01@163.com

黄伟(1982-),男,汉族,中国地质大学(武汉)机械与电子信息学院在

读硕士研究生,机电一体化专业,主要从事智能仪器与仪表的研究。

收稿日期:2008-11-10

(常会敏 编发)

作者简介:

王超(1983-),女,硕士研究生,主要研究方向为数字信号处理及其应

用。Email:wangchaodream@163.com

汪芳宗(1966-),男,博士,教授,主要研究方向为电力系统分析与控制。

收稿日期:2008-11-15

(田春雨 编发)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc