河北地质大学

信息工程学院

计算机组成原理课程设计报告

题 目 基于 MIPS 单周期处理器的设计及仿真

姓 名

学 号

班 号

指导老师

成 绩

左瑞欣

2018 年 1 月 12 日

1

�

2

�

目

录

1. 课程设计目的······························································································ 1

2. 课设的任务································································································· 1

3. 设计方案 ···································································································1

4.指令系统设计······························································································· 1

4.1 指令格式·································································································· 1

4.2 指令编码·································································································· 2

4.3 验证程序段及其机器指令·············································································3

5.数据通路的设计······························································································ 4

6.控制器的设计······························································································· 4

7. 模型机的调试仿真························································································ 19

8. 课程设计回顾总结 ····················································································· 25

9. 参考文献 ································································································· 26

3

�

1. 课程设计目的

用所学的计算机组成原理知识,通过课程设计,设计,实验,仿真,调试出一台能

执行几条指令的模型机,从而掌握计算机组成部件如寄存器,寄存器组,运算器,存储

器等的工作原理及设计方法,进而形成数据通路。通过控制器连接成整机,建立整机的

概念,深入理解指令在 CPU 中的执行过程,同时,提高设计能力和实践操作技能,为从

事计算机研制与设计打下基础。

2. 课设的任务

设计一个多周期的处理器,采用 32 位的 MIPS 指令格式,存储器按字节编址,大端

方式存放数据,数据要求按字边界对齐。

设计模型机的数据通路及控制器。在对模型机中的各功能部件进行仿真分析和功能

验证的基础上,实现模型机的整机系统,能够正确地执行存放在主存中的程序。

本课题内容要实现的功能是((const1-M[a]+const2)&const3)|const4->M[b]

3. 设计方案选择

本次实验设计单周期 CPU,基于 Quartus 开发平台,使用 VHDL 硬件描述语言,采用

模块化的设计思想,底层元件用 VHDL 进行描述,部件中设计了 32 个 32 位寄存器组,1

个 RAM,1 个 ROM,1 个 32 位的选择器,1 个 5 位的选择器,1 个位扩展器,1 个控制器,

指令地址寄存器,指令加法器以及运算器,在指令地址寄存器中取出指令地址,在 ROM

里取出指令并进行指令译码,通过层层部件,在控制器控制的情况下,完成取指,译码,

地址计算,访问存储器,数据写回。顶层模型机用原理图实现。设计步骤如下:

(1)指令系统的设计

(2)根据指令的功能给出所需的功能部件,将功能部件连接构成数据通路。

(3)依据指令执行过程中数据的流动过程,画出指令流程图。

(4)依据指令的流程图,画出状态转换图。

(5)依据状态转换图,使用状态机实现控制器的设计。

(6)使用要求的测试程序,验证模型机的功能

4. 指令系统设计

4.1 指令格式设计

1

�

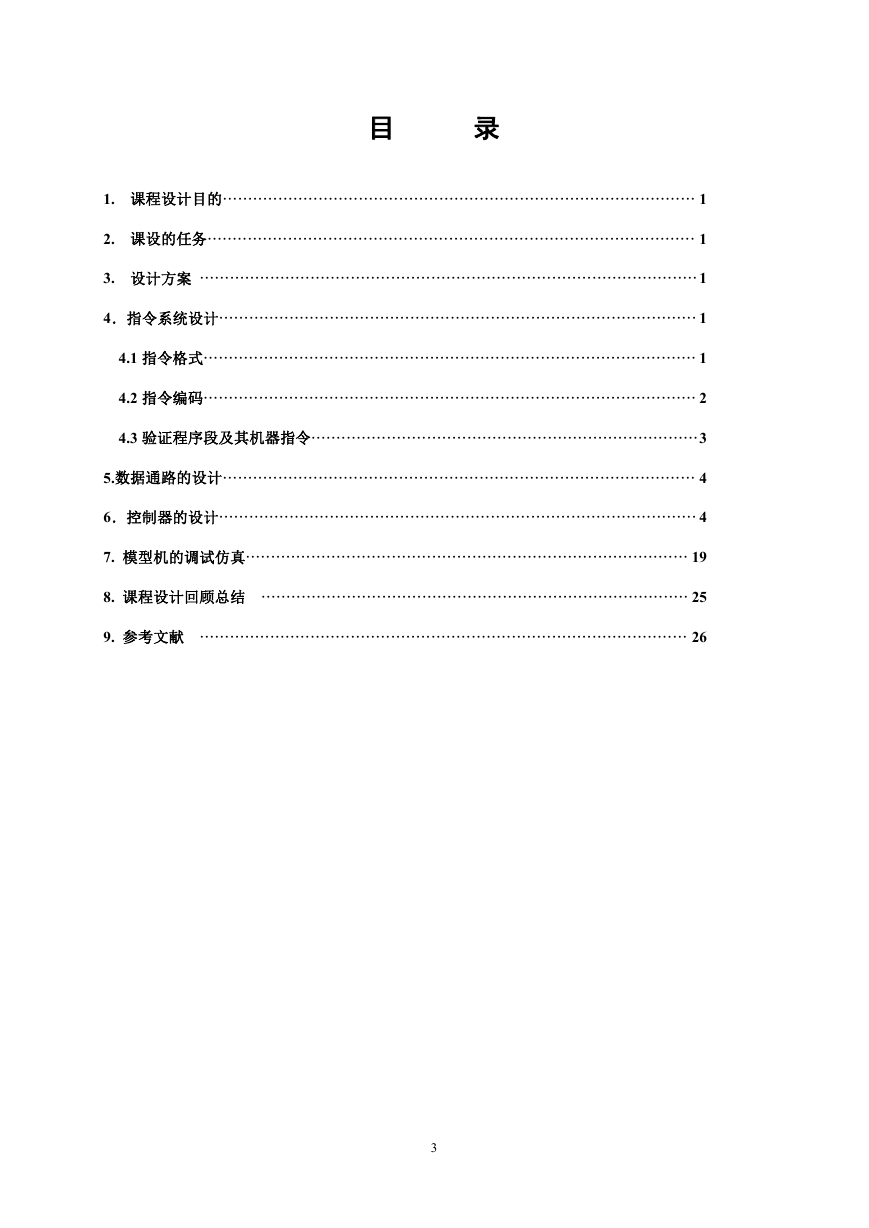

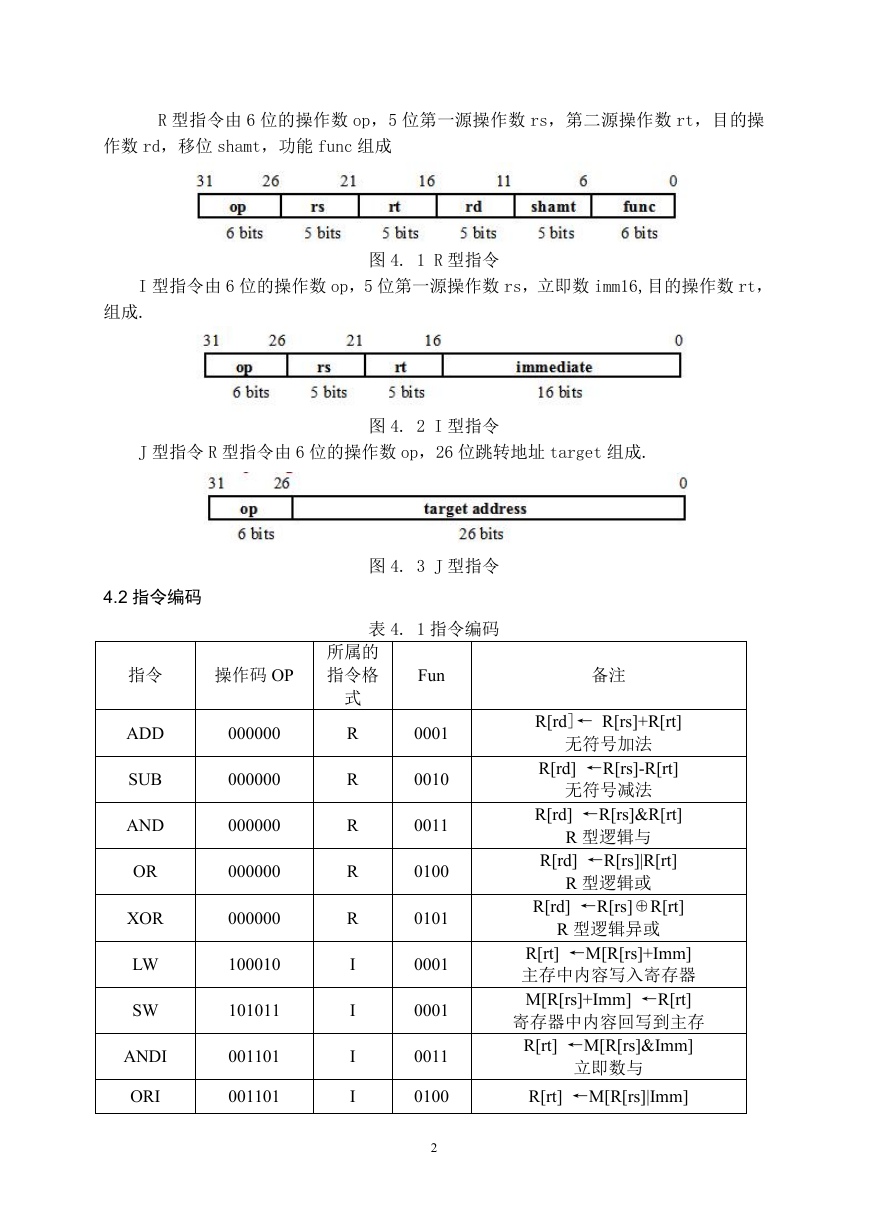

R 型指令由 6 位的操作数 op,5 位第一源操作数 rs,第二源操作数 rt,目的操

作数 rd,移位 shamt,功能 func 组成

I 型指令由 6 位的操作数 op,5 位第一源操作数 rs,立即数 imm16,目的操作数 rt,

图 4. 1 R 型指令

组成.

J 型指令 R 型指令由 6 位的操作数 op,26 位跳转地址 target 组成.

图 4. 2 I 型指令

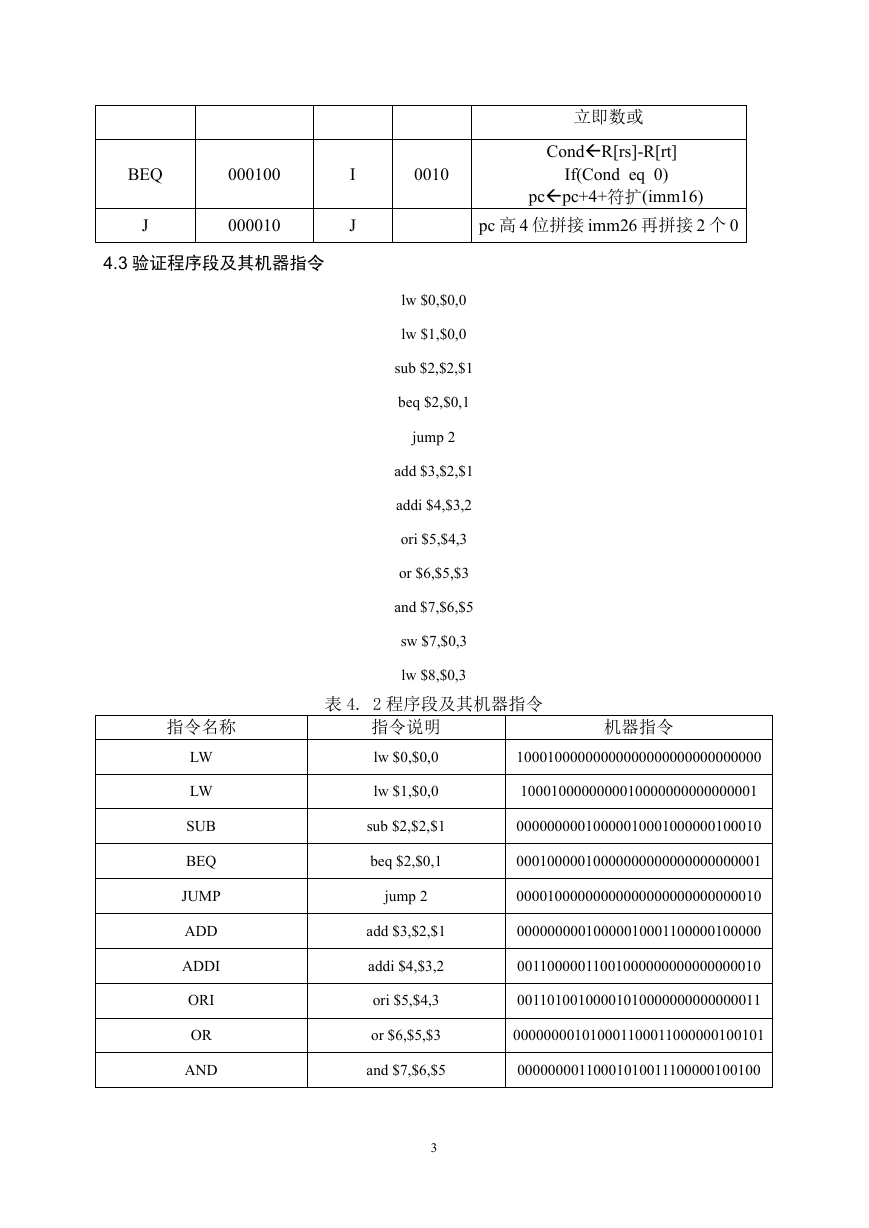

4.2 指令编码

图 4. 3 J 型指令

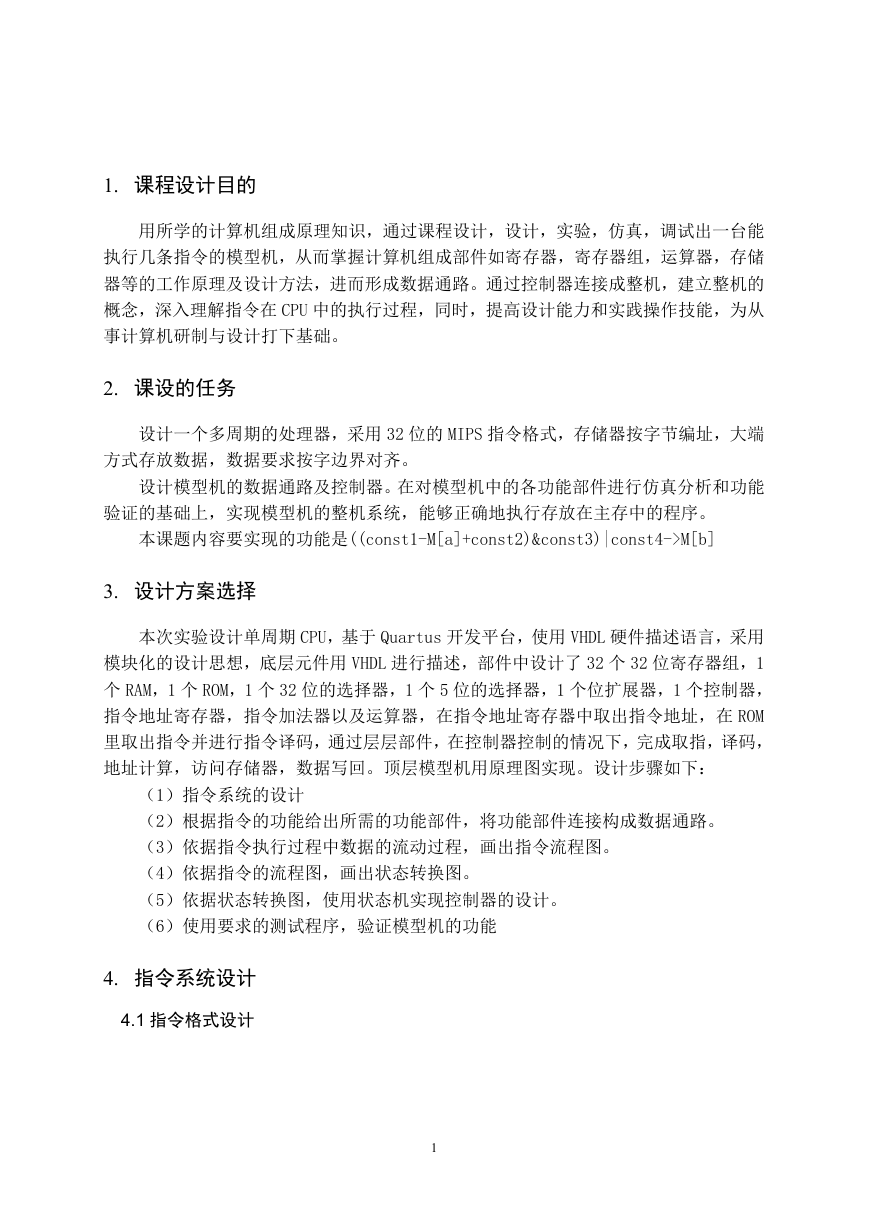

表 4. 1 指令编码

指令

操作码 OP

所属的

指令格

式

ADD

SUB

AND

OR

XOR

LW

SW

ANDI

ORI

000000

000000

000000

000000

000000

100010

101011

001101

001101

R

R

R

R

R

I

I

I

I

Fun

0001

0010

0011

0100

0101

0001

0001

0011

0100

2

备注

R[rd]← R[rs]+R[rt]

无符号加法

R[rd] ←R[rs]-R[rt]

无符号减法

R[rd] ←R[rs]&R[rt]

R 型逻辑与

R[rd] ←R[rs]|R[rt]

R 型逻辑或

R[rd] ←R[rs]⊕R[rt]

R 型逻辑异或

R[rt] ←M[R[rs]+Imm]

主存中内容写入寄存器

M[R[rs]+Imm] ←R[rt]

寄存器中内容回写到主存

R[rt] ←M[R[rs]&Imm]

立即数与

R[rt] ←M[R[rs]|Imm]

�

BEQ

J

000100

000010

I

J

0010

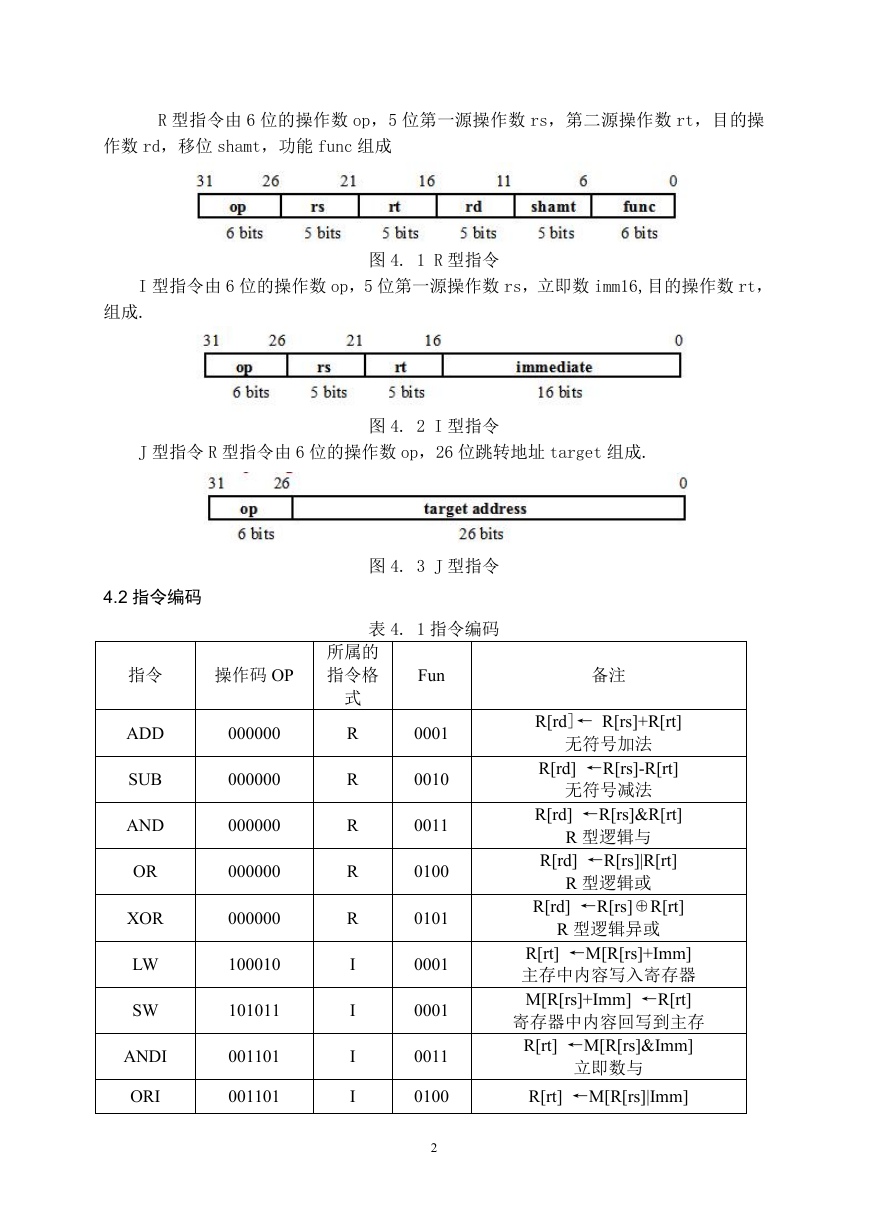

4.3 验证程序段及其机器指令

立即数或

CondR[rs]-R[rt]

If(Cond eq 0)

pcpc+4+符扩(imm16)

pc 高 4 位拼接 imm26 再拼接 2 个 0

lw $0,$0,0

lw $1,$0,0

sub $2,$2,$1

beq $2,$0,1

jump 2

add $3,$2,$1

addi $4,$3,2

ori $5,$4,3

or $6,$5,$3

and $7,$6,$5

sw $7,$0,3

lw $8,$0,3

指令名称

LW

LW

SUB

BEQ

JUMP

ADD

ADDI

ORI

OR

AND

表 4. 2 程序段及其机器指令

指令说明

lw $0,$0,0

lw $1,$0,0

sub $2,$2,$1

beq $2,$0,1

机器指令

10001000000000000000000000000000

1000100000000010000000000000001

00000000010000010001000000100010

00010000010000000000000000000001

jump 2

00001000000000000000000000000010

add $3,$2,$1

addi $4,$3,2

ori $5,$4,3

or $6,$5,$3

00000000010000010001100000100000

00110000011001000000000000000010

00110100100001010000000000000011

000000001010001100011000000100101

and $7,$6,$5

00000000110001010011100000100100

3

�

SW

LW

sw $7,$0,3

lw $8,$0,3

10101100000001110000000000000011

10001000000010000000000000000011

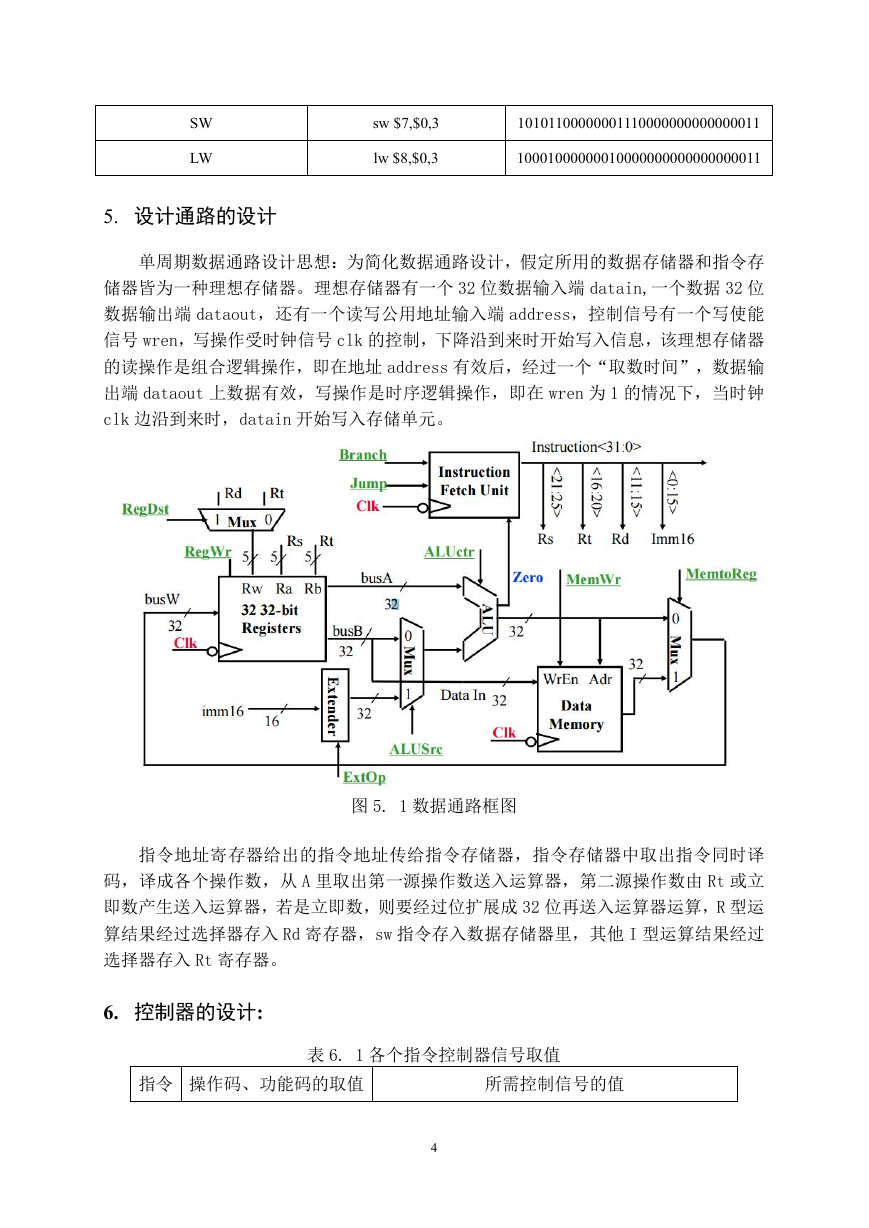

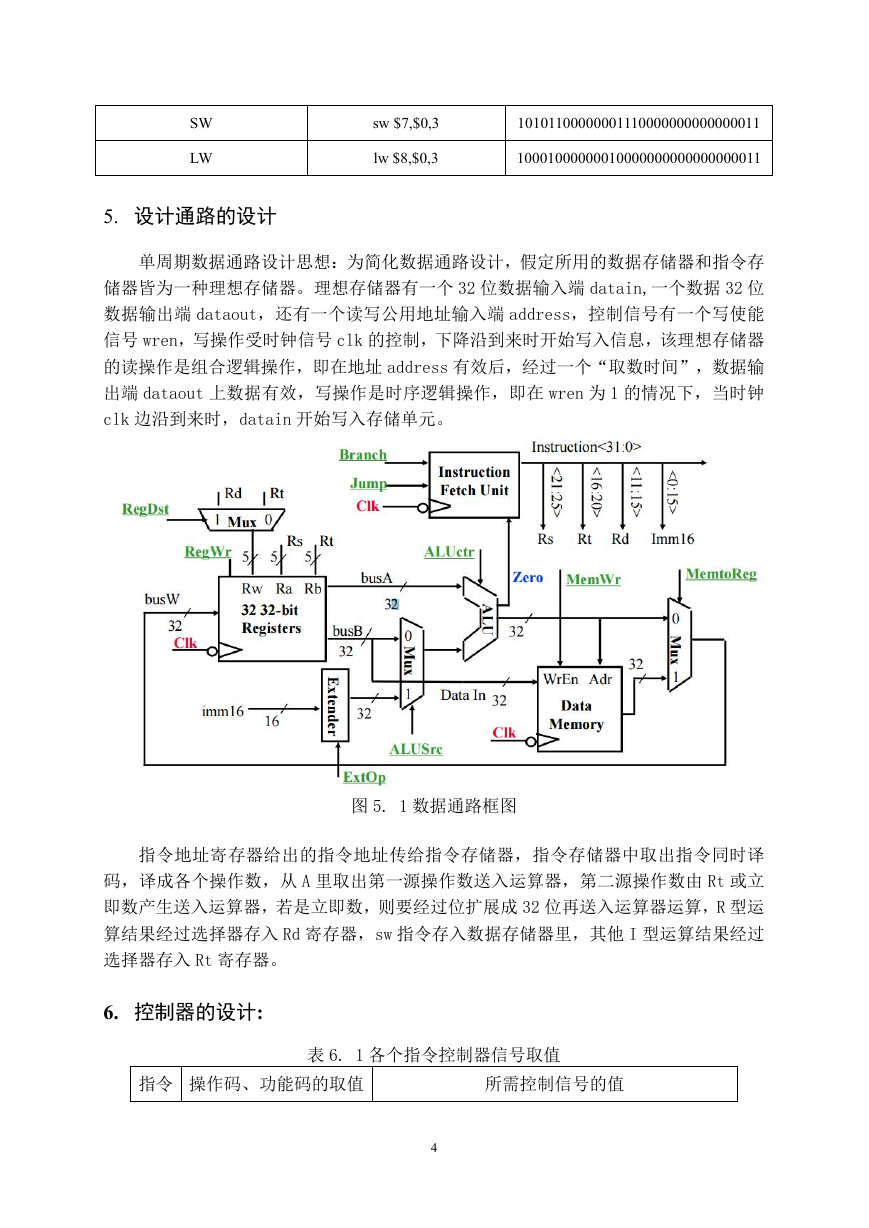

5. 设计通路的设计

单周期数据通路设计思想:为简化数据通路设计,假定所用的数据存储器和指令存

储器皆为一种理想存储器。理想存储器有一个 32 位数据输入端 datain,一个数据 32 位

数据输出端 dataout,还有一个读写公用地址输入端 address,控制信号有一个写使能

信号 wren,写操作受时钟信号 clk 的控制,下降沿到来时开始写入信息,该理想存储器

的读操作是组合逻辑操作,即在地址 address 有效后,经过一个“取数时间”,数据输

出端 dataout 上数据有效,写操作是时序逻辑操作,即在 wren 为 1 的情况下,当时钟

clk 边沿到来时,datain 开始写入存储单元。

图 5. 1 数据通路框图

指令地址寄存器给出的指令地址传给指令存储器,指令存储器中取出指令同时译

码,译成各个操作数,从 A 里取出第一源操作数送入运算器,第二源操作数由 Rt 或立

即数产生送入运算器,若是立即数,则要经过位扩展成 32 位再送入运算器运算,R 型运

算结果经过选择器存入 Rd 寄存器,sw 指令存入数据存储器里,其他 I 型运算结果经过

选择器存入 Rt 寄存器。

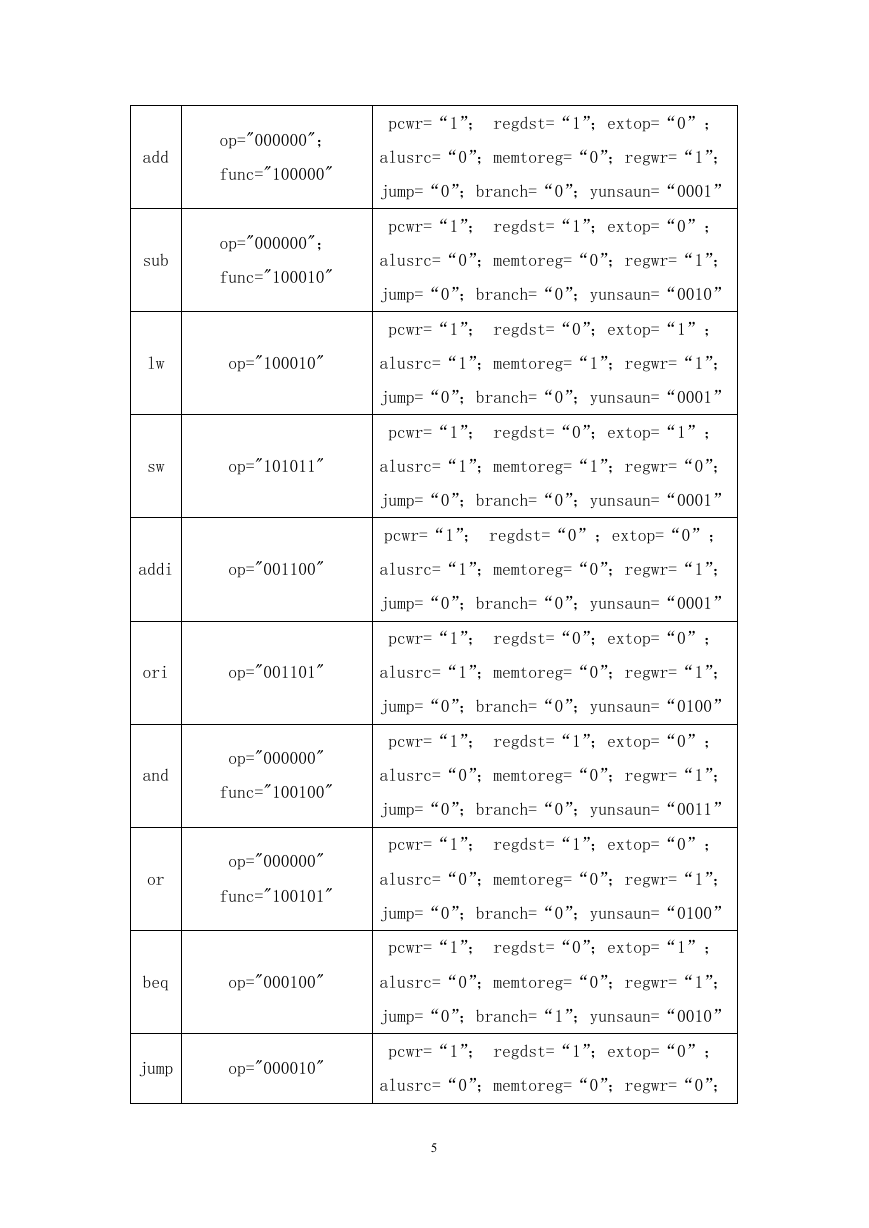

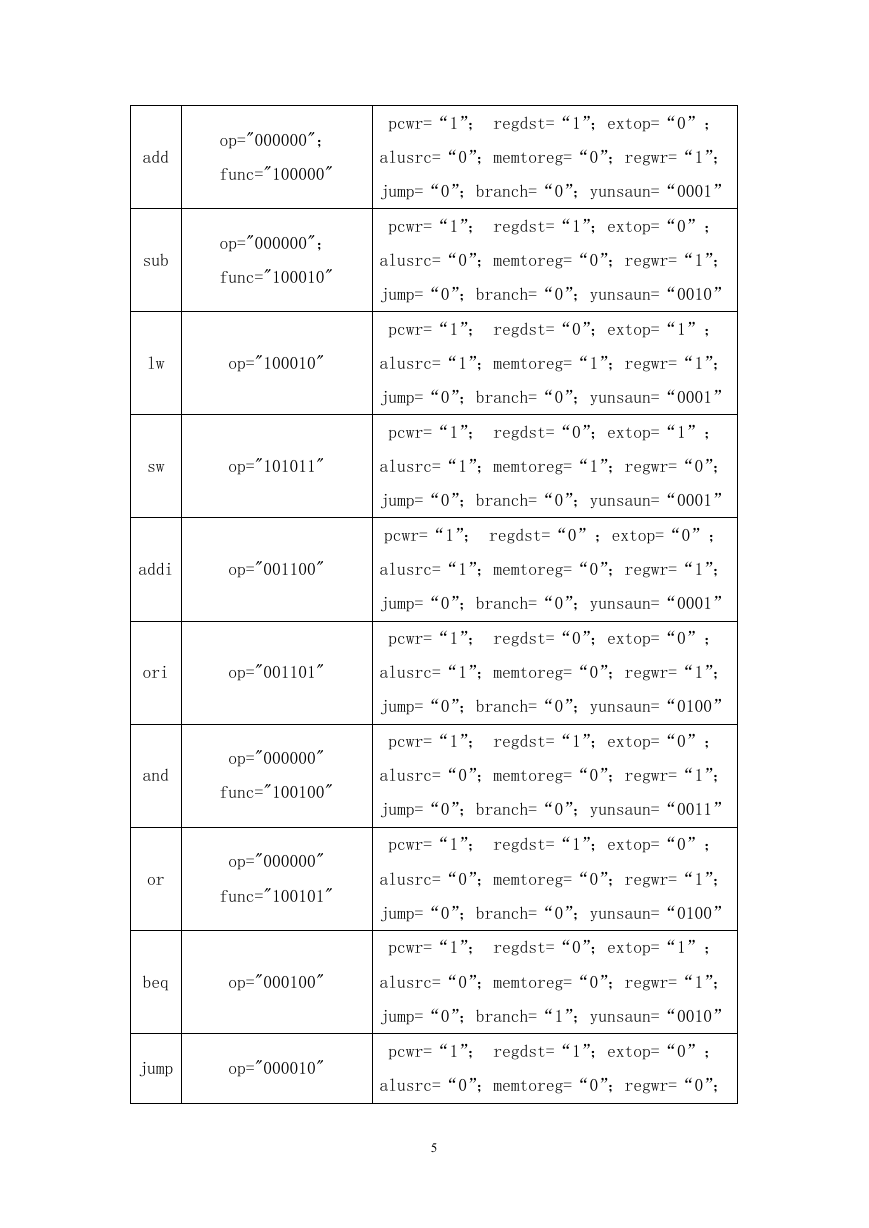

6. 控制器的设计:

表 6. 1 各个指令控制器信号取值

指令 操作码、功能码的取值

所需控制信号的值

4

�

add

sub

op="000000";

func="100000"

op="000000";

func="100010"

pcwr=“1”; regdst=“1”;extop=“0”;

alusrc=“0”;memtoreg=“0”;regwr=“1”;

jump=“0”;branch=“0”;yunsaun=“0001”

pcwr=“1”; regdst=“1”;extop=“0”;

alusrc=“0”;memtoreg=“0”;regwr=“1”;

jump=“0”;branch=“0”;yunsaun=“0010”

pcwr=“1”; regdst=“0”;extop=“1”;

lw

op="100010"

alusrc=“1”;memtoreg=“1”;regwr=“1”;

jump=“0”;branch=“0”;yunsaun=“0001”

pcwr=“1”; regdst=“0”;extop=“1”;

sw

op="101011"

alusrc=“1”;memtoreg=“1”;regwr=“0”;

jump=“0”;branch=“0”;yunsaun=“0001”

pcwr=“1”; regdst=“0”;extop=“0”;

addi

op="001100"

alusrc=“1”;memtoreg=“0”;regwr=“1”;

jump=“0”;branch=“0”;yunsaun=“0001”

pcwr=“1”; regdst=“0”;extop=“0”;

ori

op="001101"

alusrc=“1”;memtoreg=“0”;regwr=“1”;

and

or

op="000000"

func="100100"

op="000000"

func="100101"

jump=“0”;branch=“0”;yunsaun=“0100”

pcwr=“1”; regdst=“1”;extop=“0”;

alusrc=“0”;memtoreg=“0”;regwr=“1”;

jump=“0”;branch=“0”;yunsaun=“0011”

pcwr=“1”; regdst=“1”;extop=“0”;

alusrc=“0”;memtoreg=“0”;regwr=“1”;

jump=“0”;branch=“0”;yunsaun=“0100”

pcwr=“1”; regdst=“0”;extop=“1”;

beq

op="000100"

alusrc=“0”;memtoreg=“0”;regwr=“1”;

jump

op="000010"

jump=“0”;branch=“1”;yunsaun=“0010”

pcwr=“1”; regdst=“1”;extop=“0”;

alusrc=“0”;memtoreg=“0”;regwr=“0”;

5

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc