目录

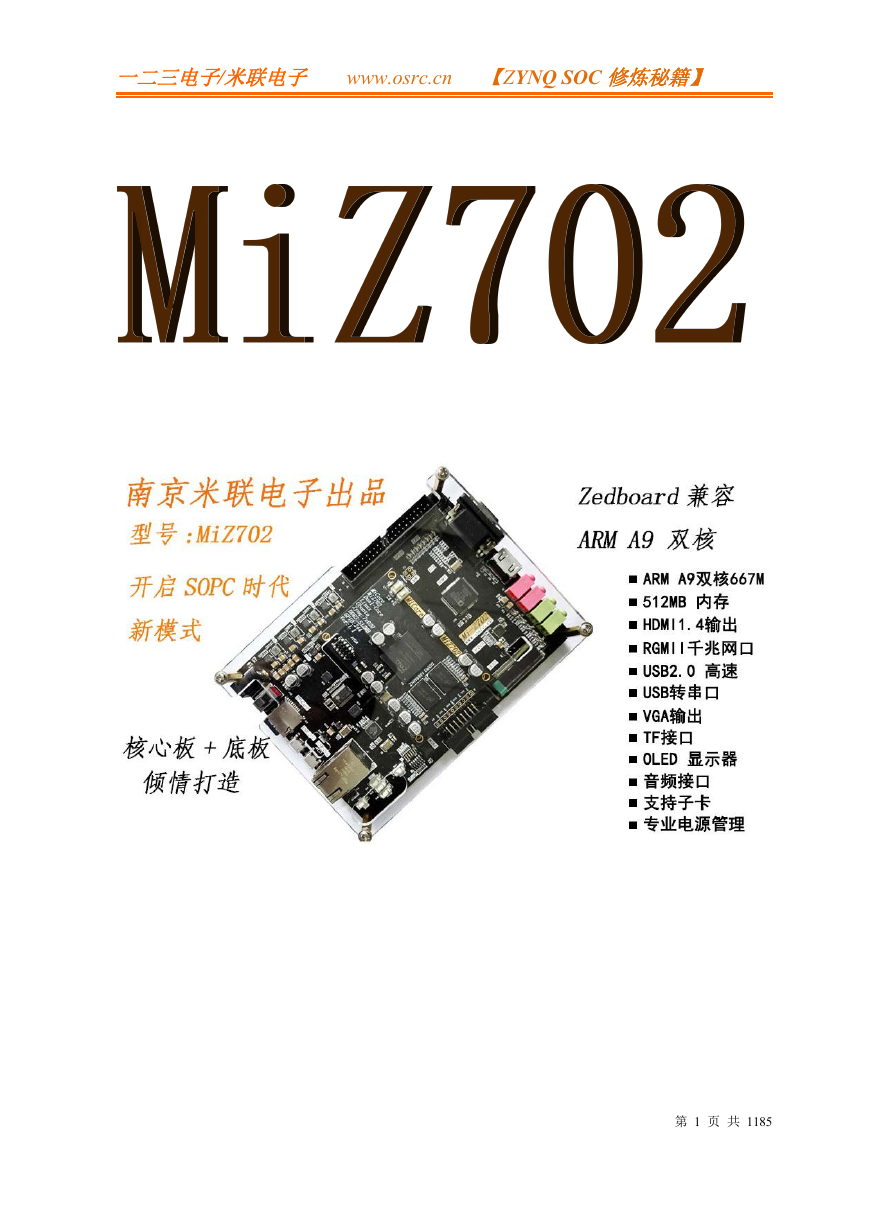

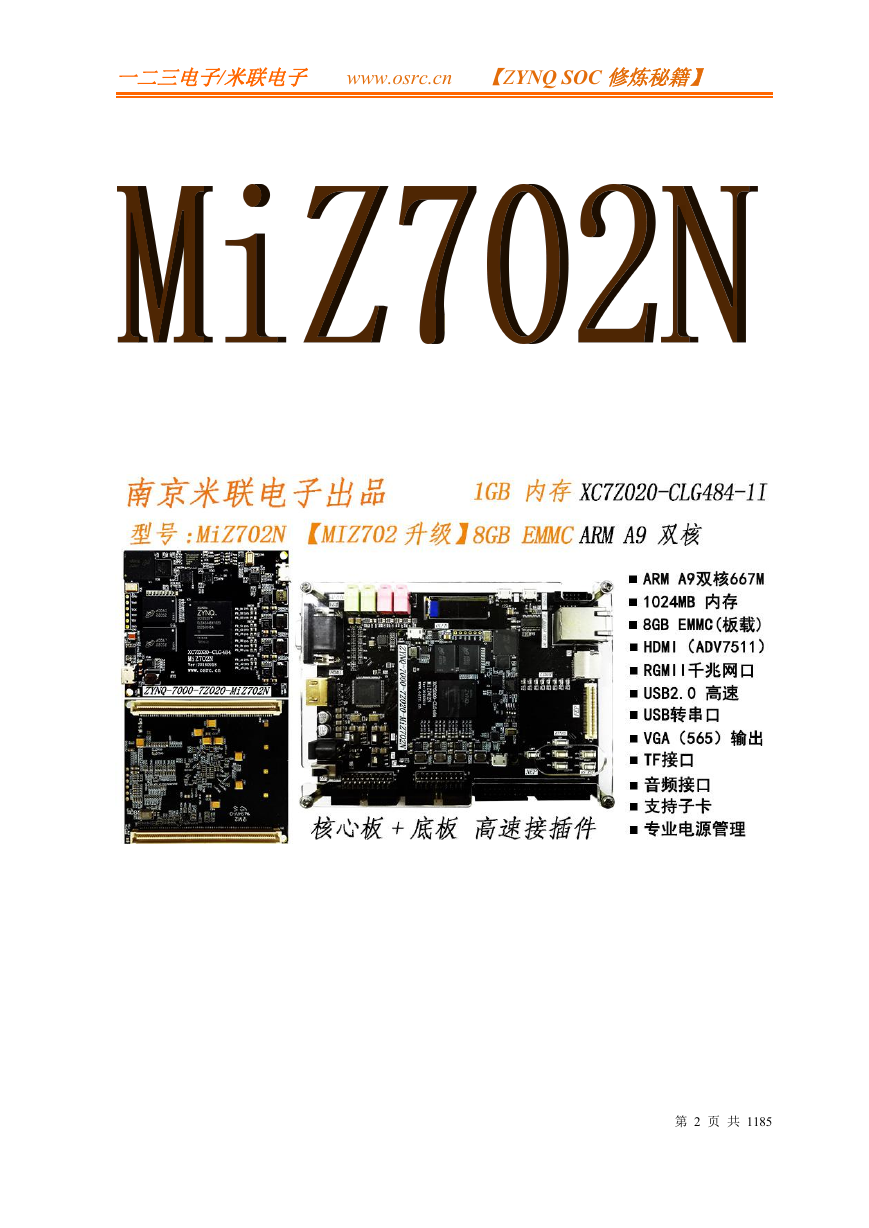

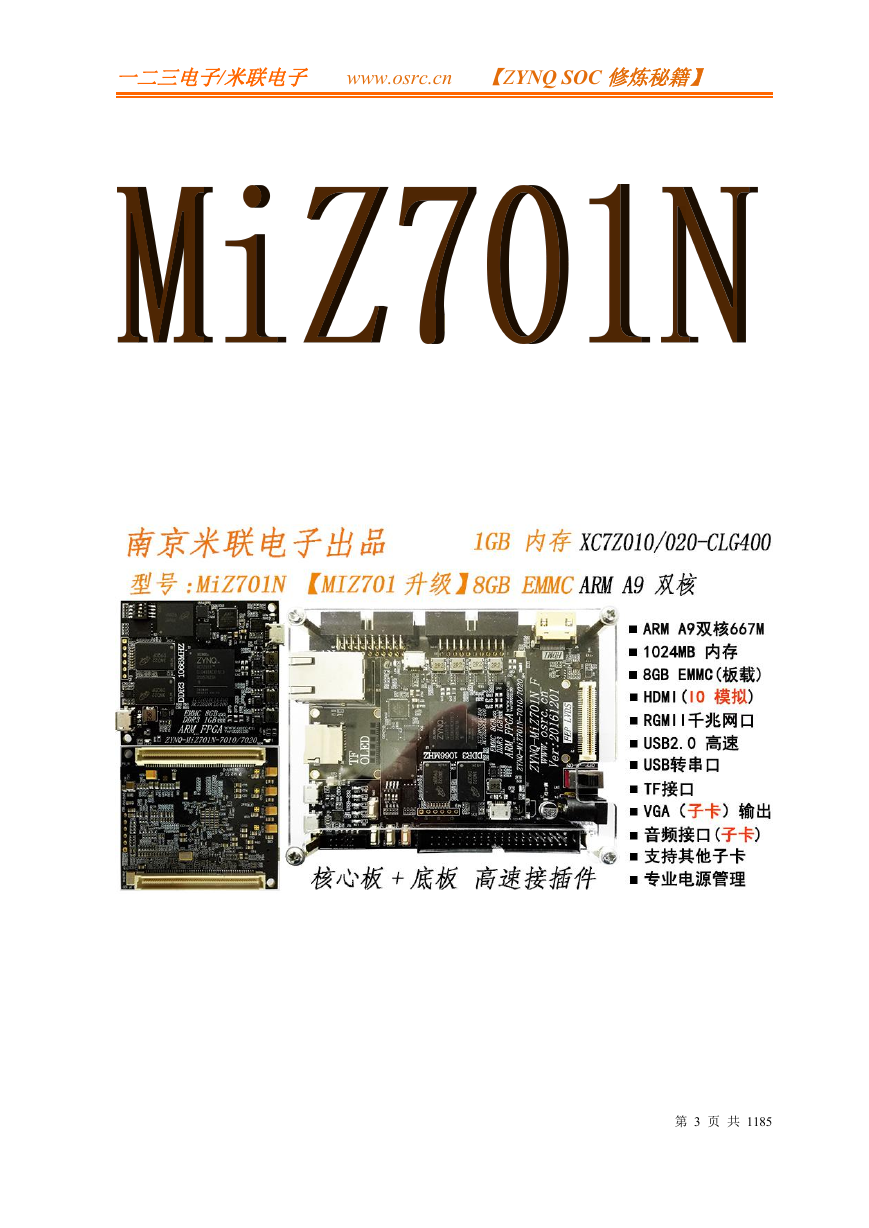

【第一季】ZYNQ SOC开机及FPGA基础 共12课时

S01_CH01_开机程序测试

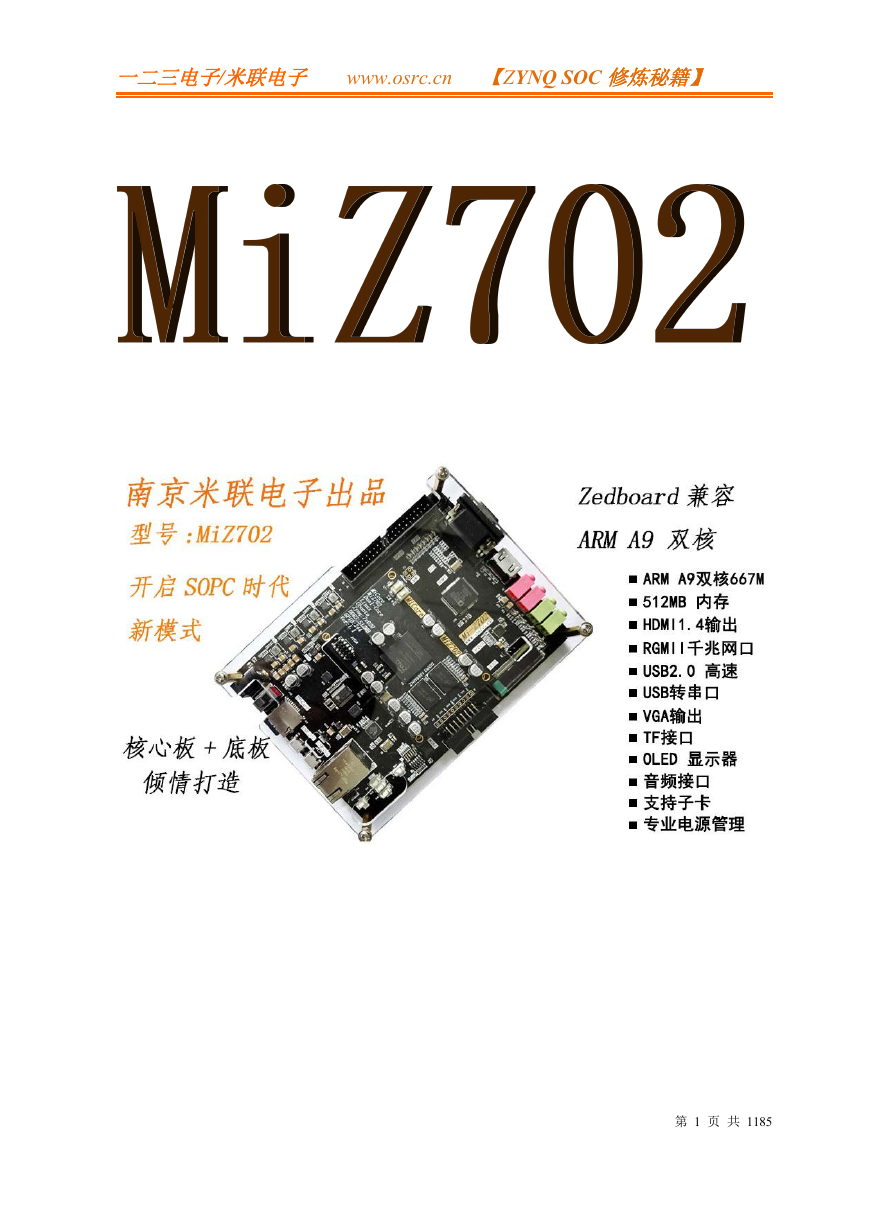

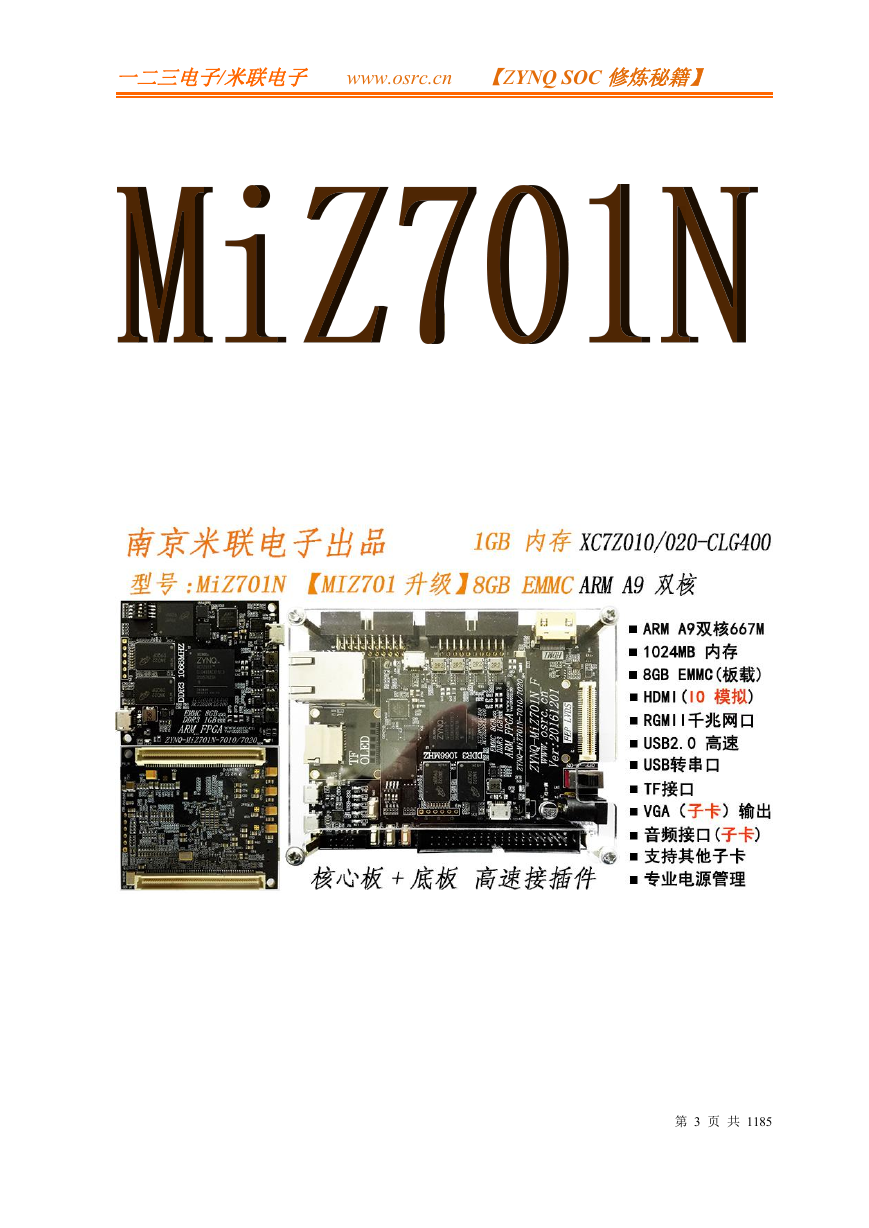

1.1 MIZ701N 开机测试连线图

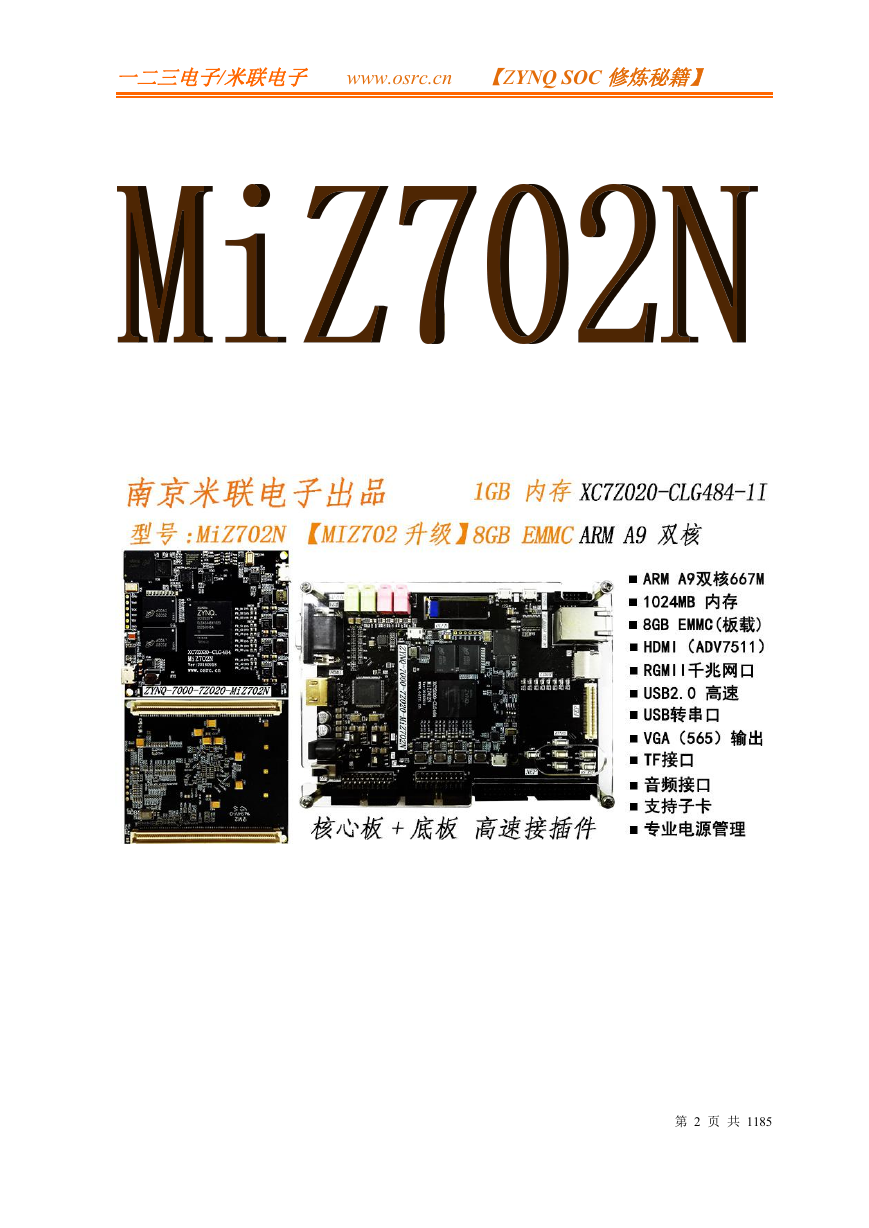

1.2 MIZ702N 开机测试连线图

1.3 MIZ702 开机测试连线图

1.5 UBUNTU系统界面

1.7 网口测试

1.8 美图欣赏

S01_CH02_ZYNQ_VIVADO 软件安装

2.1 VIVADO软件介绍

2.2 VIVADO软件安装(适合所有vivado安装)

2.3 VIVADO软件注册

2.3本章小结

S01_CH03_USB下载器驱动安装及下载程序

3.1下载器驱动的安装

3.2下载runled工程的bit文件验证板子和下载器工作正常

3.3下载器使用需要注意的问题

4.1 Verilog HDL 代码规范

4.2技术背景

4.3 Verilog最最基础语法

4.4关键字

4.5 Verilog中数值表示的方式

4.6阻塞赋值和非阻塞赋值详解

S01_CH05_FPGA设计Verilog基础(二)

5.1状态机设计

5.2一段式状态机

5.3两段式状态机

5.4三段式状态机

S01_CH06_FPGA设计Verilog基础(三)TESTBENCH¥¥¥¥¥

6.1 完成的Test bench文件结构

6.2 时钟激励设计

6.3 复位信号设计

6.4 特殊信号设计

6.5 仿真控制语句及系统任务描述

6.6加法器的仿真测试文件编写

S01_CH07_FPGA_RunLED创建VIVADO工程实验

7.1 硬件图片

7.2 硬件原理图

7.3新建VIVADO工程

7.4创建工程文件

7.5 Verilog FPGA流水灯实验

7.6 添加管脚约束文件

7.7 编译并且产生bit文件

7.8下载程序

7.9实验结果

7.10本章小结

S01_CH08_FPGA_Button 按钮去抖动实验

8.1硬件介绍

8.2时序设计

8.3程序源码

8.4程序分析

8.5综合布线前仿真时序

8.6 Chipscope在线逻辑分析仪仿真

8.7输出结果

8.8小结

S01_CH09_FPGA多路分配器设计

9.1 硬件图片

9.2 硬件原理图

9.3 介于VIVADO的FPGA设计流程

9.4 多路分配器设计思想

9.5时序设计

9.6程序源码

9.7行为仿真

9.7.1创建多路分频器工程

9.7.2添加仿真文件

9.7.3行为级仿真

9.8综合 Synthesis

9.8.1添加文件

9.8.2综合并查看报告

9.8.3综合时序仿真

9.9执行Implementation

9.9.1执行并查看报告

9.9.2布局布线后时序仿真

9.10 VIVADO在线逻辑分析仪使用

9.10.1 IP Catalog添加IA ip core

9.10.2 逻辑分析仪抓取的信号

9.10.3 逻辑分析仪使用

9.11小结

S01_CH10_VGA 接口测试

10.1 硬件介绍

10.2 时序分析

10.3新建VIVADO工程

10.4创建工程文件

10.5 添加管脚约束文件

10.6 编译并且产生bit文件

10.7 下载程序

10.8实验结果

10.9本章小结

S01_CH11_ADV7511 HDMI接口测试

11.1 ADV7511概述

11.1.1 硬件特性

11.1.2 视频输入

11.1.3 支持的输出格式

11.1.4 视频接口信号采样

11.1.5 功能框图

11.1.6 寄存器空间

11.2 硬件电路分析

11.3创建工程文件

11.4 添加管脚约束文件

11.5 编译并且产生bit文件

11.6 下载程序

11.7实验结果

S01_CH12_PL IO口模拟HDMI接口测试

12.1创建工程文件

12.4 添加管脚约束文件

12.5 编译并且产生bit文件

12.6 下载程序

12.7实验结果

【第二季】ZYNQ SOC 入门基础 共16课时

S02_CH01_Hello World实验

1.1最小系统分析

1.6 MemTest内存测试程序

1.7 DRAMTest内存测试程序

1.8 LWIP协议对千兆网口测试

1.9使用快捷按钮调试

1.10 本章小结

S02_CH02_MIO实验

2.1 GPIO简介

2.1.1 GPIO的控制寄存器地址空间

2.1.2MIO内部构造分析

2.1.3 EMIO的特性

2.2 电路分析及实验预期

2.3 ZYNQ核的添加及配置

2.4新建LED_Flash SDK工程

2.5 程序分析

2.6 本章小结

S02_CH03_EMIO实验

3.1 EMIO 和MIO的对比介绍

3.2 电路分析与实验现象

3.3 创建VIVADO工程

3.4 创建约束文件

3.5 产生bit文件并导入到SDK中

3.6 程序分析

3.7 本章小结

S02_CH04_User_IP实验

4.1 创建IP

4.2 调用自定义IP

4.3 导入到SDK

4.4 本章小结

S02_CH05_UBOOT实验

5.1什么是固化

5.2固化的流程

5.3固化准备

5.4 zynq的从SD卡的启动的过程

5.5 zynq启动模式位的选择

5.6 BOOT.bin制作过程详解

5.7 从Quad-SPI启动

5.8 本章小结

S02_CH06_XADC实验

6.1实验概述

6.2 新建一个VIVADO工程

6.3 加载到SDK

6.4函数介绍

6.5 本章小结

S02_CH07_ ZYNQ PL中断请求

7.1 ZYNQ 中断介绍

7.1.1 ZYNQ中断框图

7.1.2 ZYNQ CPU软件中断 (SGI)

7.1.3 ZYNQ CPU 私有端口中断

7.2 搭建硬件地址

7.3 加载到SDK

7.4 程序分析

7.5 本章小结

S02_CH08_ ZYNQ 定时器中断实验

8.1中断原理

8.1.1软件中断(SGI)

8.1.2共享中断SPI

8.1.3私有中断(PPI)

8.1.4私有定时器

8.2 搭建硬件工程

8.3 加载到SDK

8.4 程序分析

8.5 本章小结

S02_CH09_UART串口中断实验

9.1 加载到SDK

9.2 程序分析

9.3 本章小结

S02_CH10_ User GPIO实验

10.1 创建IP

10.2 搭建硬件工程

10.3 加载到SDK

10.4 程序分析

10.4 本章小结

11.1 方案框架

11.2 硬件工程搭建

11.3 加载到SDK

11.4 本章小结

S02_CH12_ AXI_Lite 总线详解

12.1前言

12.2 AXI总线与ZYNQ的关系

12.3 AXI总线和AXI接口以及AXI协议

12.3.1 AXI总线概述

12.3.2 AXI接口介绍

12.3.3 AXI协议概述

12.3.4 AXI协议之握手协议

12.4 AXI4-Lite详解

12.4.1 AXI4-Lite源码查看

12.4.2 AXI-Lite 源码分析

12.5 观察AXI4-Lite总线信号

12.6 加载到SDK

12.7 本章小结

S02_CH14_ EMIO_OLED 实验

14.1板载OLED硬件原理

14.1.1 硬件电路简析

14.1.2 SSD1306简介

14.2 OLED驱动开发思路解析

14.2.1 SPI接口

14.2.2 SSD1306控制

14.2.2 Frame Buffer显示机制

14.2.3 像素操作函数

14.2.4 其他API的实现

14.3 OLED驱动方案实现

14.4 点阵式OLED显示原理

14.4.1 OLED简介

14.4.2 点阵式显示设备显示原理

14.4.3 字模的获取

14.5 硬件搭建

14.6 导入到SDK

14.7 本章小结

S02_CH15_ AXI_OLED 实验

15.1 自定义IP的封装

15.2 SSD1306_OLED_ML用户IP的修改

15.3 OLED硬件控制器关键状态机

15.4 硬件工程搭建

15.5 导入到SDK

15.6 本章小结

S02_CH16 等精度频率计实验

16.1等精度频率计原理

16.1.1引 言

16.1.2频率测量原理

16.1.3脉冲计数法

16.1.4 周期测频法

16.1.5多周期同步测频原理及误差分析

16.2等精度频率计设计

16.2.1 PS寄存器功能划分

16.2.2具体实现

16.2.3频率计PL部分代码设计

16.3硬件工程搭建

16.4 导入到SDK

16.5 误差分析

16.6 本章小结

【第三季】ZYNQ SOC 裸奔应用方案共18课时

S02_CH13_ AXI_PWM 实验

13.1 自定义IP的封装

13.2 miz702_pwm用户IP的修改

13.3 搭建硬件工程

13.4 加载到SDK

13.5 程序分析

13.6 本章小结

S03_CH01_AXI_DMA_LOOP 环路测试

1.1概述

1.2搭建硬件系统

1.2.1新建VIVADO工程

1.2.2创建VIVADO硬件构架

1.3 PS部分软件分析

1.3.1新建SDK工程

1.3.2 main.c源码的分析

1.3.3 dma_intr.c 源码分析

1.3.4 dam_intr.h 文件分析

1.4测试结果

S03_CH02_AXI_DMA PL发送数据到PS

1.1概述

1.2系统构架框图

1.2.1 ZYNQ IP的设置

1.3 PS部分

1.4 测试结果

S03_CH03_AXI_DMA_OV7725摄像头采集系统

3.1概述

3.2系统构架

3.2.1构架方案图

3.2.2构BLOCK模块化设计方案图

3.3 vid in IP介绍

3.3.1 OV_Sensor_ML 自定义 IP模块

3.3.2 vid in IP模块

3.3.2 VID_IN IP接口信号的定义

3.4 VTC IP的分析

3.4.1 VTC IP的参数介绍

3.4.2 VTC IP接口信号的定义

3.4.3 VTC IP配置寄存器

3.4.5设置VTC IP

3.6 PLL时钟设置

3.7 VID_OUT IP的分析

3.7.1 VID_OUT 的参数介绍

3.7.2 VID_OUT IP接口信号的定义

3.8 FPGA 实现的用户逻辑代码

3.8.1关键信号1

3.8.2关键信号2

3.8.3关键信号3

3.8.4 部分关键代码

3.9 PS部分

3.9.1 DMA中断函数部分分析

3.9.2 main.c文件

3.10实验效果

S03_CH04_AXI_DMA_OV5640摄像头采集系统

4.1概述

4.2系统构架

4.2.1构架方案图

4.2.2构BLOCK模块化设计方案图

4.3 vid in IP介绍

4.3.1 OV_Sensor_ML 自定义 IP模块

4.3.2 vid in IP模块

4.3.2 VID_IN IP接口信号的定义

4.4 VTC IP的分析

4.4.1 VTC IP的参数介绍

4.4.2 VTC IP接口信号的定义

4.4.3 VTC IP配置寄存器

4.4.5设置VTC IP

4.6 PLL时钟设置

4.7 VID_OUT IP的分析

4.7.1 VID_OUT 的参数介绍

4.7.2 VID_OUT IP接口信号的定义

4.8 FPGA 实现的用户逻辑代码

4.8.1关键信号1

4.8.2关键信号2

4.8.3关键信号3

4.8.4 部分关键代码

4.9 PS部分

4.9.1 DMA中断函数部分分析

4.9.2 main.c文件

4.10实验效果

S03_CH05_AXI_DMA_HDMI图像输出

5.1概述

5.2系统构架

5.2.1构架方案图

5.2.2构BLOCK模块化设计方案图

5.3 vid in IP介绍

5.3.1 OV_Sensor_ML 自定义 IP模块

5.3.2 vid in IP模块

5.3.2 VID_IN IP接口信号的定义

5.4 VTC IP的分析

5.4.1 VTC IP的参数介绍

5.4.2 VTC IP接口信号的定义

5.4.3 VTC IP配置寄存器

5.4.5设置VTC IP

5.6 PLL时钟设置

5.7 VID_OUT IP的分析

5.7.1 VID_OUT 的参数介绍

5.7.2 VID_OUT IP接口信号的定义

5.8 FPGA 实现的用户逻辑代码

5.8.1关键信号1

5.8.2关键信号2

5.8.3关键信号3

5.8.4 部分关键代码

5.9 PS部分

5.9.1 DMA中断函数部分分析

5.9.2 main.c文件

5.10实验效果

S03_CH06_AXI_VDMA_OV7725摄像头采集系统

6.1 为什么要用VDMA

6.1.1 什么是帧缓存

6.1.2 双缓冲机制

6.1.3 Zynq硬件架构

6.1.4 VDMA的作用

6.2 VDMA概述

6.3 VDMA详细介绍

6.3.1 接口

6.3.1.1 时钟和复位

6.3.1.2 AXI总线相关信号

6.3.1.3 视频同步接口信号

6.3.1.4 GenLock相关信号

6.3.2 VDMA帧存格式

22.3.3 读写通道工作时序

6.3.3.1 读通道(MM2S)时序

6.3.3.2 写通道(S2MM)时序

6.3.4 寄存器

6.3.2.1 MM2S VDMA 控制寄存器(00h)

6.3.2.2 MM2S VDMA 状态寄存器(04h)

6.3.2.3 PARK_PTR_REG停留指针寄存器(28h)

6.3.2.4 MM2S 帧存起始地址(0x5C~0x98)

6.3.2.5 MM2S_FRMDLY_STRIDE MM2S帧延迟和跨度(58h)

6.3.2.6 MM2S_HSIZE MM2S水平方向尺寸(54h)

6.3.2.7 MM2S_VSIZE MM2S垂直方向尺寸(50h)

6.3.2.8 S2MM VDMA 控制寄存器(30h)

6.3.2.9 S2MM VDMA 状态寄存器(34h)

6.3.2.4 S2MM 帧存起始地址(0xAC~0xE8)

6.3.2.5 S2MM_FRMDLY_STRIDE S2MM帧延迟和跨度(A8h)

6.3.2.6 S2MM_HSIZE S2MM水平方向尺寸(A4h)

6.3.2.7 S2MM_VSIZE S2MM垂直方向尺寸(A0h)

6.3.5帧同步选项

6.3.6 Genlock同步机制

6.3.6.1 什么是Genlock?

6.3.6.2 Genlock Master

6.3.6.3 Genlock Slave

6.3.6.4 Dynamic Genlock Master

6.3.6.5 Dynamic Genlock Slave

6.4 使用VDMA

6.4.1 IP核配置

6.4.2 软件控制流程

6.5 搭建VDMA图像系统

6.5.1构架方案图

6.5.2构BLOCK模块化设计方案图

6.6 PS部分

6.6.1 main函数

6.6.2 vdma_api.c函数

6.7 测试结果

S03_CH07_AXI_VDMA_OV5640摄像头采集系统

7.1概述

7.2 搭建VDMA图像系统

7.2.1构架方案图

7.2.2构BLOCK模块化设计方案图

7.3 PS部分

7.4 测试结果

S03_CH08_DMA_LWIP以太网传输

8.1概述

8.2搭建硬件系统

8.2.1系统构架

8.2.1 启用HP接口

8.2.2启用PL到PS的中断资源

8.2.3启动PS部分的以太网接口

8.2.4 时钟的设置

8.2.5 DMA IP 配置

8.2.6 GPIO的配置

8.2.7配置axi_ data_fifo _0

8.2.8设置S_AXIS接口

8.2.9地址空间映射

8.3 FPGA的发送代码

8.4 PS部分BSP设置

8.4.1 SDK工程BSP设置

8.4.2 lwip函数库设置

8.5 PS部分程序分析

8.5.1 main.c分析

8.5.2 AXI DMA数据传输过程

8.6 连接测试

S03_CH09_DMA_4_Video_Switch视频切换系统

9.1概述

9.2修改OV_Sensor_ML摄像头采集IP

9.3搭建硬件系统

9.3.1系统图

9.3.2 OV_Sensor_ML IP接线图

9.3.3 vid_in IP的接线图

9.3.4 DMA 和FIFO通路

9.3.5 vid_out IP的通路

9.3.6 AXI HP通道和DMA中断

9.3.7 DMA IP的设置

9.3.8 时钟管理模块

9.3.9VTC 图像时序发生模块

9.4 FPGA 四路输入以及图像切换源码分析

9.4.1 按钮输入去抖代码

9.4.2 DMA 4路视频输入的FPGA代码

9.4.3 DMA 输出通道

9.5 4路视频切换DMA C处理源码分析

9.5.1 main.c源码

9.5.2 dma_intr.h源码

9.5.3 dma_intr.c中断接收源码

9.5.4 dma_intr.c中断发送源码

9.6本章小结

S03_CH10_DMA_4_Video_Stitch视频拼接系统

10.1概述

10.2修改OV_Sensor_ML摄像头采集IP

10.3搭建硬件系统

10.3.1系统图

10.3.2 OV_Sensor_ML IP接线图

10.3.3 vid_in IP的接线图

10.3.4 DMA 和FIFO通路

10.3.5 vid_out IP的通路

10.3.6 AXI HP通道和DMA中断

10.3.7 DMA IP的设置

10.3.7 时钟管理模块

10.3.8 VTC 图像时序发生模块

10.4 FPGA 四路输入以及图像拼接源码分析

10.4.1 图像常量参数

10.4.2 DMA 4路视频输入的FPGA代码

10.4.3 DMA 输出通道

10.5 4路视频切换DMA C处理源码分析

10.5.4.1 main.c源码

10.5.4.2 dma_intr.h源码

10.5.4.3 dma_intr.c中断接收源码

10.5.4.4 dma_intr.c中断发送源码

10.6测试结果

S03_CH11_基于TCP的QSPI Flash bin文件网络烧写

11.1概述

11.2基本原理

11.3 Bin文件

11.4 QSPI Flash

11.5驱动程序

11.5.1建立TCP Server

11.5.2 lwip库设置

11.5.3程序解析

11.5.4 接收保存BOOT.bin文件

11.5.5烧写QSPI Flash

11.5.6 TCP调试信息输出

11.6网络调试助手操作方法

11.6.1发送bin文件

11.6.7发送启动Flash烧写命令

11.7 Bin文件更新验证

11.8待改进之处

S03_CH12_基于UDP的QSPI Flash bin文件网络烧写

12.1概述

12.2基本原理

12.2.1 Bin文件

12.2.2 QSPI Flash

12.3驱动程序

12.3.1 main函数

12.3.3 lwip库设置

12.3.4 程序解析

12.3.5接收保存BOOT.bin文件

12.3.6烧写QSPI Flash

12.3.7 UDP调试信息输出

12.4网络调试助手操作方法

12.4.1发送bin文件

12.4.2发送启动Flash烧写命令

12.5 Bin文件更新验证

12.6待改进之处

S03_CH13_ZYNQ A9 TCP UART双核AMP例程

13.1概述

13.2基本原理

13.2.1软件中断

13.2.2共享内存通信

13.2.3双核BOOT

13.3驱动程序

13.3.3 CORE0工程

13.3.3.1 main函数

13.3.3.2建立TCP Server

13.3.3.3 初始化软件中断

13.3.3.4 启动CORE1

13.3.3.5 数据写入共享内存

13.3.3.6 触发软件中断

13.3.3.7响应软件中断

13.4 CORE1工程

13.4.1 main函数

13.4.2初始化软件中断

13.4.3响应软件中断

13.4.4共享内存数据读出

13.4.5触发软件中断

13.5工程创建及设置关键步骤

13.6工程调试关键步骤

13.7网络调试助手操作方法

13.8生成BOOT.bin

13.9双核BOOT验证

S03_CH15_EMIO光电通信-FEP子卡的使用

15.1概述

15.2基本原理

15.15.1 88E1512

15.15.2 88E1512 RGMII接口时序

15.3 PL部分设计

15.3.1 IP连线图

15.3.2 ZYNQ PS设置

15.3.3 GMII to RGMII

15.3.3.1 PS ETH EMIO

15.3.3.2 IP核设置

15.3.4 时序约束

15.3.4.1 input delay约束

15.3.4.2 output delay约束

15.3.4.3 IDELAYE2延时设置

15.3.4 IO口

15.4 PS程序设计

15.4.1 LWIP库修改

15.4.2 创建工程

15.4.15.1 lwip库设置

15.4.15.2 example代码修改

15.5程序测试

15.5.1电口测试

15.5.1.1 lwip库设置

15.5.1.2网络测试

15.5.2光口测试

15.5.15.1 lwip库设置

15.5.15.2 网络测试

S04_CH16 PL AXI ETH光电网络通信

16.1概述

16.2基本原理

16.2.1 88E1512

16.2.2 88E1512 RGMII接口时序

16.3 PL部分设计

16.3.1 IP连线图

16.3.2 ZYNQ PS设置

16.3.3 AXI 1G/2.5G Ethernet Subsystem

16.3.4 AXI Direct Memory Access

16.3.5 PL至PS的中断

16.3.6时序约束

16.3.6.1 input delay约束

16.3.6.2 output delay约束

16.3.6.3 IDELAYE2延时设置

16.3.7 IO口

16.4 PS程序设计

16.4.1 LWIP库修改

16.4.2创建工程

16.4.2.1 lwip库设置

16.4.2.2 example代码修改

16.5程序测试

16.5.1电口测试

16.5.1.1 lwip库设置

16.5.1.2网络测试

16.5.2光口测试

16.5.2.1 lwip库设置

16.5.2.2网络测试

S03_CH17基于μGUI的触摸屏GUI界面设计

17.1概述

17.2基本原理

17.3 LCD触摸屏

17.3.1液晶屏

17.3.2触摸屏

17.3.3触摸屏唤醒

17.3.4触摸中断

17.3.5 触摸信息获取

17.3.6触摸屏与Miz ZYNQ开发板的接口

17.4 μGUI概述

17.4.1 μGUI库移植

17.4.1.1添加单像素点像素值设置函数

17.4.1.2调整各种变量类型定义

17.4.1.3 GUI窗口

17.4.1.4 GUI界面刷新

17.4.1.5人机交互

17.4.2颜色空间

17.4.3字体大小

17.5 PL逻辑框架

17.5.1 PS设置

17.5.2 GUI界面显示

17.5.2.1 AXI VDMA设置

17.5.2.2 Video Timing Controller

17.5.2.3 AXI4-Sream to Video Out

17.5.2.4 AXI-Sream Subset Converter

17.5.3 AXI PWM

17.5.4 AXI GPIO

17.5.5 Clocking Wizard

17.5.6 IO口

17.5.6.1 PL IO信号定义

17.5.6.2 LCD时钟信号输出

17.5.6.3 LCD RGB信号映射

17.5.6.4 LCD控制信号

17.6 PS程序设计

17.6.1 main函数

17.6.2时钟重配置

17.6.2.1 SDK库移植

17.6.2.2 驱动程序

17.6.3 PWM信号输出

17.6.3.1 SDK库设置

17.6.3.2 驱动程序

17.6.4 GPIO输入输出

17.6.5 I2C读取触摸信息

17.6.6 GUI界面显示

17.6.7定时器

17.6.8 GUI界面设计

17.7注意事项

17.7.1 更改GUI分辨率

17.7.2 SDK路径设置

17.7.3 miz701n的LD5不受GUI控制

第四季 LINUX系统开发开发共计16课时

S04_CH01_搭建工程移植LINUX/测试EMMC/VGA

1.1概述:

1.2 LINUX开发环境搭建

1.2.1虚拟机环境配置(提供下载虚拟机已经完成)

1.2.2下载资源

1.3 VIVADO 工程的搭建

1.3.1 VIVADO 硬件工程构架

1.3.2 时钟设置

1.4 PS设置

1.4.1 PS SDK测试显示器输出

1.4.2测试效果 缺图

1.4.3 新建FSBL工程

1.4.4产生设备树

1.5编译 u-boot、kernel、设备树和文件系统

1.5.1批处理文件

1.5.2 修改设备树

1.5.3 添加 framebuffer驱动

1.5.4执行mk_kernel.sh编译内核

1.5.5执行mk_bootloader.sh编译uboot

1.5.6制作UBOOT.BIN

1.6 EMMC 8GB内存测试(MIZ702不支持)

1.7 测试 framebuffer

S03_CH14_通过BRAM进行PS和PL间的数据交互

14.1概述

14.2基本原理

14.3 PL部分设计

14.3.1 IP连线图

14.3.2 PS配置

14.3.3 AXI BRAM Controller

14.3.4 Block Memory Generator

14.3.5 AXI GPIO

14.4逻辑设计

14.4.1 BRAM读时序

14.4.2 BRAM写时序

14.5 PS程序设计

14.5.1 main函数

14.5.2 GPIO输入输出

14.5.3 BRAM数据写入

14.5.4 BRAM数据读出

14.6 程序测试

14.7 课后习题

S04_CH02_工程移植ubuntu并一键制作启动盘

2.1概述

2.2搭建硬件系统

2.3一键制作

2.4 运行结果

S04_CH03_QSPI烧写LINUX系统

3.1概述

3.2搭建硬件系统

3.3修改内核文件

3.3编译内核及uboot

3.4制作qspi镜像

3.5安装screen

3.6一件烧写QSPI FLASH 1

3.7烧写QSPI FLASH 2

S04_CH04_自动挂载8GB EMMC板载内存

4.1概述

4.2 执行source setup_env.sh

4.3修改zynq-7000.dtsi文件

4.4 设置mount_emmc.sh批处理命令的开机启动

4.5烧写程序到QSPI FLASH

4.6验证测试

S04_CH05_在线升级QSPI镜像(U盘方式)

5.1概述

5.2 执行source setup_env.sh

5.3烧写程序到QSPI FLASH

5.4查看系统根目录

5.5基于U盘在线升级

S04_CH06_hello_linux

6.1概述

6.2 执行source setup_env.sh

6.3 SD卡手动运行hello程序

6.4 EMMC卡手动运行hello程序

S04_CH07_Hello_Qt在开发板上的运行

7.1概述

7.2 搭建交叉编译环境

7.2.1使用批处理命令搭建交叉编译环境

7.2.2 setup_env.sh 批处理文件源码

7.2.3 get_qt_sources.sh 批处理文件源码

7.2.4 mk_qt_img.sh 批处理文件源码

7.2.4 init.sh文件

7.2.5测试结果

7.3 在PC端LINUX安装qt5.8.0

7.4 QtE LINUX PC端创建工程

7.5对QtE设置交叉编译

7.6测试结果

第五季 HSL算法基础入门12课时

S05_CH01_搭建Modelsim和Vivado联合调试环境

1.1 概述

1.2 使用GUI编译仿真库

1.3 使用命令行编译仿真库

1.4 HLS简单介绍

1.4.1 OpenCV和HLS视频库

1.4.2 AXI4流和视频接口

1.4.3 OpenCV到RTL代码转换的流程

1.5 本章小结

S05_CH02_shift_led实验

2.1 概述

工程创建、仿真及优化

2.2.1 工程创建

代码综合

代码优化

2.2.4仿真实现

2.3 HLS代码封装

2.4硬件平台实现

S05_CH03_ImageLoad 实验

3.1 概述

3.2 图片数据的获取

3.3 视频流文件的载入

3.4 外部摄像头的调用

3.5 工程创建与验证

3.6 本章小结

S05_CH04_Skin_Dection实验

4.1 肤色检测原理及应用

4.2 检测算法实现

4.2.1 工程创建

4.2.2 代码综合

4.2.3 代码优化

仿真测试

本章小结

S05_CH05_Sobel算子硬件实现(一)_HLS实现

5.1 Sobel原理介绍

Sobel算子在HLS上的实现

5.2.1 工程创建

5.2.2 代码优化及仿真

5.2.3 工程封装

5.3 代码详解

本章小结

S05_CH06_Sobel算子硬件实现(二)_硬件验证

6.1 系统硬件设计

6.2硬件工程创建

6.3 导入到SDK

6.4 程序分析

S05_CH07_基于Hough变换的圆检测

7.1 Hough变换原理介绍

7.1.1 Hough变换直线检测

7.1.2 Hough变换圆检测

7.1.3 Hough变换圆检测算法实现流程

7.2 Hough在HLS上的实现

7.2.1 工程创建

7.2.2仿真及优化

7.3 程序分析

7.4 本章小结

S05_CH08_傅里叶变换的HLS实现

8.1 FFT原理介绍

8.2 HLS实现

8.3 Vivado模块例化及IP封包

8.4 本章小结

S05_CH09_OTSU自适应二值化

9.1 OTSU自适应二值化原理简介

9.2 HLS实现

9.2.1 工程创建

9.2.2 仿真及优化

9.3硬件工程实现 (待更新)

9.4 程序分析

S05_CH10_音频滤波

10.1 ADAU1761简介

10.1.1 ADAU1761 收发时序

10.1.2 ADAU1761时钟和采样率

10.2硬件平台的搭建

10.3 导入到SDK

10.4 程序分析

10.5 本章小结

S05_CH11_快速角点检测的HLS实现

11.1 角点定义

11.2 角点检测算法

11.2.1 Moravec角点检测算法

11.2.2 Harris角点检测

11.2.3 FAST角点检测算法

11.3 HLS实现

11.3.1 工程创建

11.3.2仿真及优化

11.4 硬件工程创建

11.4.1 硬件平台搭建

11.4.2 导入到SDK

11.5 程序分析

11.6 本章小结

S05_CH12_HLS车牌识别(待更新)

附录(常见问题汇总)

一、工具篇

1.1 HLS中文注释乱码问题解决方案

1.2 代码字体大小修改

二、设计篇

2.1 hls::stream仿真警告

2.2 仿真时使用cvShowImage()函数但是没有任何错误提示仿真界面直接关闭

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc