中国科技论文在线

http://www.paper.edu.cn

基于有载品质因数的低抖动时钟电路研究#

邱渡裕,田书林,曾浩,谭峰*

(电子科技大学自动化工程学院,成都 611731)

10

5 摘要:抖动作为衡量时钟信号质量的重要指标,对电子系统的性能有重要的意义。数据采集

系统要获得良好的信噪比,就必须要有高性能低抖动的时钟信号。本文应用相位噪声与抖动

的关系,同时结合相位噪声 Leeson 模型,研究了时钟信号发生电路的抖动及相位噪声特性,

分析了电路有载品质因数 QL 对抖动的影响,并给出了电路主要器件与抖动关系的显性表达

式。以一种 100MHz 低抖动时钟信号发生电路为例,进行了理论分析,仿真和实验验证,并

将其应用到 2.5GHz 采样时钟信号发生电路中进行了对比测试。结果表明,提高电路的有载

品质因素 QL 可以明显改善其抖动及相位噪声特性。

关键词:测试计量技术;相位噪声;低抖动时钟;有载品质因数

中图分类号:TN710 TH7

15

Research of a low jitter clock circuit based on loaded quality

factor of circuit

(School of Automation Engineering, University of Electronic Science and Technology of China,

QIU Duyu, TIAN Shulin, ZENG Hao, TAN Feng

Chengdu 611731)

Abstract: Jitter is an important specification which quantifies the quality of a clock signal, it is of

great significance for an electronic system. To obtain a good signal-to-noise ratio performance for

sampling systems, there must be clock signals with low jitter performance. By using the

relationship between phase noise and jitter, the jitter and phase noise characteristics of the clock

signal generating circuit are studied in this paper. Impacts of loaded quality factor (QL) of the

circuit on the jitter are analyzed, and the explicit expression of main components in circuit for

jitter is given as well. Theoretical calculations and analysis are made with the 100MHz low jitter

clock signal generating circuit, and the application of this method to the 2.5GHz sampling clock

signal generator circuit is proposed. The simulation and experiment results show that the jitter and

phase noise characteristics can be improved by increase of quality factor QL of the circuit.

Key words: Testing Technology; Phase Noise; Low Jitter clock; Loaded Quality Factor

20

25

30

0 引言

抖动是时钟发生电路噪声引起的短期不稳定性的表征,它是信号在时域上的一种随机波

35

动特性,表现为信号波形偏离其理想位置的短期瞬态变化。时钟信号的抖动会降低采集系统

的信噪比,影响高速数据采集系统的有效位数以及动态范围[1-3]。在高精度时间间隔测量相

关系统中,低抖动时钟是保证测量精度的重要前提条件[4-5]。在通信系统中,抖动还会减小

信道的带宽,影响数据传输的误码率。因此分析影响时钟抖动的因素,并设计低抖动时钟电

路,是高速数据采集系统中的重要研究内容之一[6-7]。从构成来看,抖动由随机抖动和确定

40

性抖动叠加而成,其中,确定性抖动是电路中确定的源产生,用 Jitterp-p 量化;而随机抖动

主要由热噪声引起,用 Jitterrms 量化。本文重点研究信号发生电路的随机抖动及相位噪声。

基金项目:基金项目:国家自然科学基金(61301263 )、中央高校基本科研基金资助项目(A03008023801080,

ZYGX2014J067)

作者简介:2003 年于电子科技大学获得学士学位,2006 年于电子科技大学获得硕士学位,在职博士,现为

电子科技大学高级工程师,主要研究方向为高速信号获取与处理、高分辨率时间间隔测量,测试系统集成

等. E-mail: qiuduyu@uestc.edu.cn

- 1 -

�

中国科技论文在线

http://www.paper.edu.cn

对于随机抖动,很多学者进行了深入的研究[1-2],他们主要从算法的角度对随机抖动进

行了分析处理。但据我们所知,到目前为止,并没有从信号发生电路设计的角度进行随机抖

45

动抑制的研究。本文从电路的角度研究了信号发生电路的抖动和噪声,接着应用 Leeson 模

型并结合相位噪声与的抖动关系,推导了电网络参数有载品质因数 QL 的表达式。并以一种

Pierce 型时钟信号发生电路为例,进行了验证。结果表明:要获得良好的低抖动特性,就需

要选择低噪声系数、低拐角频率的三极管,谐振电路中的电感和电容对抖动的降低有比较明

显的贡献。

1 基本原理

50

1.1 抖动与相位噪声的转换

研究表明,抖动和相位噪声都是时钟信号短期不稳定性的表征[8]。时钟信号短期不稳定

性在时域表现为抖动,而在频域表现为相位噪声。根据文献[9]的理论[9],即有:

55

对积分用近似求和,可得:

由此可得,抖动与相位噪声的关系,即:

(1)

(2)

(3)

其中,

是随机抖动,

是单边带相位噪声, 是载波频率, 是偏离载波频

率。

60

由式 3 可知,要想降低信号抖动,必须降低相位噪声的功率谱密度。

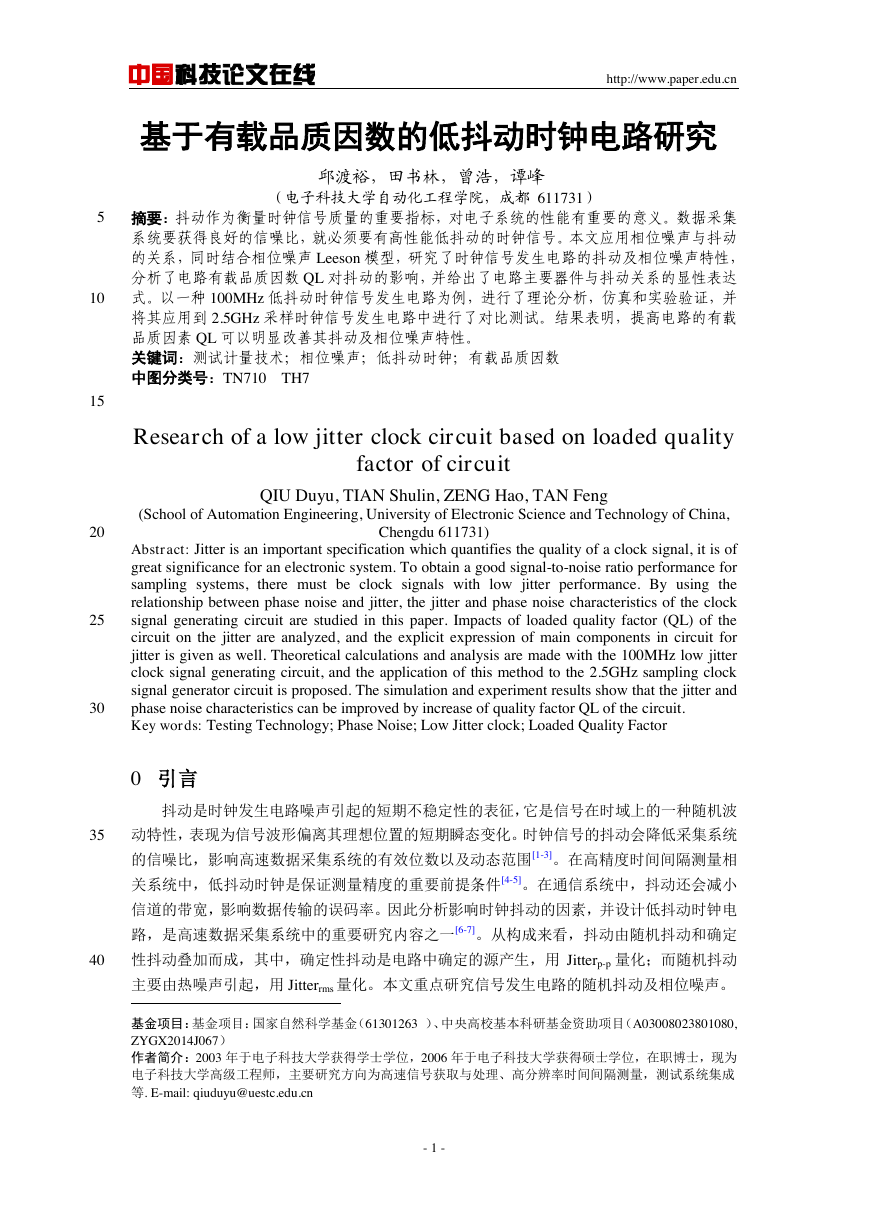

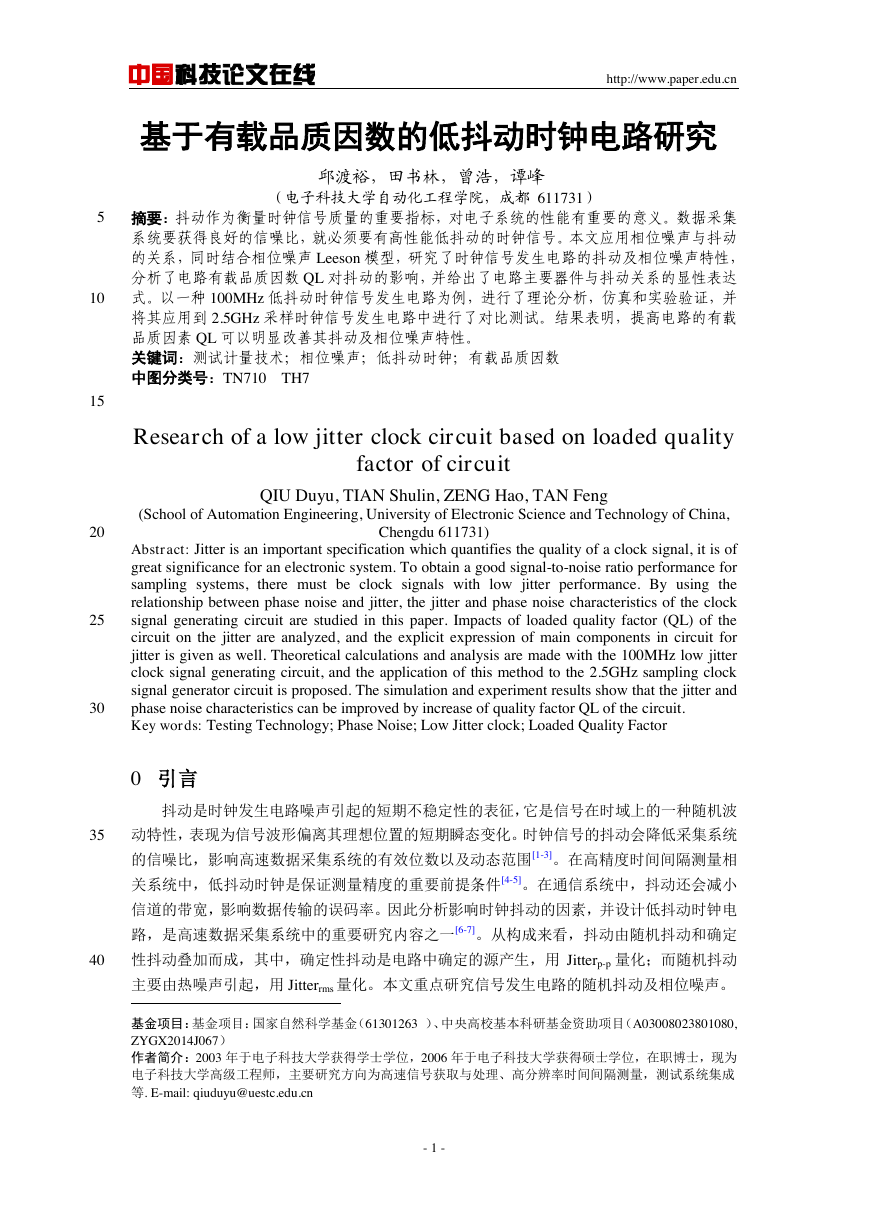

1.2 Leeson 模型与相位噪声

图 1 反馈型振荡器模型

Fig.1 Feedback oscillator model

65

从某种意义上讲,信号发生电路实质上就是振荡器,而振荡器由带有正反馈回路的放大

器构成,也就是 Leeson 反馈振荡器模型[10-11],由图 1 表示。其中

是放大器输入噪声

功率谱密度,

是输出噪声功率谱密度。

根据 Leeson 模型,反馈振荡器在稳定工作条件下的相位反馈表示式为:

(4)

- 2 -

21012frmsfJLfdff2112212nfifiLfLfLfdfmff2112210011222fRMSmmfLfLfJLfdfffffRMSJ()Lf0fmf理想放大器谐振电路()mSf()mSf()mSf()mSf()()()ttt�

中国科技论文在线

http://www.paper.edu.cn

70

由信号传输理论可得放大器内部相位噪声谱密度

与振荡器输出端相位噪声谱

密度

之间的关系:

75

若谐振回路是由 RLC 电路组成的带通滤波回路,其等效低通传递函数为:

(5)

(6)

(7)

其中 QL 是谐振回路的有载品质因数。

把式(7)、(6)代入式(5)中,并将相位噪声功率谱密度函数用对数表示,就可得到振荡器

输出端的单边带相位噪声,即:

(8)

80

其中 为拐角频率, 为偏离载波频率, 为噪声指数, 为波尔兹曼常数, 为绝

对温度, 为信号功率。

由式(8)可知,要使相位噪声降低,可从四个方面改进:降低噪声系数 ;减小拐角频

率 ;提高信号功率 ;提高振荡器的有载品质因数 。而噪声系数 和拐角频率 由

所选双极型晶体管(Bipolar Junction Transistor ,简称 BJT)决定;信号功率 对相位噪声的

85

提高有限。所以,要想降低相位噪声,减小抖动,还需进一步从电网络参数的有载品质因数

QL 着手。实际电路中,电网络参数的有载品质因数 QL 的值从几十到上百万,提高 QL 值非

常有利于降低输出信号的相位噪声,这与文献[12-16]的研究结果相符[12-16]。

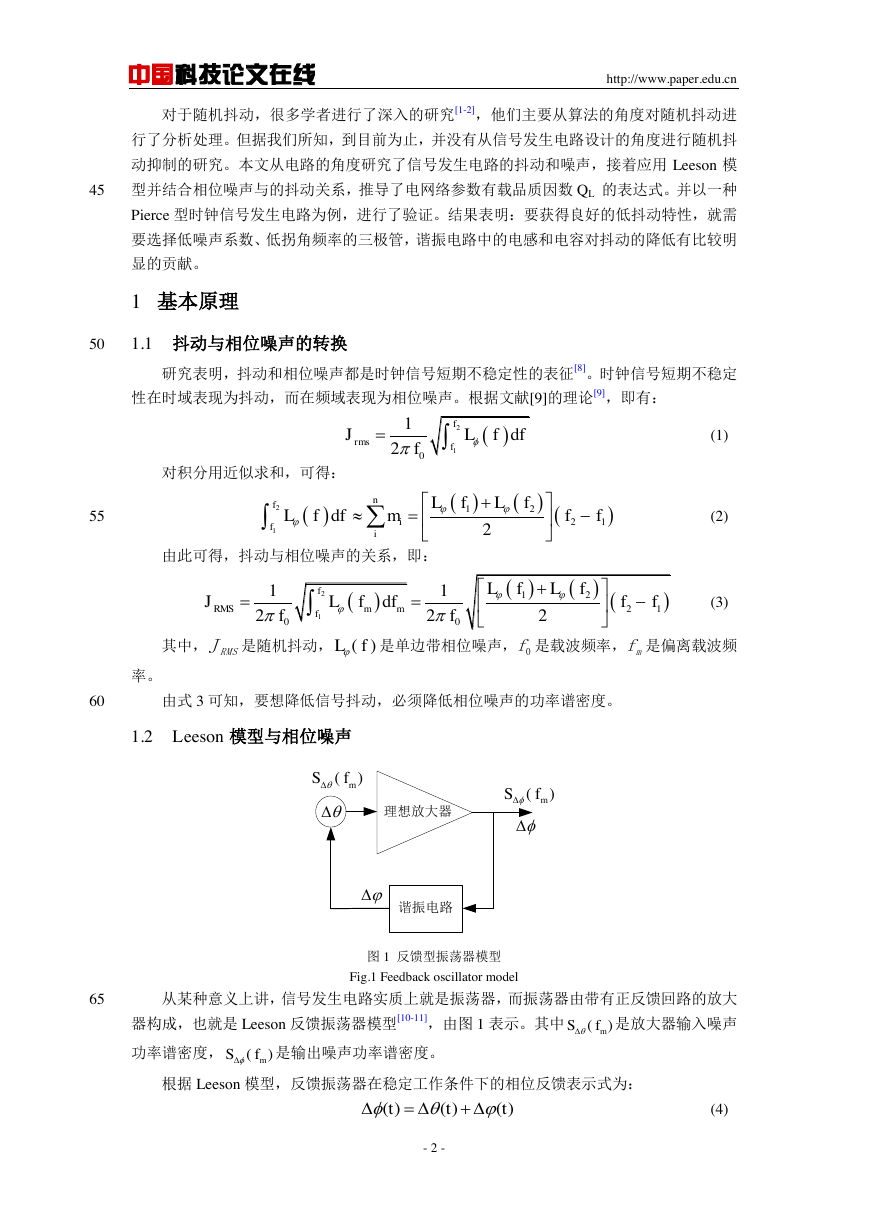

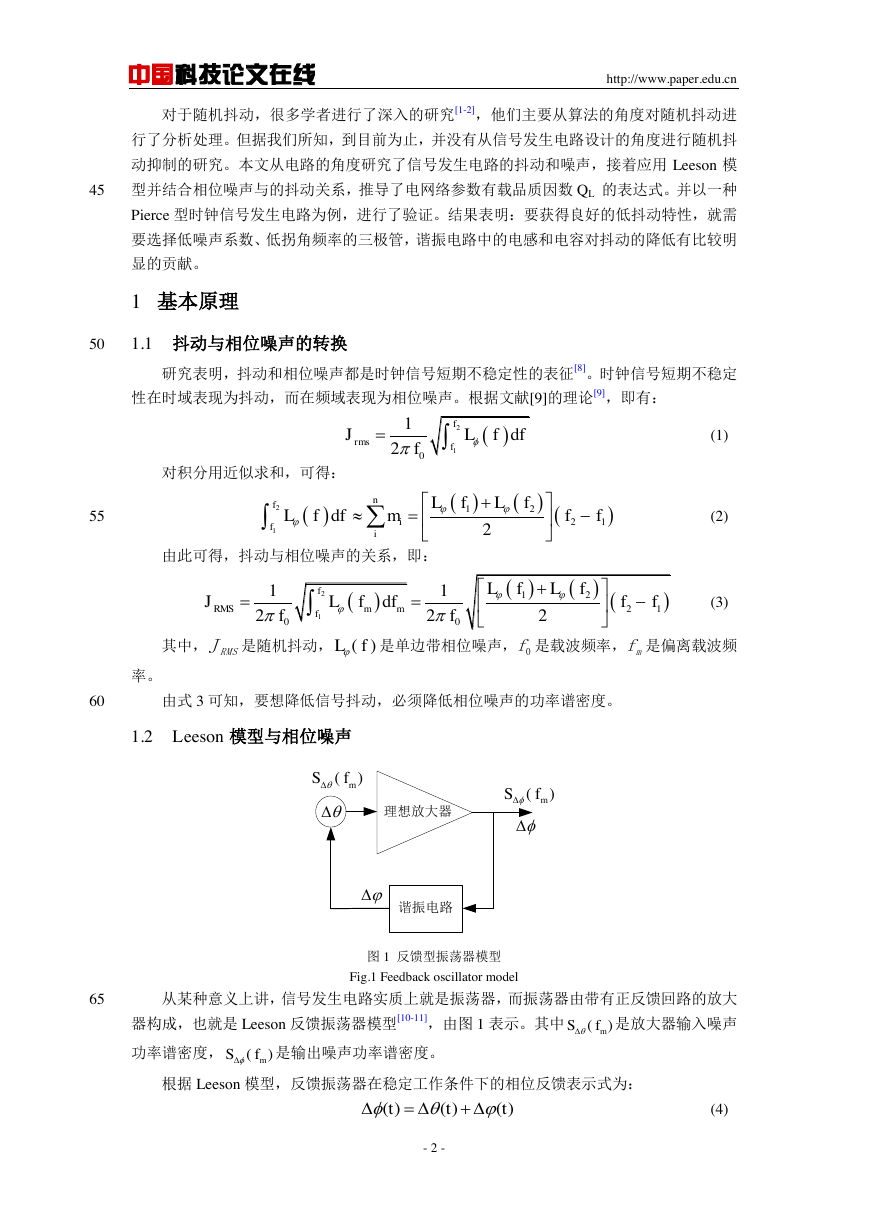

1.3 谐振回路有载品质因数

90

根据 T. Ohira、K. Araki 等研究人员的理论[17-20],对于 BJT 构成的振荡电路,其电网络

参数的有载品质因数 QL 主要由无源器件构成的网络决定。电路中无源器件构成的网络既参

与了振荡又起到了滤波器的作用。如于图 2 所示的电路,有源器件 BJT 引入的噪声只有通

过其外围无源器件组成的电网络来抑制。有载品质因数 QL 越大,噪声抑制效果越明显。

95

图 2 Pierce 交流振荡原型电路

Fig.2 Prototype of Pierce oscillator circuit

由图 2 可得到其无源网络的等效电路,如图 3 所示。

- 3 -

()mS()mS**()()[1()()()()]mmmmmmSSHjHjHjHj()1cmsimfFkTSfPf01()221mLmmRHjjQRjL202111()10lg()10lg11222cmmsmmLffFkTLfSfPffQcfmfFkTspFcfspLQFcfspC1C2LRBJT�

中国科技论文在线

http://www.paper.edu.cn

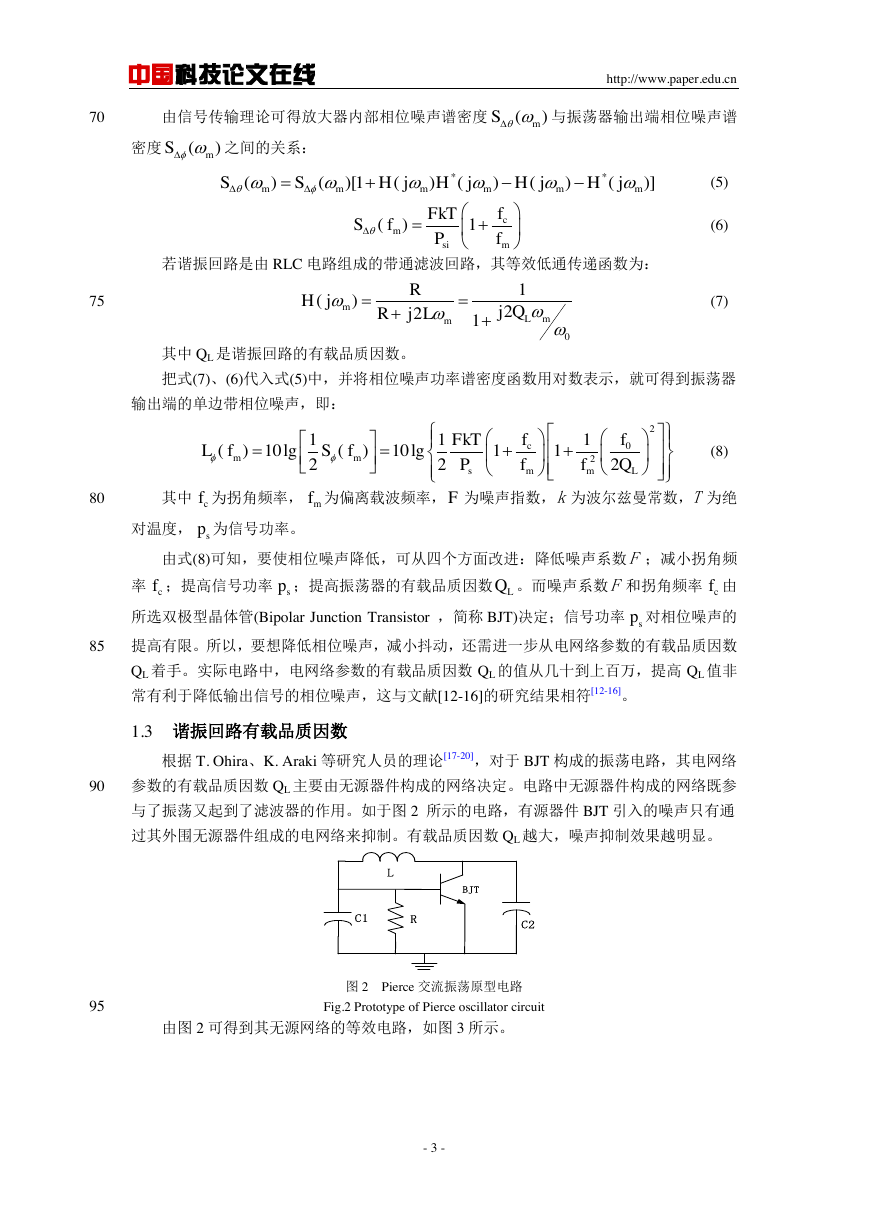

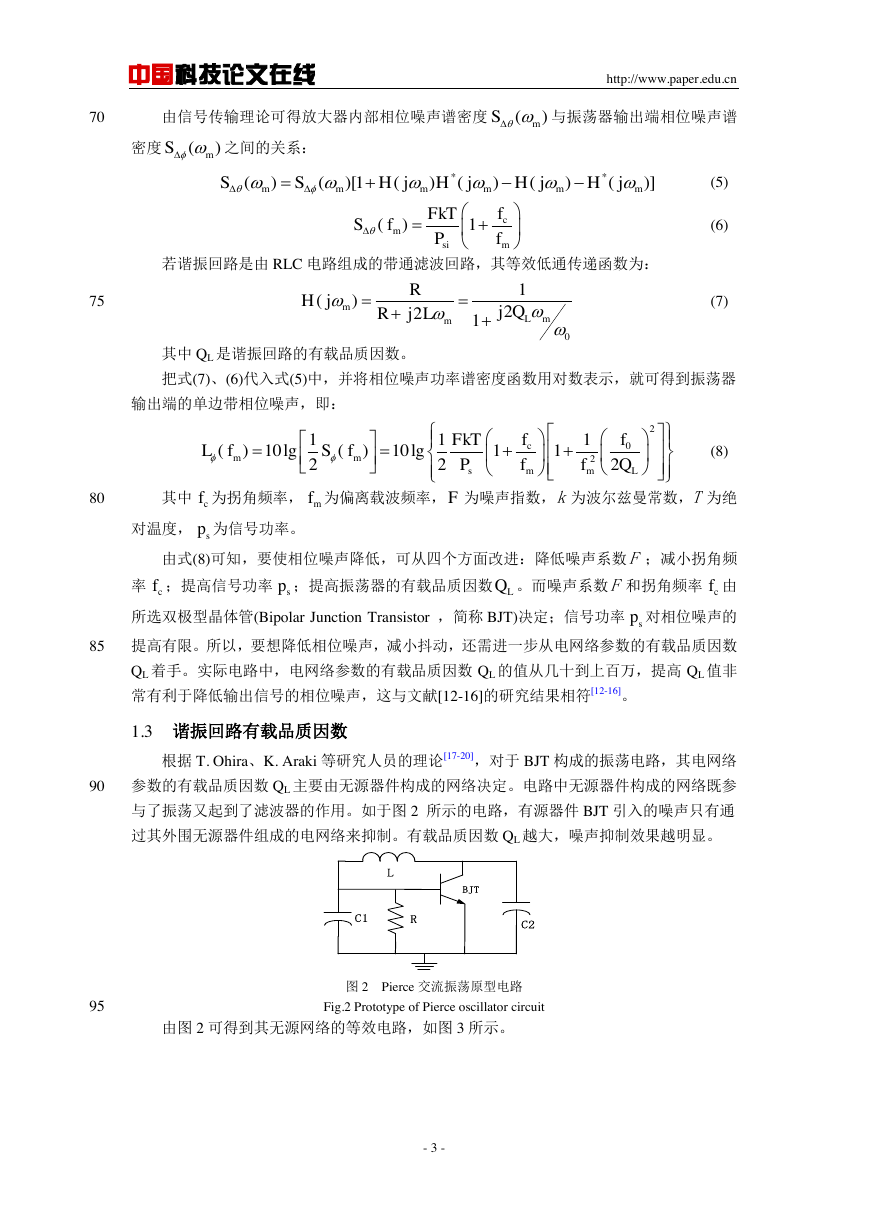

图 3 振荡电路无源网络的等效电路图

Fig.3 Equivalent circuit of passive network

100

该无源网络对应的阻抗矩阵为:

105

则可得 Z11 和 Z12 表达式如下:

(9)

(10)

(11)

由于 BJT 是电流控制电流源(VCCS)器件,根据参考文献[16],则有:

(12)

由此可见,该电路的有载品质因数 QL 与 C1 无关。在允许的范围内适当增加电感 L 和电

容 C2 有利于提高电路的有载品质因数 QL。

110

由(式 3)可知抖动与相位噪声功率谱密度有关,通过 Leeson 模型又可知电路无源网

络的有载品质因数 QL 是影响相位噪声的主要因素。所以,由(式 12)和(式 3),得到 Pierce 电

路的抖动与电网络参数的显性关系可以表示为:

(13)

其中 为三极管的噪声系数, 为波尔兹曼常数, 为绝对温度, 为放大电路的拐

115

角频率,通常为 3~5KHz[21], 和 为偏离载波频率, 为信号功率, 和 是谐振回

路的电感和电容。

2 系统电路实现与实验验证

由(式 13)可知,要获得良好的低抖动特性,就需要尽量选择低噪声系数、低拐

角频率的 BJT,谐振电路中的电感 和电容 对抖动的降低有比较明显的贡献。在允许的

- 4 -

C1C2LR222221211112RRLCRZRRjLLRCjRCjRCLC2211221112RRLCZjRCjRCLC12221112RZjRCjRCLC00222001102121ln22LdLCzQLCzd222220222222211012301222222022321285()(164)4()(164)scRMScFkTPfLCffffffLCJffffffLCfFkTcf1f2fspL2CL2C�

中国科技论文在线

http://www.paper.edu.cn

120

范围内,适当加大 和 的值有助于获得更好的低抖动性能。

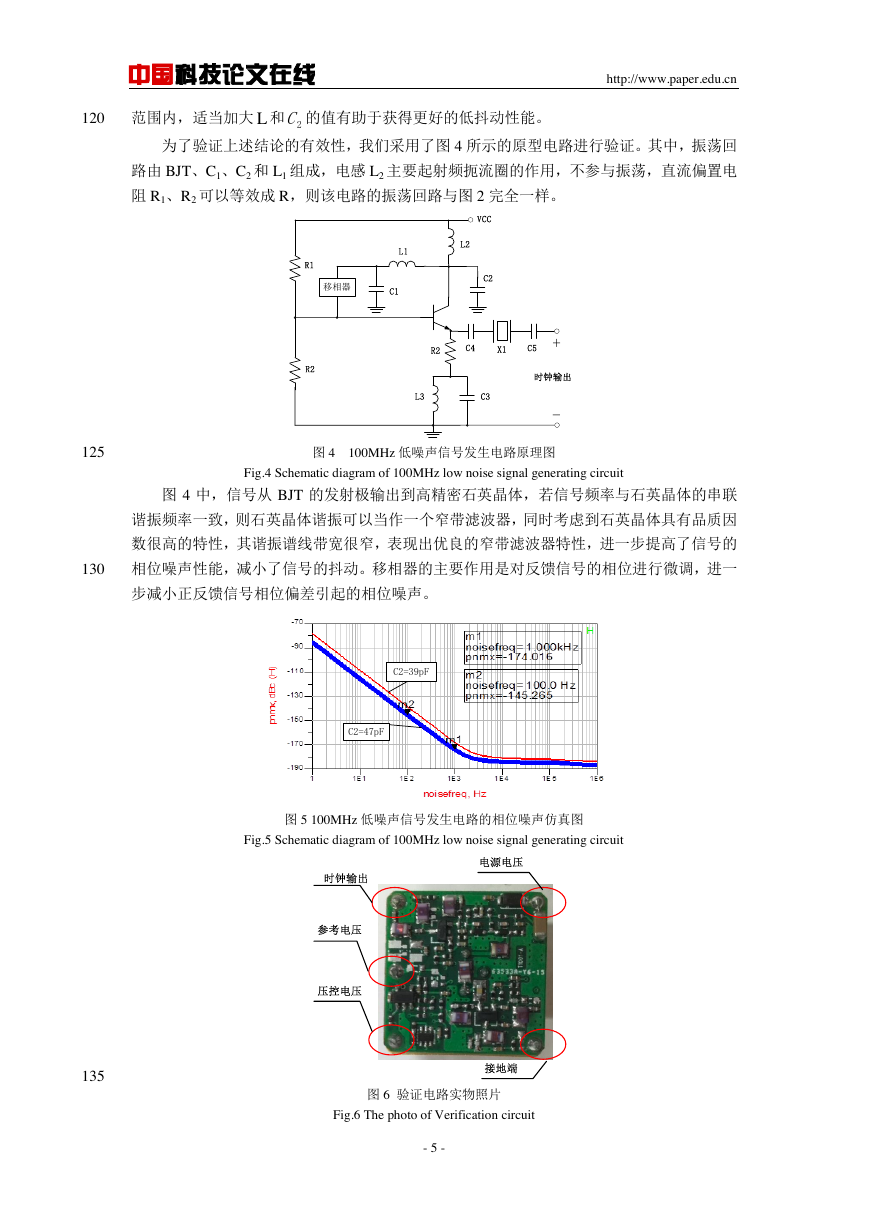

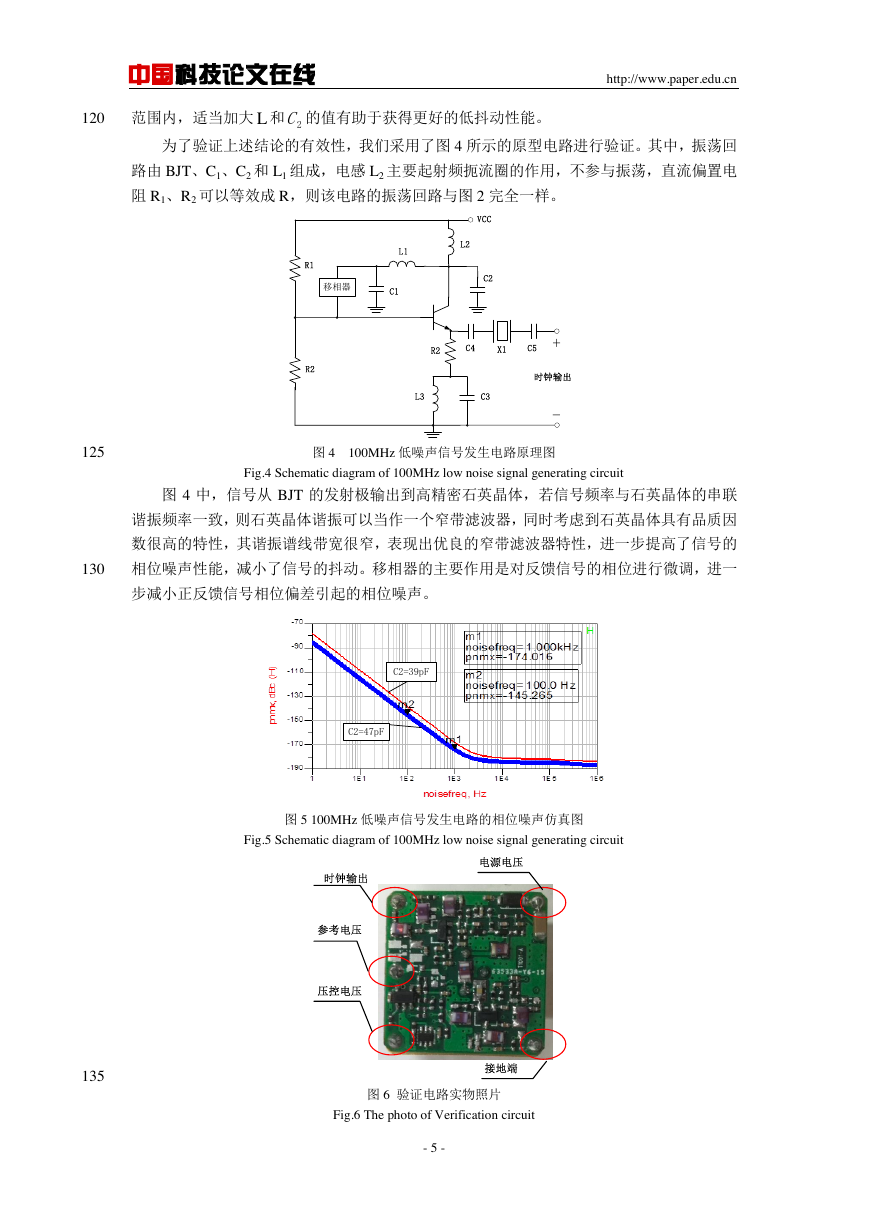

为了验证上述结论的有效性,我们采用了图 4 所示的原型电路进行验证。其中,振荡回

路由 BJT、C1、C2 和 L1 组成,电感 L2 主要起射频扼流圈的作用,不参与振荡,直流偏置电

阻 R1、R2 可以等效成 R,则该电路的振荡回路与图 2 完全一样。

125

图 4 100MHz 低噪声信号发生电路原理图

Fig.4 Schematic diagram of 100MHz low noise signal generating circuit

图 4 中,信号从 BJT 的发射极输出到高精密石英晶体,若信号频率与石英晶体的串联

谐振频率一致,则石英晶体谐振可以当作一个窄带滤波器,同时考虑到石英晶体具有品质因

数很高的特性,其谐振谱线带宽很窄,表现出优良的窄带滤波器特性,进一步提高了信号的

130

相位噪声性能,减小了信号的抖动。移相器的主要作用是对反馈信号的相位进行微调,进一

步减小正反馈信号相位偏差引起的相位噪声。

图 5 100MHz 低噪声信号发生电路的相位噪声仿真图

Fig.5 Schematic diagram of 100MHz low noise signal generating circuit

135

图 6 验证电路实物照片

Fig.6 The photo of Verification circuit

- 5 -

L2CR1R2移相器L1VCCC1R2L3C3C2X1C4C5+-时钟输出L2C2=47pFC2=39pF参考电压压控电压时钟输出电源电压接地端�

中国科技论文在线

http://www.paper.edu.cn

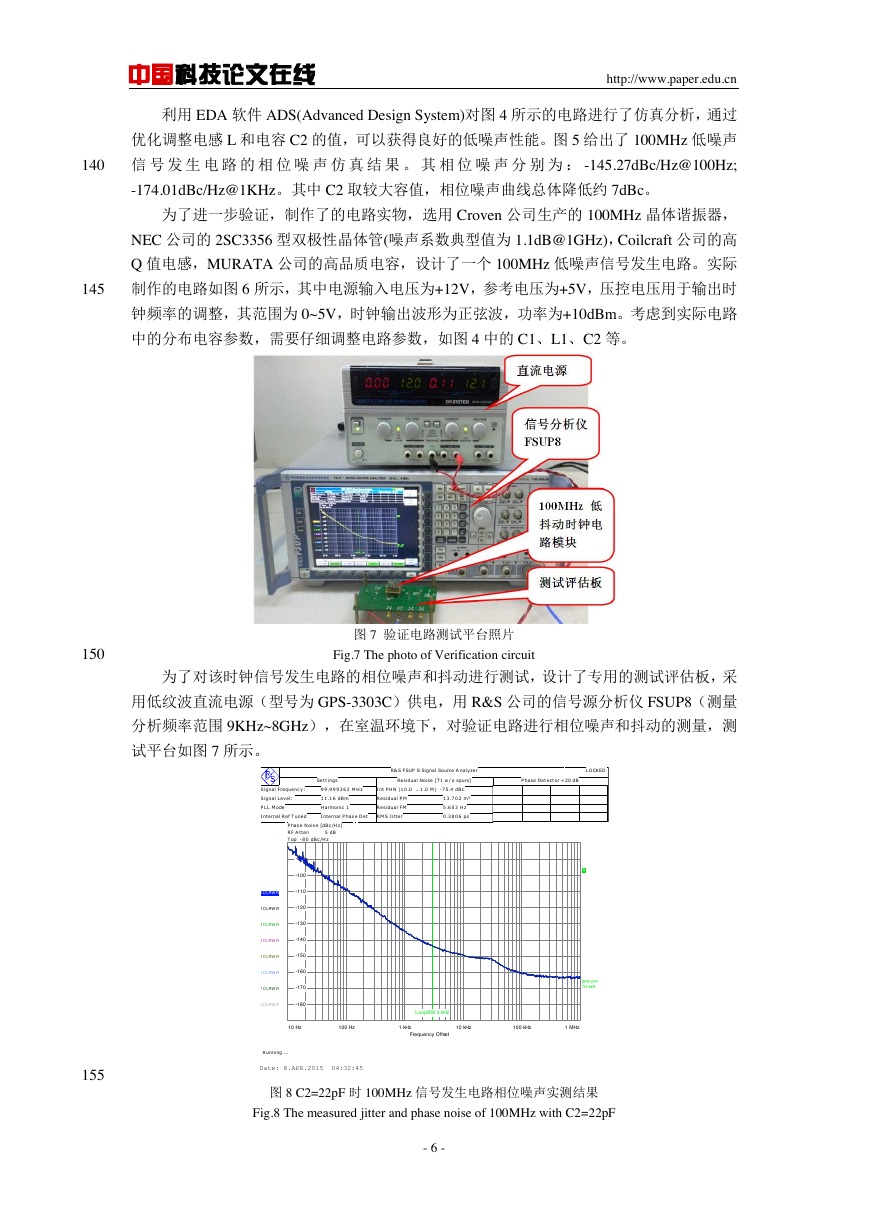

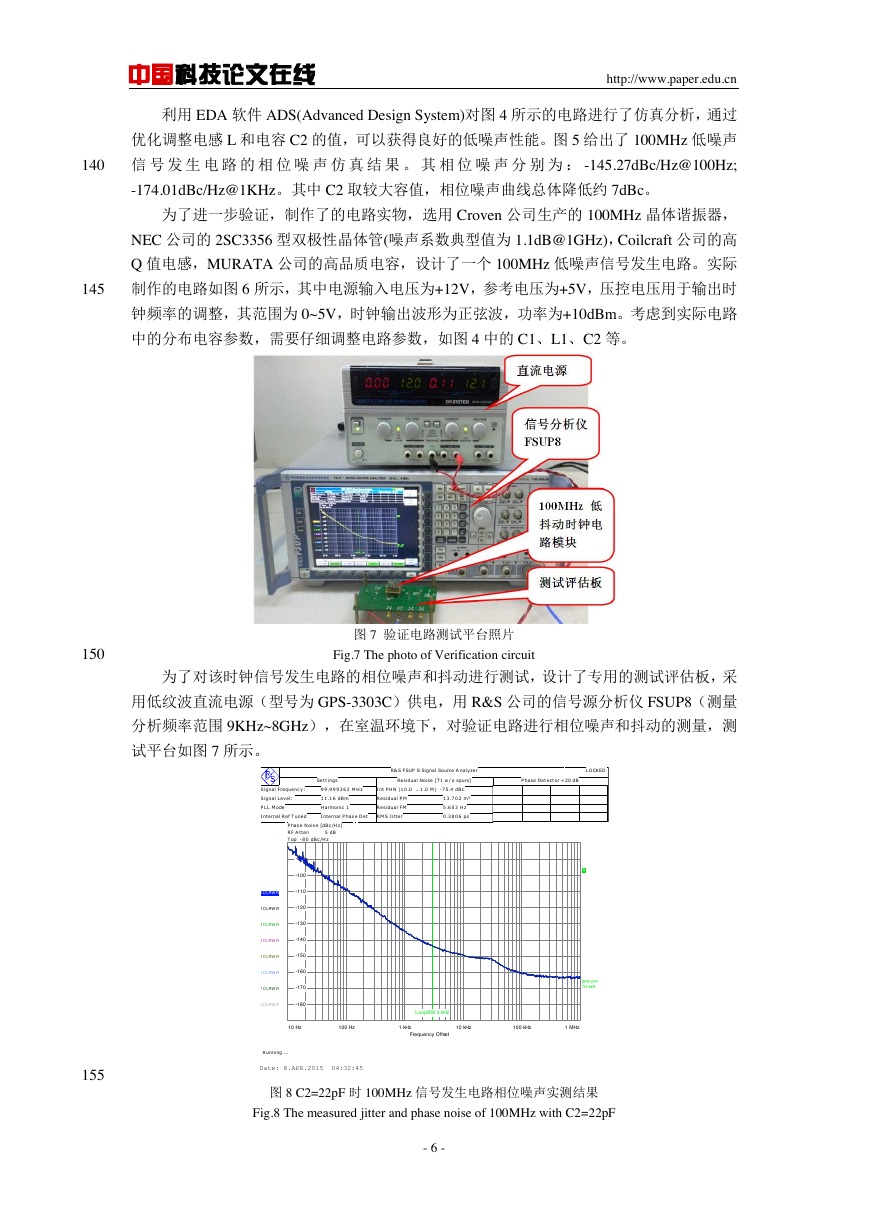

利用 EDA 软件 ADS(Advanced Design System)对图 4 所示的电路进行了仿真分析,通过

优化调整电感 L 和电容 C2 的值,可以获得良好的低噪声性能。图 5 给出了 100MHz 低噪声

140

信 号 发 生 电 路 的 相 位 噪 声 仿 真 结 果 。 其 相 位 噪 声 分 别 为 : -145.27dBc/Hz@100Hz;

-174.01dBc/Hz@1KHz。其中 C2 取较大容值,相位噪声曲线总体降低约 7dBc。

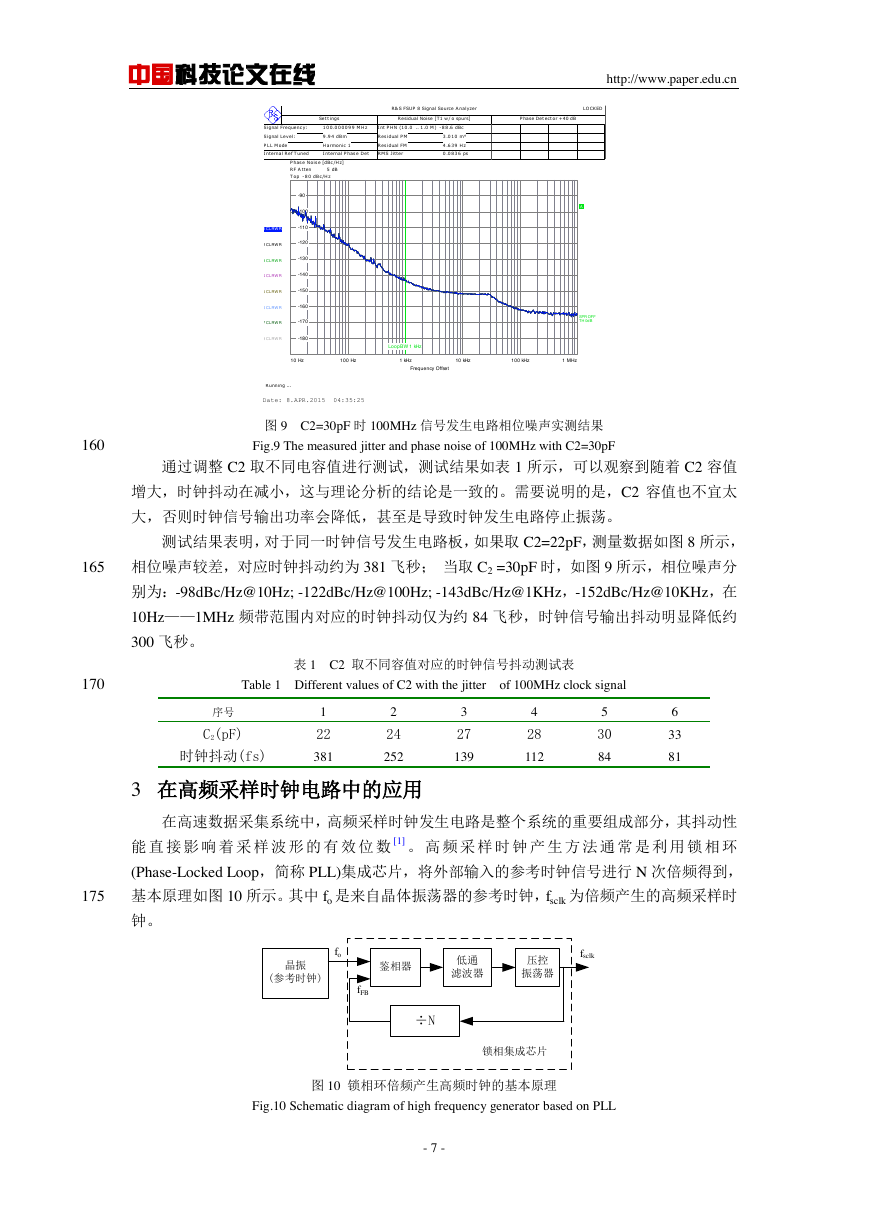

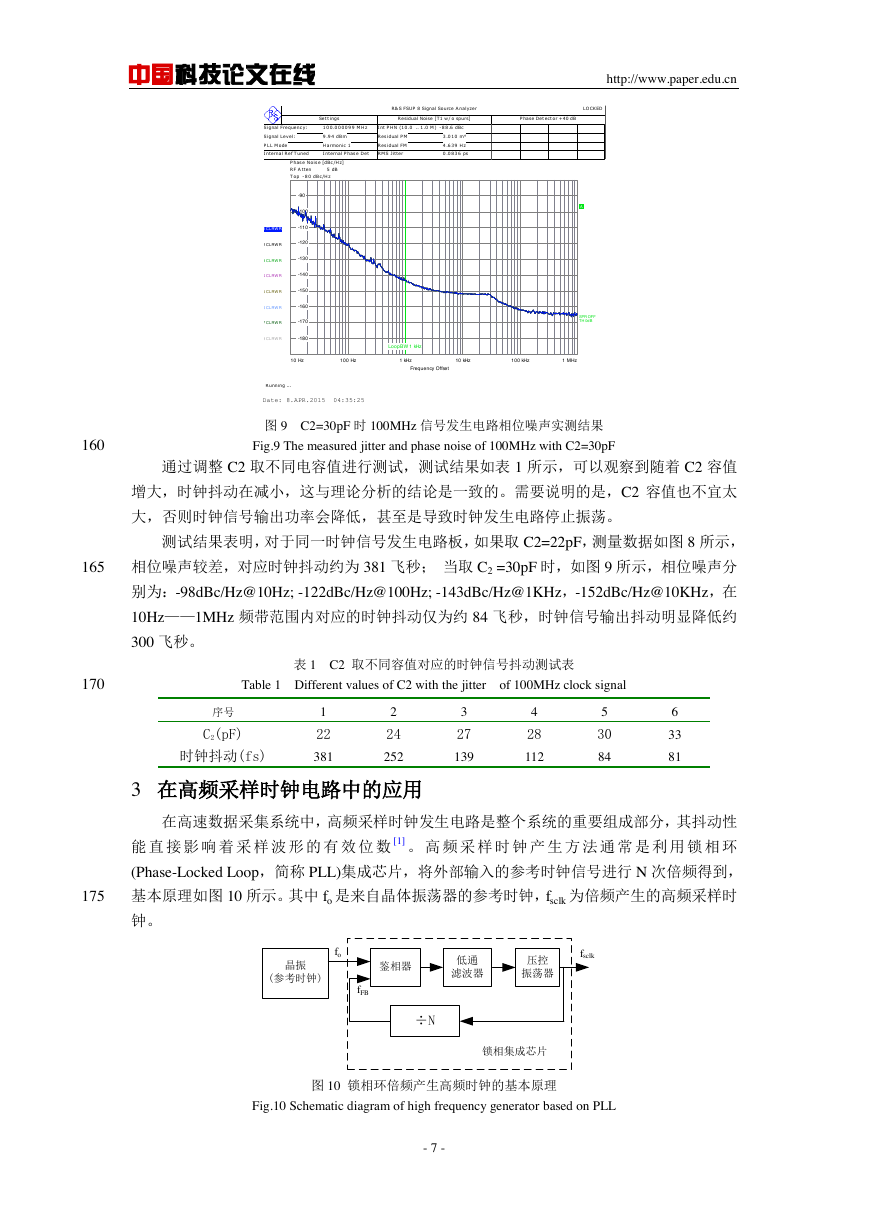

为了进一步验证,制作了的电路实物,选用 Croven 公司生产的 100MHz 晶体谐振器,

NEC 公司的 2SC3356 型双极性晶体管(噪声系数典型值为 1.1dB@1GHz),Coilcraft 公司的高

Q 值电感,MURATA 公司的高品质电容,设计了一个 100MHz 低噪声信号发生电路。实际

145

制作的电路如图 6 所示,其中电源输入电压为+12V,参考电压为+5V,压控电压用于输出时

钟频率的调整,其范围为 0~5V,时钟输出波形为正弦波,功率为+10dBm。考虑到实际电路

中的分布电容参数,需要仔细调整电路参数,如图 4 中的 C1、L1、C2 等。

150

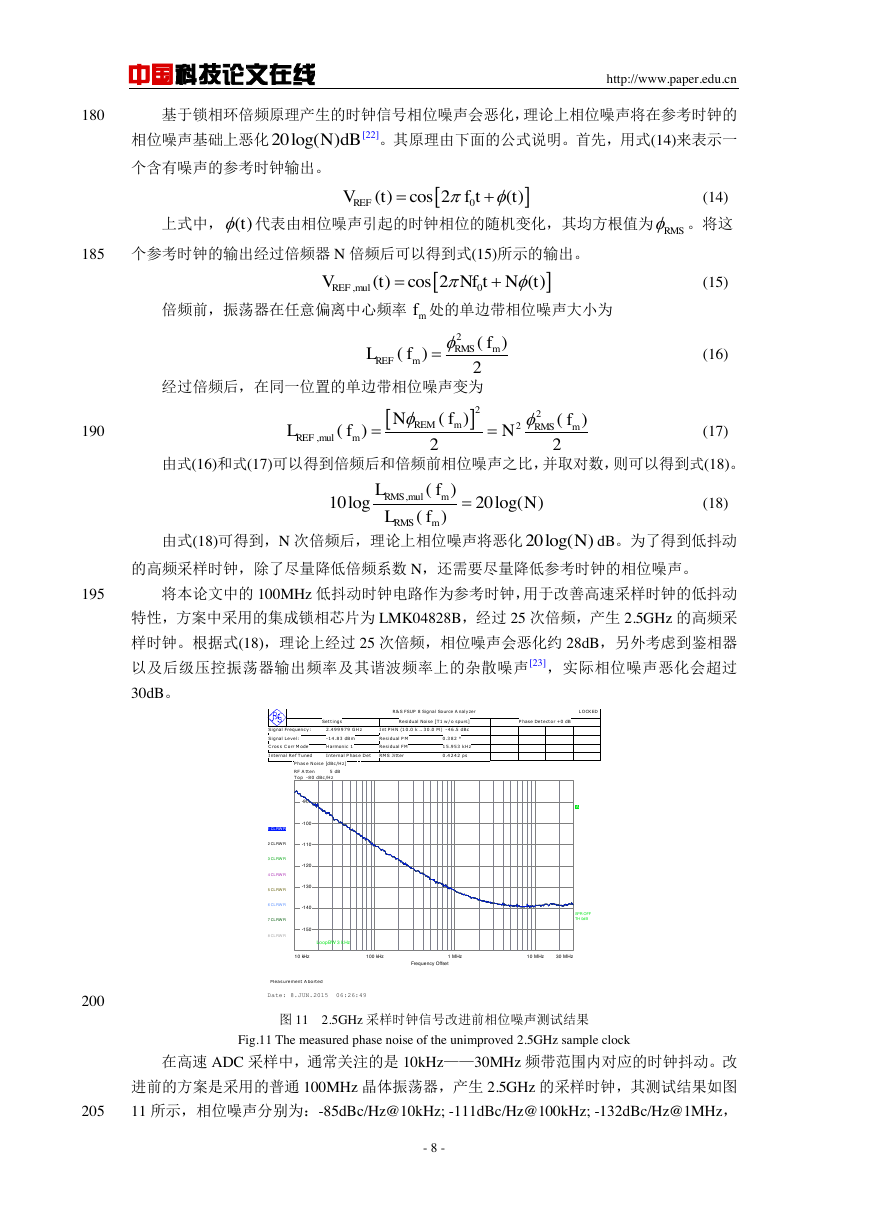

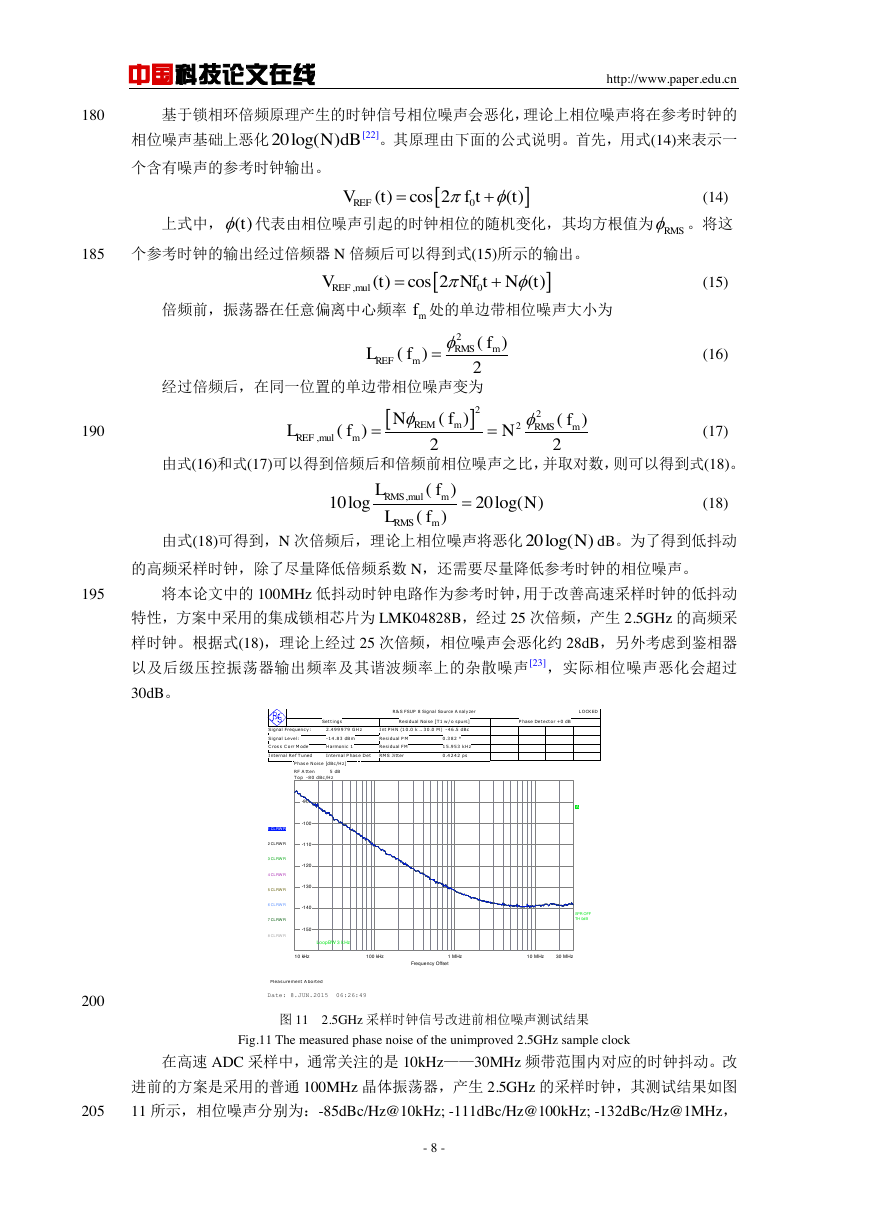

图 7 验证电路测试平台照片

Fig.7 The photo of Verification circuit

为了对该时钟信号发生电路的相位噪声和抖动进行测试,设计了专用的测试评估板,采

用低纹波直流电源(型号为 GPS-3303C)供电,用 R&S 公司的信号源分析仪 FSUP8(测量

分析频率范围 9KHz~8GHz),在室温环境下,对验证电路进行相位噪声和抖动的测量,测

试平台如图 7 所示。

155

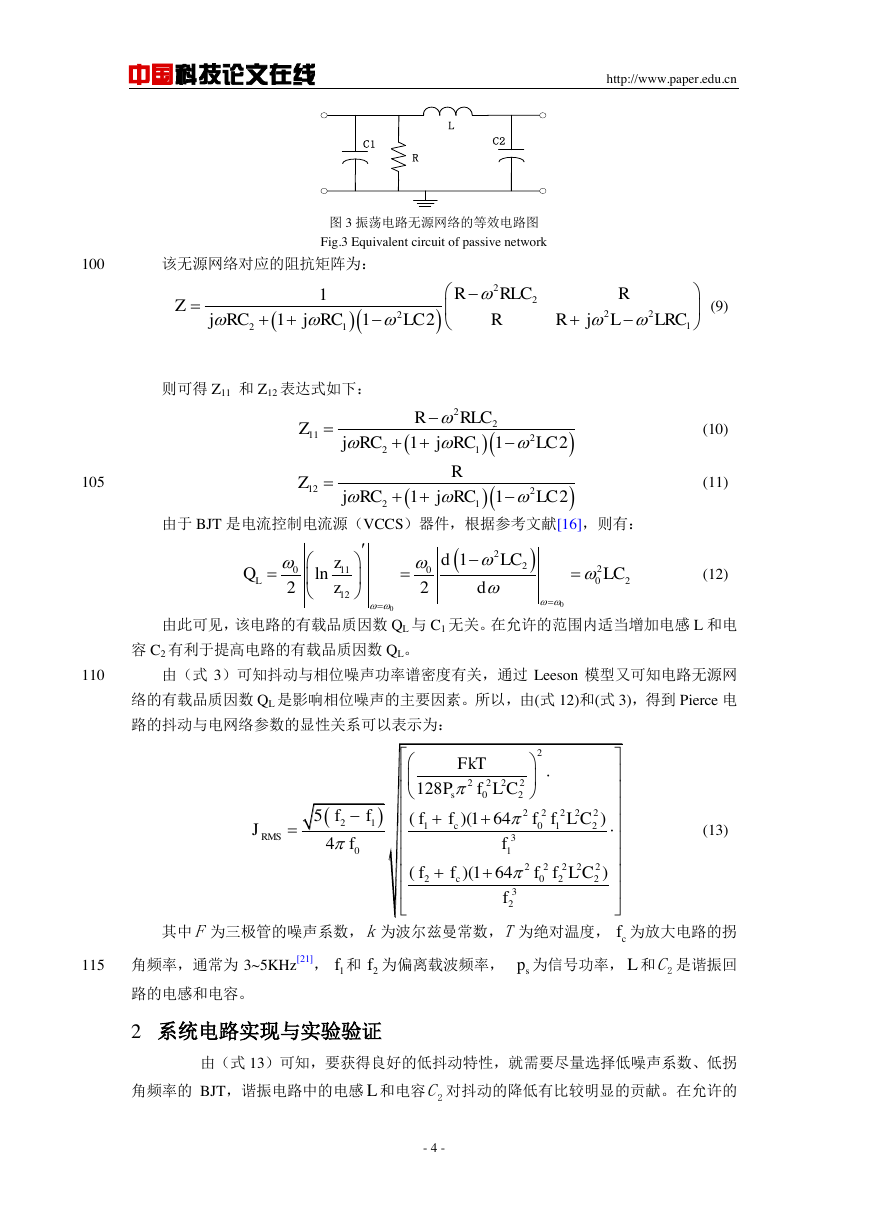

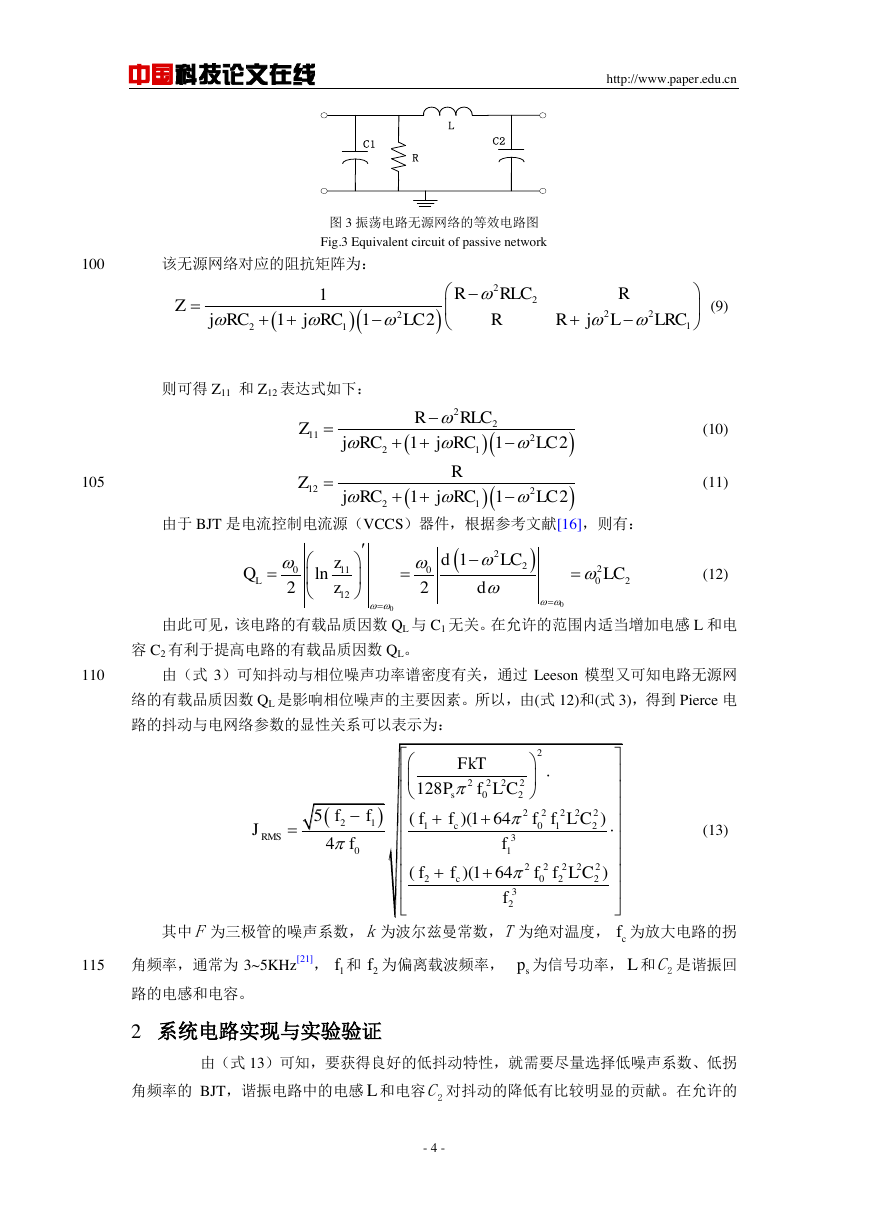

图 8 C2=22pF 时 100MHz 信号发生电路相位噪声实测结果

Fig.8 The measured jitter and phase noise of 100MHz with C2=22pF

- 6 -

Running ... R&S FSUP 8 Signal Source Analyzer LOCKED SettingsResidual Noise [T1 w/o spurs]Phase Detector +20 dBSignal Frequency:99.999362 MHzInt PHN (10.0 .. 1.0 M) -75.4 dBc Signal Level: 11.16 dBmResidual PM13.702 m° PLL ModeHarmonic 1Residual FM5.653 Hz Internal Ref TunedInternal Phase DetRMS Jitter0.3806 ps Phase Noise [dBc/Hz] RF Atten5 dB Top-80 dBc/Hz 100 Hz1 kHz10 kHz100 kHz10 Hz1 MHz-180-170-160-150-140-130-120-110-100-90LoopBW 3 kHz1 CLRWR2 CLRWR3 CLRWR4 CLRWR5 CLRWR6 CLRWR7 CLRWR8 CLRWR A SPR OFFTH 0dBFrequency OffsetDate: 8.APR.2015 04:32:45�

中国科技论文在线

http://www.paper.edu.cn

图 9 C2=30pF 时 100MHz 信号发生电路相位噪声实测结果

160

Fig.9 The measured jitter and phase noise of 100MHz with C2=30pF

通过调整 C2 取不同电容值进行测试,测试结果如表 1 所示,可以观察到随着 C2 容值

增大,时钟抖动在减小,这与理论分析的结论是一致的。需要说明的是,C2 容值也不宜太

大,否则时钟信号输出功率会降低,甚至是导致时钟发生电路停止振荡。

165

测试结果表明,对于同一时钟信号发生电路板,如果取 C2=22pF,测量数据如图 8 所示,

相位噪声较差,对应时钟抖动约为 381 飞秒; 当取 C2 =30pF 时,如图 9 所示,相位噪声分

别为:-98dBc/Hz@10Hz; -122dBc/Hz@100Hz; -143dBc/Hz@1KHz,-152dBc/Hz@10KHz,在

10Hz——1MHz 频带范围内对应的时钟抖动仅为约 84 飞秒,时钟信号输出抖动明显降低约

300 飞秒。

170

Table 1 Different values of C2 with the jitter of 100MHz clock signal

表 1 C2 取不同容值对应的时钟信号抖动测试表

序号

C2(pF)

时钟抖动(fs)

1

22

381

2

24

252

3

27

139

4

28

112

5

30

84

6

33

81

3 在高频采样时钟电路中的应用

在高速数据采集系统中,高频采样时钟发生电路是整个系统的重要组成部分,其抖动性

能 直 接 影 响 着 采 样 波 形 的 有 效 位 数 [1] 。 高 频 采 样 时 钟 产 生 方 法 通 常 是 利 用 锁 相 环

175

(Phase-Locked Loop,简称 PLL)集成芯片,将外部输入的参考时钟信号进行 N 次倍频得到,

基本原理如图 10 所示。其中 fo 是来自晶体振荡器的参考时钟,fsclk 为倍频产生的高频采样时

钟。

图 10 锁相环倍频产生高频时钟的基本原理

Fig.10 Schematic diagram of high frequency generator based on PLL

- 7 -

Running ... R&S FSUP 8 Signal Source Analyzer LOCKED SettingsResidual Noise [T1 w/o spurs]Phase Detector +40 dBSignal Frequency:100.000099 MHzInt PHN (10.0 .. 1.0 M) -88.6 dBc Signal Level: 9.94 dBmResidual PM3.010 m° PLL ModeHarmonic 1Residual FM4.639 Hz Internal Ref TunedInternal Phase DetRMS Jitter0.0836 ps Phase Noise [dBc/Hz] RF Atten5 dB Top-80 dBc/Hz 100 Hz1 kHz10 kHz100 kHz10 Hz1 MHz-180-170-160-150-140-130-120-110-100-90LoopBW 1 kHz1 CLRWR2 CLRWR3 CLRWR4 CLRWR5 CLRWR6 CLRWR7 CLRWR8 CLRWR A SPR OFFTH 0dBFrequency OffsetDate: 8.APR.2015 04:35:25晶振(参考时钟)鉴相器低通滤波器压控振荡器÷NfofFBfsclk锁相集成芯片�

中国科技论文在线

http://www.paper.edu.cn

180

基于锁相环倍频原理产生的时钟信号相位噪声会恶化,理论上相位噪声将在参考时钟的

[22]。其原理由下面的公式说明。首先,用式(14)来表示一

相位噪声基础上恶化

个含有噪声的参考时钟输出。

(14)

上式中,

代表由相位噪声引起的时钟相位的随机变化,其均方根值为

。将这

185

个参考时钟的输出经过倍频器 N 倍频后可以得到式(15)所示的输出。

190

倍频前,振荡器在任意偏离中心频率 处的单边带相位噪声大小为

经过倍频后,在同一位置的单边带相位噪声变为

(15)

(16)

由式(16)和式(17)可以得到倍频后和倍频前相位噪声之比,并取对数,则可以得到式(18)。

(17)

(18)

由式(18)可得到,N 次倍频后,理论上相位噪声将恶化

dB。为了得到低抖动

的高频采样时钟,除了尽量降低倍频系数 N,还需要尽量降低参考时钟的相位噪声。

195

将本论文中的 100MHz 低抖动时钟电路作为参考时钟,用于改善高速采样时钟的低抖动

特性,方案中采用的集成锁相芯片为 LMK04828B,经过 25 次倍频,产生 2.5GHz 的高频采

样时钟。根据式(18),理论上经过 25 次倍频,相位噪声会恶化约 28dB,另外考虑到鉴相器

以及后级压控振荡器输出频率及其谐波频率上的杂散噪声[23],实际相位噪声恶化会超过

30dB。

200

图 11 2.5GHz 采样时钟信号改进前相位噪声测试结果

Fig.11 The measured phase noise of the unimproved 2.5GHz sample clock

在高速 ADC 采样中,通常关注的是 10kHz——30MHz 频带范围内对应的时钟抖动。改

进前的方案是采用的普通 100MHz 晶体振荡器,产生 2.5GHz 的采样时钟,其测试结果如图

205

11 所示,相位噪声分别为:-85dBc/Hz@10kHz; -111dBc/Hz@100kHz; -132dBc/Hz@1MHz,

- 8 -

20log()NdB0()cos2()REFVtftt()tRMS,0()cos2()REFmulVtNftNtmf2()()2RMSmREFmfLf222,()()()22REMmRMSmREFmulmNffLfN,()10log20log()()RMSmulmRMSmLfNLf20log()N Measurement Aborted R&S FSUP 8 Signal Source Analyzer LOCKED SettingsResidual Noise [T1 w/o spurs]Phase Detector +0 dBSignal Frequency:2.499979 GHzInt PHN (10.0 k .. 30.0 M) -46.5 dBc Signal Level: -14.83 dBmResidual PM0.382 ° Cross Corr ModeHarmonic 1Residual FM15.953 kHz Internal Ref TunedInternal Phase DetRMS Jitter0.4242 ps Phase Noise [dBc/Hz] RF Atten5 dB Top-80 dBc/Hz 100 kHz1 MHz10 MHz10 kHz30 MHz-150-140-130-120-110-100-90LoopBW 3 kHz1 CLRWR2 CLRWR3 CLRWR4 CLRWR5 CLRWR6 CLRWR7 CLRWR8 CLRWR A SPR OFFTH 0dBFrequency OffsetDate: 8.JUN.2015 06:26:49�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc