数字集成电路低功耗物理实现技术与UPF

摘要

1.0 概述

2.0 CMOS电路的低功耗设计原理

3.0 低功耗设计手段及Library需求

3.1 0.18um及以上工艺

3.1.1 静态功耗可以忽略

3.1.2 时钟门控减小不必要的动态功耗

图 3�1 时钟门控原理图

3.1.2.1. Clock Gating Cells

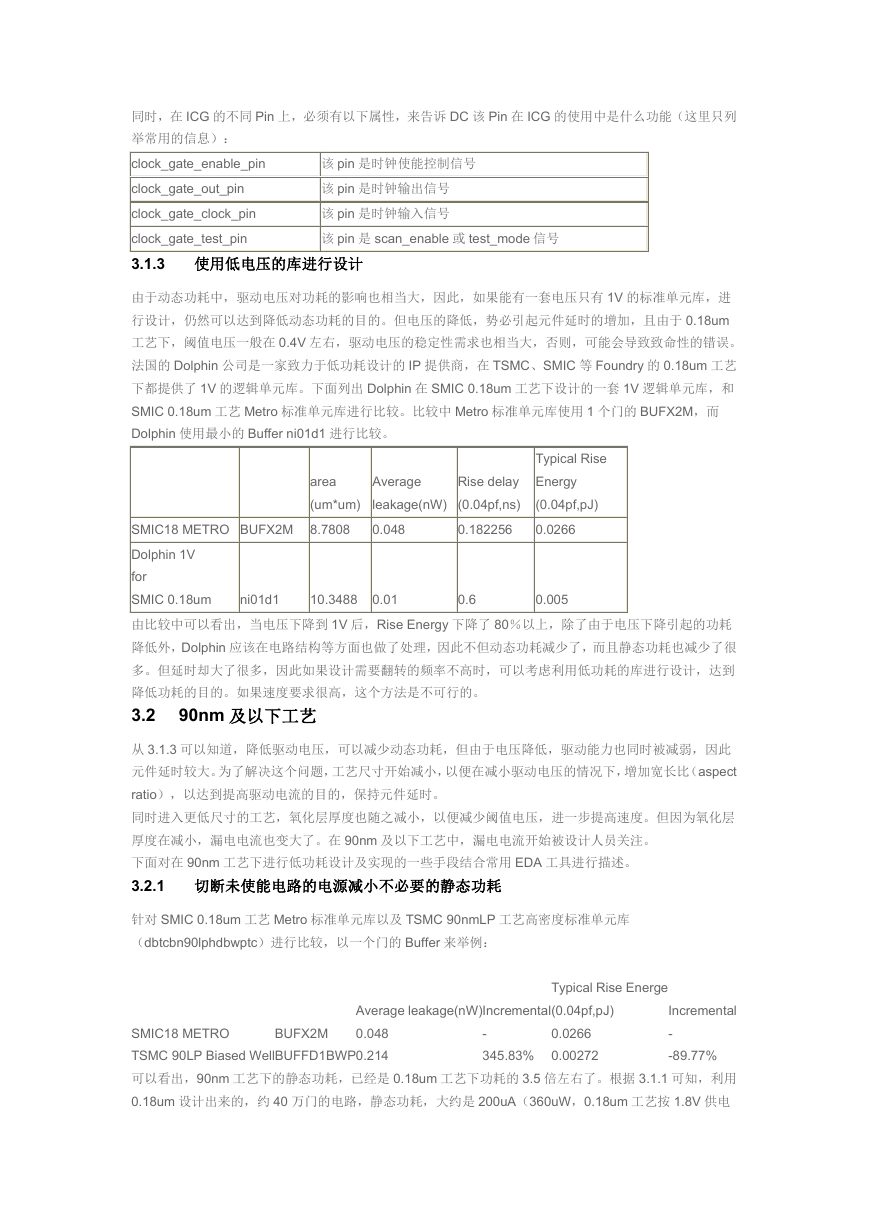

3.1.3 使用低电压的库进行设计

3.2 90nm及以下工艺

3.2.1 切断未使能电路的电源减小不必要的静态功耗

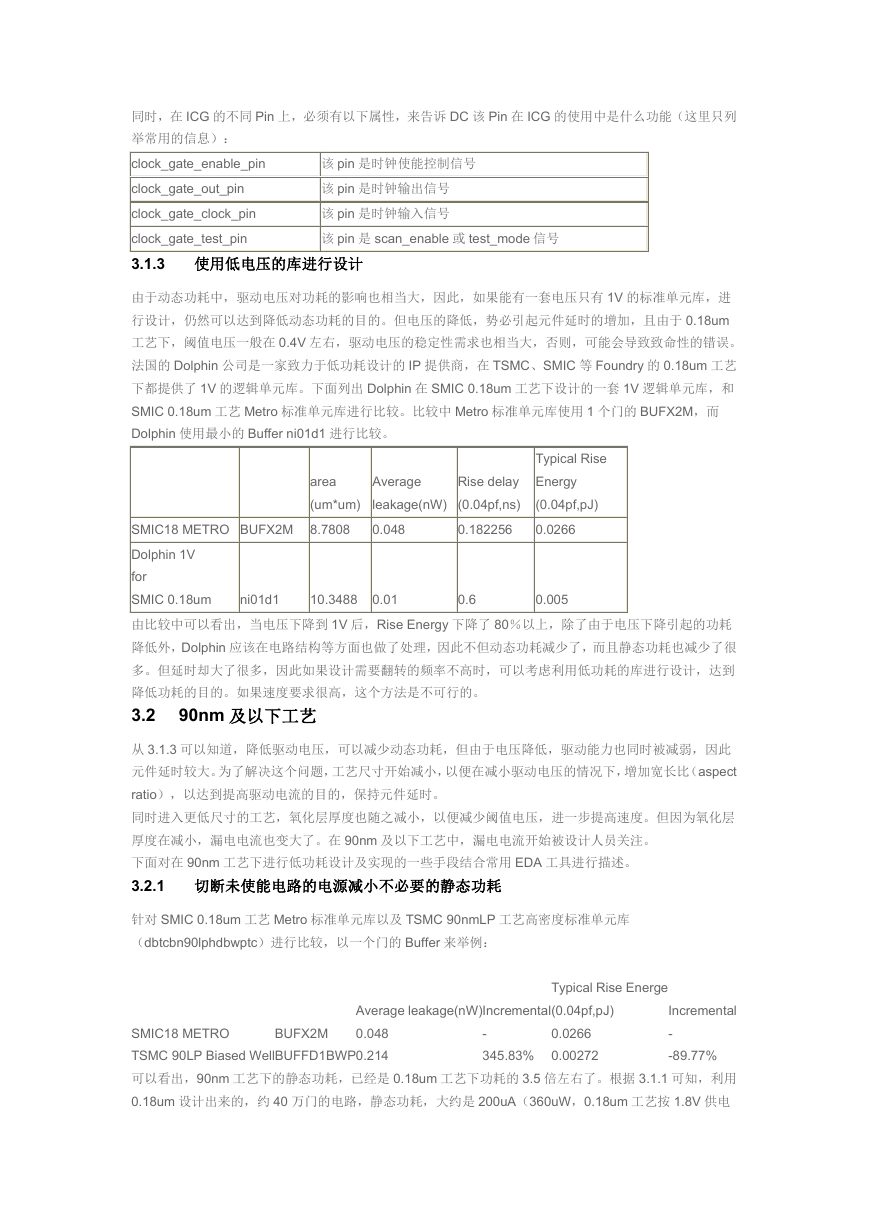

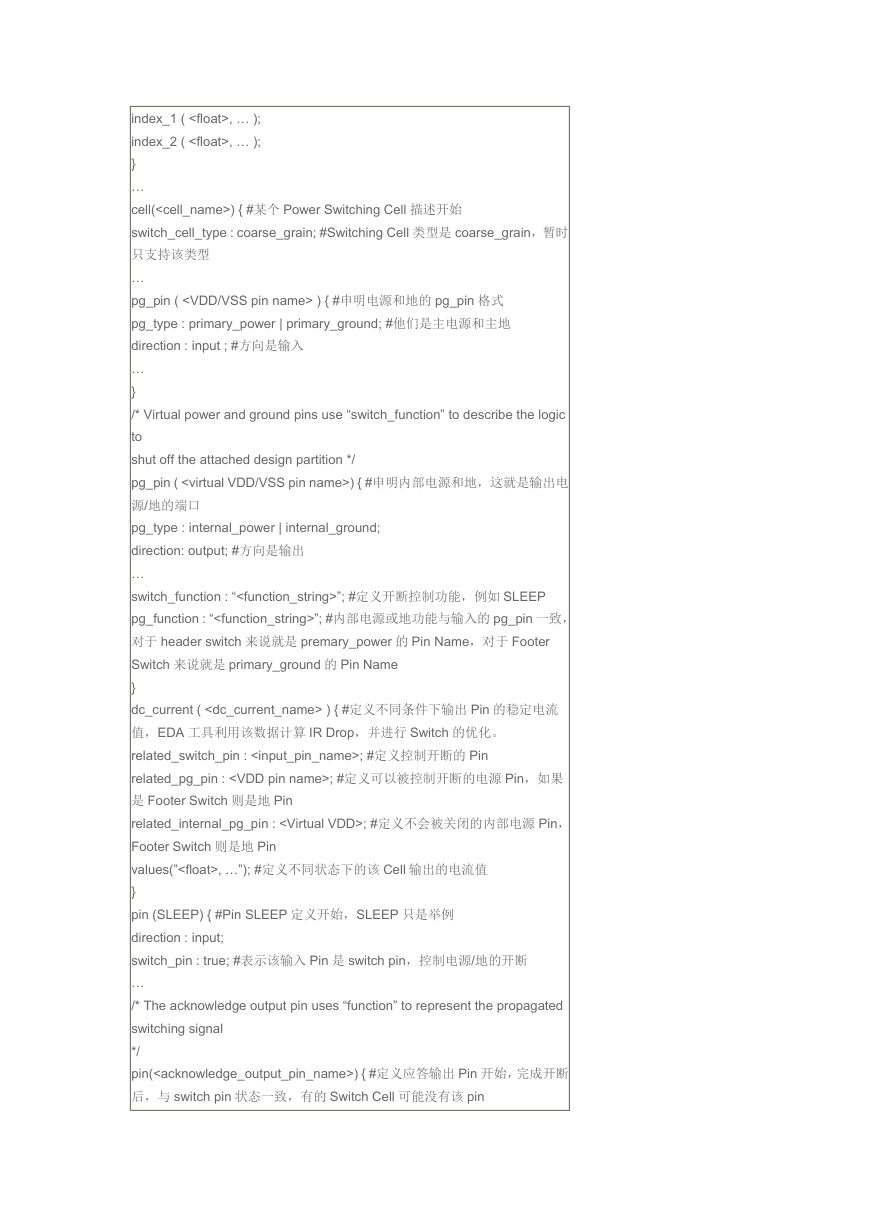

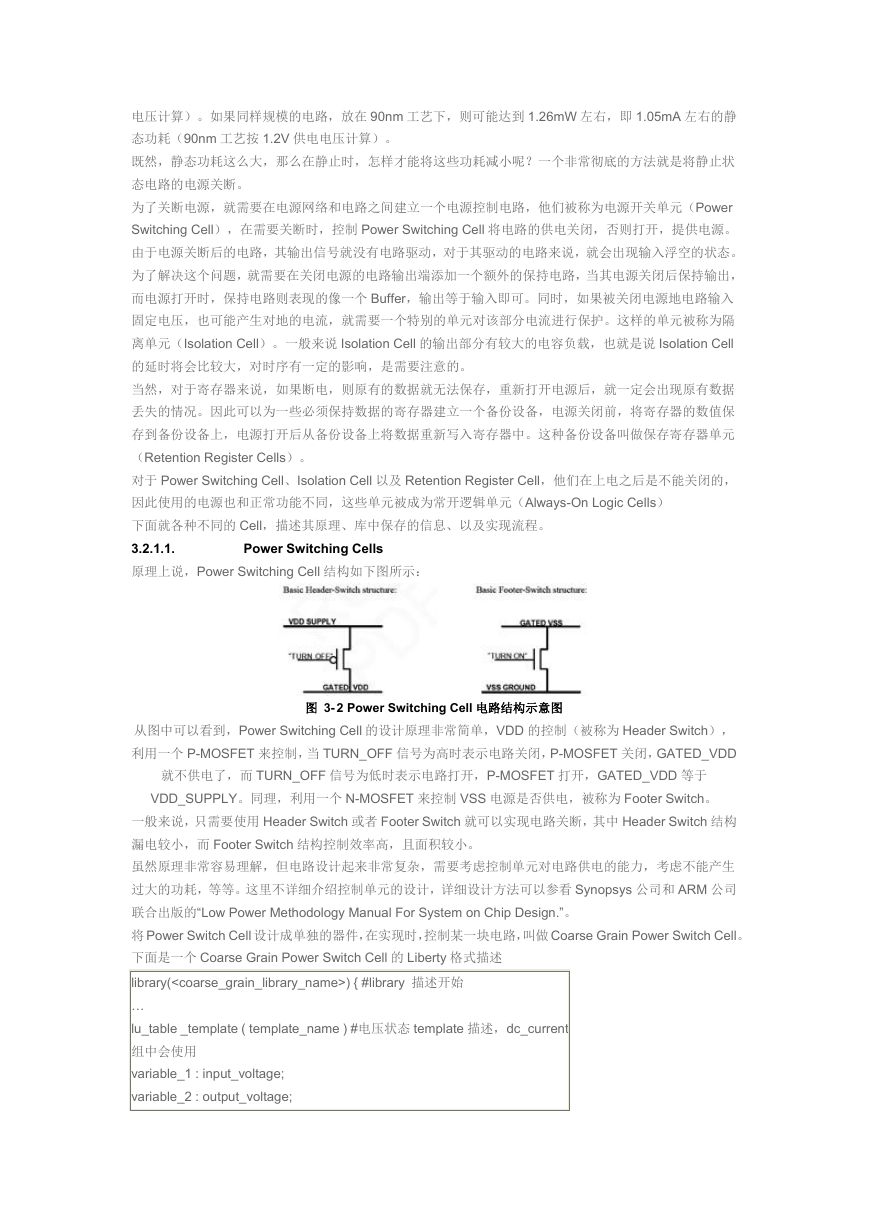

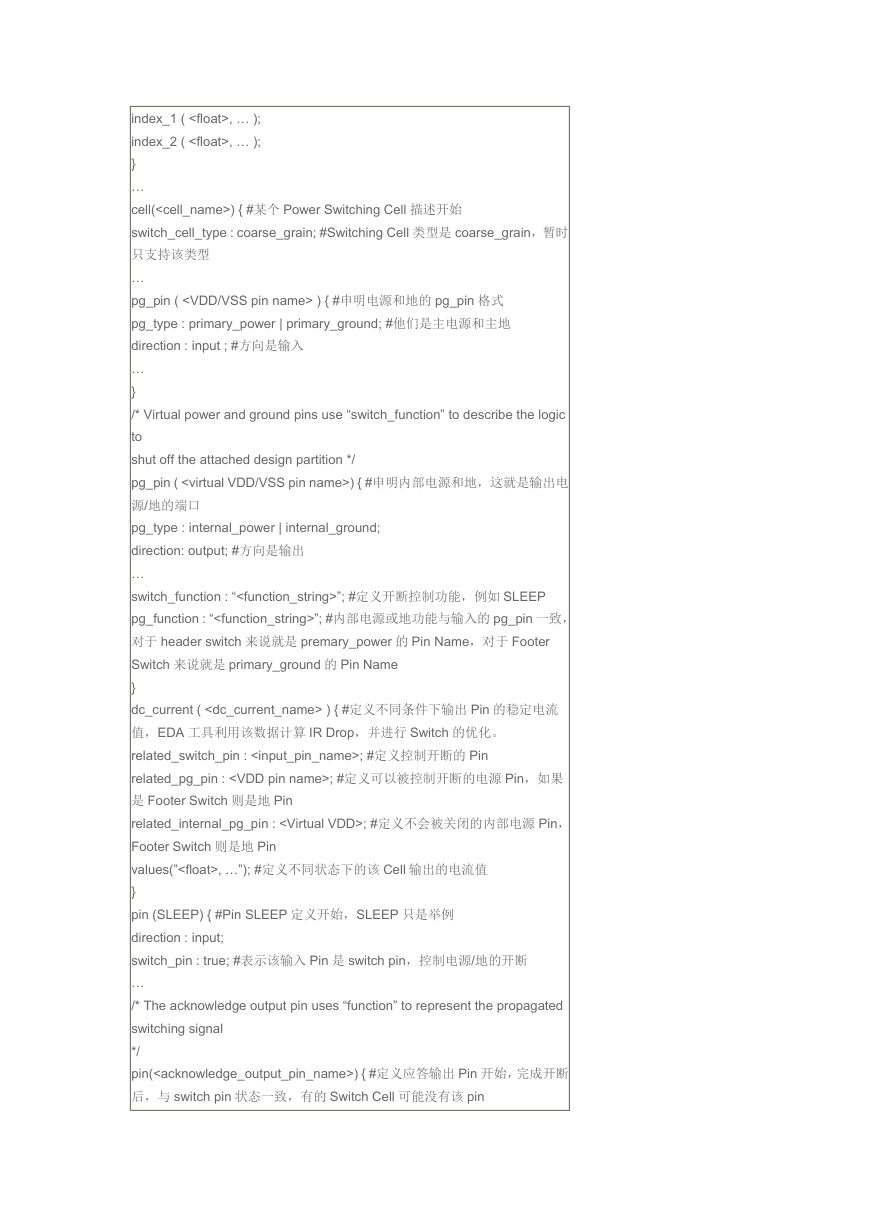

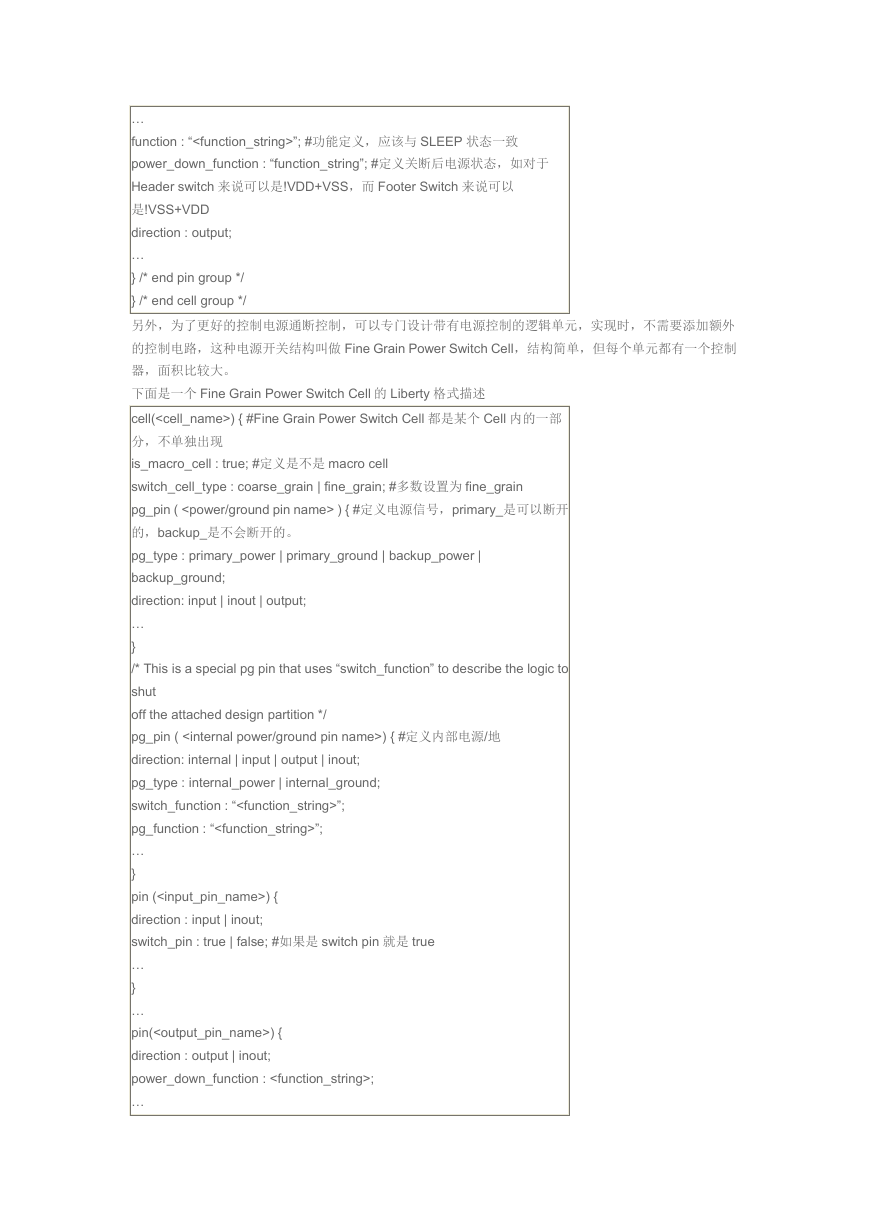

3.2.1.1. Power Switching Cells

图 3�2 Power Switching Cell电路结构示意图

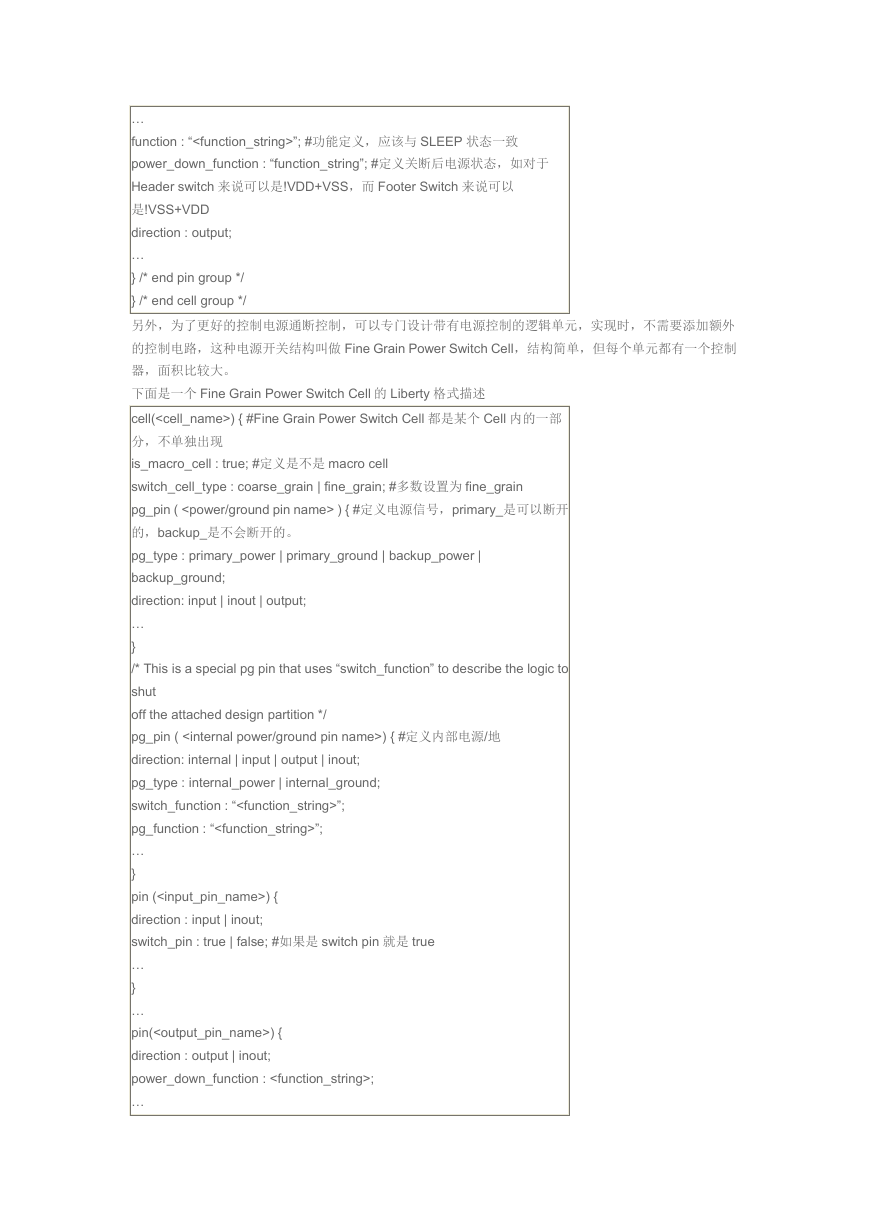

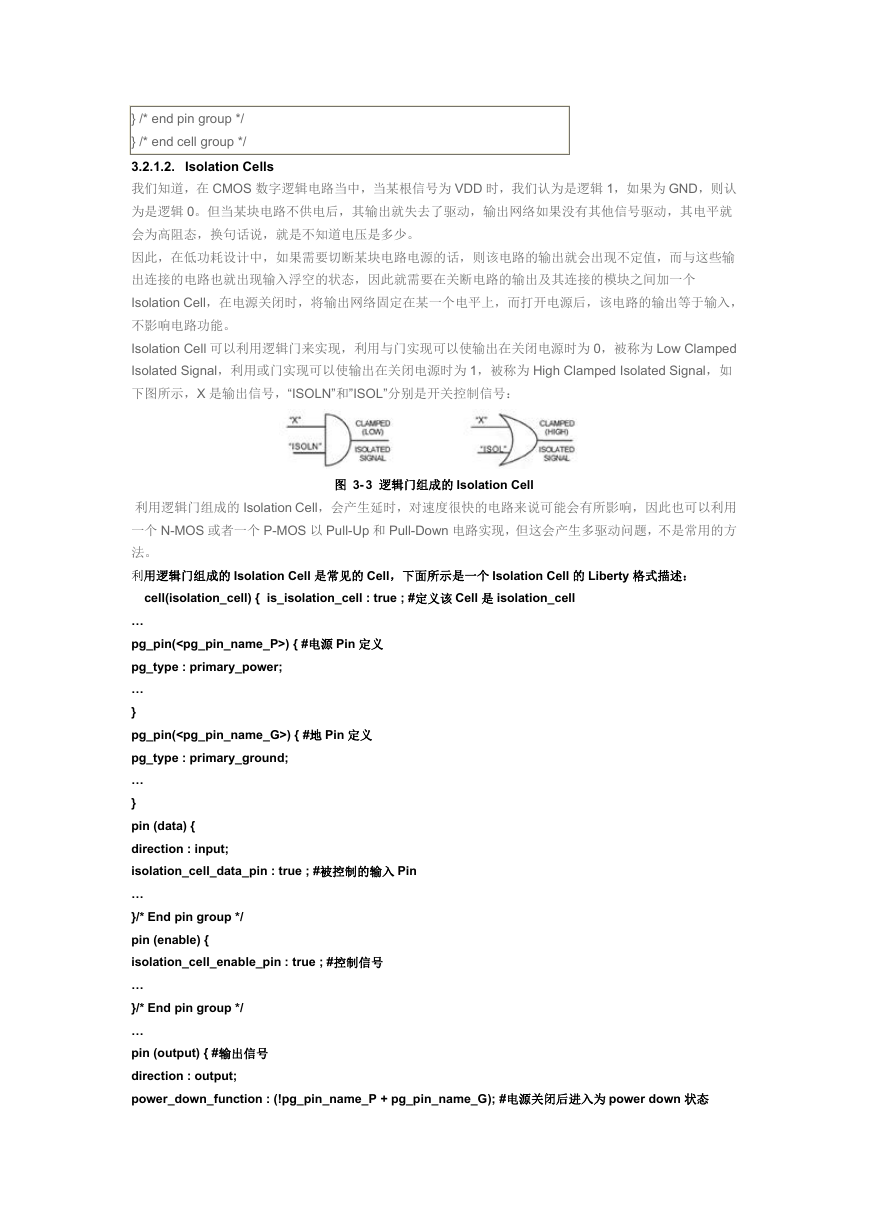

3.2.1.2. Isolation Cells

图 3�3 逻辑门组成的Isolation Cell

利用逻辑门组成的Isolation Cell是常见的Cell,下面所示是一个Isolation Ce

cell(isolation_cell) { is_isolation_cell : tru

…

pg_type : primary_power;

…

}

pg_type : primary_ground;

…

}

pin (data) {

direction : input;

isolation_cell_data_pin : true ; #被控制的输入Pin

…

}/* End pin group */

pin (enable) {

isolation_cell_enable_pin : true ; #控制信号

…

}/* End pin group */

…

pin (output) { #输出信号

direction : output;

power_down_function : (!pg_pin_name_P + pg_pin_nam

…

}/* End pin group */

}/* End Cell group */

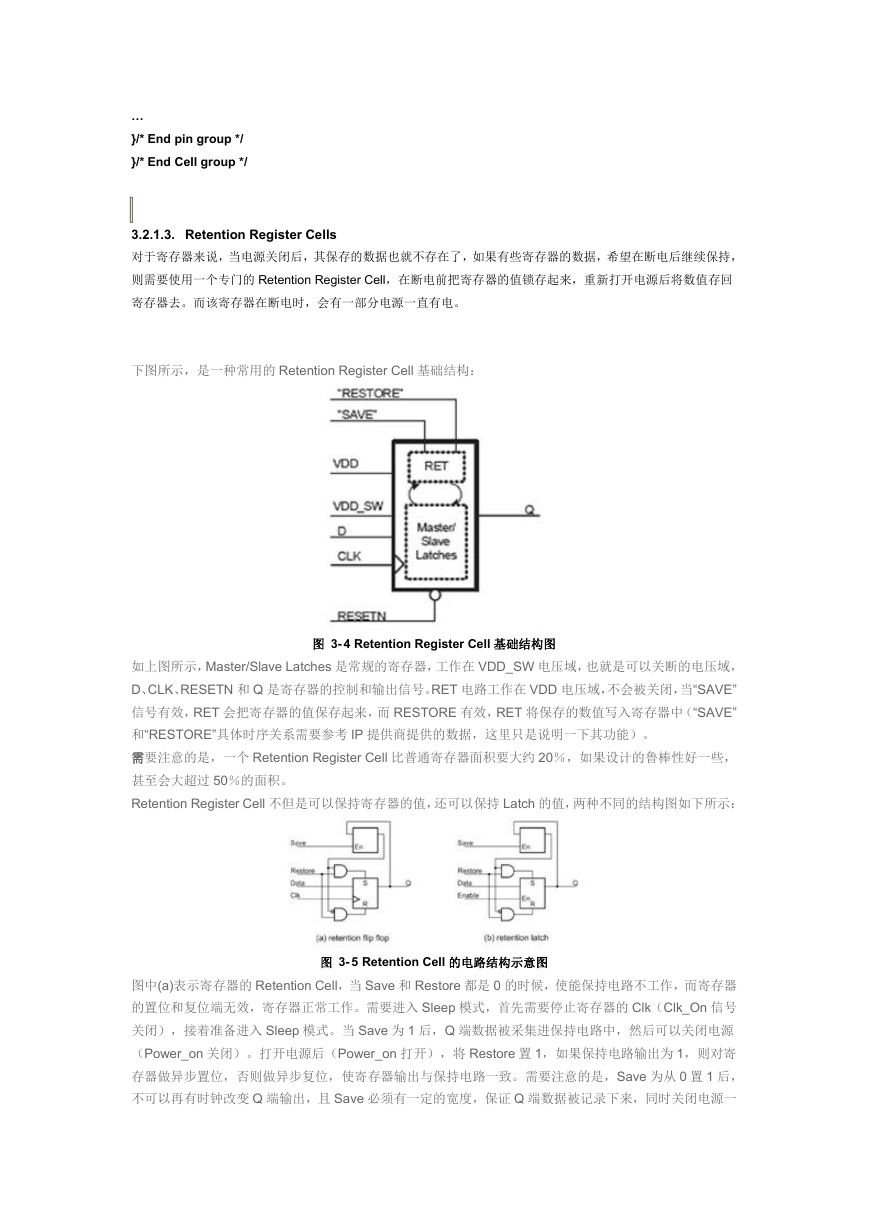

3.2.1.3. Retention Register Cells

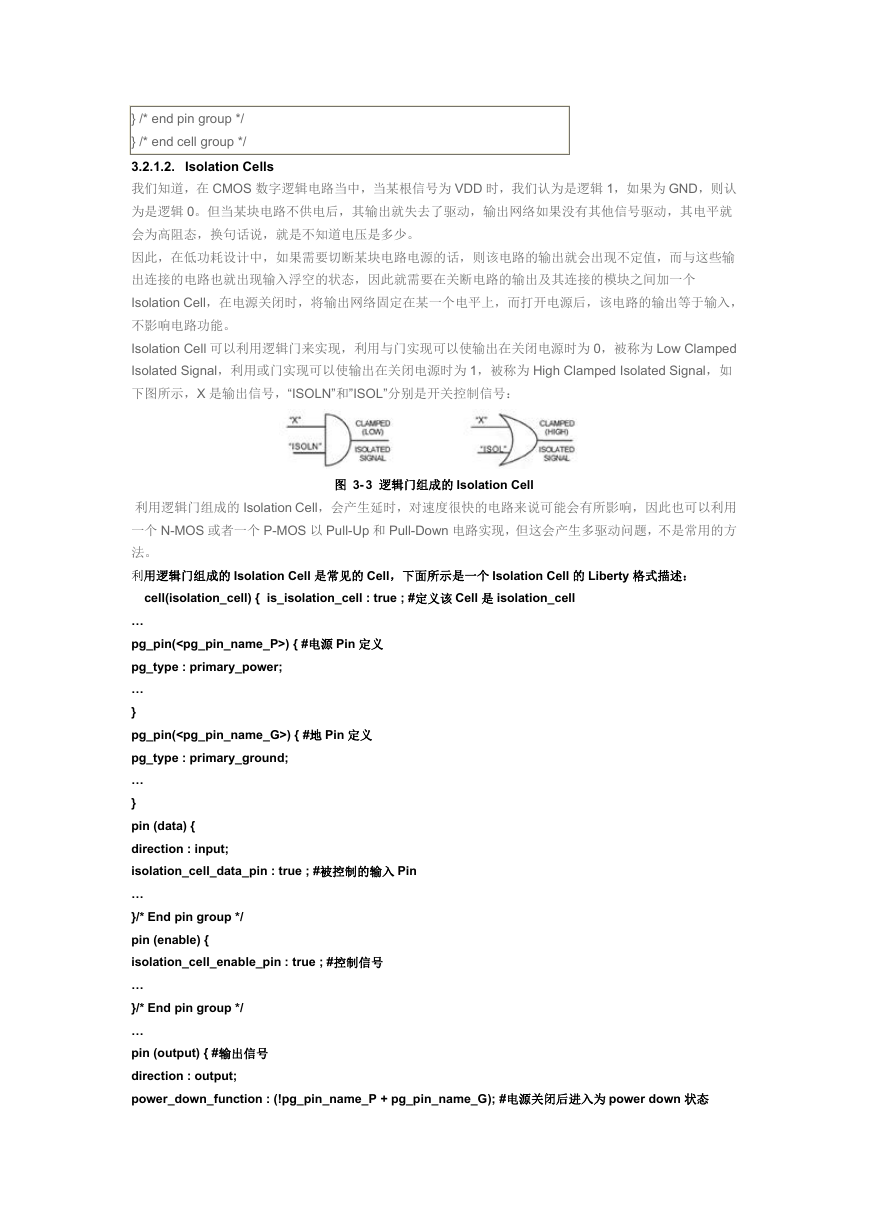

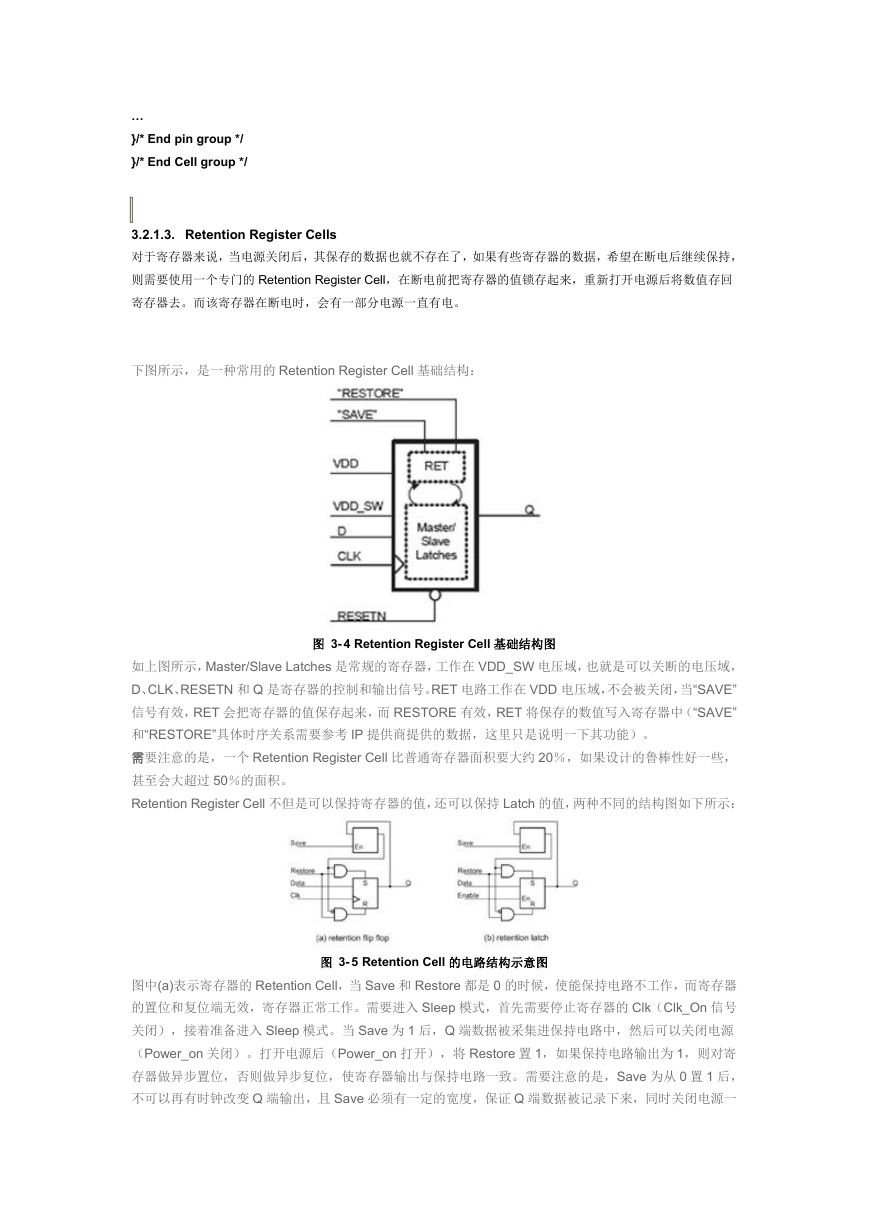

对于寄存器来说,当电源关闭后,其保存的数据也就不存在了,如果有些寄存器的数据,希望在断电后继续保持,

图 3�4 Retention Register Cell基础结构图

图 3�5 Retention Cell的电路结构示意图

图 3�6 Retention Register工作时序示意图

retention_cell_style主要是定义一个器件识别名,不同功能名字不能一样。这里所说的功

retention_pin是的定义表示该pin是与retention cell功能有关的,其中pin

3.2.1.4. Always-On Logic Cells

3.2.2 利用不同VT值的库,实现静态功耗和时序的平衡(Multi-VT)

随着工艺尺寸的减小,Oxide层厚度的减少,VT值也一直在减少,这是为了在驱动电压较低的情况下,提高

3.2.2.1. 常用EDA工具中Multi-VT的实现方法

由于综合时,时序信息并不完全准确,特别是setup类的时序。因此可以对setup时序做稍紧一些的约束

如在IC Compiler里,在布线后优化时可以使用如下语句来进行优化:

3.2.4 多供电电压,实现动态功耗与时序的平衡(Multi-Voltage)

这里check_mv_design主要是检查UPF对设计的描述是否正确,在compile之后再做一次

接着,需要在不同电压电路之间,添加Level_shifters,进行电压转换。如下所示:

3.2.4.1. 常用EDA工具中Multi-VT的实现方法

3.2.4.2. Liberty PG Pin格式

3.2.4.3. 电压和频率的Scaling分析

3.3 其他未提及工艺

4.0 一个低功耗设计实现的例子

图 4�1 pl8051_extend_chip功能结构图

图 4�2 低功耗设计方案示例

4.1 申明电压域以及虚拟电压接口

根据上述指令,工具会识别出如下图所示中画圈的信息,电压域及虚拟电压端口开始出现:

图 4�3 电压域及虚拟电压端口信息

以上语句添加下图中画圈部分:

图 4�4 产生顶层电源网络

create_supply_net VDD12 –domain DES_DOMAIN –reuse

create_supply_net VDD12G

create_supply_net VDD12G –domain DES_DOMAIN -reuse

create_supply_net VSS –domain DES_DOMAIN –reuse

create_supply_net VDD –domain DES_DOMAIN –reuse

图 4�5 子电路的电源网路申明

图 4�6 连接电源网络和电源端口

4.3 添加Power Switch

图 4�7 添加Power Switch Cell

4.4 建立电源状态表格(Power State Table, PST)

4.5 插入Isolation Cell

图 4�8 插入Isolation Cell

4.6 替换Retention Register Cell

图 4�9 替换Retention Register Cell

4.7 插入Level Shifters

图 4�10 插入Level Shifters

4.8 UPF Demo

4.9 DC UPF Flow Script Demo

source -e ../scr/ variable.tcl

set_clock_gating_style -min ${CG_MIN_BITWIDTH} -ma

-sequential_cell ${CG

-positive_edge_logic

-negative_edge_logic

-control_point ${CG_C

-control_signal ${CG_

-setup ${CG_SETUP_VAL

set_operand_isolation_style -logic adaptive

set_operand_isolation_slack 0.1

set_svf ${NETLIST_PATH}${top}${VER}.svf

read_verilog ${RTL_INCLUDE}

current_design $top

uniquify

link

load_upf ${SCRIPT_PATH}power.upf

set auto_insert_level_shifters_on_clocks all ;#can

set_voltage 1.08 -object_list {VDD12 VDD12G}

set_voltage 0.84 -object_list VDD

set_voltage 0.0 -object_list VSS

source -e -v ${SCRIPT_PATH}timing.tcl

#M1~M9 are avaliable, M1 will be used by STD

#set_ignored_layers -min_routing_layer M4

set_ignored_layers -max_routing_layer M7

report_ignored_layers > ${REPORT_PATH}${top}_ignor

set_clock_gating_check -setup ${CG_SETUP_CHECK} -h

set_fix_multiple_port_nets -feedthroughs -outputs

set_attr -type string tcbn90lphpwc0d70d9_pg.db:tcb

set_attr -type string tcbn90lphphvtwc0d70d9_pg.db:

set_attr -type string tcbn90lphpwc0d7_pg.db:tcbn90

set_attr -type string tcbn90lphphvtwc0d7_pg.db:tcb

set_attr -type string tcbn90lphpwc_pg.db:tcbn90lph

set_attr -type string tcbn90lphphvtwc_pg.db:tcbn90

set_attr -type string tcbn90lphphvtcgwc_pg.db:tcbn

set_attr -type string tcbn90lphphvtwc0d90d9_pg.db:

set_attr -type string tcbn90lphphvtwc0d90d7_pg.db:

set_attr -type string tcbn90lphpwc0d90d7_pg.db:tcb

check_mv_design -verbose

compile_ultra -scan -no_autoungroup -no_boundary_

change_names -rules verilog -hierarchy

write -format ddc -hierarchy -output ${DDC_PATH}${

write -format verilog -hierarchy -output ${NETLIST

set write_sdc_output_lumped_net_capacitance false

set write_sdc_output_net_resistance false

write_sdc -version 1.5 ${SDC_PATH}${top}_cons${VER

check_design > ${REPORT_PATH}${top}_check_design_p

report_area > ${REPORT_PATH}${top}_area.rpt

check_mv_design –verbose > ${REPORT_PATH}${top}_ch

report_constraint -all > ${REPORT_PATH}${top}_all_

report_clock_gating -gating_elements >> ${REPORT_P

report_operand_isolation -verbose -isolated > ${RE

report_threshold_voltage_group > ${REPORT_PATH}${t

report_threshold_voltage_group -verbose >> ${REPOR

save_upf ${NETLIST_PATH}${top}${VER}_dc.upf #upf’

5.0 总结

[1] Page 14, “Low Power Methodology Manual For Sy

[2] Page 42, “Low Power Methodology Manual For Sys

[3] Page 2-29, “Library Compiler™ User Guide: Mode

[4] Page 2-32, “Library Compiler™ User Guide: Mode

[5] Page 46, “Low Power Methodology Manual For Sys

[6] Page 2-23, “Library Compiler™ User Guide: Mode

[7] Page 55, “Low Power Methodology Manual For Sys

[8] Page 2-46, “Library Compiler™ User Guide: Mode

[9] Page 2-11, “Library Compiler™ User Guide: Mode

[10]Page 2-2, “Library Compiler™ User Guide: Model

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc