OR1200

OR1200

OR1200

OR1200 指令集整理学习笔记

张智彬

zhangzhibin010@gmail.com

MSN:zezeba@live.cn

MSN:zezeba@live.cn

MSN:zezeba@live.cn

MSN:zezeba@live.cn

本文包括所有 ORBIS32 I 类指令。

说明:指令格式中的 D,A,B 下面的 5bit 是指相应通用寄存器的具体地址。

l.add

l.add

l.add

l.add

AddAddAddAdd Signed

Signed

Signed

Signed

l.add

l.add

l.add

l.add

31

.

.

.

. 26 25 .

.

. 21 20 .

.

. 16 15 .

.

. 11 10

9

8 7

.

.

4 3

.

.

0

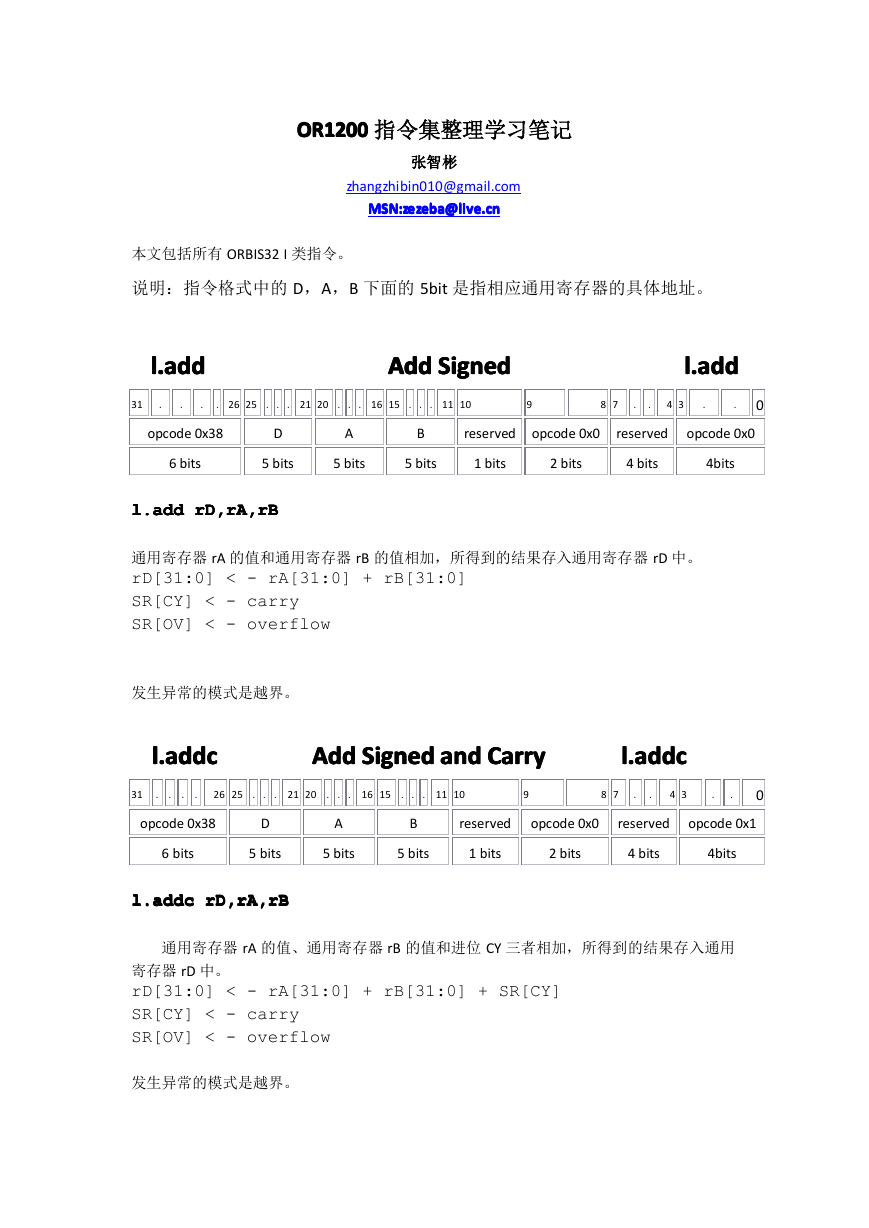

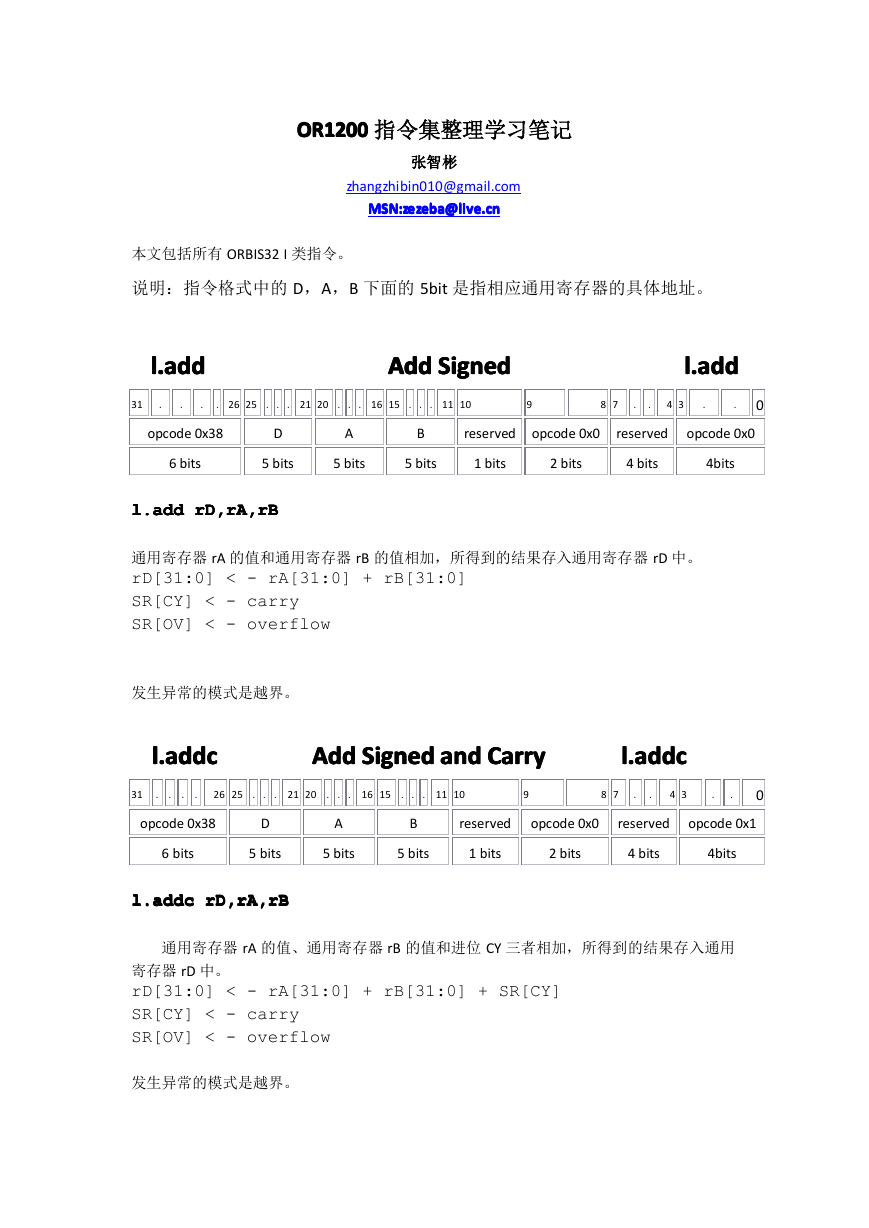

opcode 0x38

D

A

B

reserved

opcode 0x0

reserved

opcode 0x0

6 bits

5 bits

llll.add

.add.add

rD,rA,rB

rD,rA,rB

.add rD,rA,rB

rD,rA,rB

5 bits

5 bits

1 bits

2 bits

4 bits

4bits

通用寄存器 rA 的值和通用寄存器 rB 的值相加,所得到的结果存入通用寄存器 rD 中。

rD[31:0] < - rA[31:0] + rB[31:0]

SR[CY] < - carry

SR[OV] < - overflow

发生异常的模式是越界。

l.addc

l.addc

l.addc

l.addc

Signed andandandand Carry

Signed

AddAddAddAdd Signed

Carry

Signed

Carry

Carry

l.addc

l.addc

l.addc

l.addc

31

.

.

.

.

26 25 .

.

. 21 20 .

.

. 16 15 .

.

. 11 10

9

8 7

.

.

4 3

.

.

0

opcode 0x1

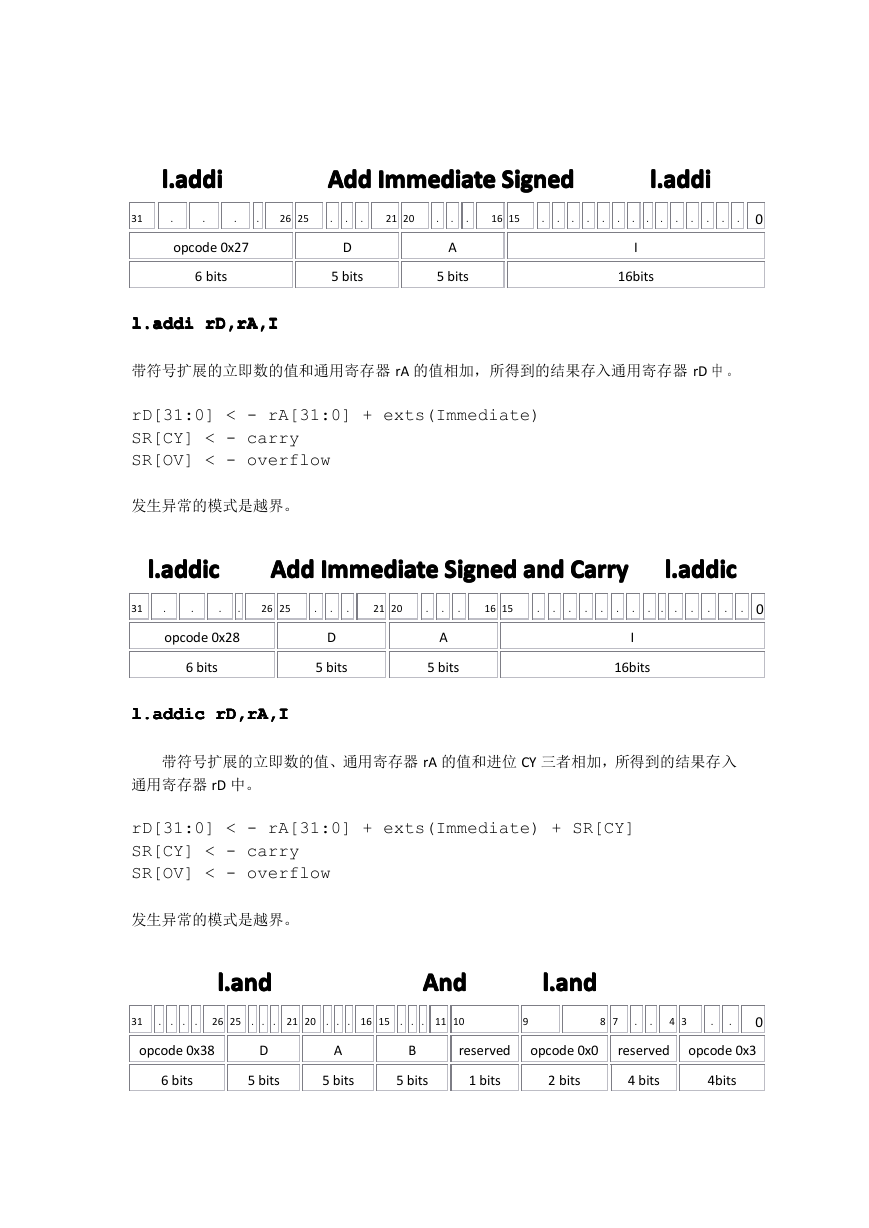

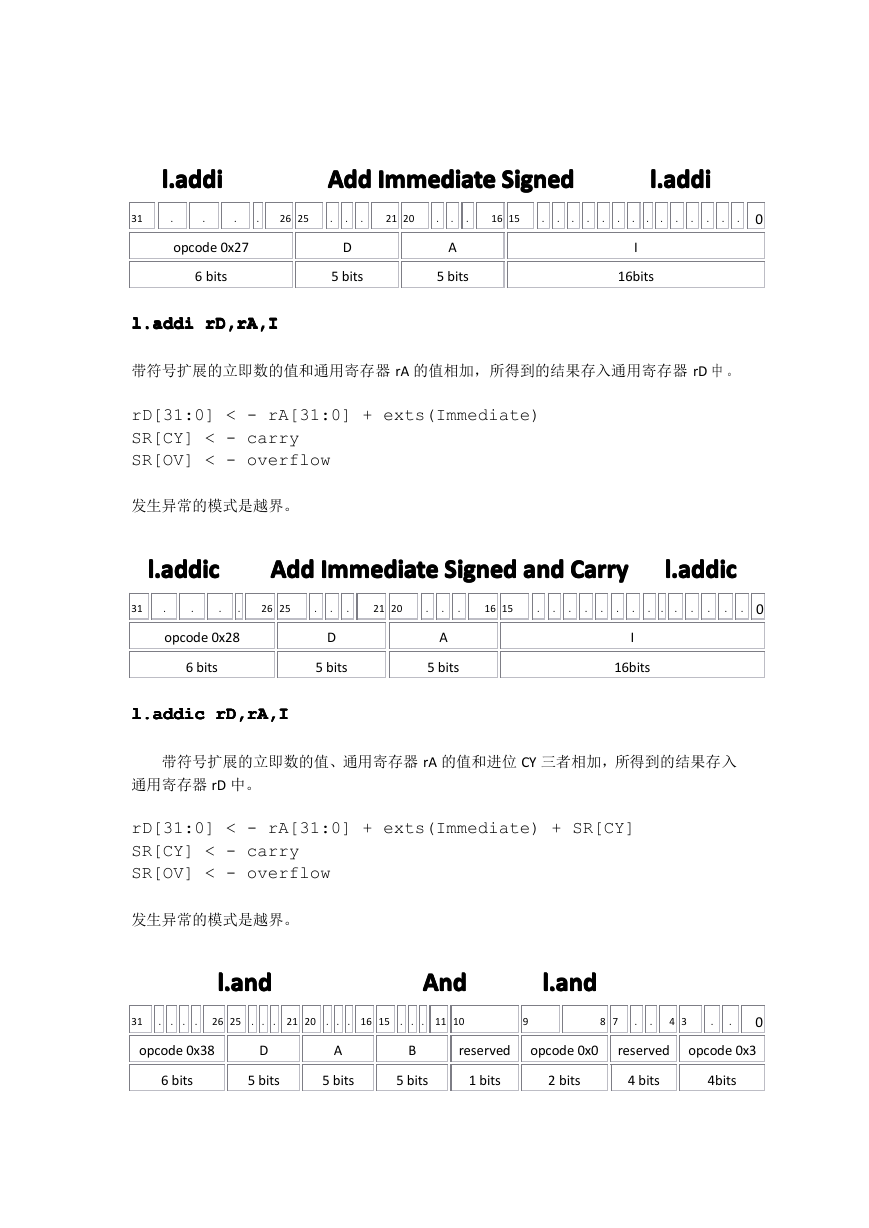

opcode 0x38

D

5 bits

6 bits

l.addc

rD,rA,rB

l.addc

rD,rA,rB

l.addc rD,rA,rB

l.addc

rD,rA,rB

A

5 bits

B

reserved

opcode 0x0

reserved

5 bits

1 bits

2 bits

4 bits

4bits

通用寄存器 rA 的值、通用寄存器 rB 的值和进位 CY 三者相加,所得到的结果存入通用

寄存器 rD 中。

rD[31:0] < - rA[31:0] + rB[31:0] + SR[CY]

SR[CY] < - carry

SR[OV] < - overflow

发生异常的模式是越界。

�

l.addi

l.addi

l.addi

l.addi

Immediate

AddAddAddAdd Immediate

Signed

Immediate

Signed

Immediate Signed

Signed

l.addi

l.addi

l.addi

l.addi

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

.

.

.

.

.

.

.

0

.

I

16bits

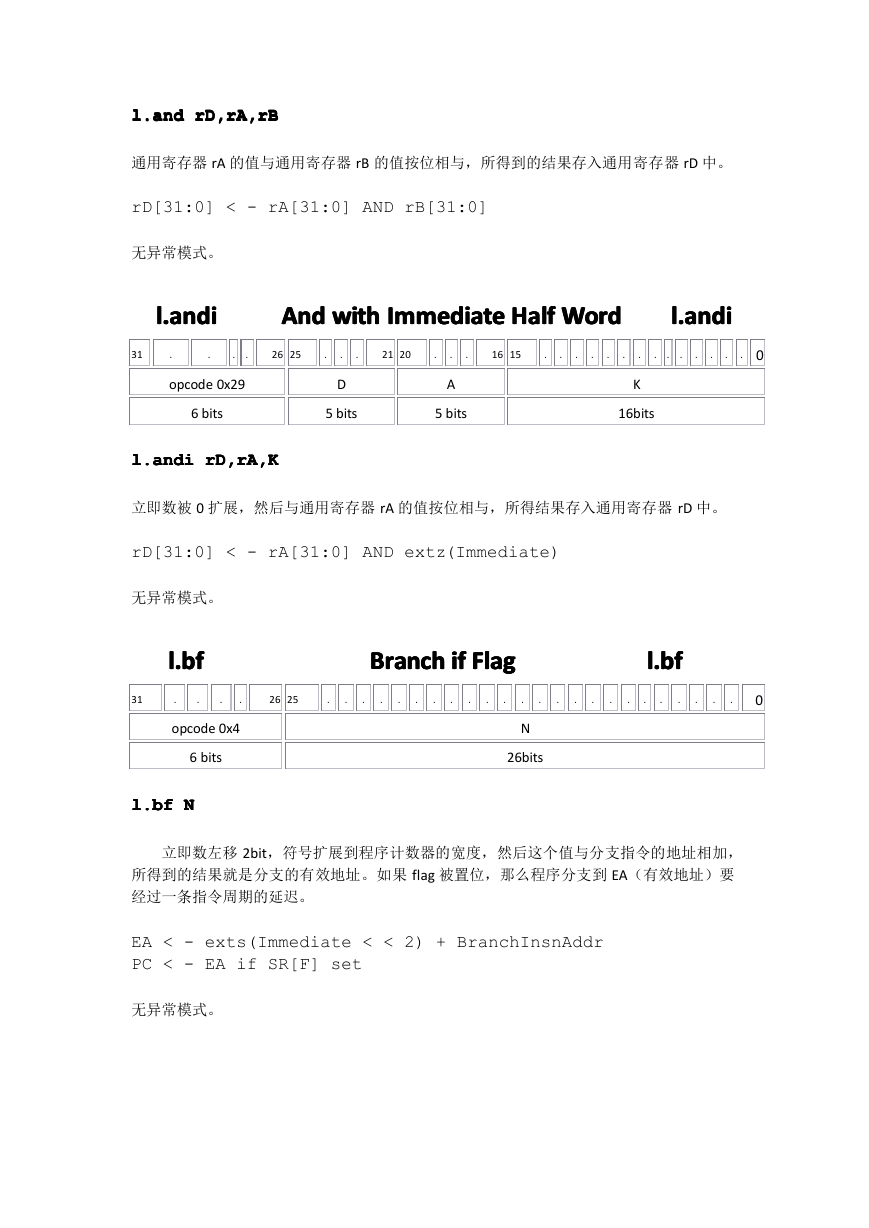

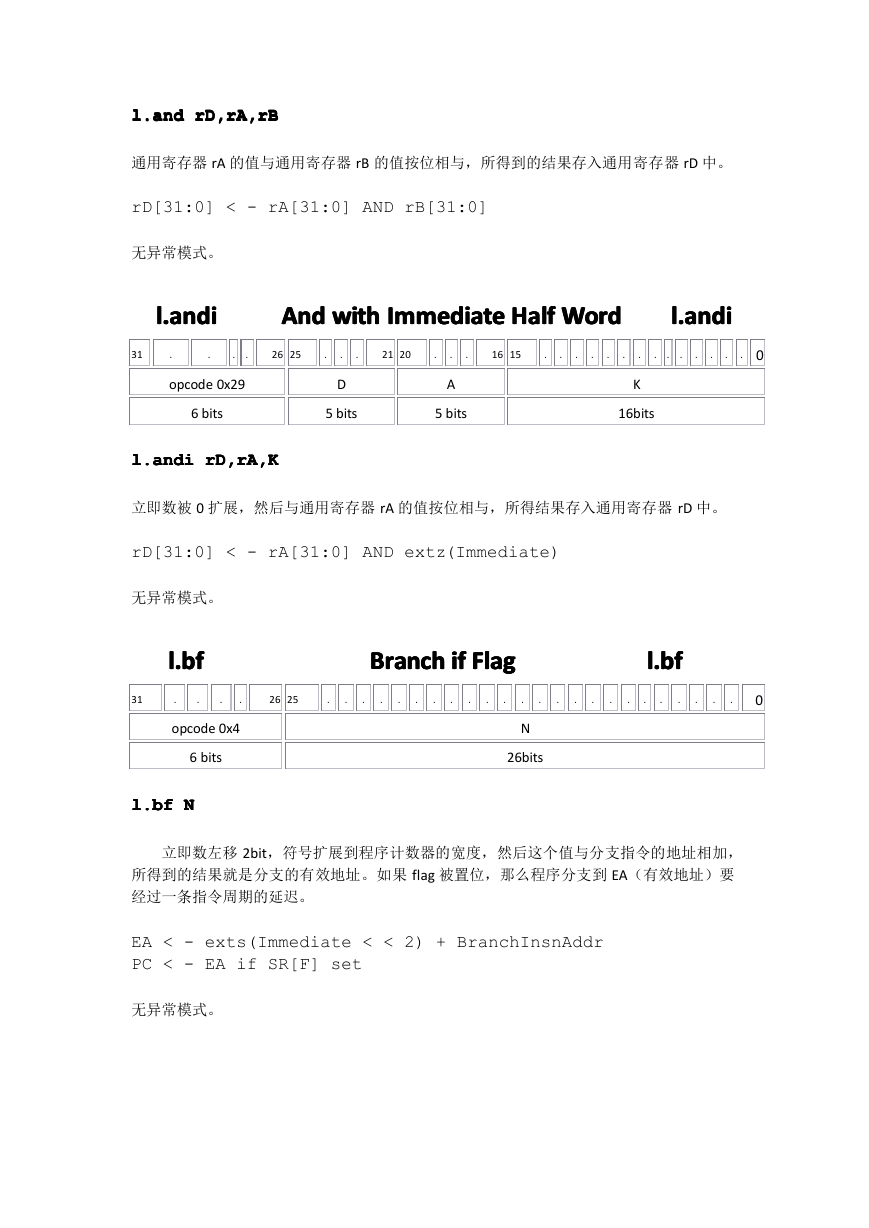

opcode 0x27

6 bits

l.addi

rD,rA,I

l.addi

rD,rA,I

l.addi rD,rA,I

l.addi

rD,rA,I

D

5 bits

A

5 bits

带符号扩展的立即数的值和通用寄存器 rA 的值相加,所得到的结果存入通用寄存器 rD 中 。

rD[31:0] < - rA[31:0] + exts(Immediate)

SR[CY] < - carry

SR[OV] < - overflow

发生异常的模式是越界。

l.addic

l.addic

l.addic

l.addic

Signed andandandand Carry

Signed

Immediate

AddAddAddAdd Immediate

Carry

Immediate

Signed

Carry

Immediate Signed

Carry

l.addic

l.addic

l.addic

l.addic

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

.

.

.

.

.

.

. 0

.

I

16bits

opcode 0x28

6 bits

l.addic

rD,rA,I

l.addic

rD,rA,I

l.addic rD,rA,I

l.addic

rD,rA,I

D

5 bits

A

5 bits

带符号扩展的立即数的值、通用寄存器 rA 的值和进位 CY 三者相加,所得到的结果存入

通用寄存器 rD 中。

rD[31:0] < - rA[31:0] + exts(Immediate) + SR[CY]

SR[CY] < - carry

SR[OV] < - overflow

发生异常的模式是越界。

l.and

l.and

l.and

l.and

AndAndAndAnd

l.and

l.and

l.and

l.and

31

.

.

.

.

26 25 .

.

. 21 20 .

.

. 16 15 .

.

. 11 10

9

8 7

.

.

4 3

opcode 0x38

6 bits

D

5 bits

A

5 bits

B

reserved

opcode 0x0

reserved

5 bits

1 bits

2 bits

4 bits

4bits

.

.

0

opcode 0x3

�

l.and

rD,rA,rB

l.and

rD,rA,rB

l.and rD,rA,rB

l.and

rD,rA,rB

通用寄存器 rA 的值与通用寄存器 rB 的值按位相与,所得到的结果存入通用寄存器 rD 中。

rD[31:0] < - rA[31:0] AND rB[31:0]

无异常模式。

l.andi

l.andi

l.andi

l.andi

Immediate

AndAndAndAnd withwithwithwith Immediate

Immediate HalfHalfHalfHalf WordWordWordWord

Immediate

l.andi

l.andi

l.andi

l.andi

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

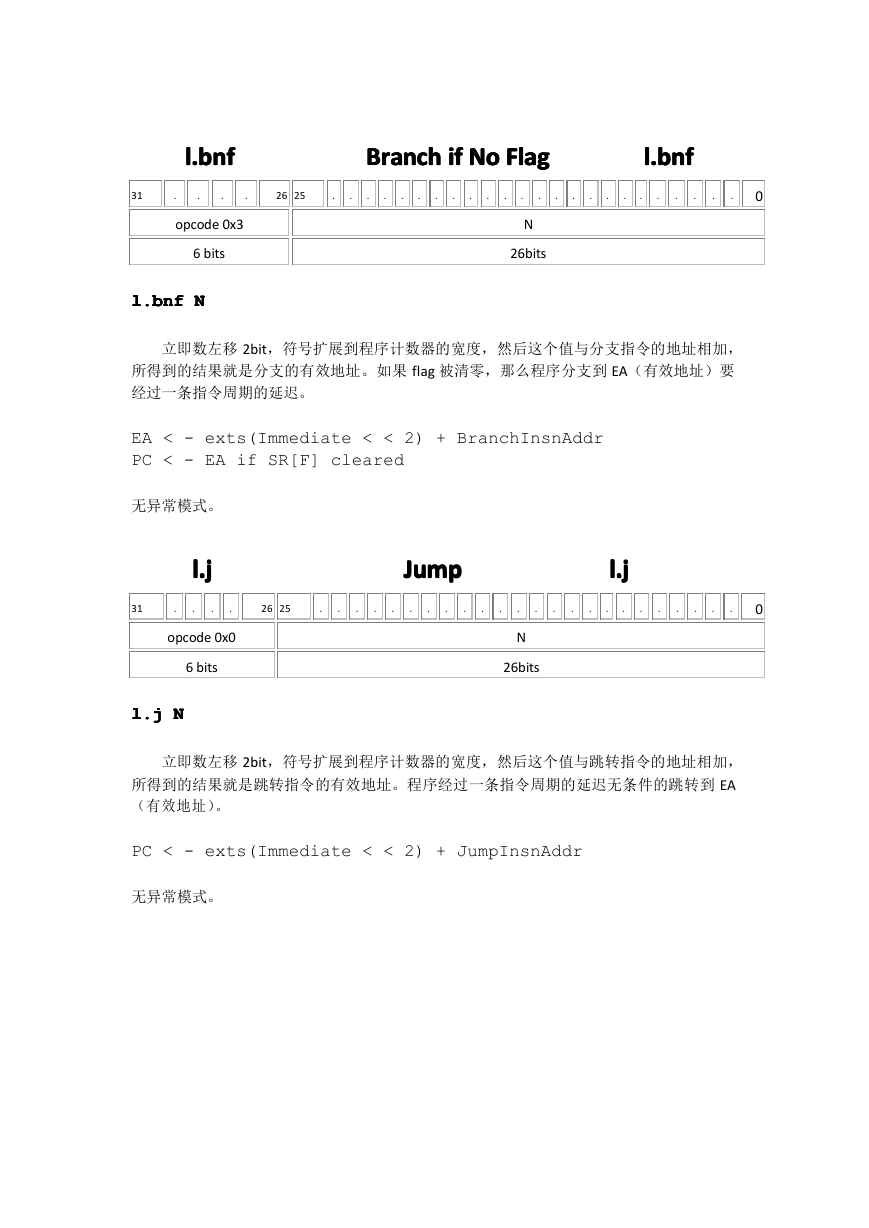

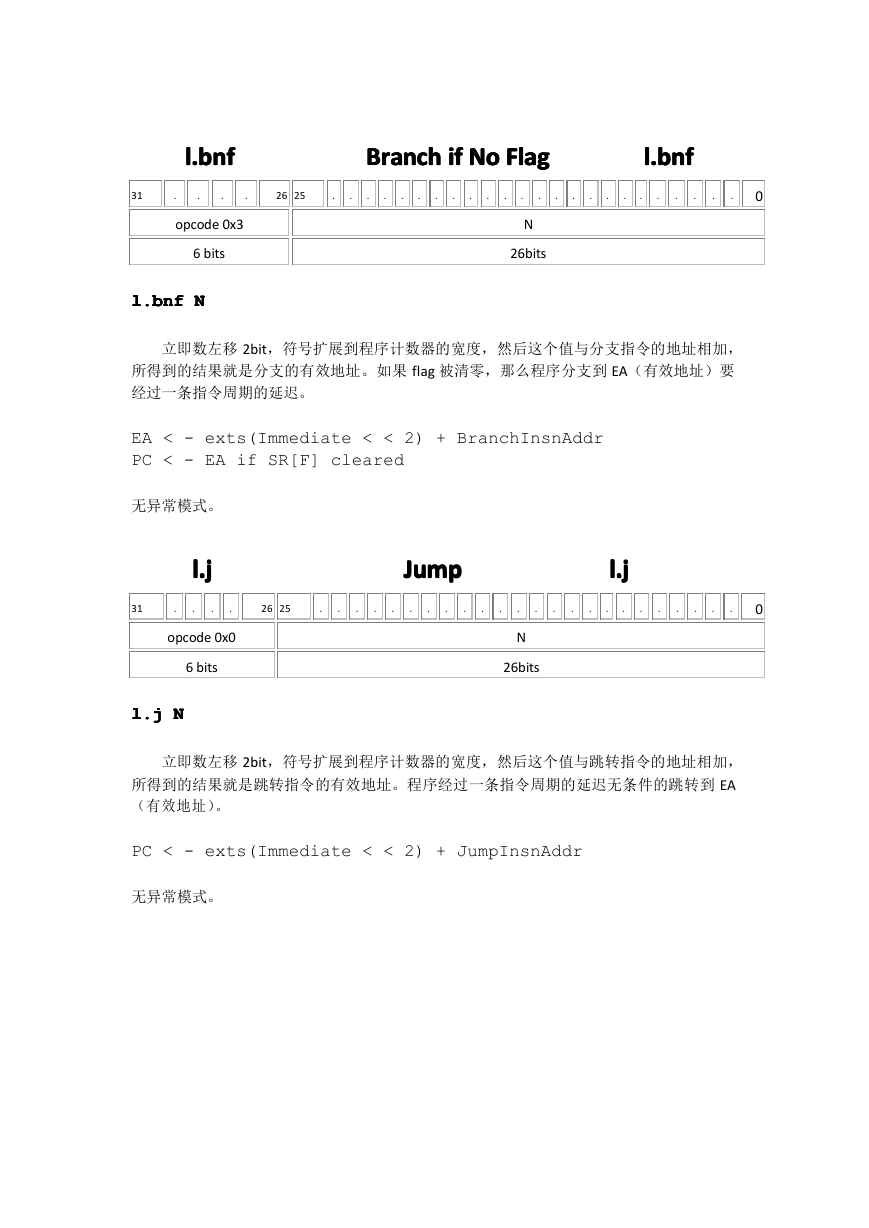

opcode 0x29

6 bits

l.andi

rD,rA,K

l.andi

rD,rA,K

l.andi rD,rA,K

l.andi

rD,rA,K

D

5 bits

A

5 bits

.

.

.

.

.

.

. 0

.

K

16bits

立即数被 0 扩展,然后与通用寄存器 rA 的值按位相与,所得结果存入通用寄存器 rD 中。

rD[31:0] < - rA[31:0] AND extz(Immediate)

无异常模式。

l.bf

l.bf

l.bf

l.bf

Branch

Branch ifififif FlagFlagFlagFlag

Branch

Branch

l.bf

l.bf

l.bf

l.bf

31

.

.

.

.

26 25

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

0

opcode 0x4

6 bits

l.bfl.bf

l.bf NNNN

l.bf

N

26bits

立即数左移 2bit,符号扩展到程序计数器的宽度,然后这个值与分支指令的地址相加,

所得到的结果就是分支的有效地址。如果 flag 被置位,那么程序分支到 EA(有效地址)要

经过一条指令周期的延迟。

EA < - exts(Immediate < < 2) + BranchInsnAddr

PC < - EA if SR[F] set

无异常模式。

�

0

0

l.bnf

l.bnf

l.bnf

l.bnf

Branch

Branch ifififif NoNoNoNo FlagFlagFlagFlag

Branch

Branch

l.bnf

l.bnf

l.bnf

l.bnf

31

.

.

.

.

26 25

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

opcode 0x3

6 bits

l.bnf

l.bnf NNNN

l.bnf

l.bnf

N

26bits

立即数左移 2bit,符号扩展到程序计数器的宽度,然后这个值与分支指令的地址相加,

所得到的结果就是分支的有效地址。如果 flag 被清零,那么程序分支到 EA(有效地址)要

经过一条指令周期的延迟。

EA < - exts(Immediate < < 2) + BranchInsnAddr

PC < - EA if SR[F] cleared

无异常模式。

l.jl.jl.jl.j

Jump

Jump

Jump

Jump

l.jl.jl.jl.j

31

.

.

.

.

26 25

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

opcode 0x0

6 bits

l.jl.jl.jl.j NNNN

N

26bits

立即数左移 2bit,符号扩展到程序计数器的宽度,然后这个值与跳转指令的地址相加,

所得到的结果就是跳转指令的有效地址。程序经过一条指令周期的延迟无条件的跳转到 EA

(有效地址)。

PC < - exts(Immediate < < 2) + JumpInsnAddr

无异常模式。

�

0

0

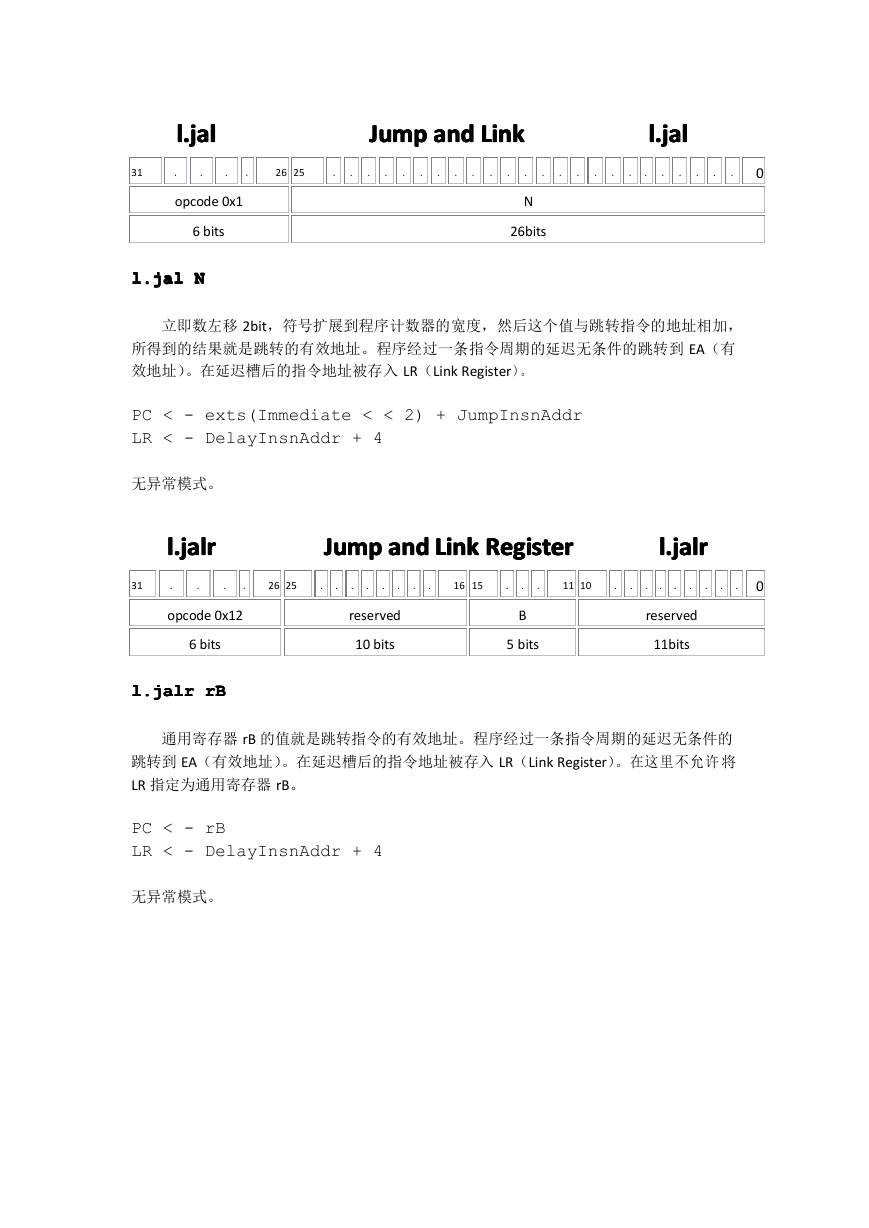

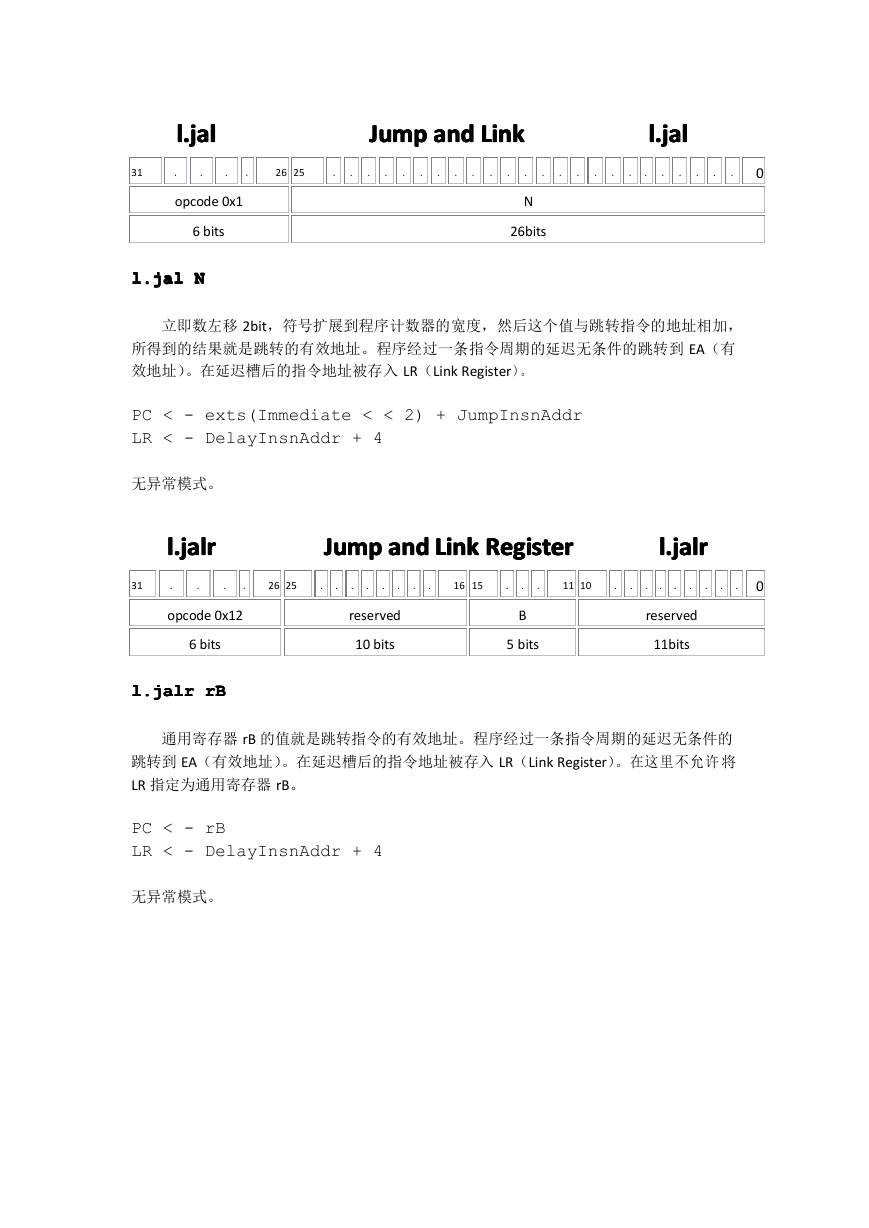

l.jal

l.jal

l.jal

l.jal

Jump

Jump andandandand LinkLinkLinkLink

Jump

Jump

l.jal

l.jal

l.jal

l.jal

31

.

.

.

.

26 25

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

opcode 0x1

6 bits

l.jal

l.jal NNNN

l.jal

l.jal

N

26bits

立即数左移 2bit,符号扩展到程序计数器的宽度,然后这个值与跳转指令的地址相加,

所得到的结果就是跳转的有效地址。程序经过一条指令周期的延迟无条件的跳转到 EA(有

效地址)。在延迟槽后的指令地址被存入 LR(Link Register)。

PC < - exts(Immediate < < 2) + JumpInsnAddr

LR < - DelayInsnAddr + 4

无异常模式。

l.jalr

l.jalr

l.jalr

l.jalr

Jump andandandand LinkLinkLinkLink Register

Jump

Register

Jump

Register

Jump

Register

l.jalr

l.jalr

l.jalr

l.jalr

31

.

.

.

.

26 25

.

.

.

.

.

.

.

.

16 15

.

.

.

11 10

.

.

.

.

.

.

.

.

.

opcode 0x12

6 bits

l.jalr

l.jalr rBrBrBrB

l.jalr

l.jalr

reserved

10 bits

B

5 bits

reserved

11bits

通用寄存器 rB 的值就是跳转指令的有效地址。程序经过一条指令周期的延迟无条件的

跳转到 EA(有效地址)。在延迟槽后的指令地址被存入 LR(Link Register)。在这里不允许 将

LR 指定为通用寄存器 rB。

PC < - rB

LR < - DelayInsnAddr + 4

无异常模式。

�

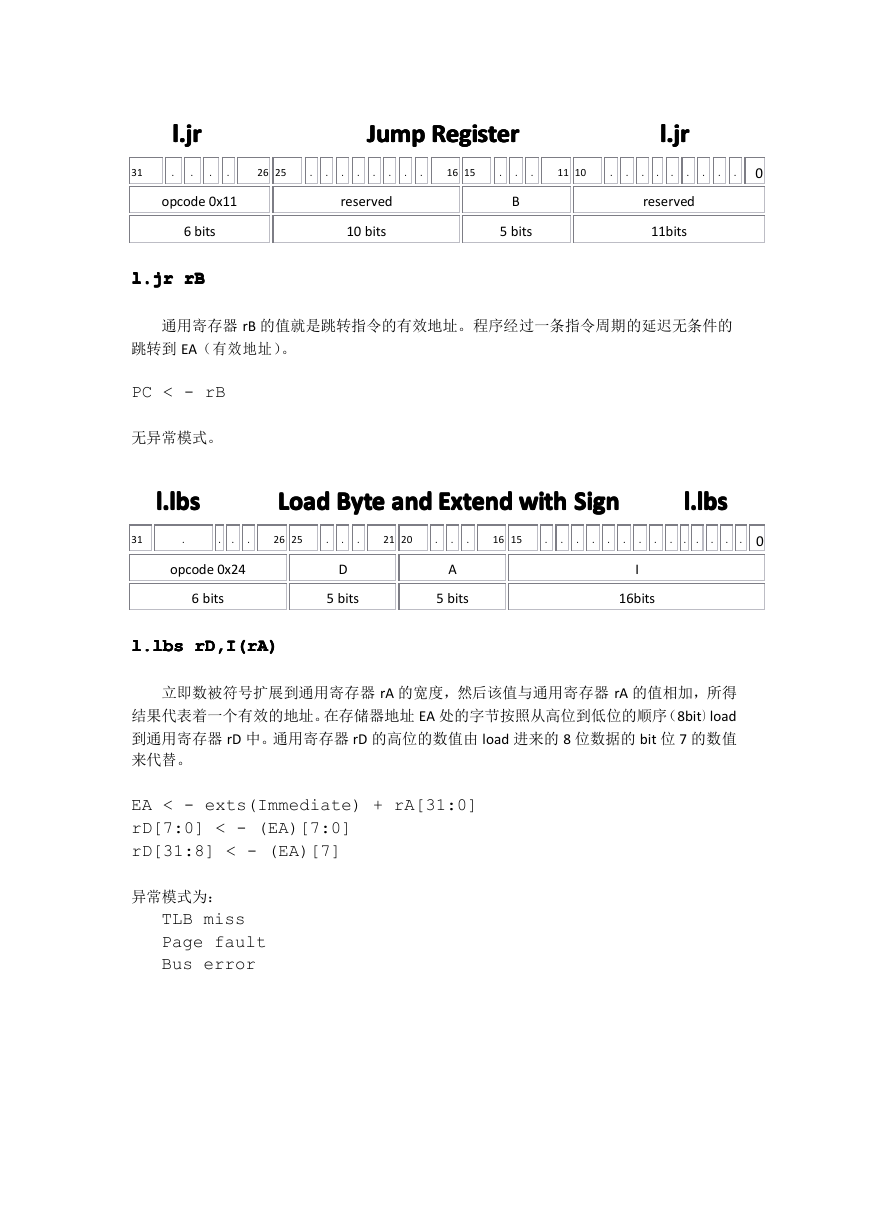

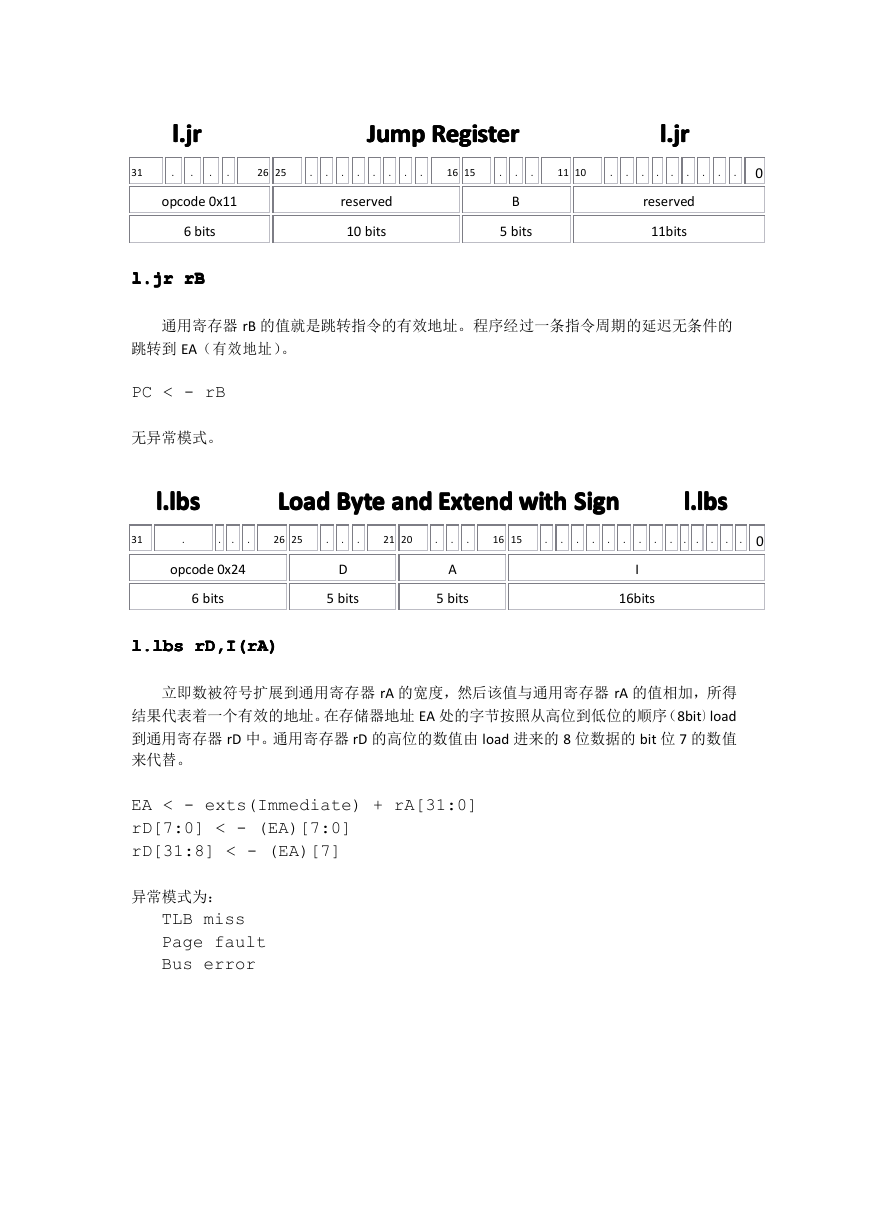

l.jrl.jrl.jrl.jr

Jump

Register

Jump

Register

Jump Register

Jump

Register

l.jrl.jrl.jrl.jr

31

.

.

.

.

26 25

.

.

.

.

.

.

.

.

16 15

.

.

11 10

.

.

.

.

.

.

.

.

.

0

opcode 0x11

6 bits

l.jrl.jr

l.jr rBrBrBrB

l.jr

reserved

10 bits

.

B

5 bits

reserved

11bits

通用寄存器 rB 的值就是跳转指令的有效地址。程序经过一条指令周期的延迟无条件的

跳转到 EA(有效地址)。

PC < - rB

无异常模式。

l.lbs

l.lbs

l.lbs

l.lbs

Extend

LoadLoadLoadLoad ByteByteByteByte andandandand Extend

Extend withwithwithwith SignSignSignSign

Extend

l.lbs

l.lbs

l.lbs

l.lbs

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

.

.

.

.

.

.

.

. 0

opcode 0x24

6 bits

l.lbs

rD,I(rA)

l.lbs

rD,I(rA)

l.lbs rD,I(rA)

l.lbs

rD,I(rA)

D

5 bits

A

5 bits

I

16bits

立即数被符号扩展到通用寄存器 rA 的宽度,然后该值与通用寄存器 rA 的值相加,所得

结果代表着一个有效的地址。在存储器地址 EA 处的字节按照从高位到低位的顺序(8bit)load

到通用寄存器 rD 中。通用寄存器 rD 的高位的数值由 load 进来的 8 位数据的 bit 位 7 的数值

来代替。

EA < - exts(Immediate) + rA[31:0]

rD[7:0] < - (EA)[7:0]

rD[31:8] < - (EA)[7]

异常模式为:

TLB miss

Page fault

Bus error

�

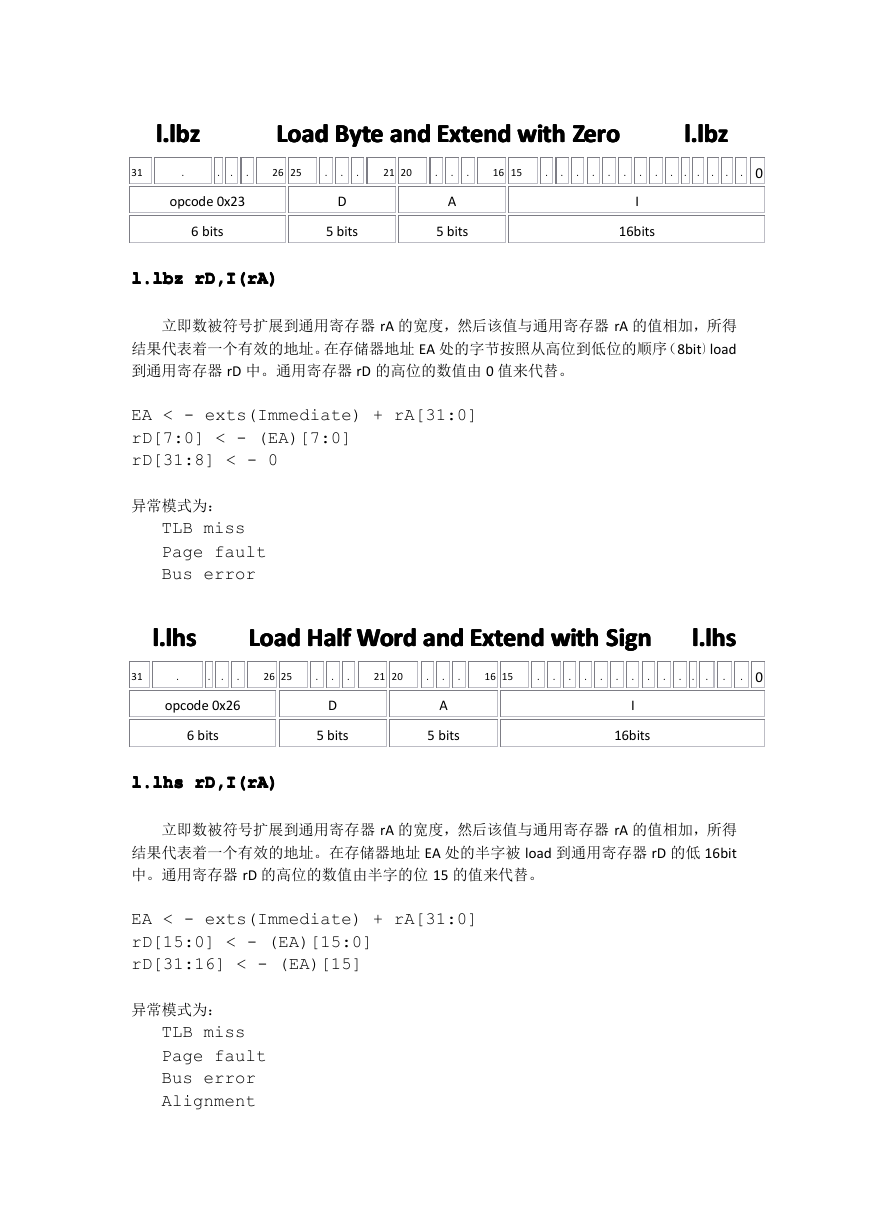

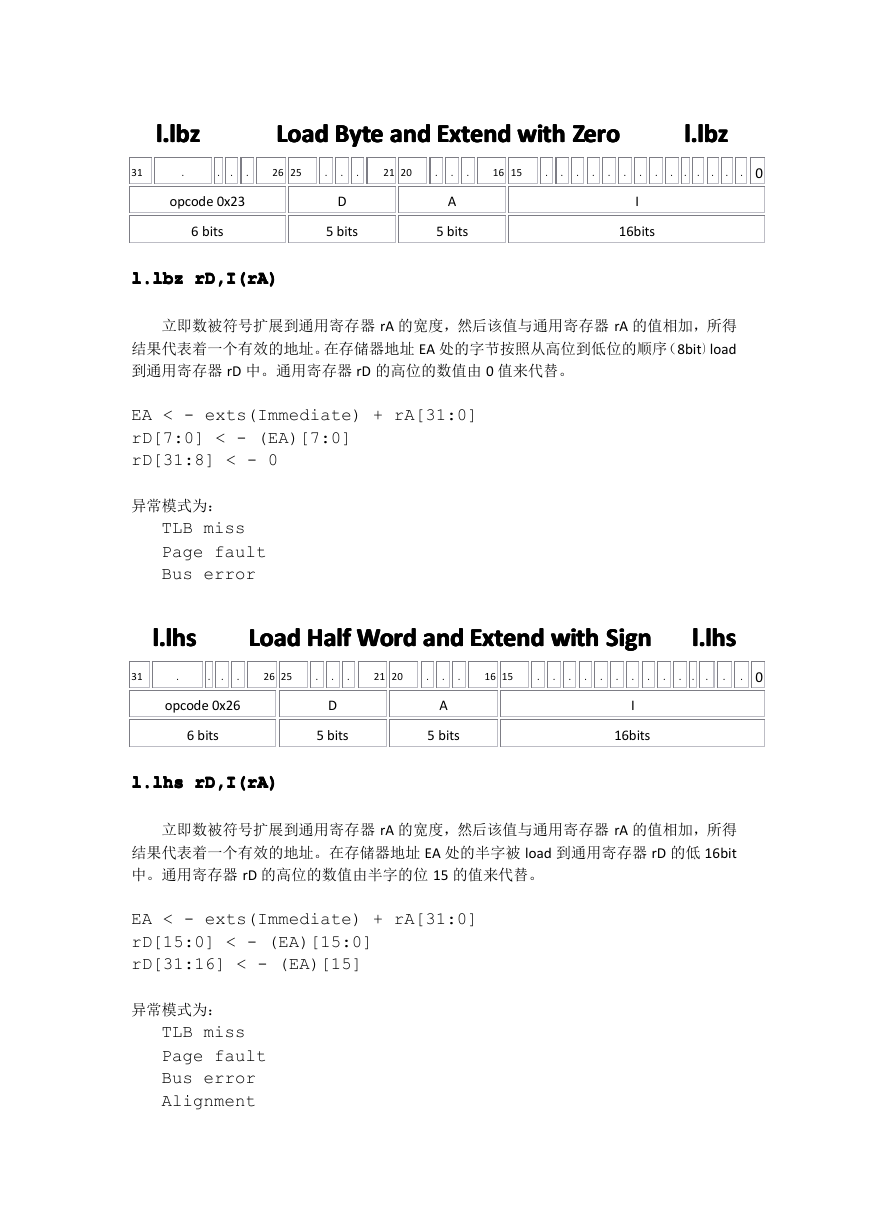

l.lbz

l.lbz

l.lbz

l.lbz

Extend

LoadLoadLoadLoad ByteByteByteByte andandandand Extend

Extend withwithwithwith ZeroZeroZeroZero

Extend

l.lbz

l.lbz

l.lbz

l.lbz

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

.

.

.

.

.

.

.

. 0

opcode 0x23

6 bits

l.lbz

rD,I(rA)

l.lbz

rD,I(rA)

l.lbz rD,I(rA)

l.lbz

rD,I(rA)

D

5 bits

A

5 bits

I

16bits

立即数被符号扩展到通用寄存器 rA 的宽度,然后该值与通用寄存器 rA 的值相加,所得

结果代表着一个有效的地址。在存储器地址 EA 处的字节按照从高位到低位的顺序(8bit)load

到通用寄存器 rD 中。通用寄存器 rD 的高位的数值由 0 值来代替。

EA < - exts(Immediate) + rA[31:0]

rD[7:0] < - (EA)[7:0]

rD[31:8] < - 0

异常模式为:

TLB miss

Page fault

Bus error

l.lhs

l.lhs

l.lhs

l.lhs

Extend

LoadLoadLoadLoad HalfHalfHalfHalf WordWordWordWord andandandand Extend

Extend withwithwithwith SignSignSignSign

Extend

l.lhs

l.lhs

l.lhs

l.lhs

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

opcode 0x26

6 bits

l.lhs

rD,I(rA)

l.lhs

rD,I(rA)

l.lhs rD,I(rA)

l.lhs

rD,I(rA)

D

5 bits

A

5 bits

.

.

.

.

.

.

. 0

.

I

16bits

立即数被符号扩展到通用寄存器 rA 的宽度,然后该值与通用寄存器 rA 的值相加,所得

结果代表着一个有效的地址。在存储器地址 EA 处的半字被 load 到通用寄存器 rD 的低 16bit

中。通用寄存器 rD 的高位的数值由半字的位 15 的值来代替。

EA < - exts(Immediate) + rA[31:0]

rD[15:0] < - (EA)[15:0]

rD[31:16] < - (EA)[15]

异常模式为:

TLB miss

Page fault

Bus error

Alignment

�

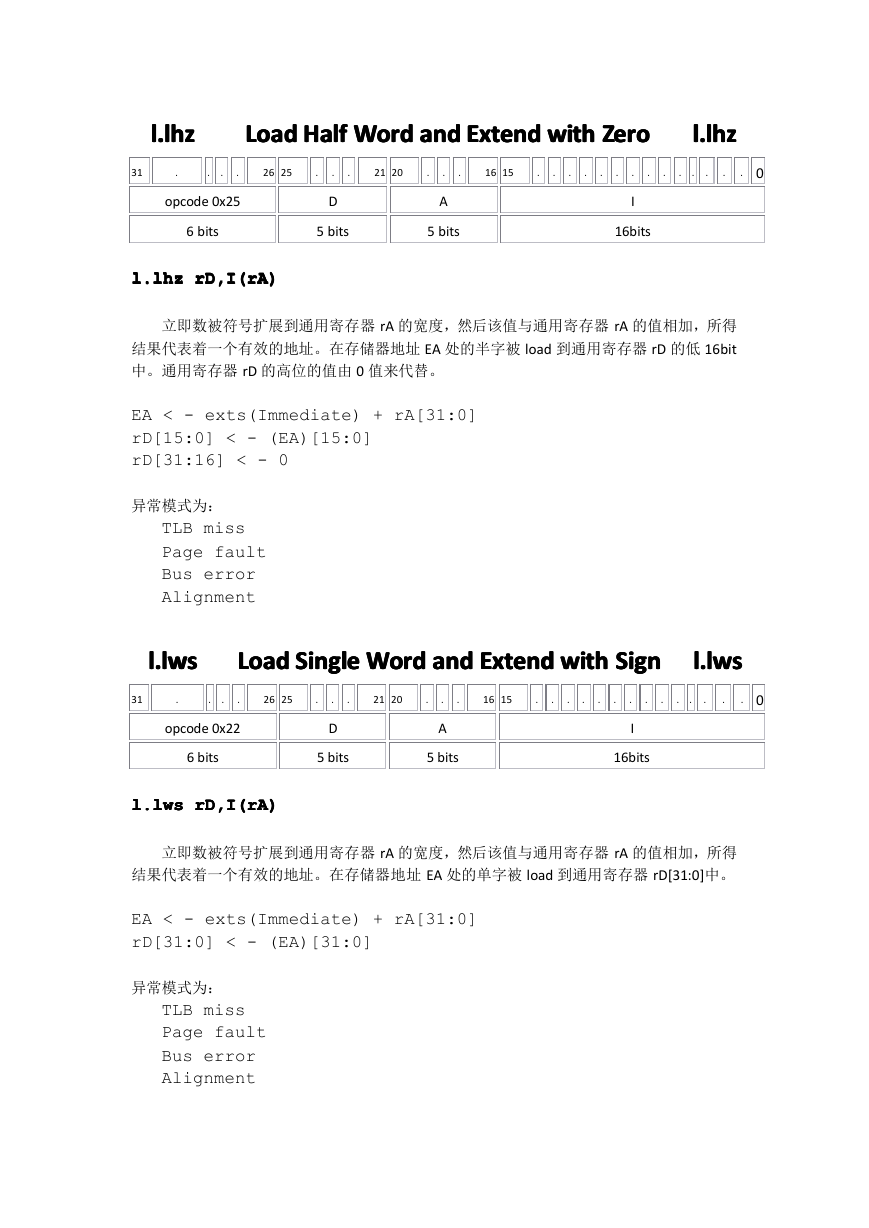

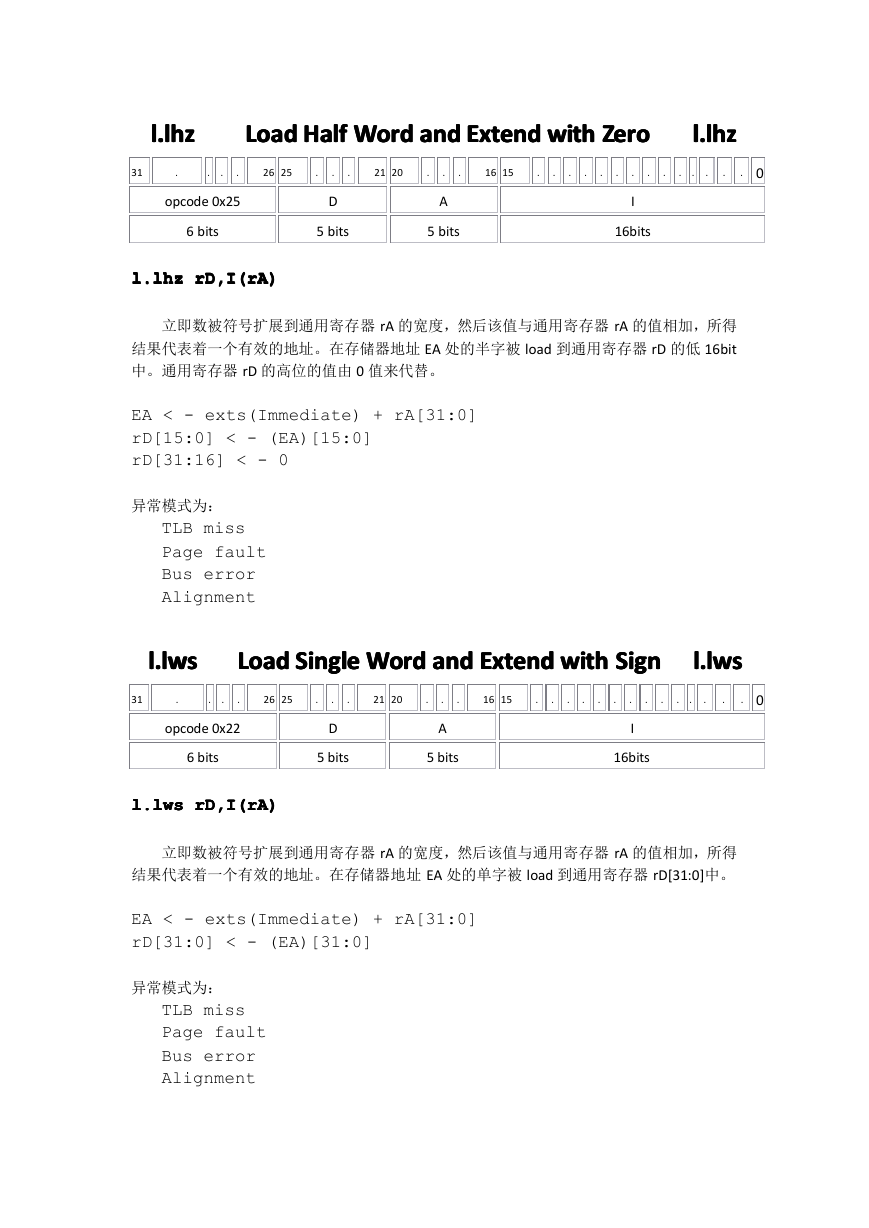

l.lhz

l.lhz

l.lhz

l.lhz

Extend

LoadLoadLoadLoad HalfHalfHalfHalf WordWordWordWord andandandand Extend

Extend withwithwithwith ZeroZeroZeroZero

Extend

l.lhz

l.lhz

l.lhz

l.lhz

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

.

.

.

.

.

.

. 0

.

I

16bits

opcode 0x25

6 bits

l.lhz

rD,I(rA)

l.lhz

rD,I(rA)

l.lhz rD,I(rA)

l.lhz

rD,I(rA)

D

5 bits

A

5 bits

立即数被符号扩展到通用寄存器 rA 的宽度,然后该值与通用寄存器 rA 的值相加,所得

结果代表着一个有效的地址。在存储器地址 EA 处的半字被 load 到通用寄存器 rD 的低 16bit

中。通用寄存器 rD 的高位的值由 0 值来代替。

EA < - exts(Immediate) + rA[31:0]

rD[15:0] < - (EA)[15:0]

rD[31:16] < - 0

异常模式为:

TLB miss

Page fault

Bus error

Alignment

l.lws

l.lws

l.lws

l.lws

Extend

Single WordWordWordWord andandandand Extend

Single

LoadLoadLoadLoad Single

Extend withwithwithwith SignSignSignSign

Single

Extend

l.lws

l.lws

l.lws

l.lws

31

.

.

.

.

26 25

.

.

.

21 20

.

.

.

16 15

.

.

.

.

.

.

opcode 0x22

6 bits

l.lws

rD,I(rA)

l.lws

rD,I(rA)

l.lws rD,I(rA)

l.lws

rD,I(rA)

D

5 bits

A

5 bits

.

.

.

.

.

.

. 0

.

I

16bits

立即数被符号扩展到通用寄存器 rA 的宽度,然后该值与通用寄存器 rA 的值相加,所得

结果代表着一个有效的地址。在存储器地址 EA 处的单字被 load 到通用寄存器 rD[31:0]中。

EA < - exts(Immediate) + rA[31:0]

rD[31:0] < - (EA)[31:0]

异常模式为:

TLB miss

Page fault

Bus error

Alignment

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc