2Gb: x4, x8, x16 DDR3L SDRAM

Description

DDR3L SDRAM

MT41K512M4 – 64 Meg x 4 x 8 banks

MT41K256M8 – 32 Meg x 8 x 8 banks

MT41K128M16 – 16 Meg x 16 x 8 banks

Description

The 1.35V DDR3L SDRAM device is a low-voltage ver-

sion of the 1.5V DDR3 SDRAM device. Refer to the

DDR3 (1.5V) SDRAM data sheet specifications when

running in 1.5V compatible mode.

Features

• VDD = VDDQ = 1.35V (1.283–1.45V)

• Backward-compatible to VDD = VDDQ = 1.5V ±0.075V

• Differential bidirectional data strobe

• 8n-bit prefetch architecture

• Differential clock inputs (CK, CK#)

• 8 internal banks

• Nominal and dynamic on-die termination (ODT)

for data, strobe, and mask signals

• Programmable CAS (READ) latency (CL)

• Programmable posted CAS additive latency (AL)

• Programmable CAS (WRITE) latency (CWL)

• Fixed burst length (BL) of 8 and burst chop (BC) of 4

(via the mode register set [MRS])

• Selectable BC4 or BL8 on-the-fly (OTF)

• Self refresh mode

• TC of 0°C to +95°C

– 64ms, 8192-cycle refresh at 0°C to +85°C

– 32ms at +85°C to +95°C

• Self refresh temperature (SRT)

• Automatic self refresh (ASR)

• Write leveling

• Multipurpose register

• Output driver calibration

Options

• Configuration

– 512 Meg x 4

– 256 Meg x 8

– 128 Meg x 16

• FBGA package (Pb-free) – x4, x8

– 78-ball (8mm x 10.5mm)

Rev. M, K

– 78-ball FBGA (9mm x 11.5mm)

Rev. D

• FBGA package (Pb-free) – x16

– 96-ball FBGA (9mm x 14mm)

Rev. D

– 96-ball FBGA (8mm x 14mm)

Rev. K

• Timing – cycle time

– 1.071ns @ CL = 13 (DDR3-1866)

– 1.25ns @ CL = 11 (DDR3-1600)

– 1.5ns @ CL = 9 (DDR3-1333)

– 1.875ns @ CL = 7 (DDR3-1066)

• Operating temperature

– Commercial (0°C ≤ TC ≤ +95°C)

– Industrial (–40°C ≤ TC ≤ +95°C)

• Revision

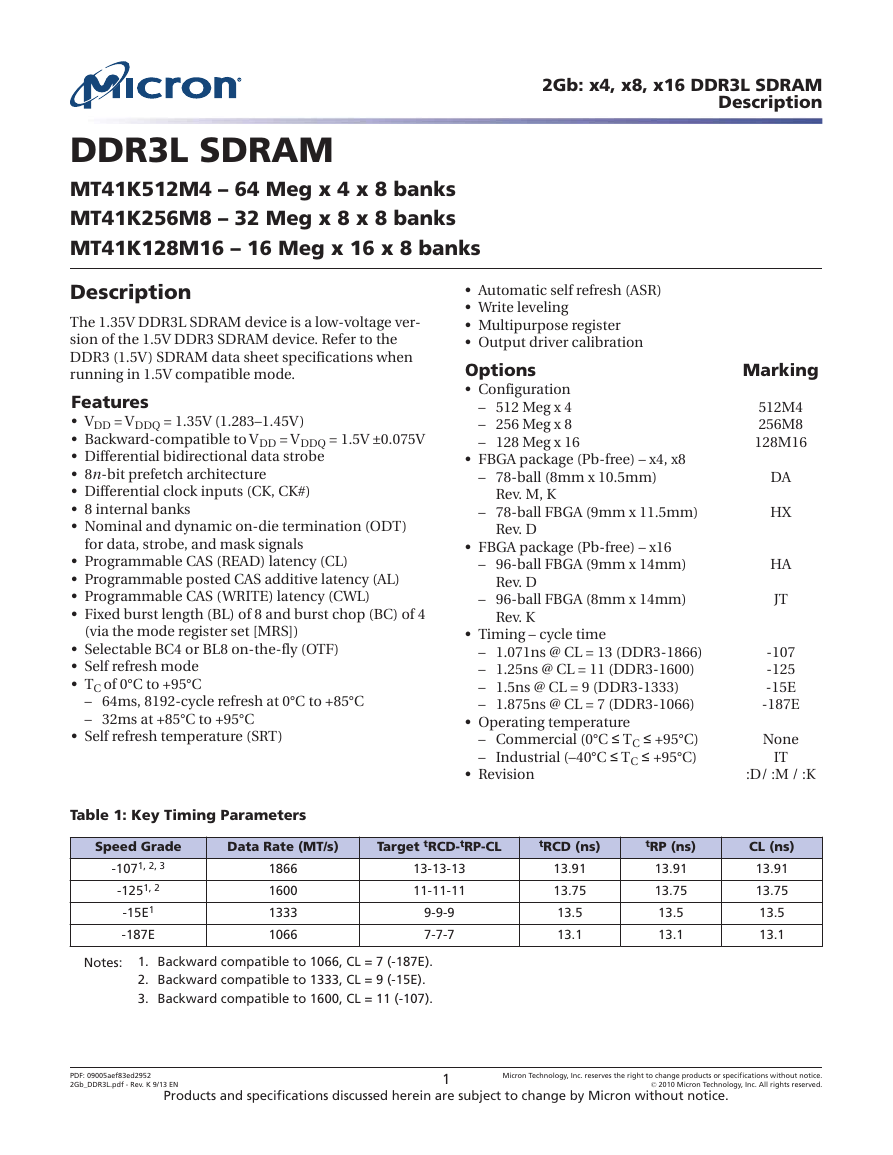

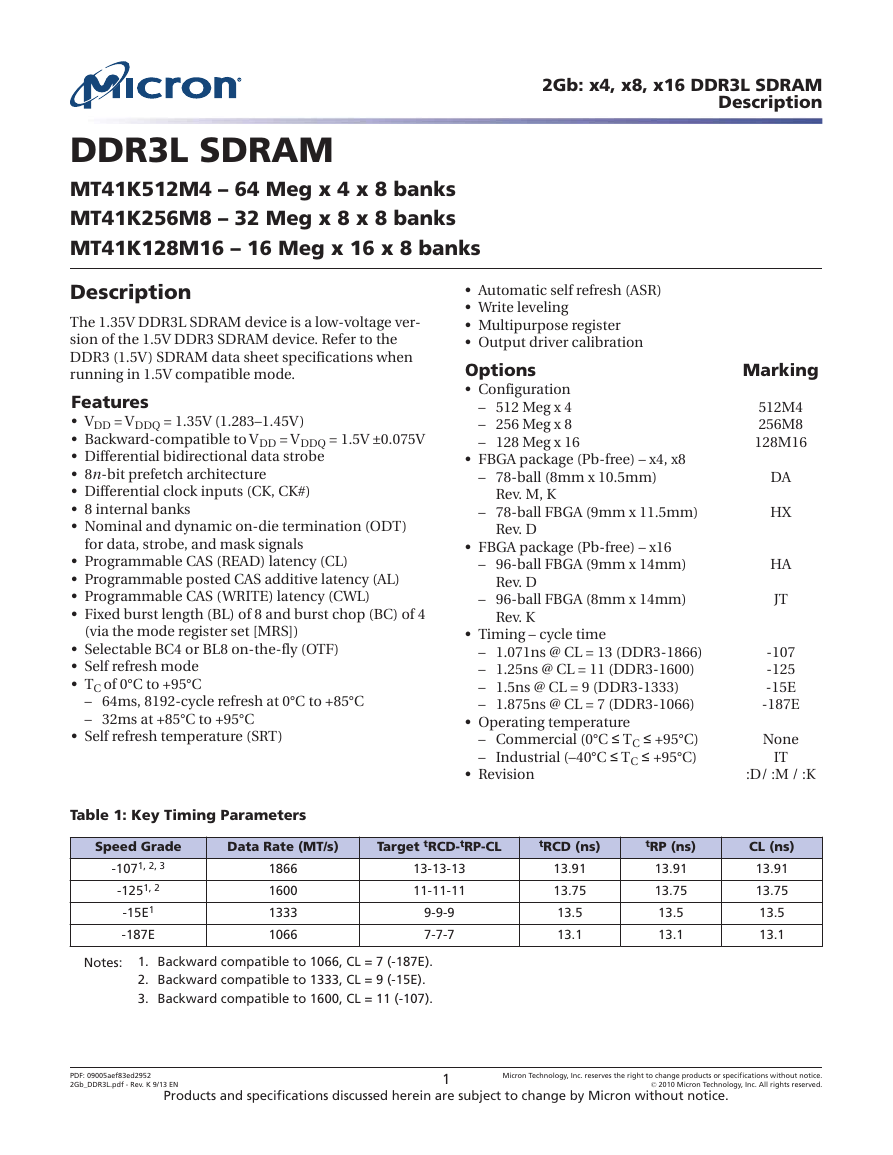

Table 1: Key Timing Parameters

Speed Grade

Data Rate (MT/s)

Target tRCD-tRP-CL

tRCD (ns)

tRP (ns)

-1071, 2, 3

-1251, 2

-15E1

-187E

1866

1600

1333

1066

13-13-13

11-11-11

9-9-9

7-7-7

13.91

13.75

13.5

13.1

13.91

13.75

13.5

13.1

Notes:

1. Backward compatible to 1066, CL = 7 (-187E).

2. Backward compatible to 1333, CL = 9 (-15E).

3. Backward compatible to 1600, CL = 11 (-107).

Marking

512M4

256M8

128M16

DA

HX

HA

JT

-107

-125

-15E

-187E

None

IT

:D/ :M / :K

CL (ns)

13.91

13.75

13.5

13.1

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

Products and specifications discussed herein are subject to change by Micron without notice.

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

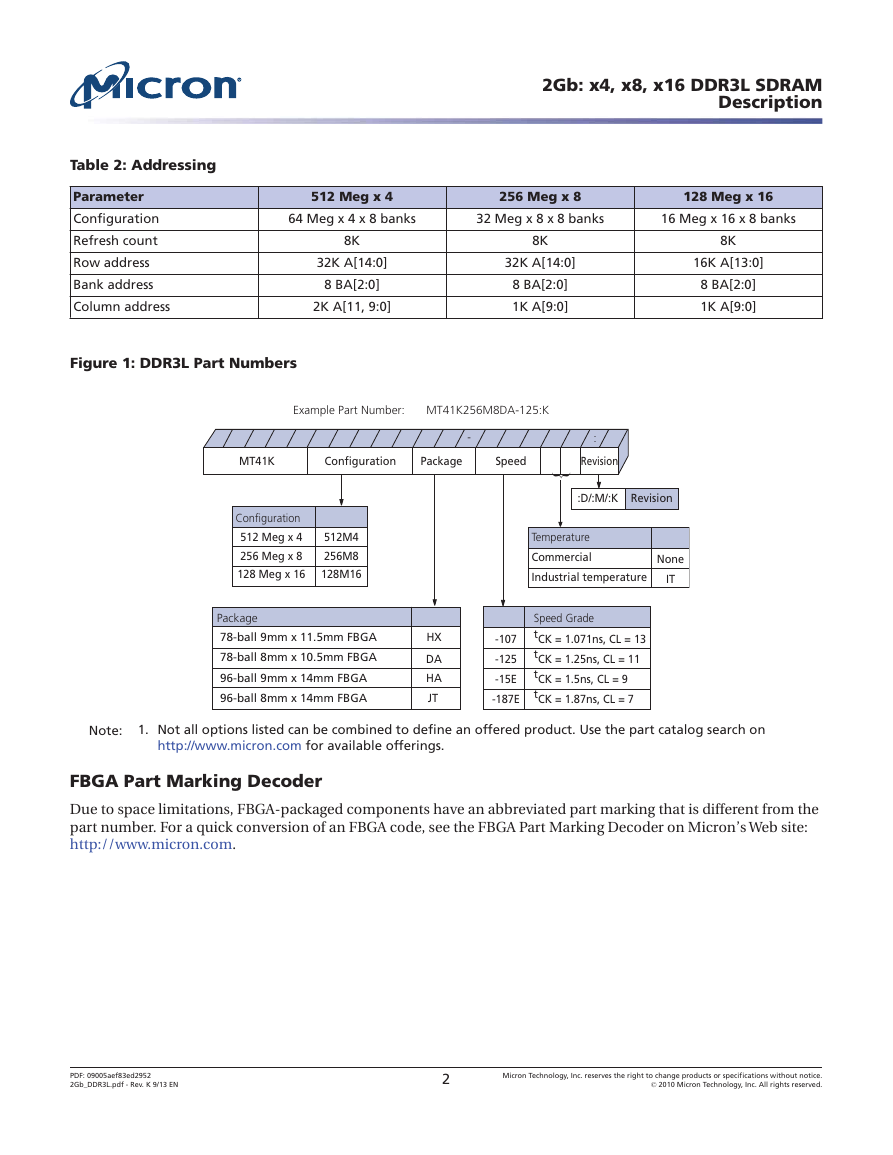

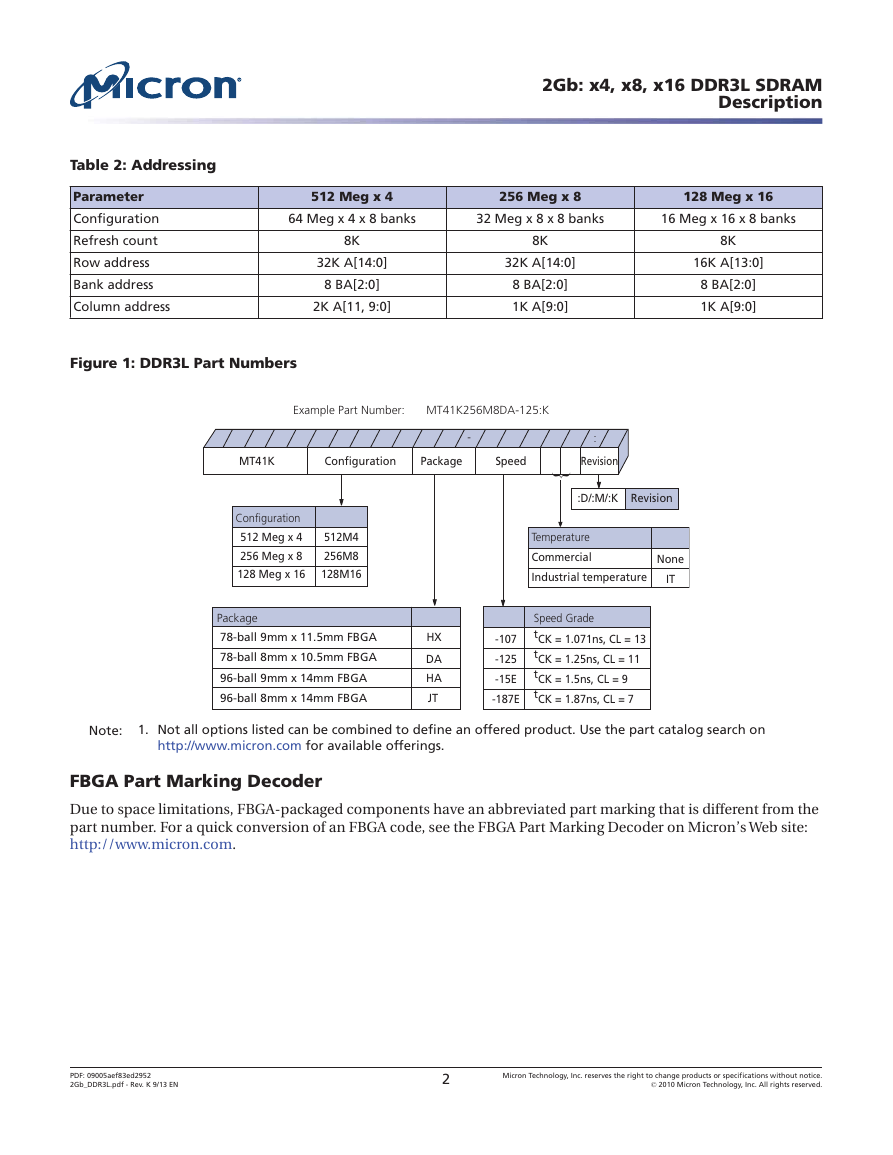

Table 2: Addressing

Parameter

Configuration

Refresh count

Row address

Bank address

Column address

512 Meg x 4

256 Meg x 8

128 Meg x 16

64 Meg x 4 x 8 banks

32 Meg x 8 x 8 banks

16 Meg x 16 x 8 banks

8K

32K A[14:0]

8 BA[2:0]

2K A[11, 9:0]

8K

32K A[14:0]

8 BA[2:0]

1K A[9:0]

8K

16K A[13:0]

8 BA[2:0]

1K A[9:0]

Figure 1: DDR3L Part Numbers

Example Part Number: MT41K256M8DA-125:K

MT41K

Configuration

Package

Speed

Revision

-

:

Configuration

512 Meg x 4

256 Meg x 8

128 Meg x 16

512M4

256M8

128M16

{

:D/:M/:K

Revision

Temperature

Commercial

Industrial temperature

None

IT

Package

78-ball 9mm x 11.5mm FBGA

78-ball 8mm x 10.5mm FBGA

96-ball 9mm x 14mm FBGA

96-ball 8mm x 14mm FBGA

HX

DA

HA

JT

-107

-125

-15E

-187E

Speed Grade

tCK = 1.071ns, CL = 13

tCK = 1.25ns, CL = 11

tCK = 1.5ns, CL = 9

tCK = 1.87ns, CL = 7

Note:

1. Not all options listed can be combined to define an offered product. Use the part catalog search on

http://www.micron.com for available offerings.

FBGA Part Marking Decoder

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the

part number. For a quick conversion of an FBGA code, see the FBGA Part Marking Decoder on Micron’s Web site:

http://www.micron.com.

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

Contents

State Diagram ................................................................................................................................................ 11

Functional Description ................................................................................................................................... 12

Industrial Temperature ............................................................................................................................... 12

General Notes ............................................................................................................................................ 12

Functional Block Diagrams ............................................................................................................................. 14

Ball Assignments and Descriptions ................................................................................................................. 16

Package Dimensions ....................................................................................................................................... 22

Electrical Specifications .................................................................................................................................. 26

Absolute Ratings ......................................................................................................................................... 26

Input/Output Capacitance .......................................................................................................................... 27

Thermal Characteristics .................................................................................................................................. 28

Electrical Specifications – IDD Specifications and Conditions ............................................................................ 30

Electrical Characteristics – IDD Specifications .................................................................................................. 41

Electrical Specifications – DC and AC .............................................................................................................. 44

DC Operating Conditions ........................................................................................................................... 44

Input Operating Conditions ........................................................................................................................ 45

DDR3L 1.35V AC Overshoot/Undershoot Specification ................................................................................ 49

DDR3L 1.35V Slew Rate Definitions for Single-Ended Input Signals .............................................................. 52

DDR3L 1.35V Slew Rate Definitions for Differential Input Signals ................................................................. 54

ODT Characteristics ....................................................................................................................................... 55

1.35V ODT Resistors ................................................................................................................................... 56

ODT Sensitivity .......................................................................................................................................... 57

ODT Timing Definitions ............................................................................................................................. 57

Output Driver Impedance ............................................................................................................................... 61

34 Ohm Output Driver Impedance .............................................................................................................. 62

DDR3L 34 Ohm Driver ................................................................................................................................ 63

DDR3L 34 Ohm Output Driver Sensitivity .................................................................................................... 64

DDR3L Alternative 40 Ohm Driver ............................................................................................................... 65

DDR3L 40 Ohm Output Driver Sensitivity .................................................................................................... 65

Output Characteristics and Operating Conditions ............................................................................................ 67

Reference Output Load ............................................................................................................................... 70

Slew Rate Definitions for Single-Ended Output Signals ................................................................................. 70

Slew Rate Definitions for Differential Output Signals .................................................................................... 72

Speed Bin Tables ............................................................................................................................................ 73

Electrical Characteristics and AC Operating Conditions ................................................................................... 77

Command and Address Setup, Hold, and Derating ........................................................................................... 97

Data Setup, Hold, and Derating ...................................................................................................................... 104

Commands – Truth Tables ............................................................................................................................. 112

Commands ................................................................................................................................................... 115

DESELECT ................................................................................................................................................ 115

NO OPERATION ........................................................................................................................................ 115

ZQ CALIBRATION LONG ........................................................................................................................... 115

ZQ CALIBRATION SHORT .......................................................................................................................... 115

ACTIVATE ................................................................................................................................................. 115

READ ........................................................................................................................................................ 115

WRITE ...................................................................................................................................................... 116

PRECHARGE ............................................................................................................................................. 117

REFRESH .................................................................................................................................................. 117

SELF REFRESH .......................................................................................................................................... 118

DLL Disable Mode ..................................................................................................................................... 119

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

Input Clock Frequency Change ...................................................................................................................... 123

Write Leveling ............................................................................................................................................... 125

Write Leveling Procedure ........................................................................................................................... 127

Write Leveling Mode Exit Procedure ........................................................................................................... 129

Initialization ................................................................................................................................................. 130

Voltage Initialization / Change ....................................................................................................................... 132

VDD Voltage Switching ............................................................................................................................... 133

Mode Registers .............................................................................................................................................. 134

Mode Register 0 (MR0) ................................................................................................................................... 135

Burst Length ............................................................................................................................................. 135

Burst Type ................................................................................................................................................. 136

DLL RESET ................................................................................................................................................ 137

Write Recovery .......................................................................................................................................... 137

Precharge Power-Down (Precharge PD) ...................................................................................................... 138

CAS Latency (CL) ....................................................................................................................................... 138

Mode Register 1 (MR1) ................................................................................................................................... 139

DLL Enable/DLL Disable ........................................................................................................................... 139

Output Drive Strength ............................................................................................................................... 140

OUTPUT ENABLE/DISABLE ...................................................................................................................... 140

TDQS Enable ............................................................................................................................................. 140

On-Die Termination .................................................................................................................................. 141

WRITE LEVELING ..................................................................................................................................... 141

POSTED CAS ADDITIVE Latency ................................................................................................................ 141

Mode Register 2 (MR2) ................................................................................................................................... 142

CAS Write Latency (CWL) ........................................................................................................................... 143

AUTO SELF REFRESH (ASR) ....................................................................................................................... 143

SELF REFRESH TEMPERATURE (SRT) ........................................................................................................ 144

SRT vs. ASR ............................................................................................................................................... 144

DYNAMIC ODT ......................................................................................................................................... 144

Mode Register 3 (MR3) ................................................................................................................................... 145

MULTIPURPOSE REGISTER (MPR) ............................................................................................................ 145

MPR Functional Description ...................................................................................................................... 146

MPR Register Address Definitions and Bursting Order ................................................................................. 147

MPR Read Predefined Pattern .................................................................................................................... 153

MODE REGISTER SET (MRS) Command ........................................................................................................ 153

ZQ CALIBRATION Operation ......................................................................................................................... 154

ACTIVATE Operation ..................................................................................................................................... 155

READ Operation ............................................................................................................................................ 157

WRITE Operation .......................................................................................................................................... 168

DQ Input Timing ....................................................................................................................................... 176

PRECHARGE Operation ................................................................................................................................. 178

SELF REFRESH Operation .............................................................................................................................. 178

Extended Temperature Usage ........................................................................................................................ 180

Power-Down Mode ........................................................................................................................................ 181

RESET Operation ........................................................................................................................................... 189

On-Die Termination (ODT) ............................................................................................................................ 191

Functional Representation of ODT ............................................................................................................. 191

Nominal ODT ............................................................................................................................................ 191

Dynamic ODT ............................................................................................................................................... 193

Dynamic ODT Special Use Case ................................................................................................................. 193

Functional Description .............................................................................................................................. 193

Synchronous ODT Mode ................................................................................................................................ 199

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

ODT Latency and Posted ODT .................................................................................................................... 199

Timing Parameters .................................................................................................................................... 199

ODT Off During READs .............................................................................................................................. 202

Asynchronous ODT Mode .............................................................................................................................. 204

Synchronous to Asynchronous ODT Mode Transition (Power-Down Entry) .................................................. 206

Asynchronous to Synchronous ODT Mode Transition (Power-Down Exit) ........................................................ 208

Asynchronous to Synchronous ODT Mode Transition (Short CKE Pulse) ...................................................... 210

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

List of Figures

Figure 1: DDR3L Part Numbers ........................................................................................................................ 2

Figure 2: Simplified State Diagram ................................................................................................................. 11

Figure 3: 512 Meg x 4 Functional Block Diagram ............................................................................................. 14

Figure 4: 256 Meg x 8 Functional Block Diagram ............................................................................................. 15

Figure 5: 128 Meg x 16 Functional Block Diagram ........................................................................................... 15

Figure 6: 78-Ball FBGA – x4, x8 Ball Assignments (Top View) ........................................................................... 16

Figure 7: 96-Ball FBGA – x16 Ball Assignments (Top View) ............................................................................... 17

Figure 8: 78-Ball FBGA – x4, x8 (DA) ............................................................................................................... 22

Figure 9: 78-Ball FBGA – x4, x8 (HX) ............................................................................................................... 23

Figure 10: 96-Ball FBGA – x16 (HA) ................................................................................................................. 24

Figure 11: 96-Ball FBGA – x16 (JT) .................................................................................................................. 25

Figure 12: Thermal Measurement Point ......................................................................................................... 29

Figure 13: DDR3L 1.35V Input Signal .............................................................................................................. 48

Figure 14: Overshoot ..................................................................................................................................... 49

Figure 15: Undershoot ................................................................................................................................... 49

Figure 16: VIX for Differential Signals .............................................................................................................. 50

Figure 17: Single-Ended Requirements for Differential Signals ........................................................................ 50

Figure 18: Definition of Differential AC-Swing and tDVAC ............................................................................... 51

Figure 19: Nominal Slew Rate Definition for Single-Ended Input Signals .......................................................... 53

Figure 20: DDR3L 1.35V Nominal Differential Input Slew Rate Definition for DQS, DQS# and CK, CK# .............. 54

Figure 21: ODT Levels and I-V Characteristics ................................................................................................ 55

Figure 22: ODT Timing Reference Load .......................................................................................................... 58

Figure 23: tAON and tAOF Definitions ............................................................................................................ 59

Figure 24: tAONPD and tAOFPD Definitions ................................................................................................... 59

Figure 25: tADC Definition ............................................................................................................................. 60

Figure 26: Output Driver ................................................................................................................................ 61

Figure 27: DQ Output Signal .......................................................................................................................... 68

Figure 28: Differential Output Signal .............................................................................................................. 69

Figure 29: Reference Output Load for AC Timing and Output Slew Rate ........................................................... 70

Figure 30: Nominal Slew Rate Definition for Single-Ended Output Signals ....................................................... 71

Figure 31: Nominal Differential Output Slew Rate Definition for DQS, DQS# .................................................... 72

Figure 32: Nominal Slew Rate and tVAC for tIS (Command and Address – Clock) ............................................. 100

Figure 33: Nominal Slew Rate for tIH (Command and Address – Clock) ........................................................... 101

Figure 34: Tangent Line for tIS (Command and Address – Clock) .................................................................... 102

Figure 35: Tangent Line for tIH (Command and Address – Clock) .................................................................... 103

Figure 36: Nominal Slew Rate and tVAC for tDS (DQ – Strobe) ......................................................................... 108

Figure 37: Nominal Slew Rate for tDH (DQ – Strobe) ...................................................................................... 109

Figure 38: Tangent Line for tDS (DQ – Strobe) ................................................................................................ 110

Figure 39: Tangent Line for tDH (DQ – Strobe) ............................................................................................... 111

Figure 40: Refresh Mode ............................................................................................................................... 118

Figure 41: DLL Enable Mode to DLL Disable Mode ........................................................................................ 120

Figure 42: DLL Disable Mode to DLL Enable Mode ........................................................................................ 121

Figure 43: DLL Disable tDQSCK .................................................................................................................... 122

Figure 44: Change Frequency During Precharge Power-Down ........................................................................ 124

Figure 45: Write Leveling Concept ................................................................................................................. 125

Figure 46: Write Leveling Sequence ............................................................................................................... 128

Figure 47: Write Leveling Exit Procedure ....................................................................................................... 129

Figure 48: Initialization Sequence ................................................................................................................. 131

Figure 49: VDD Voltage Switching .................................................................................................................. 133

Figure 50: MRS to MRS Command Timing (tMRD) ......................................................................................... 134

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

6

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

Figure 51: MRS to nonMRS Command Timing (tMOD) .................................................................................. 135

Figure 52: Mode Register 0 (MR0) Definitions ................................................................................................ 136

Figure 53: READ Latency .............................................................................................................................. 138

Figure 54: Mode Register 1 (MR1) Definition ................................................................................................. 139

Figure 55: READ Latency (AL = 5, CL = 6) ....................................................................................................... 142

Figure 56: Mode Register 2 (MR2) Definition ................................................................................................. 143

Figure 57: CAS Write Latency ........................................................................................................................ 143

Figure 58: Mode Register 3 (MR3) Definition ................................................................................................. 145

Figure 59: Multipurpose Register (MPR) Block Diagram ................................................................................. 146

Figure 60: MPR System Read Calibration with BL8: Fixed Burst Order Single Readout ..................................... 149

Figure 61: MPR System Read Calibration with BL8: Fixed Burst Order, Back-to-Back Readout .......................... 150

Figure 62: MPR System Read Calibration with BC4: Lower Nibble, Then Upper Nibble .................................... 151

Figure 63: MPR System Read Calibration with BC4: Upper Nibble, Then Lower Nibble .................................... 152

Figure 64: ZQ CALIBRATION Timing (ZQCL and ZQCS) ................................................................................. 154

Figure 65: Example: Meeting tRRD (MIN) and tRCD (MIN) ............................................................................. 155

Figure 66: Example: tFAW ............................................................................................................................. 156

Figure 67: READ Latency .............................................................................................................................. 157

Figure 68: Consecutive READ Bursts (BL8) .................................................................................................... 159

Figure 69: Consecutive READ Bursts (BC4) .................................................................................................... 159

Figure 70: Nonconsecutive READ Bursts ....................................................................................................... 160

Figure 71: READ (BL8) to WRITE (BL8) .......................................................................................................... 160

Figure 72: READ (BC4) to WRITE (BC4) OTF .................................................................................................. 161

Figure 73: READ to PRECHARGE (BL8) .......................................................................................................... 161

Figure 74: READ to PRECHARGE (BC4) ......................................................................................................... 162

Figure 75: READ to PRECHARGE (AL = 5, CL = 6) ........................................................................................... 162

Figure 76: READ with Auto Precharge (AL = 4, CL = 6) ..................................................................................... 162

Figure 77: Data Output Timing – tDQSQ and Data Valid Window .................................................................... 164

Figure 78: Data Strobe Timing – READs ......................................................................................................... 165

Figure 79: Method for Calculating tLZ and tHZ ............................................................................................... 166

Figure 80: tRPRE Timing ............................................................................................................................... 166

Figure 81: tRPST Timing ............................................................................................................................... 167

Figure 82: tWPRE Timing .............................................................................................................................. 169

Figure 83: tWPST Timing .............................................................................................................................. 169

Figure 84: WRITE Burst ................................................................................................................................ 170

Figure 85: Consecutive WRITE (BL8) to WRITE (BL8) ..................................................................................... 171

Figure 86: Consecutive WRITE (BC4) to WRITE (BC4) via OTF ........................................................................ 171

Figure 87: Nonconsecutive WRITE to WRITE ................................................................................................. 172

Figure 88: WRITE (BL8) to READ (BL8) .......................................................................................................... 172

Figure 89: WRITE to READ (BC4 Mode Register Setting) ................................................................................. 173

Figure 90: WRITE (BC4 OTF) to READ (BC4 OTF) ........................................................................................... 174

Figure 91: WRITE (BL8) to PRECHARGE ........................................................................................................ 175

Figure 92: WRITE (BC4 Mode Register Setting) to PRECHARGE ...................................................................... 175

Figure 93: WRITE (BC4 OTF) to PRECHARGE ................................................................................................ 176

Figure 94: Data Input Timing ........................................................................................................................ 177

Figure 95: Self Refresh Entry/Exit Timing ...................................................................................................... 179

Figure 96: Active Power-Down Entry and Exit ................................................................................................ 183

Figure 97: Precharge Power-Down (Fast-Exit Mode) Entry and Exit ................................................................. 183

Figure 98: Precharge Power-Down (Slow-Exit Mode) Entry and Exit ................................................................ 184

Figure 99: Power-Down Entry After READ or READ with Auto Precharge (RDAP) ............................................. 184

Figure 100: Power-Down Entry After WRITE .................................................................................................. 185

Figure 101: Power-Down Entry After WRITE with Auto Precharge (WRAP) ...................................................... 185

Figure 102: REFRESH to Power-Down Entry .................................................................................................. 186

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

7

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2Gb: x4, x8, x16 DDR3L SDRAM

Description

Figure 103: ACTIVATE to Power-Down Entry ................................................................................................. 186

Figure 104: PRECHARGE to Power-Down Entry ............................................................................................. 187

Figure 105: MRS Command to Power-Down Entry ......................................................................................... 187

Figure 106: Power-Down Exit to Refresh to Power-Down Entry ....................................................................... 188

Figure 107: RESET Sequence ......................................................................................................................... 190

Figure 108: On-Die Termination ................................................................................................................... 191

Figure 109: Dynamic ODT: ODT Asserted Before and After the WRITE, BC4 .................................................... 196

Figure 110: Dynamic ODT: Without WRITE Command .................................................................................. 196

Figure 111: Dynamic ODT: ODT Pin Asserted Together with WRITE Command for 6 Clock Cycles, BL8 ............ 197

Figure 112: Dynamic ODT: ODT Pin Asserted with WRITE Command for 6 Clock Cycles, BC4 .......................... 198

Figure 113: Dynamic ODT: ODT Pin Asserted with WRITE Command for 4 Clock Cycles, BC4 .......................... 198

Figure 114: Synchronous ODT ...................................................................................................................... 200

Figure 115: Synchronous ODT (BC4) ............................................................................................................. 201

Figure 116: ODT During READs .................................................................................................................... 203

Figure 117: Asynchronous ODT Timing with Fast ODT Transition .................................................................. 205

Figure 118: Synchronous to Asynchronous Transition During Precharge Power-Down (DLL Off) Entry ............ 207

Figure 119: Asynchronous to Synchronous Transition During Precharge Power-Down (DLL Off) Exit ............... 209

Figure 120: Transition Period for Short CKE LOW Cycles with Entry and Exit Period Overlapping ..................... 211

Figure 121: Transition Period for Short CKE HIGH Cycles with Entry and Exit Period Overlapping ................... 211

PDF: 09005aef83ed2952

2Gb_DDR3L.pdf - Rev. K 9/13 EN

8

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc