AD9954 芯片资料-20101207

AD9954- Direct Digital Synthesizer

400 MSPS 14-Bit, 1.8 V CMOS

功能: ..................................................................................................................... 2

应用 ......................................................................................................................... 2

概述 ......................................................................................................................... 2

AD9954 电气特性 ...................................................................................................... 3

最大操作范围 ........................................................................................................... 4

Table 2. ................................................................................................................... 4

管脚定义 .................................................................................................................. 4

管脚功能描述 ........................................................................................................... 4

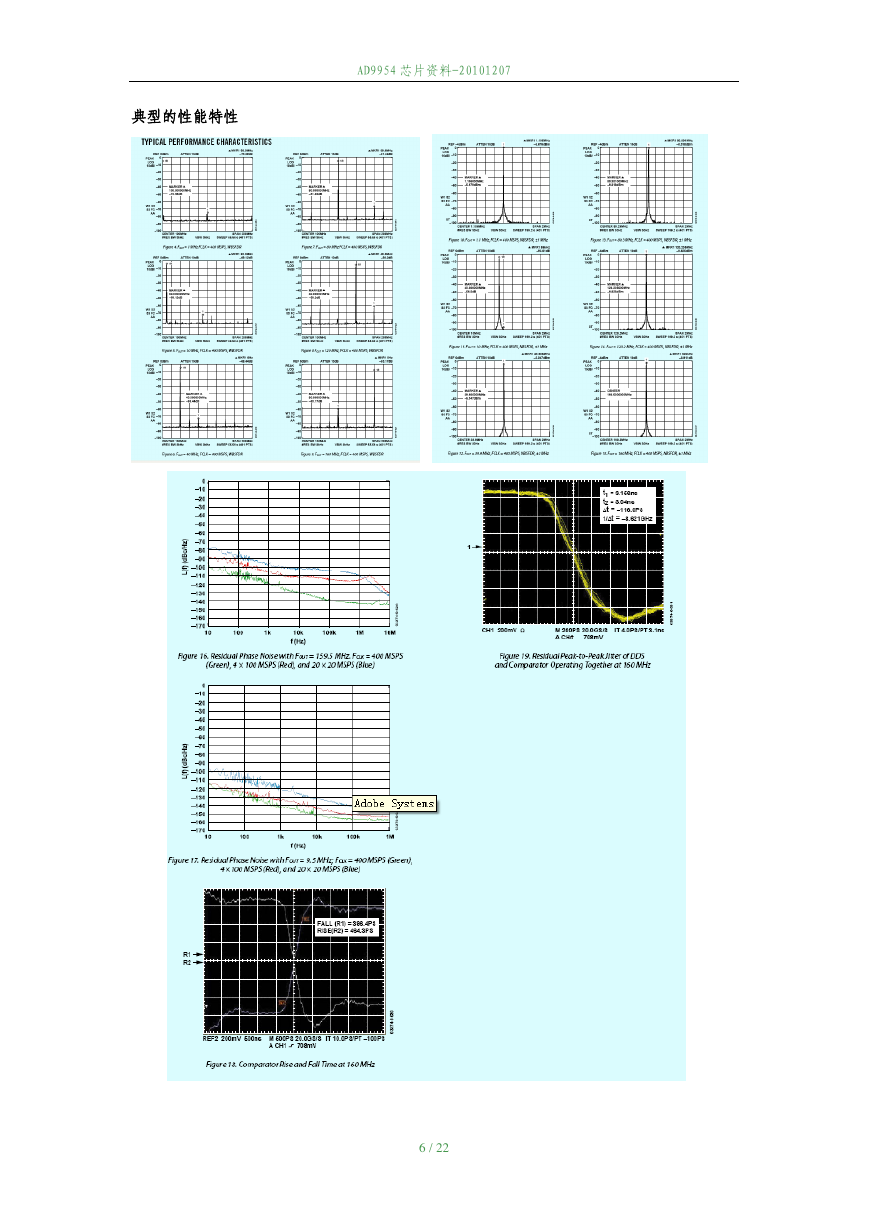

典型的性能特性 ........................................................................................................ 6

原理 ......................................................................................................................... 7

器件块 ............................................................................................................... 7

控制寄存器位描述 ............................................................................................. 10

Other Register Descriptions 其他寄存器描述 ....................................................... 14

Programming AD9954 Features-- AD9954 编程特性 ............................................. 18

SERIAL PORT OPERATION 串口操作 ................................................................. 19

INSTRUCTION BYTE 指令字节 ............................................................................ 20

SERIAL INTERFACE PORT PIN DESCRIPTION 串行接口管脚描述 ........................... 20

MSB/LSB TRANSFERS ........................................................................................ 20

RAM I/O VIA SERIAL PORT ................................................................................ 21

Power-Down Functions of the AD9954 AD9954 省电功能 ................................ 21

1 / 22

�

AD9954 芯片资料-20101207

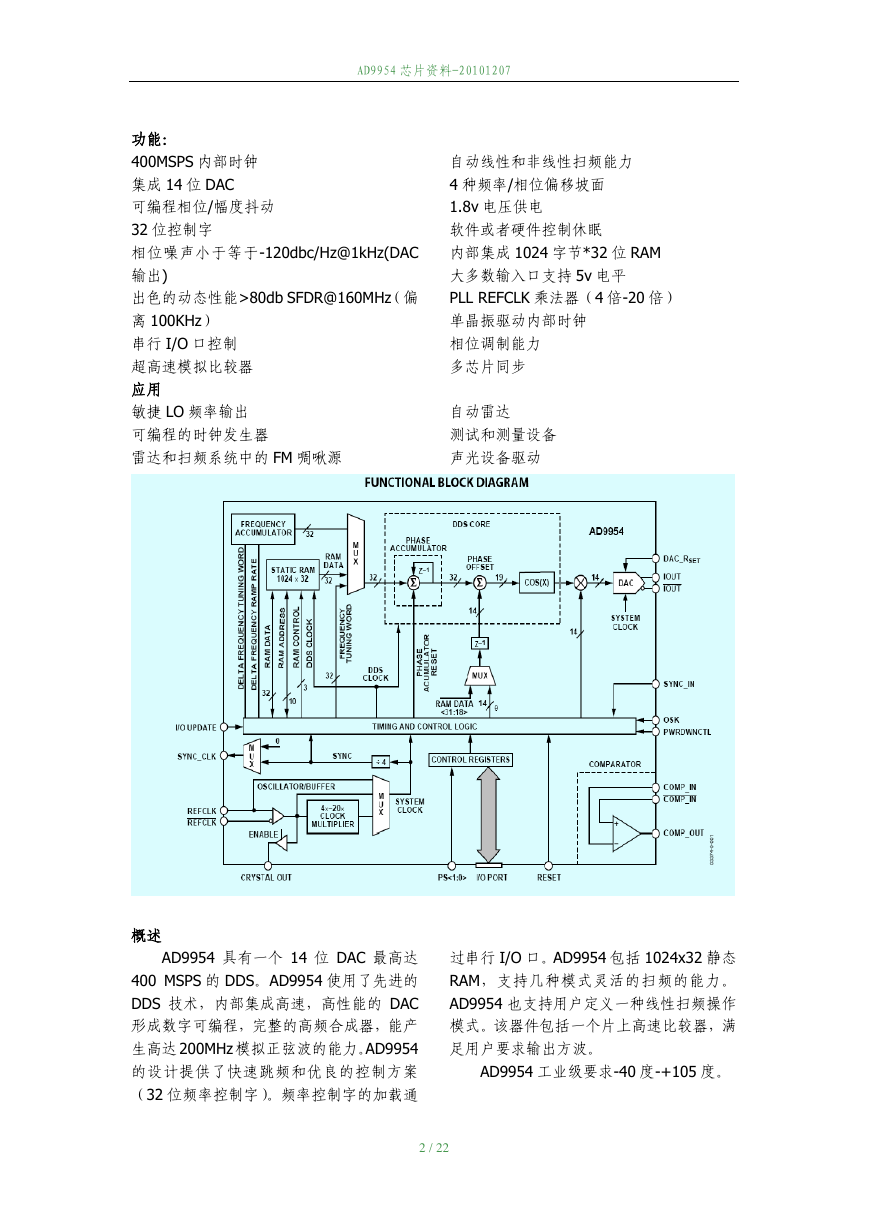

功能:

400MSPS 内部时钟

集成 14 位 DAC

可编程相位/幅度抖动

32 位控制字

相位噪声小于等于-120dbc/Hz@1kHz(DAC

输出)

出色的动态性能>80db SFDR@160MHz(偏

离 100KHz)

串行 I/O 口控制

超高速模拟比较器

应用

敏捷 LO 频率输出

可编程的时钟发生器

雷达和扫频系统中的 FM 啁啾源

自动线性和非线性扫频能力

4 种频率/相位偏移坡面

1.8v 电压供电

软件或者硬件控制休眠

内部集成 1024 字节*32 位 RAM

大多数输入口支持 5v 电平

PLL REFCLK 乘法器(4 倍-20 倍)

单晶振驱动内部时钟

相位调制能力

多芯片同步

自动雷达

测试和测量设备

声光设备驱动

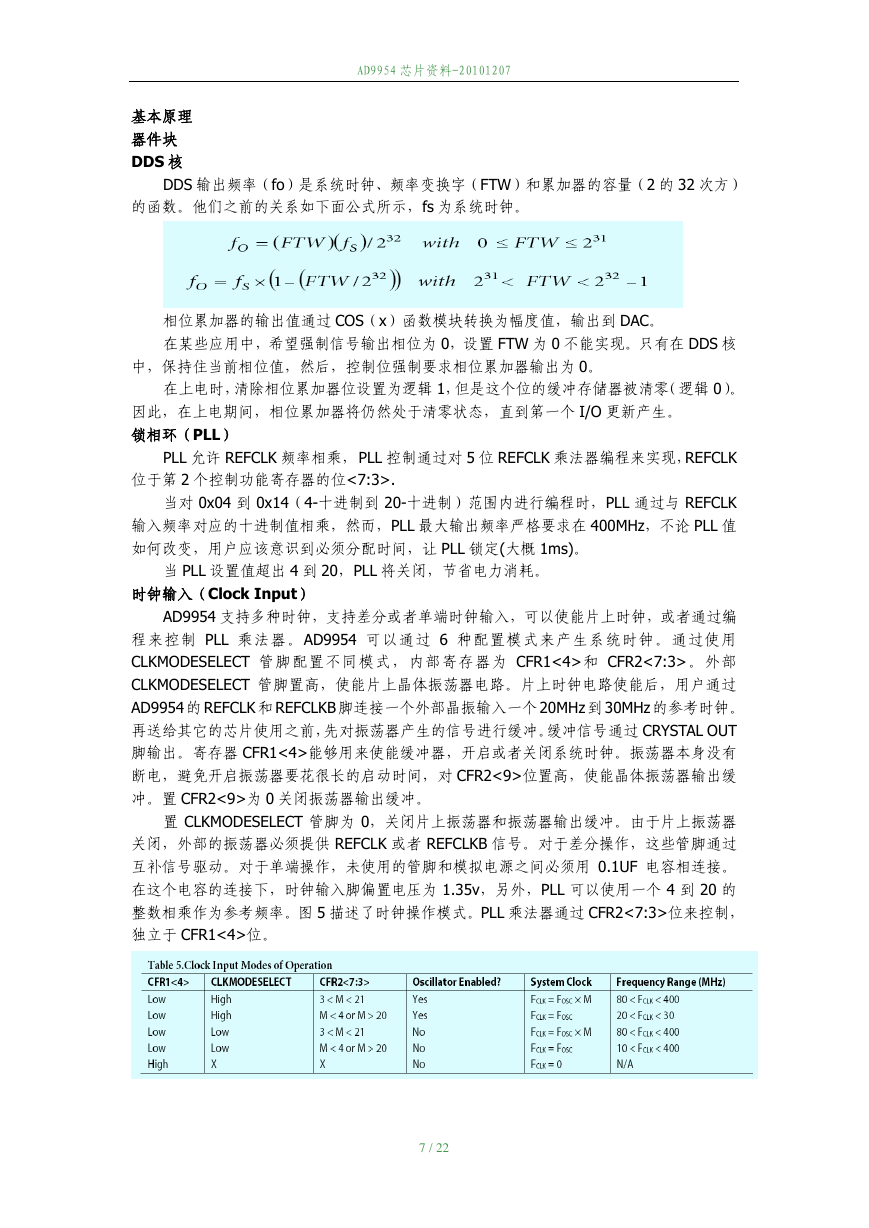

概述

AD9954 具有一个 14 位 DAC 最高达

400 MSPS 的 DDS。AD9954 使用了先进的

DDS 技术,内部集成高速,高性能的 DAC

形成数字可编程,完整的高频合成器,能产

生高达 200MHz 模拟正弦波的能力。AD9954

的设计提供了快速跳频和优良的控制方案

(32 位频率控制字)。频率控制字的加载通

过串行 I/O 口。AD9954 包括 1024x32 静态

RAM,支持几种模式灵活的扫频的能力。

AD9954 也支持用户定义一种线性扫频操作

模式。该器件包括一个片上高速比较器,满

足用户要求输出方波。

AD9954 工业级要求-40 度-+105 度。

2 / 22

�

AD9954 芯片资料-20101207

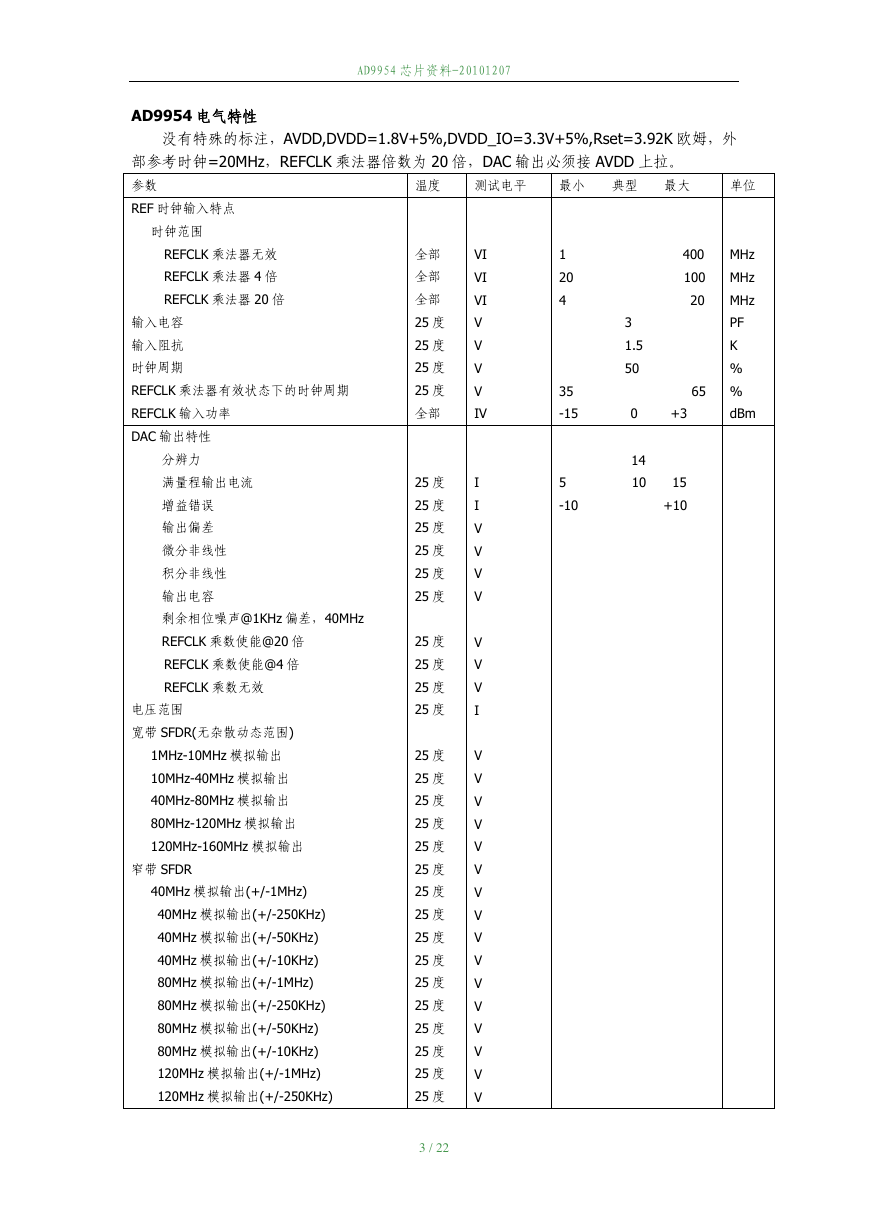

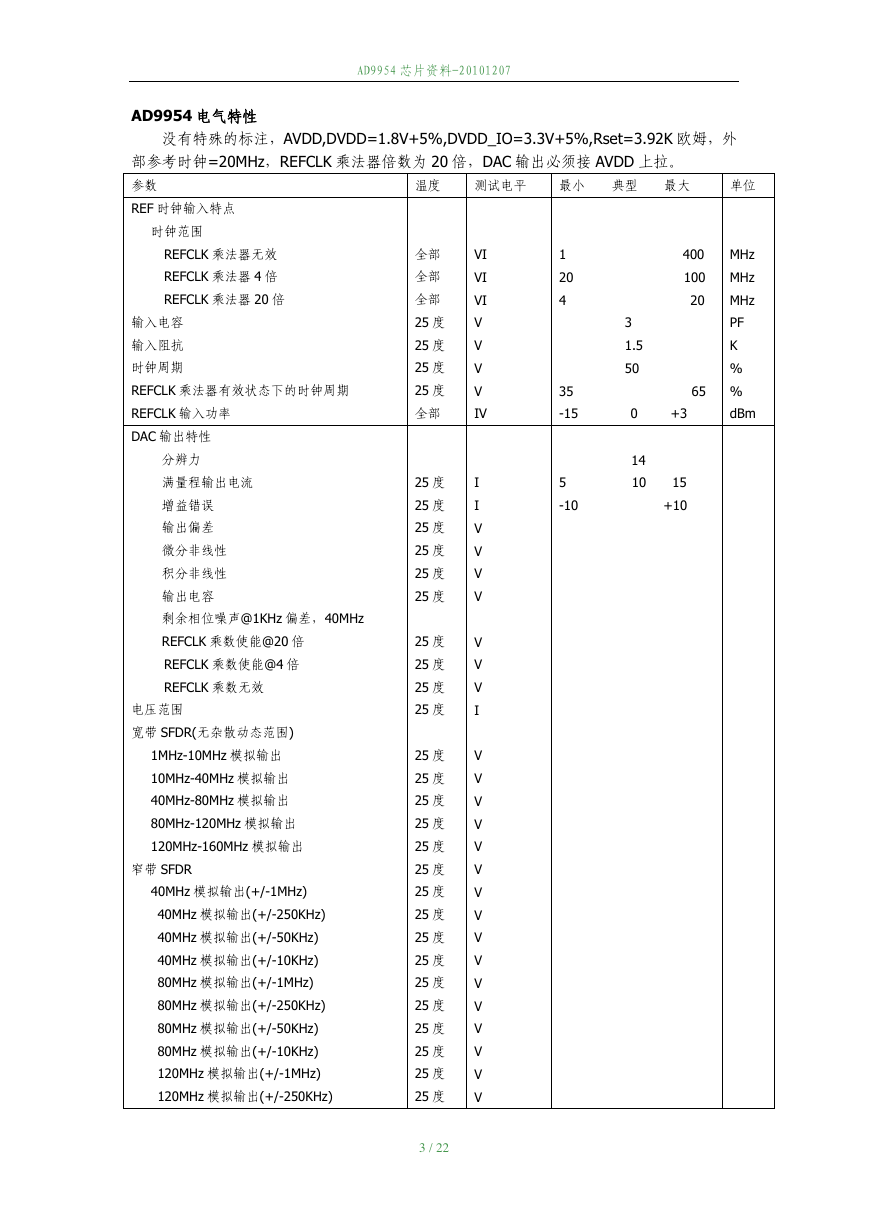

AD9954 电气特性

没有特殊的标注,AVDD,DVDD=1.8V+5%,DVDD_IO=3.3V+5%,Rset=3.92K 欧姆,外

部参考时钟=20MHz,REFCLK 乘法器倍数为 20 倍,DAC 输出必须接 AVDD 上拉。

参数

REF 时钟输入特点

时钟范围

REFCLK 乘法器无效

REFCLK 乘法器 4 倍

REFCLK 乘法器 20 倍

输入电容

输入阻抗

时钟周期

REFCLK 乘法器有效状态下的时钟周期

REFCLK 输入功率

DAC 输出特性

分辨力

满量程输出电流

增益错误

输出偏差

微分非线性

积分非线性

输出电容

剩余相位噪声@1KHz 偏差,40MHz

REFCLK 乘数使能@20 倍

REFCLK 乘数使能@4 倍

REFCLK 乘数无效

电压范围

宽带 SFDR(无杂散动态范围)

1MHz-10MHz 模拟输出

10MHz-40MHz 模拟输出

40MHz-80MHz 模拟输出

80MHz-120MHz 模拟输出

120MHz-160MHz 模拟输出

窄带 SFDR

40MHz 模拟输出(+/-1MHz)

40MHz 模拟输出(+/-250KHz)

40MHz 模拟输出(+/-50KHz)

40MHz 模拟输出(+/-10KHz)

80MHz 模拟输出(+/-1MHz)

80MHz 模拟输出(+/-250KHz)

80MHz 模拟输出(+/-50KHz)

80MHz 模拟输出(+/-10KHz)

120MHz 模拟输出(+/-1MHz)

120MHz 模拟输出(+/-250KHz)

温度

测试电平

最小 典型 最大

单位

1

20

4

400

MHz

100

MHz

20

MHz

3

1.5

50

35

65

PF

K

%

%

-15 0 +3

dBm

14

5 10 15

-10 +10

VI

VI

VI

V

V

V

V

IV

I

I

V

V

V

V

V

V

V

I

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

全部

全部

全部

25 度

25 度

25 度

25 度

全部

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

25 度

3 / 22

�

AD9954 芯片资料-20101207

120MHz 模拟输出(+/-50KHz)

120MHz 模拟输出(+/-10KHz)

160MHz 模拟输出(+/-1MHz)

160MHz 模拟输出(+/-250KHz)

160MHz 模拟输出(+/-50KHz)

160MHz 模拟输出(+/-10KHz)

V

V

V

V

V

25 度

25 度

25 度

25 度

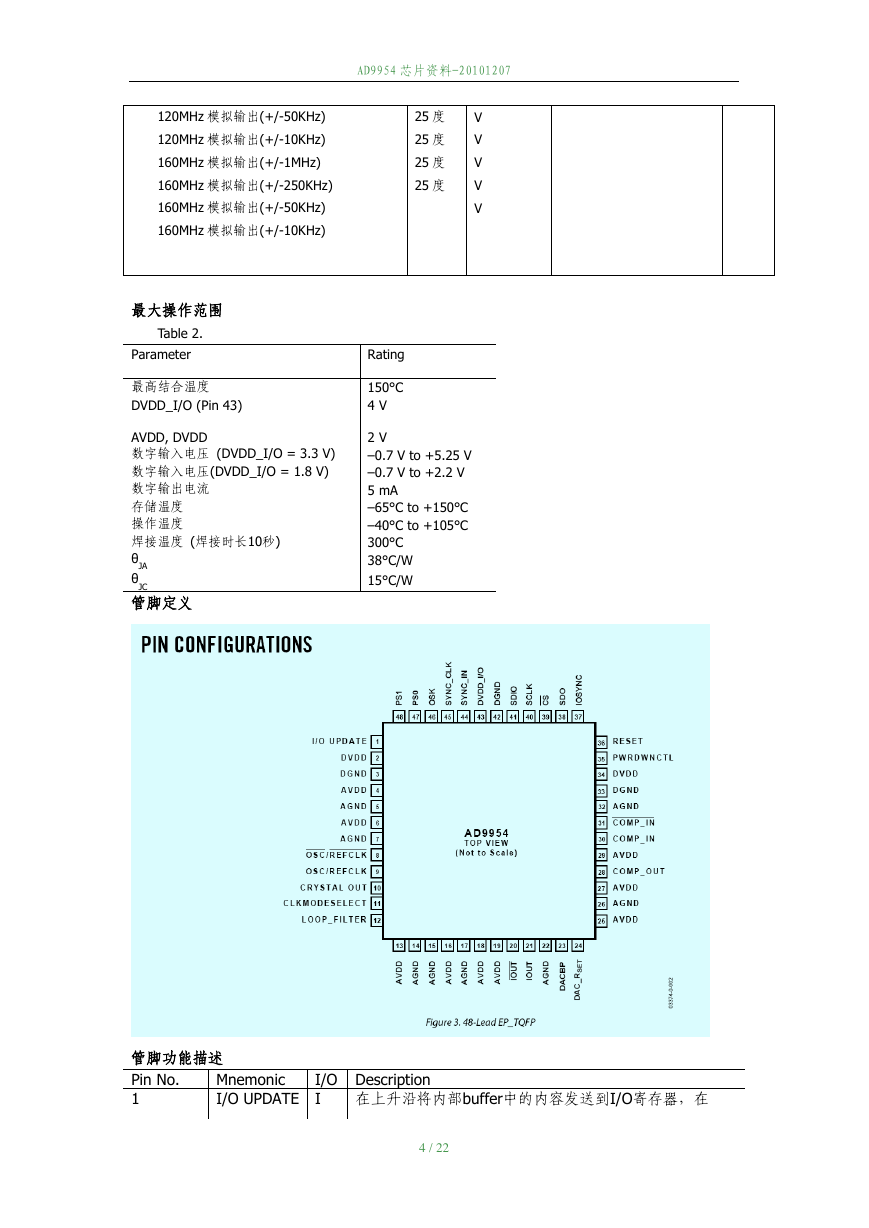

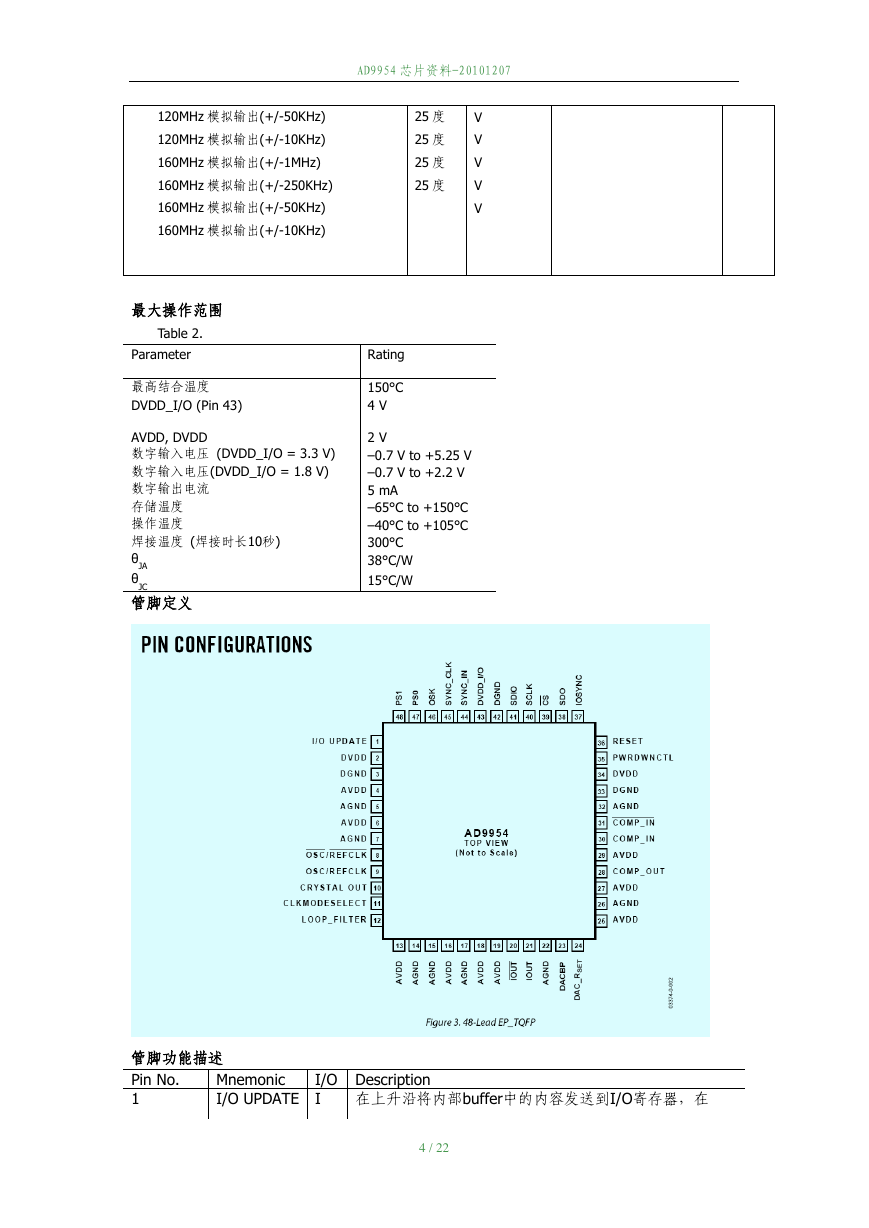

最大操作范围

Table 2.

Parameter

最高结合温度

DVDD_I/O (Pin 43)

AVDD, DVDD

数字输入电压 (DVDD_I/O = 3.3 V)

数字输入电压(DVDD_I/O = 1.8 V)

数字输出电流

存储温度

操作温度

焊接温度 (焊接时长10秒)

θ

JA

θ

JC

管脚定义

Rating

150°C

4 V

2 V

–0.7 V to +5.25 V

–0.7 V to +2.2 V

5 mA

–65°C to +150°C

–40°C to +105°C

300°C

38°C/W

15°C/W

管脚功能描述

Pin No.

1

Mnemonic

I/O UPDATE I 在上升沿将内部buffer中的内容发送到I/O寄存器,在

I/O Description

4 / 22

�

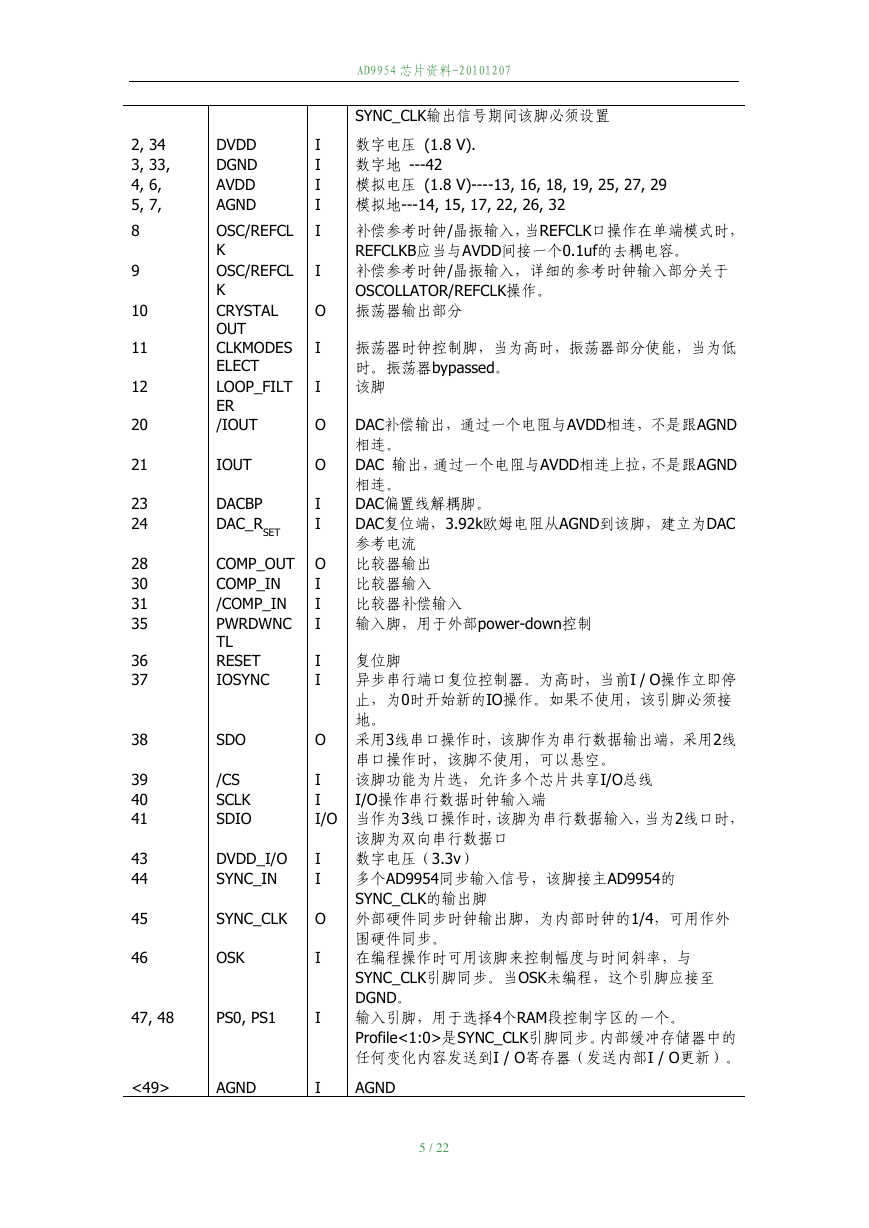

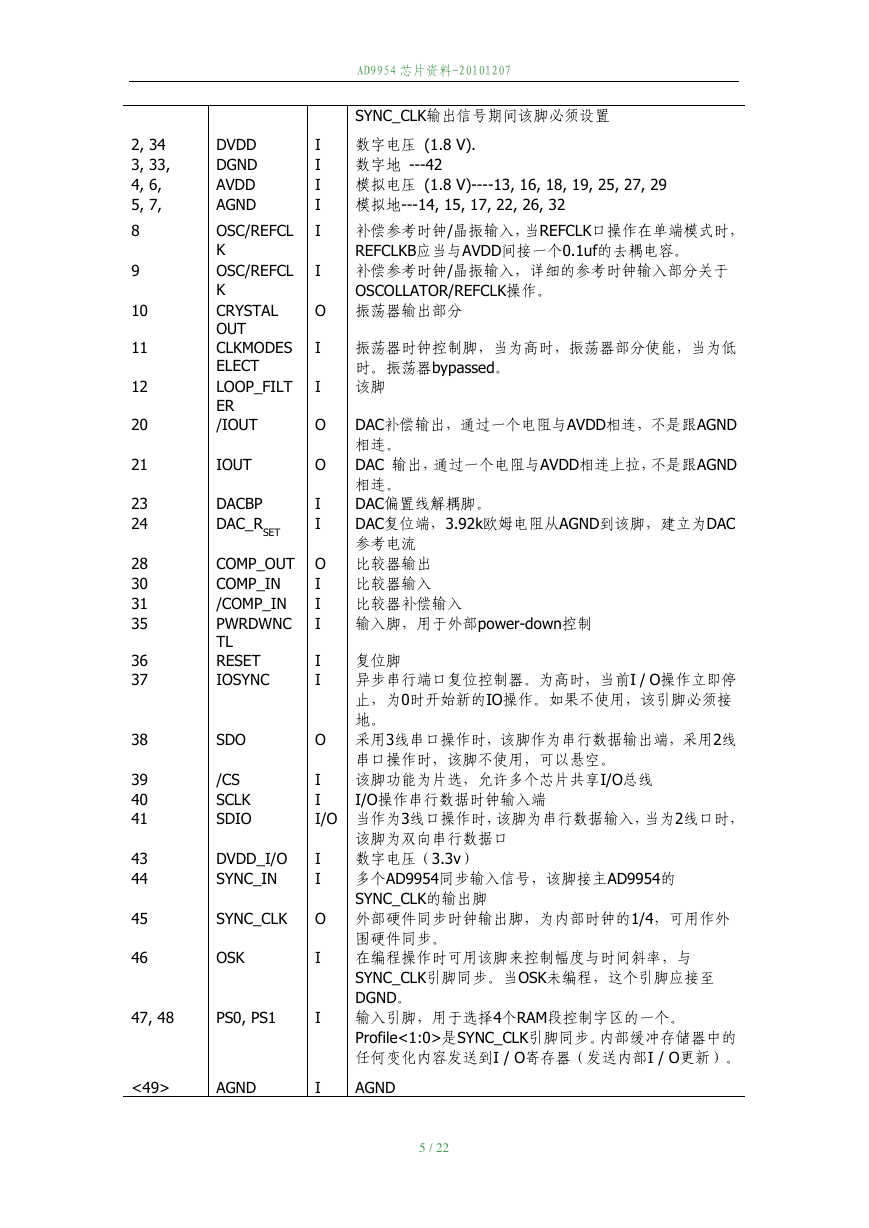

AD9954 芯片资料-20101207

SYNC_CLK输出信号期间该脚必须设臵

2, 34

3, 33,

4, 6,

5, 7,

DVDD

DGND

AVDD

AGND

I 数字电压 (1.8 V).

I 数字地 ---42

I 模拟电压 (1.8 V)----13, 16, 18, 19, 25, 27, 29

I 模拟地---14, 15, 17, 22, 26, 32

8

9

10

11

12

20

21

23

24

28

30

31

35

36

37

38

39

40

41

43

44

45

46

OSC/REFCL

K

OSC/REFCL

K

CRYSTAL

OUT

CLKMODES

ELECT

LOOP_FILT

ER

/IOUT

I 补偿参考时钟/晶振输入,当REFCLK口操作在单端模式时,

REFCLKB应当与AVDD间接一个0.1uf的去耦电容。

I 补偿参考时钟/晶振输入,详细的参考时钟输入部分关于

OSCOLLATOR/REFCLK操作。

O 振荡器输出部分

I 振荡器时钟控制脚,当为高时,振荡器部分使能,当为低

时。振荡器bypassed。

I 该脚

O DAC补偿输出,通过一个电阻与AVDD相连,不是跟AGND

相连。

IOUT

O DAC 输出,通过一个电阻与AVDD相连上拉,不是跟AGND

DACBP

DAC_R

SET

I

I

相连。

DAC偏臵线解耦脚。

DAC复位端,3.92k欧姆电阻从AGND到该脚,建立为DAC

参考电流

COMP_OUT O 比较器输出

I 比较器输入

COMP_IN

I 比较器补偿输入

/COMP_IN

I 输入脚,用于外部power-down控制

PWRDWNC

TL

RESET

IOSYNC

I 复位脚

I 异步串行端口复位控制器。为高时,当前I / O操作立即停

止,为0时开始新的IO操作。如果不使用,该引脚必须接

地。

SDO

O 采用3线串口操作时,该脚作为串行数据输出端,采用2线

串口操作时,该脚不使用,可以悬空。

/CS

SCLK

SDIO

I 该脚功能为片选,允许多个芯片共享I/O总线

I

I/O 当作为3线口操作时,该脚为串行数据输入,当为2线口时,

I/O操作串行数据时钟输入端

该脚为双向串行数据口

DVDD_I/O

SYNC_IN

I 数字电压(3.3v)

I 多个AD9954同步输入信号,该脚接主AD9954的

SYNC_CLK O 外部硬件同步时钟输出脚,为内部时钟的1/4,可用作外

SYNC_CLK的输出脚

围硬件同步。

OSK

I 在编程操作时可用该脚来控制幅度与时间斜率,与

SYNC_CLK引脚同步。当OSK未编程,这个引脚应接至

DGND。

47, 48

PS0, PS1

I 输入引脚,用于选择4个RAM段控制字区的一个。

Profile<1:0>是SYNC_CLK引脚同步。内部缓冲存储器中的

任何变化内容发送到I / O寄存器(发送内部I / O更新)。

<49>

AGND

I

AGND

5 / 22

�

AD9954 芯片资料-20101207

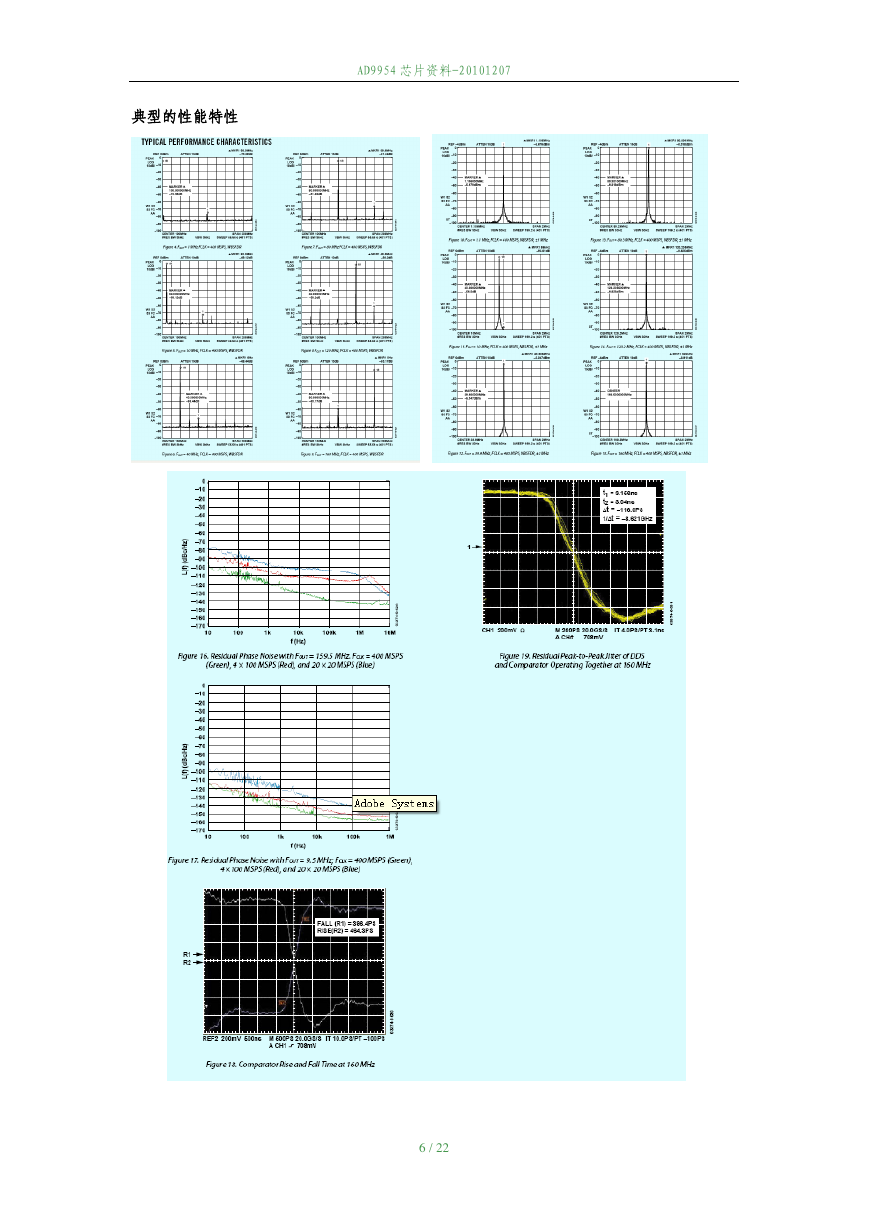

典型的性能特性

6 / 22

�

AD9954 芯片资料-20101207

基本原理

器件块

DDS 核

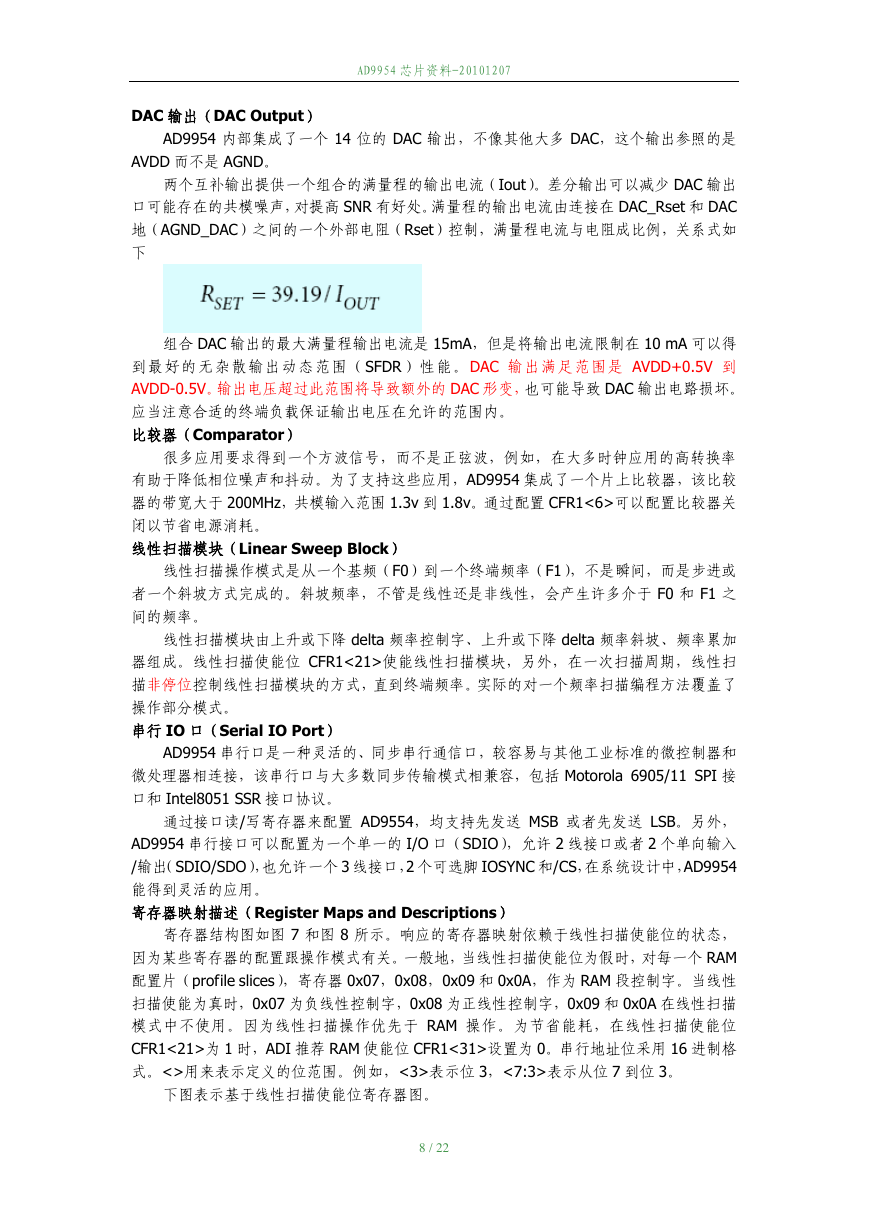

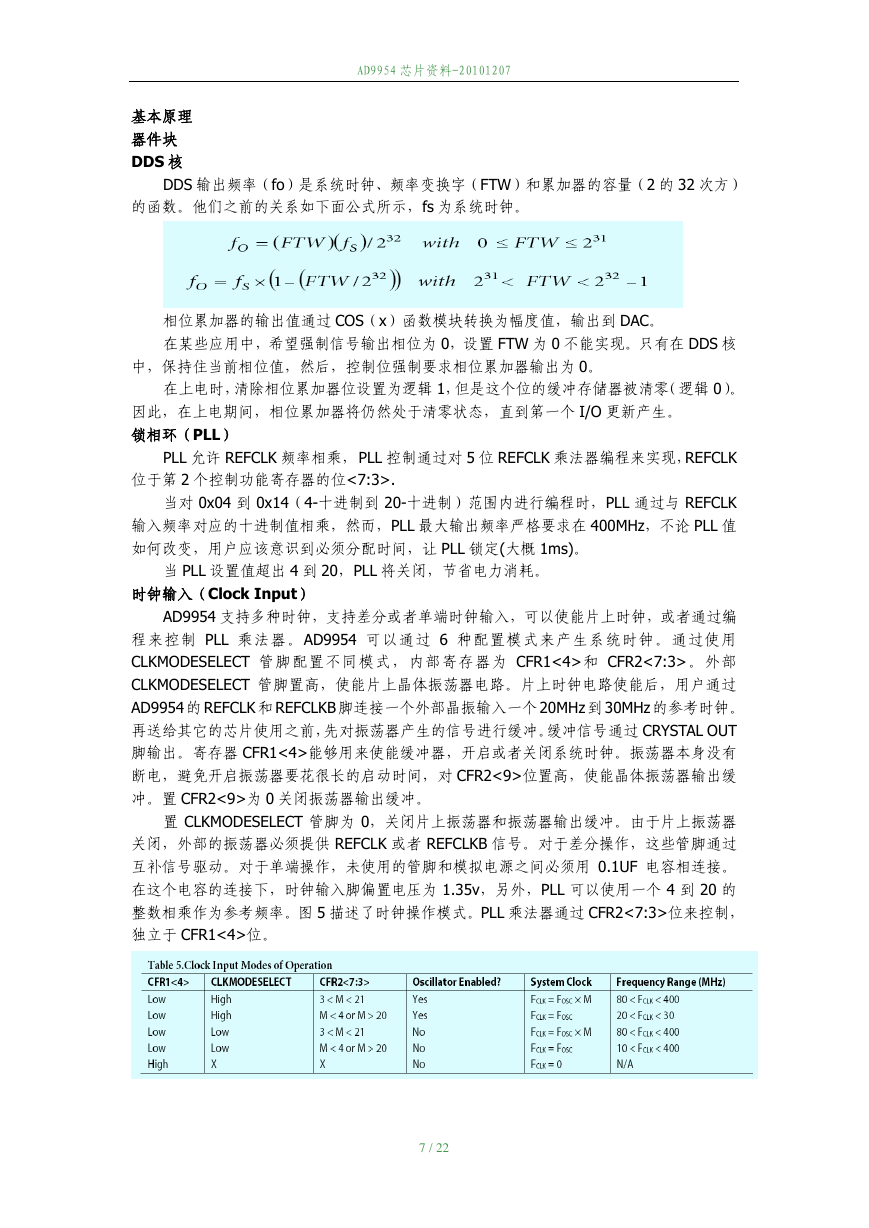

DDS 输出频率(fo)是系统时钟、频率变换字(FTW)和累加器的容量(2 的 32 次方)

的函数。他们之前的关系如下面公式所示,fs 为系统时钟。

相位累加器的输出值通过 COS(x)函数模块转换为幅度值,输出到 DAC。

在某些应用中,希望强制信号输出相位为 0,设臵 FTW 为 0 不能实现。只有在 DDS 核

中,保持住当前相位值,然后,控制位强制要求相位累加器输出为 0。

在上电时,清除相位累加器位设臵为逻辑 1,但是这个位的缓冲存储器被清零(逻辑 0)。

因此,在上电期间,相位累加器将仍然处于清零状态,直到第一个 I/O 更新产生。

锁相环(PLL)

PLL 允许 REFCLK 频率相乘, PLL 控制通过对 5 位 REFCLK 乘法器编程来实现,REFCLK

位于第 2 个控制功能寄存器的位<7:3>.

当对 0x04 到 0x14(4-十进制到 20-十进制)范围内进行编程时,PLL 通过与 REFCLK

输入频率对应的十进制值相乘,然而,PLL 最大输出频率严格要求在 400MHz,不论 PLL 值

如何改变,用户应该意识到必须分配时间,让 PLL 锁定(大概 1ms)。

当 PLL 设臵值超出 4 到 20,PLL 将关闭,节省电力消耗。

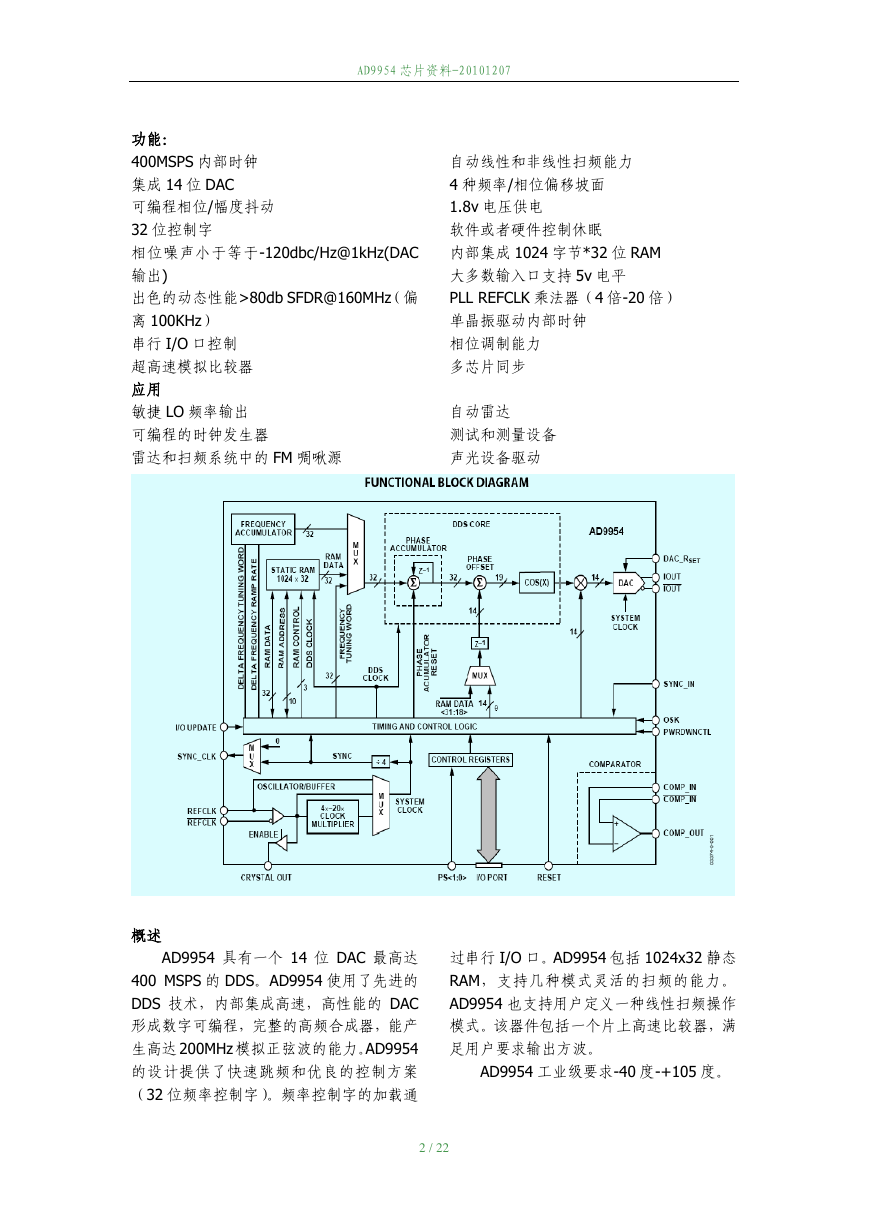

时钟输入(Clock Input)

AD9954 支持多种时钟,支持差分或者单端时钟输入,可以使能片上时钟,或者通过编

程来控制 PLL 乘法器。AD9954 可以通过 6 种配臵模式来产生系统时钟。通过使用

CLKMODESELECT 管脚配臵不同模式,内部寄存器为 CFR1<4>和 CFR2<7:3>。外部

CLKMODESELECT 管脚臵高,使能片上晶体振荡器电路。片上时钟电路使能后,用户通过

AD9954 的 REFCLK 和 REFCLKB 脚连接一个外部晶振输入一个 20MHz 到 30MHz 的参考时钟。

再送给其它的芯片使用之前,先对振荡器产生的信号进行缓冲。缓冲信号通过 CRYSTAL OUT

脚输出。寄存器 CFR1<4>能够用来使能缓冲器,开启或者关闭系统时钟。振荡器本身没有

断电,避免开启振荡器要花很长的启动时间,对 CFR2<9>位臵高,使能晶体振荡器输出缓

冲。臵 CFR2<9>为 0 关闭振荡器输出缓冲。

臵 CLKMODESELECT 管脚为 0,关闭片上振荡器和振荡器输出缓冲。由于片上振荡器

关闭,外部的振荡器必须提供 REFCLK 或者 REFCLKB 信号。对于差分操作,这些管脚通过

互补信号驱动。对于单端操作,未使用的管脚和模拟电源之间必须用 0.1UF 电容相连接。

在这个电容的连接下,时钟输入脚偏臵电压为 1.35v,另外,PLL 可以使用一个 4 到 20 的

整数相乘作为参考频率。图 5 描述了时钟操作模式。PLL 乘法器通过 CFR2<7:3>位来控制,

独立于 CFR1<4>位。

7 / 22

�

AD9954 芯片资料-20101207

DAC 输出(DAC Output)

AD9954 内部集成了一个 14 位的 DAC 输出,不像其他大多 DAC,这个输出参照的是

AVDD 而不是 AGND。

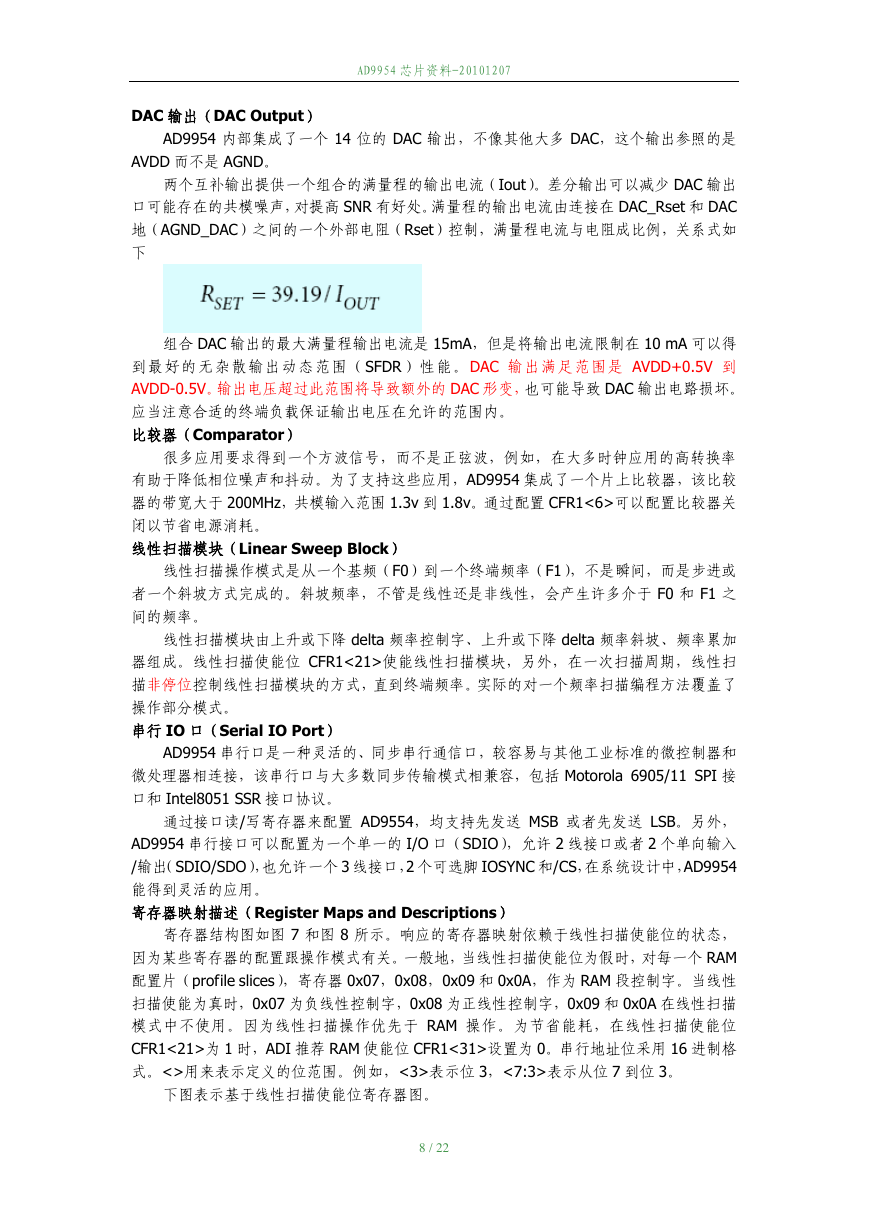

两个互补输出提供一个组合的满量程的输出电流(Iout)。差分输出可以减少 DAC 输出

口可能存在的共模噪声,对提高 SNR 有好处。满量程的输出电流由连接在 DAC_Rset 和 DAC

地(AGND_DAC)之间的一个外部电阻(Rset)控制,满量程电流与电阻成比例,关系式如

下

组合 DAC 输出的最大满量程输出电流是 15mA,但是将输出电流限制在 10 mA 可以得

到最好的无杂散输出动态范围( SFDR)性能。DAC 输出满足范围是 AVDD+0.5V 到

AVDD-0.5V。输出电压超过此范围将导致额外的 DAC 形变,也可能导致 DAC 输出电路损坏。

应当注意合适的终端负载保证输出电压在允许的范围内。

比较器(Comparator)

很多应用要求得到一个方波信号,而不是正弦波,例如,在大多时钟应用的高转换率

有助于降低相位噪声和抖动。为了支持这些应用,AD9954 集成了一个片上比较器,该比较

器的带宽大于 200MHz,共模输入范围 1.3v 到 1.8v。通过配臵 CFR1<6>可以配臵比较器关

闭以节省电源消耗。

线性扫描模块(Linear Sweep Block)

线性扫描操作模式是从一个基频(F0)到一个终端频率(F1),不是瞬间,而是步进或

者一个斜坡方式完成的。斜坡频率,不管是线性还是非线性,会产生许多介于 F0 和 F1 之

间的频率。

线性扫描模块由上升或下降 delta 频率控制字、上升或下降 delta 频率斜坡、频率累加

器组成。线性扫描使能位 CFR1<21>使能线性扫描模块,另外,在一次扫描周期,线性扫

描非停位控制线性扫描模块的方式,直到终端频率。实际的对一个频率扫描编程方法覆盖了

操作部分模式。

串行 IO 口(Serial IO Port)

AD9954 串行口是一种灵活的、同步串行通信口,较容易与其他工业标准的微控制器和

微处理器相连接,该串行口与大多数同步传输模式相兼容,包括 Motorola 6905/11 SPI 接

口和 Intel8051 SSR 接口协议。

通过接口读/写寄存器来配臵 AD9554,均支持先发送 MSB 或者先发送 LSB。另外,

AD9954 串行接口可以配臵为一个单一的 I/O 口(SDIO),允许 2 线接口或者 2 个单向输入

/输出(SDIO/SDO),也允许一个 3 线接口,2 个可选脚 IOSYNC 和/CS,在系统设计中,AD9954

能得到灵活的应用。

寄存器映射描述(Register Maps and Descriptions)

寄存器结构图如图 7 和图 8 所示。响应的寄存器映射依赖于线性扫描使能位的状态,

因为某些寄存器的配臵跟操作模式有关。一般地,当线性扫描使能位为假时,对每一个 RAM

配臵片(profile slices),寄存器 0x07,0x08,0x09 和 0x0A,作为 RAM 段控制字。当线性

扫描使能为真时,0x07 为负线性控制字,0x08 为正线性控制字,0x09 和 0x0A 在线性扫描

模式中不使用。因为线性扫描操作优先于 RAM 操作。为节省能耗,在线性扫描使能位

CFR1<21>为 1 时,ADI 推荐 RAM 使能位 CFR1<31>设臵为 0。串行地址位采用 16 进制格

式。<>用来表示定义的位范围。例如,<3>表示位 3,<7:3>表示从位 7 到位 3。

下图表示基于线性扫描使能位寄存器图。

8 / 22

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc