华 中 科 技 大 学 课 程 设 计 报 告

数字电路与逻辑设计

课程设计报告

报 告 人:

实验指导教师:

报告批阅教师:

计算机科学与技术学院

年 月 日

I

�

华 中 科 技 大 学 课 程 设 计 报 告

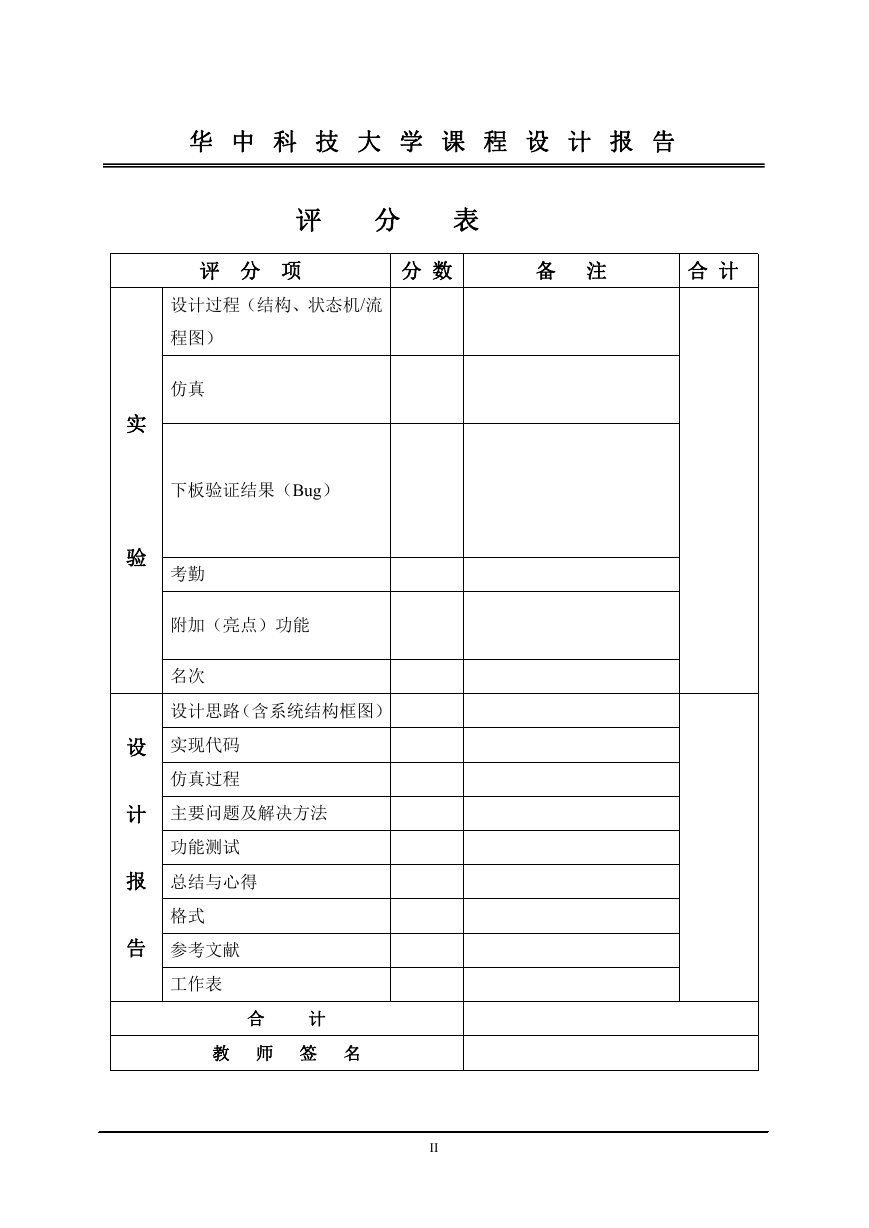

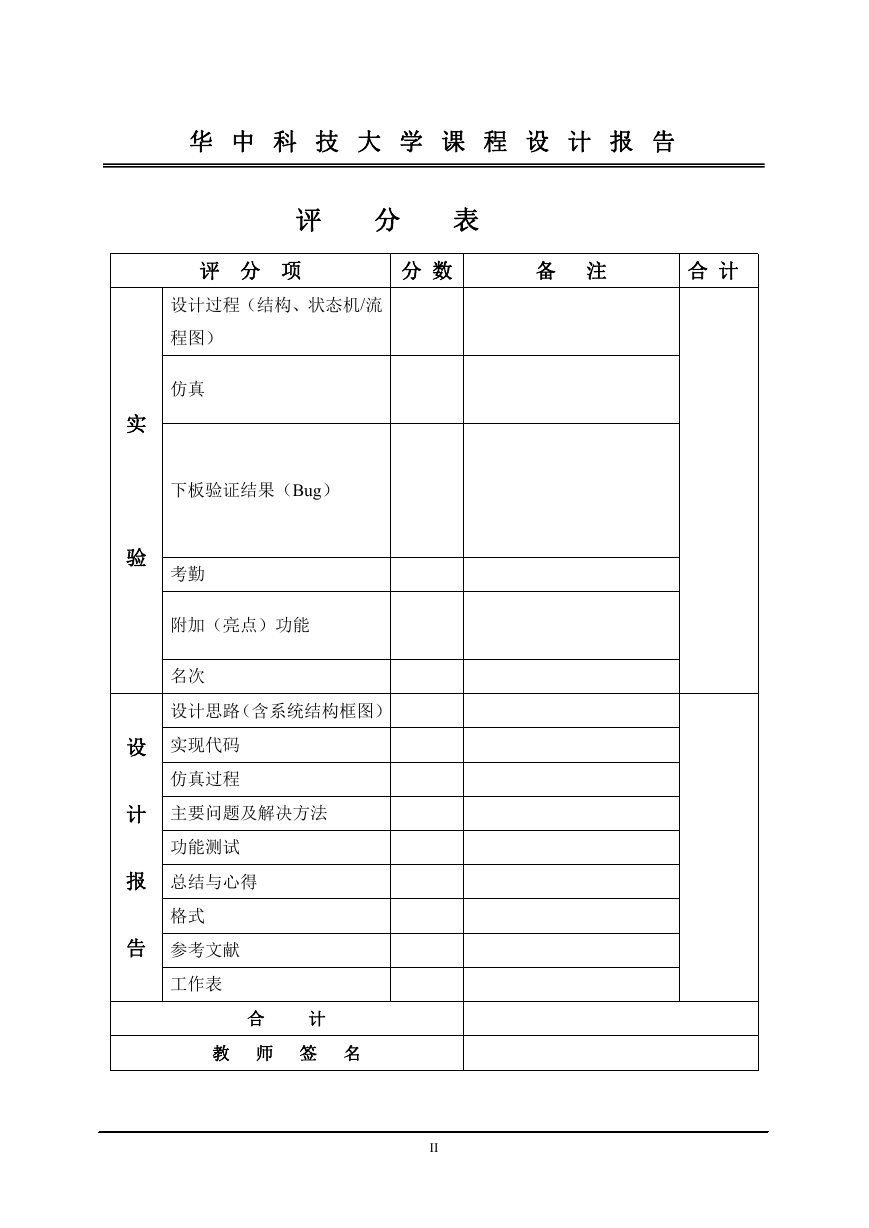

评

分

表

评 分 项

分 数

备 注

合 计

设计过程(结构、状态机/流

程图)

仿真

实

下板验证结果(Bug)

验

考勤

附加(亮点)功能

名次

设计思路(含系统结构框图)

设

实现代码

仿真过程

计

主要问题及解决方法

功能测试

报

总结与心得

格式

告

参考文献

工作表

合

计

教 师 签 名

II

�

华 中 科 技 大 学 课 程 设 计 报 告

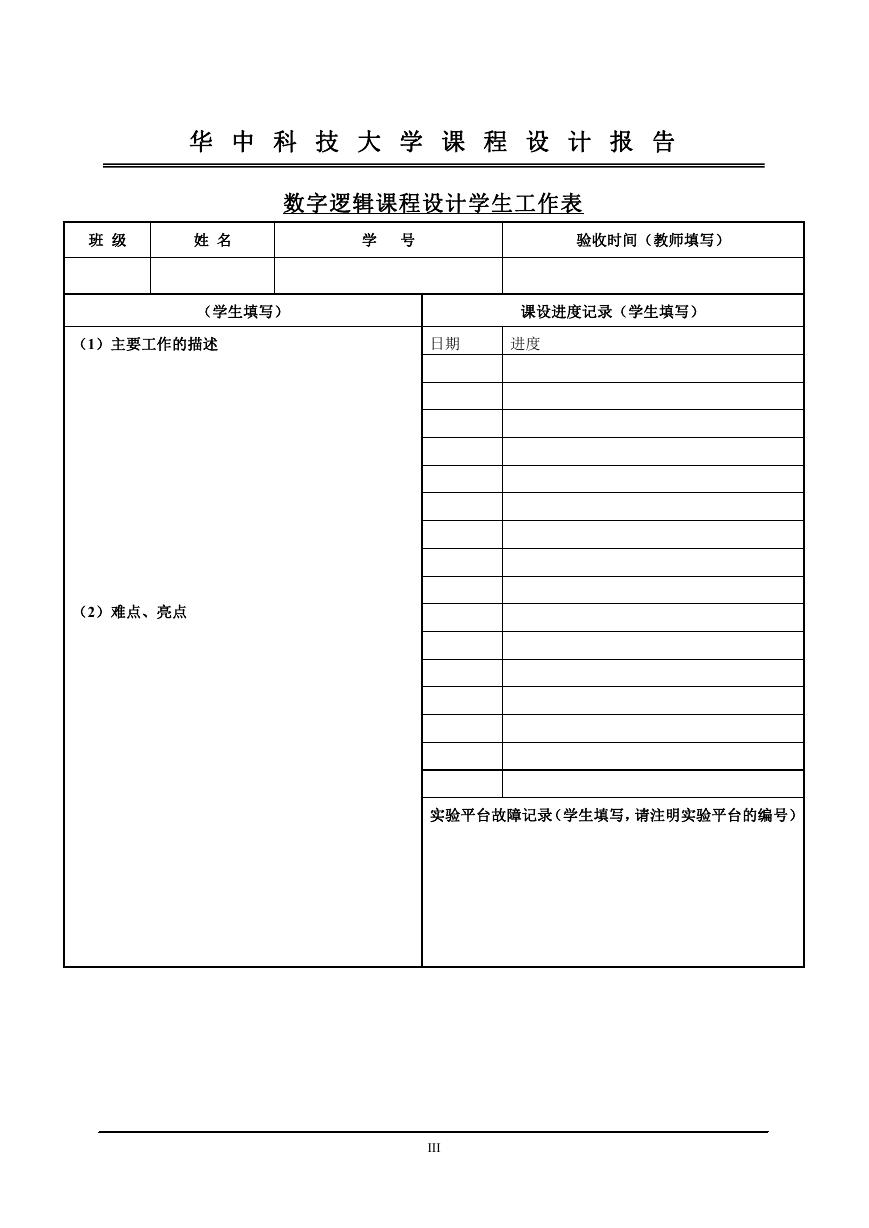

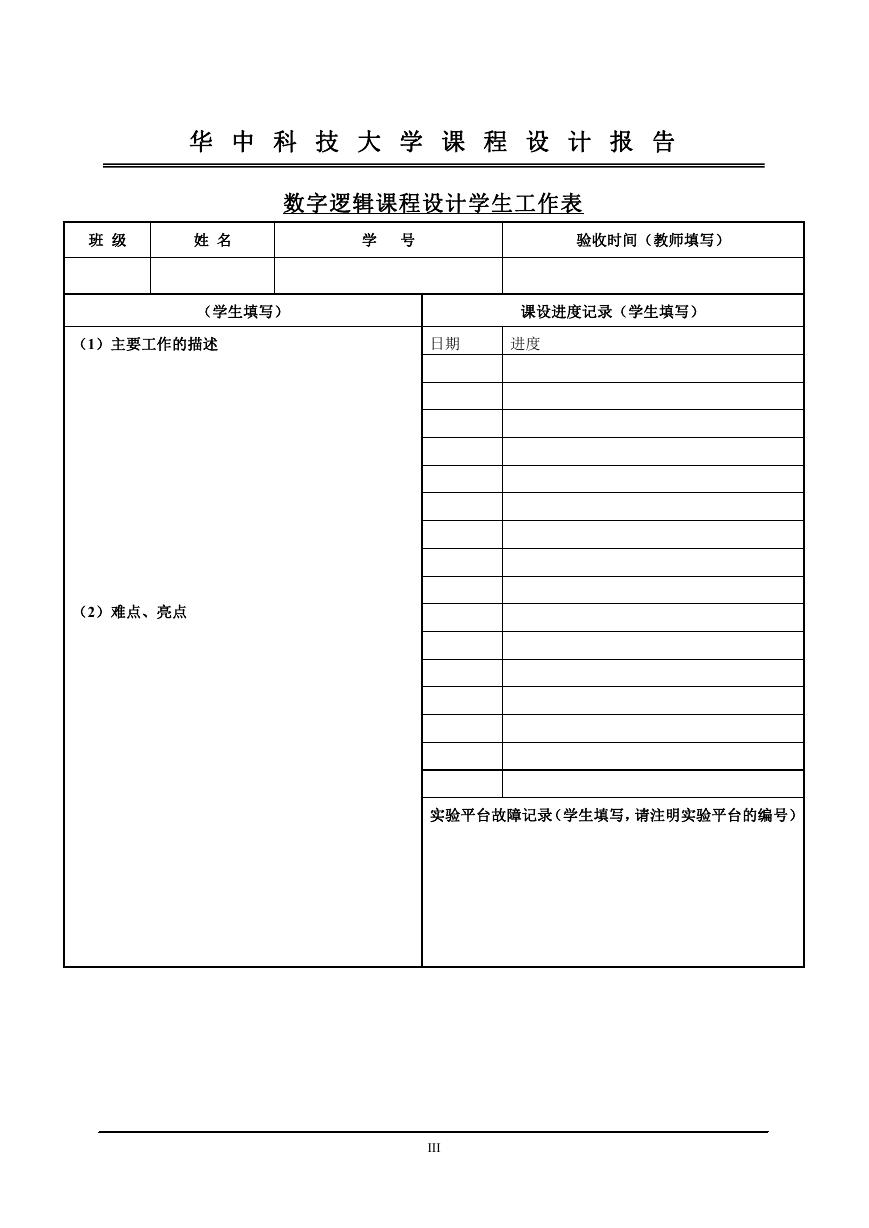

数字逻辑课程设计学生工作表

班 级

姓 名

学 号

验收时间(教师填写)

(学生填写)

课设进度记录(学生填写)

(1)主要工作的描述

日期

进度

(2)难点、亮点

实验平台故障记录(学生填写,请注明实验平台的编号)

III

�

华 中 科 技 大 学 课 程 设 计 报 告

重要说明

1、 时间安排:课内 2 周。

2、 验收准备:

1) 完成本表学生应该填写部分;

2) 每位学生必须都能以独自完成的方式应对任何形式的验收;

3) 完成课程设计报告书(格式参见模板);

4) 将源程序和报告的电子文档交班长。

3、 检查过程:

1) 提交验收准备材料,请求老师验收,之后按验收老师的要求做;

2) 在开发平台上根据验收老师的要求进行演示;

3) 检查过程中独立回答老师提出的相关问题;

4) 验收老师有权根据具体情况调整验收的内容与方式;

5) 验收完成后关闭电源,整理好设备。

4、 评分标准:

1) 在完成控制器基本要求外,有亮点为加分项;

2) 在规定时间内完成控制器基本要求;

3) 在规定时间内完成控制器部分基本要求;

4) 检查时间。

5、 课程设计判定为不合格的一些情形: (本人已阅读此条款 1-5 项:签名

)

1) 请人代做或冒名顶替者;

2) 替人做且不听劝告者;

3) 课程设计报告内容抄袭或雷同者;

4) 课程设计报告内容与实际实验内容不一致者;

5) 课程设计代码抄袭者。

IV

�

华 中 科 技 大 学 课 程 设 计 报 告

目 录

1 综合实验设计概述.............................................................................................................................. 6

1.1 实验目的........................................................................................................................................6

1.2 实验要求........................................................................................................................................6

1.3 实验任务.........................................................................................................................................6

1.4 实验环境........................................................................................................................................7

2 药片装瓶系统设计方案...................................................................................................................... 8

2.1 内容................................................................................................................................................8

2.2 设计思路........................................................................................................................................9

2.2.1 顶层模块设计.................................................................................................................. 10

2.2.2 状态机模块设计.............................................................................................................. 10

2.2.3 显示模块设计.................................................................................................................. 12

2.2.4 2_10 进制转换模块设计.................................................................................................. 12

2.3 代码实现......................................................................................................................................13

2.4 仿真过程......................................................................................................................................18

2.5 主要问题及解决方法................................................................................................................. 23

2.6 功能测试......................................................................................................................................25

3 总结与心得 .........................................................................................................................................29

3.1 课设总结.......................................................................................................................................29

3.2 课设心得.......................................................................................................................................30

4 参考文献.................................................................................................................................................31

附录 1 药片装瓶系统源程序、仿真文件、引脚约束文件...................................................................32

V

�

华 中 科 技 大 学 课 程 设 计 报 告

1.综合实验设计概述

1.1 实验目的

(1)掌握 Vivado 软件的使用方法;

(2)熟悉 FPGA 器件的使用方法;

(3)用 Verilog HDL 进行较复杂逻辑电路的设计和调试;

(4)学习数字系统的设计方法;

(5)通过规范化的实验报告,培养学生良好的文档习惯以及撰写规范文档的能力。

1.2 实验要求

(1)能够全面地应用课程中所学的基本理论和基本方法,完成从设计逻辑电路到设计简单数

字系统的过渡;

(2)能力独立思考、独立查阅资料,独立设计规定的系统;

(3)能够独立地完成实施过程,包括电路设计、调试、排除故障、仿真和下载验证。

1.3 实验任务

本次课程设计每人要完成一个设计任务,具体参见数字逻辑课程综合实验设计题目。

(1)制定出详细设计方案,认真记载毕业设计工作日记;

(2)通过 Verilog HDL 完成规定的设计任务,采取模块化、层次化的设计方法设计电路,然

后进行编译和仿真,认真记录实施过程中遇到的各自故障以及解决方法,保证设计的正确性;

(3)生成 bit 文件,下载到开发板上,通过实际线路进行验证设计的正确性;

(4)撰写设计报告,并对存在的问题进行分析、提出改进意见。

6

�

华 中 科 技 大 学 课 程 设 计 报 告

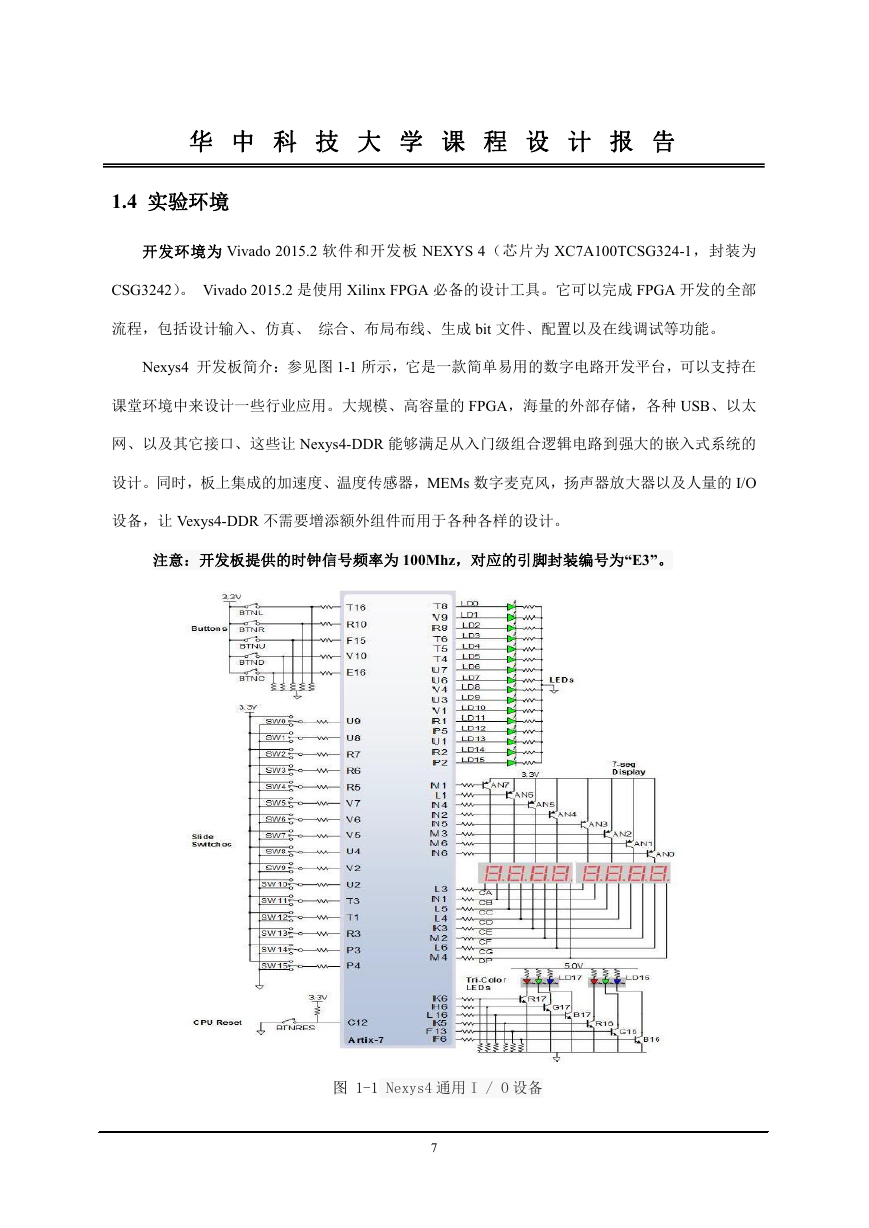

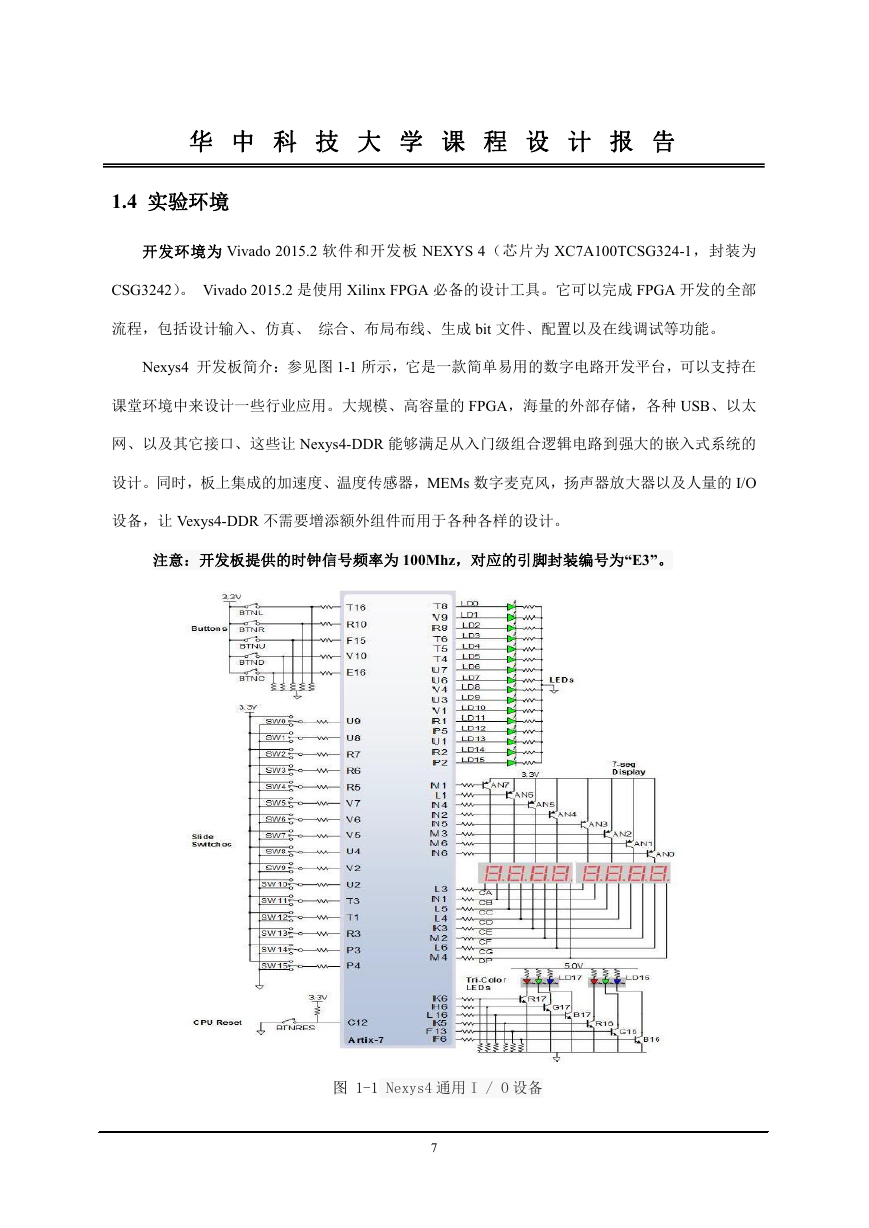

1.4 实验环境

开发环境为 Vivado 2015.2 软件和开发板 NEXYS 4(芯片为 XC7A100TCSG324-1,封装为

CSG3242)。 Vivado 2015.2 是使用 Xilinx FPGA 必备的设计工具。它可以完成 FPGA 开发的全部

流程,包括设计输入、仿真、 综合、布局布线、生成 bit 文件、配置以及在线调试等功能。

Nexys4 开发板简介:参见图 1-1 所示,它是一款简单易用的数字电路开发平台,可以支持在

课堂环境中来设计一些行业应用。大规模、高容量的 FPGA,海量的外部存储,各种 USB、以太

网、以及其它接口、这些让 Nexys4-DDR 能够满足从入门级组合逻辑电路到强大的嵌入式系统的

设计。同时,板上集成的加速度、温度传感器,MEMs 数字麦克风,扬声器放大器以及人量的 I/O

设备,让 Vexys4-DDR 不需要增添额外组件而用于各种各样的设计。

注意:开发板提供的时钟信号频率为 100Mhz,对应的引脚封装编号为“E3”。

图 1-1 Nexys4 通用 I / O 设备

7

�

华 中 科 技 大 学 课 程 设 计 报 告

2.药片装瓶系统设计方案

2.1 内容

(1)设计并利用 Nexys4 开发板实现药片装瓶系统,它具有下述功能:

a.电路清零信号(rst),用按钮实现清零信号,可以产生清零信号,对系统进行清零,同时机

电装置的工作状态置为不工作状态(S_off)。

b.假设输入的药片数量与装瓶数最大为 20,40,开关用于药片数量(number)与装瓶数

(bottle_num)的 BCD 码输入。

c.开始装瓶脉冲(start)用于药片与药瓶数据的输入,并且药片数量或药瓶数量超过最大装瓶

数或最大瓶数时,显示系统出现告警提示。

d.机电装置启动信号脉冲(open),用于启动机电装置表示可以进行滴落药片,移动传送带。

e.机电装置停止信号脉冲(stop),用于停止机电装置表示进入不工作状态。

f.七段数码管显示,能够显示当前的总的计数药片的数量,当前计数的药瓶数量,要装瓶的单

瓶药片数量,输入超过最大值能够出现报警提示。

g.发光二极管的显示即信号(red 与 green)表示机电装置的关闭与运行状态。

h.输出 led 灯显示,信号(led0)与信号(led1)用于表示机电装置的工作状态位于 S_on1,S_on2。

i.输出 led 灯显示,信号(on)与信号(off)用于表示是有机电装置启动脉冲或停止脉冲出现。

j.输出 led 灯显示,信号(finish)用于表示装瓶数量达到规定值。

(2)根据功能描述画出系统结构框图

由功能描述容易确定系统的输入与输出,系统结构框图如图 2-1 所示。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc