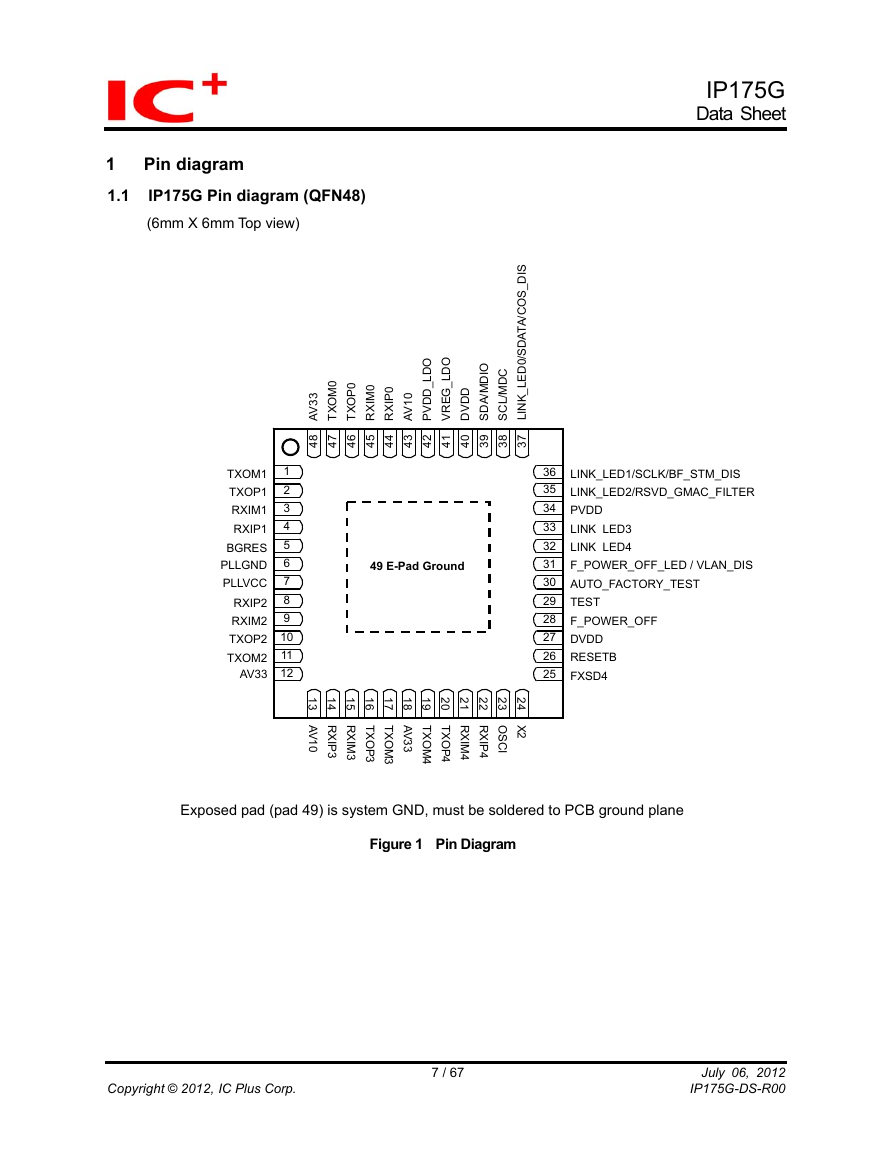

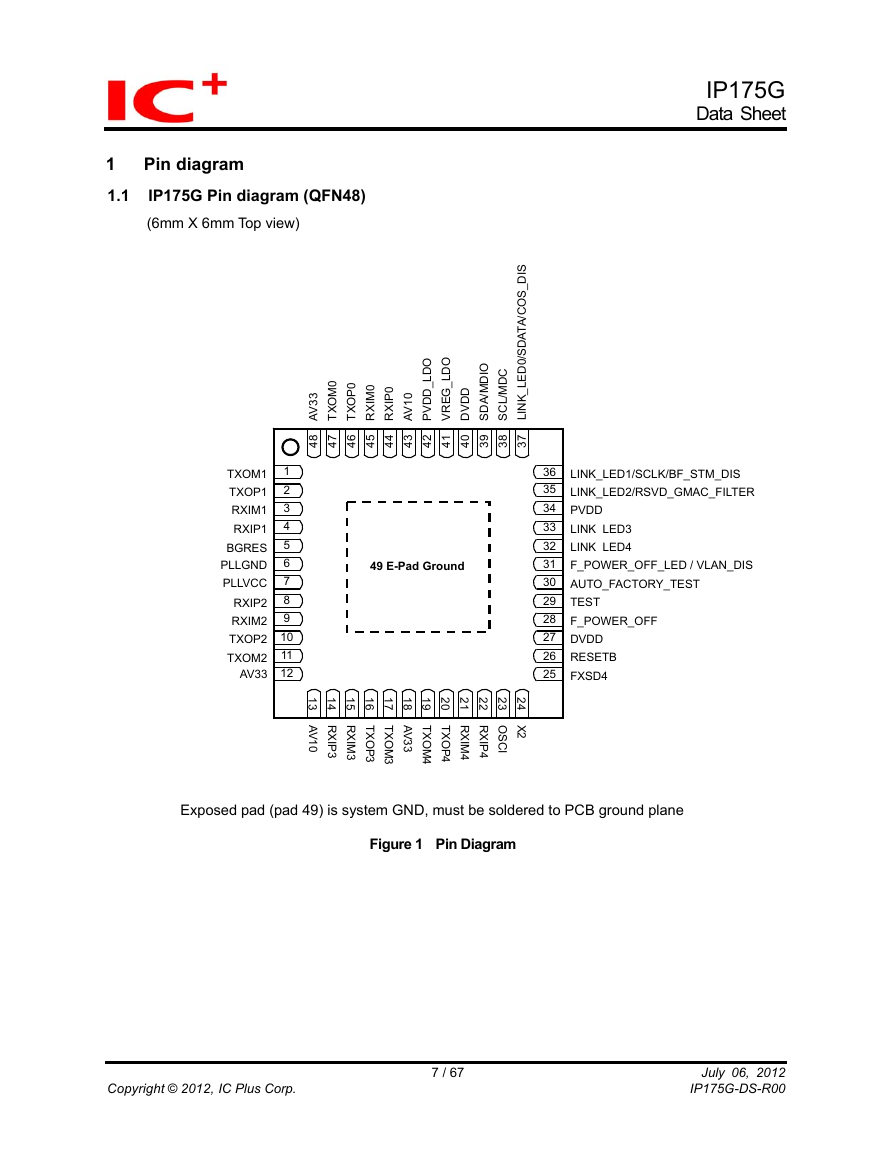

1 Pin diagram

1.1 IP175G Pin diagram (QFN48)

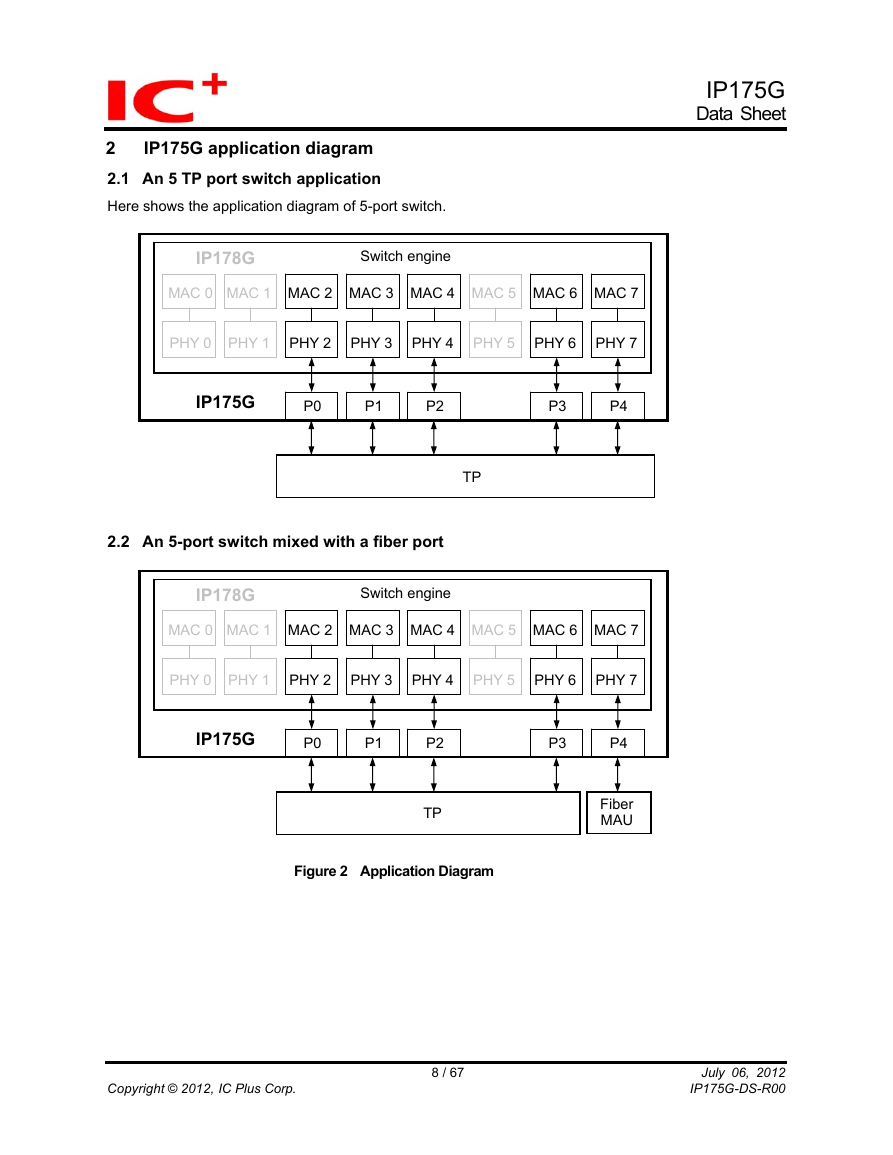

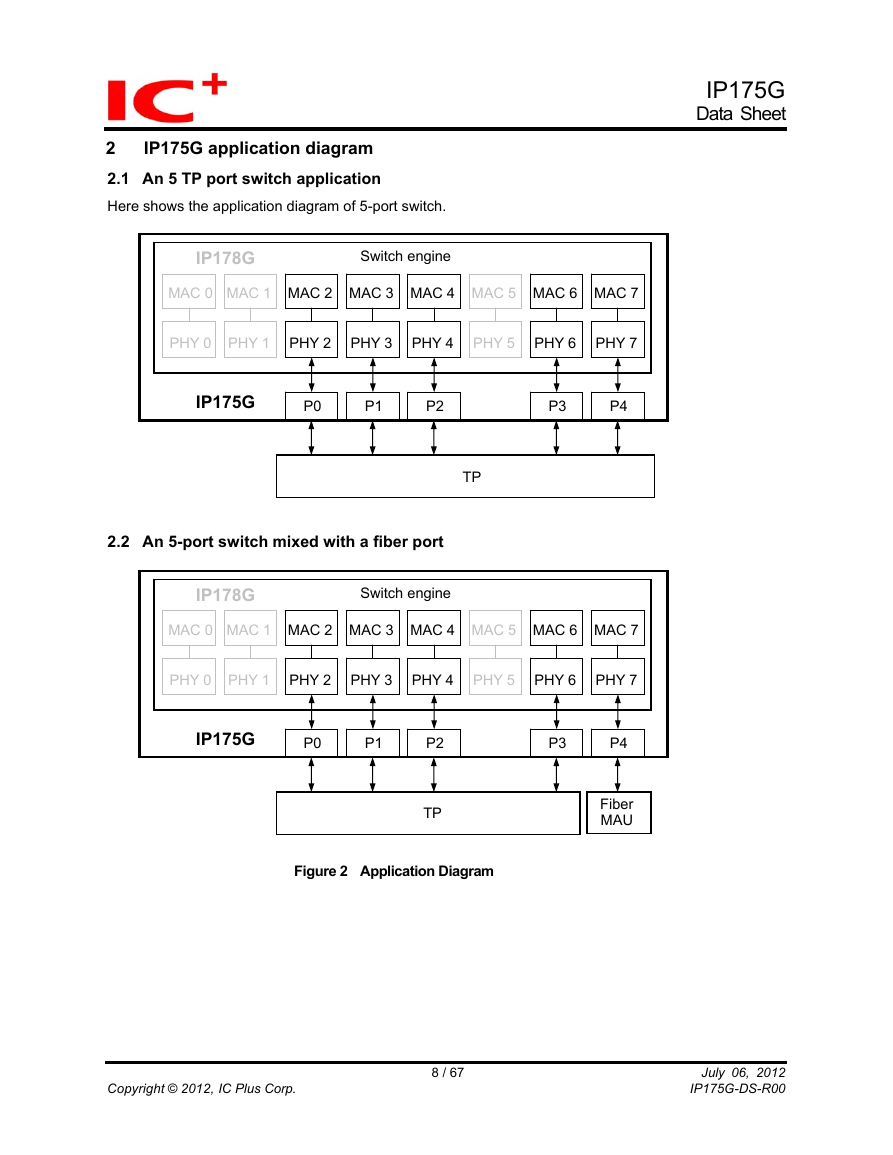

2 IP175G application diagram

2.1 An 5 TP port switch application

2.2 An 5-port switch mixed with a fiber port

3 Pin description

3.1 Analog pins

3.2 MDI (Media Dependent Interface)

3.3 System clock & reset pins

3.4 Boundry scan & test mode

TEST

3.5 EEPROM interface /SMI (Serial Management interface)

3.6 Miscellaneous setting pins

COS_EN

3.7 LED interface

3.8 Power & ground pads

4 Functional Description

4.1 Switch Engine and Queue Management

4.1.1 Switch Engine

4.1.2 Packet Forwarding

4.1.3 Flow control

4.1.4 Backpressure

4.1.5 Broadcast storm protection

4.2 Rserved Group MAC Address

4.3 Green Power

4.3.1 Auto Power Saving Mode

4.3.2 IEEE802.3az EEE (Energy Efficient Ethernet)

4.3.3 WOL+ (Wake On LAN Plus)

4.4 Force Power Off

4.5 Auto Factory Test (AFT) Mode

4.6 Reset

4.7 Serial management interface

4.8 CoS

4.8.1 Port base priority

4.8.2 Frame base priority

4.8.2.1 VLAN tag and TCP/IP TOS

4.8.2.2 IPv4/IPv6 DiffServ

4.8.2.3 TCP/UDP logical port priority

4.9 Port Mirroring

4.10 Link Aggergation

4.11 Buffer Aging

4.12 PAD Driving Calibration

4.13 Fiber port configuration

5 Register descriptions

5.1 Register map

5.1.1 MII register map

6 PHY registers

6.1 MII Register

6.2 MMD Control Register

6.3 MMD Data Register

6.4 LED mode Control Register

6.5 Register Page mode Control Register

6.6 WOL+ Control Register

6.7 Switch control registers (I)

6.8 Test mode control registers

6.9 Port mirroring control registers

6.10 Debug Register

6.11 Fiber duplex setting registers

6.12 Backpressure setting registers

6.13 TCP/UDP port priority registers

6.14 Test mode

6.15 CoS control registers – port 0

6.16 CoS control registers – port 1

6.17 CoS control registers – port 2

6.18 CoS control registers – port 3

6.19 CoS control registers – port 4

6.20 Switch control registers (IV)

6.21 Reserved Group MAC addresses

6.22 Switch control registers (II)

6.23 EEE Timing Parameter

6.24 WOL (Wake on LAN)

6.25 Link Aggregation

6.26 VLAN Group Control Register

6.26.1 VLAN Classification

6.26.2 VLAN Ingress Rule

6.26.3 Default VLAN Information

6.26.4 VLAN TAG Control Register

6.26.5 Port Based VLAN Member Register

6.26.6 Leaky VLAN Control Register

6.27 VLAN Table

6.27.1 VLAN Control Register

6.27.2 VLAN Identifier Register

6.27.3 VLAN Member Register

7 Electrical Characteristics

7.1 Absolute Maximum Rating

7.2 DC Characteristic

7.3 AC Timing

7.3.1 Power On Sequence and Reset Timing

8 Crystal Specifications

8.1.1 EEPROM Timing

8.1.1.1 Data read cycle

8.1.1.2 Command cycle

8.2 Thermal Data

9 Order Information

10 Package Detail

10.1 48 QFN Outline Dimensions

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc