Freescale Semiconductor

Data Sheet: Technical Data

Document Number S9KEA128P80M48SF0

Rev 4, 09/2014

KEA128 Sub-Family Data

Sheet

Supports the following:

S9KEAZ64AMLK(R),

S9KEAZ128AMLK(R),

S9KEAZ64AVLK(R),

S9KEAZ128AVLK(R),

S9KEAZ64ACLK(R),

S9KEAZ128ACLK(R),

S9KEAZ64AMLH(R),

S9KEAZ128AMLH(R),

S9KEAZ64AVLH(R),

S9KEAZ128AVLH(R),

S9KEAZ64ACLH(R) and

S9KEAZ128ACLH(R)

Key features

• Operating characteristics

– Voltage range: 2.7 to 5.5 V

– Flash write voltage range: 2.7 to 5.5 V

– Temperature range (ambient): -40 to 125°C

• Performance

– Up to 48 MHz ARM® Cortex-M0+ core

– Single cycle 32-bit x 32-bit multiplier

– Single cycle I/O access port

• Memories and memory interfaces

– Up to 128 KB flash

– Up to 16 KB RAM

• Clocks

– Oscillator (OSC) - supports 32.768 kHz crystal or 4

MHz to 24 MHz crystal or ceramic resonator; choice

of low power or high gain oscillators

– Internal clock source (ICS) - internal FLL with

internal or external reference, 37.5 kHz pre-trimmed

internal reference for 48 MHz system clock

– Internal 1 kHz low-power oscillator (LPO)

S9KEA128P80M48SF0

• System peripherals

– Power management module (PMC) with three power

modes: Run, Wait, Stop

– Low-voltage detection (LVD) with reset or interrupt,

selectable trip points

– Watchdog with independent clock source (WDOG)

– Programmable cyclic redundancy check module

(CRC)

– Serial wire debug interface (SWD)

– Aliased SRAM bitband region (BIT-BAND)

– Bit manipulation engine (BME)

• Security and integrity modules

– 80-bit unique identification (ID) number per chip

• Human-machine interface

– Up to 71 general-purpose input/output (GPIO)

– Two 32-bit keyboard interrupt modules (KBI)

– External interrupt (IRQ)

• Analog modules

– One up to 16-channel 12-bit SAR ADC, operation in

Stop mode, optional hardware trigger (ADC)

– Two analog comparators containing a 6-bit DAC

and programmable reference input (ACMP)

Freescale reserves the right to change the detail specifications as may be

required to permit improvements in the design of its products.

© 2014 Freescale Semiconductor, Inc.

�

• Timers

– One 6-channel FlexTimer/PWM (FTM)

– Two 2-channel FlexTimer/PWM (FTM)

– One 2-channel periodic interrupt timer (PIT)

– One pulse width timer (PWT)

– One real-time clock (RTC)

• Communication interfaces

– Two SPI modules (SPI)

– Up to three UART modules (UART)

– Two I2C modules (I2C)

– One MSCAN module (MSCAN)

• Package options

– 80-pin LQFP

– 64-pin LQFP

2

Freescale Semiconductor, Inc.

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

Table of Contents

1 Ordering parts.......................................................................................4

4.2.2

FTM module timing....................................................... 16

1.1 Determining valid orderable parts............................................... 4

4.3 Thermal specifications.................................................................17

2 Part identification................................................................................. 4

4.3.1

Thermal characteristics.................................................. 17

2.1 Description...................................................................................4

5 Peripheral operating requirements and behaviors................................ 19

2.2 Format..........................................................................................4

5.1 Core modules............................................................................... 19

2.3 Fields............................................................................................4

5.1.1

SWD electricals .............................................................19

2.4 Example....................................................................................... 5

5.2 External oscillator (OSC) and ICS characteristics.......................20

3 Ratings..................................................................................................5

5.3 NVM specifications..................................................................... 22

3.1 Thermal handling ratings............................................................. 5

5.4 Analog..........................................................................................23

3.2 Moisture handling ratings............................................................ 5

5.4.1 ADC characteristics....................................................... 23

3.3 ESD handling ratings................................................................... 6

5.4.2 Analog comparator (ACMP) electricals.........................25

3.4 Voltage and current operating ratings..........................................6

5.5 Communication interfaces........................................................... 26

4 General................................................................................................. 7

5.5.1

SPI switching specifications.......................................... 26

4.1 Nonswitching electrical specifications........................................ 7

5.5.2 MSCAN......................................................................... 29

4.1.1 DC characteristics.......................................................... 7

6 Dimensions...........................................................................................29

4.1.2

Supply current characteristics........................................ 13

6.1 Obtaining package dimensions.................................................... 29

4.1.3

EMC performance..........................................................15

7 Pinout................................................................................................... 30

4.2 Switching specifications.............................................................. 15

7.1 Signal multiplexing and pin assignments.................................... 30

4.2.1

Control timing................................................................ 15

8 Revision History...................................................................................30

Freescale Semiconductor, Inc.

3

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

Ordering parts

1

Ordering parts

1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part

numbers for this device, go to freescale.com and perform a part number search for the

following device numbers: KEAZ128.

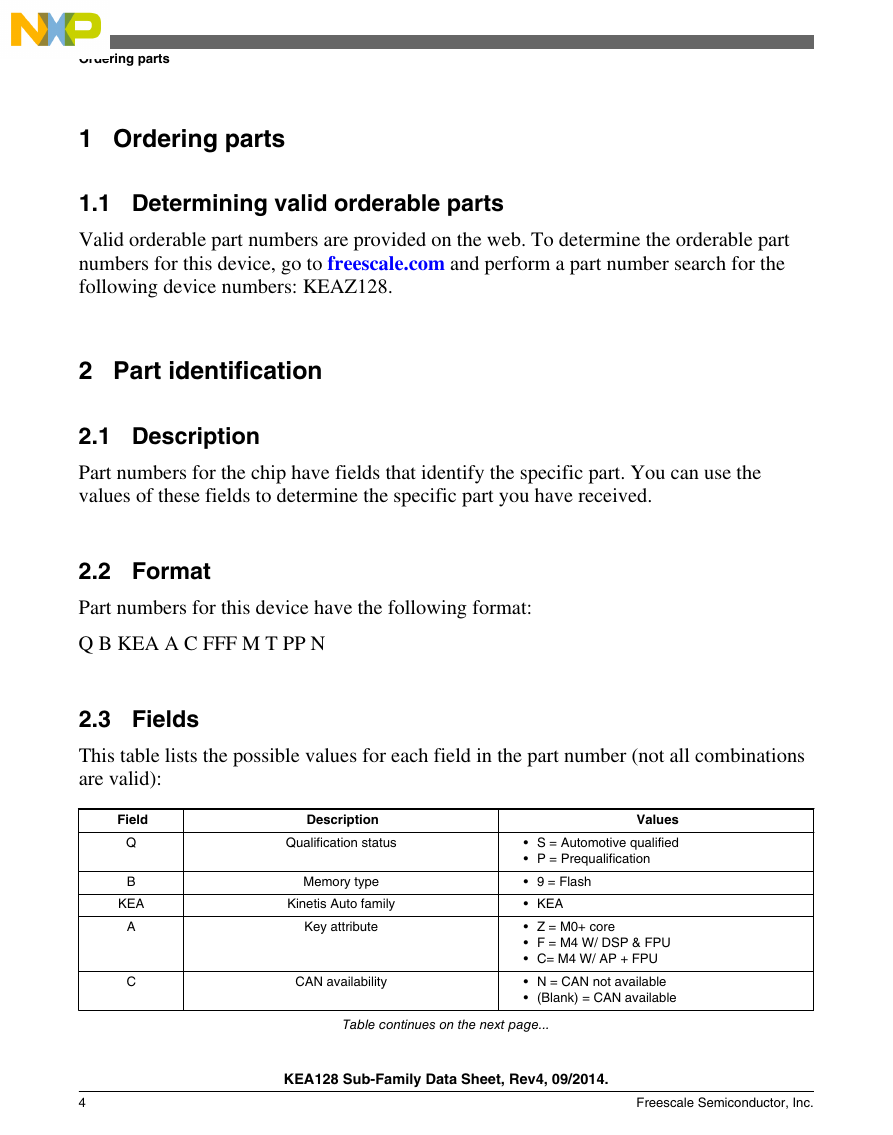

2

Part identification

2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the

values of these fields to determine the specific part you have received.

2.2 Format

Part numbers for this device have the following format:

Q B KEA A C FFF M T PP N

2.3 Fields

This table lists the possible values for each field in the part number (not all combinations

are valid):

Field

Q

B

KEA

A

C

Description

Qualification status

Memory type

Kinetis Auto family

Key attribute

CAN availability

Values

• S = Automotive qualified

• P = Prequalification

• 9 = Flash

• KEA

• Z = M0+ core

• F = M4 W/ DSP & FPU

• C= M4 W/ AP + FPU

• N = CAN not available

• (Blank) = CAN available

Table continues on the next page...

4

Freescale Semiconductor, Inc.

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

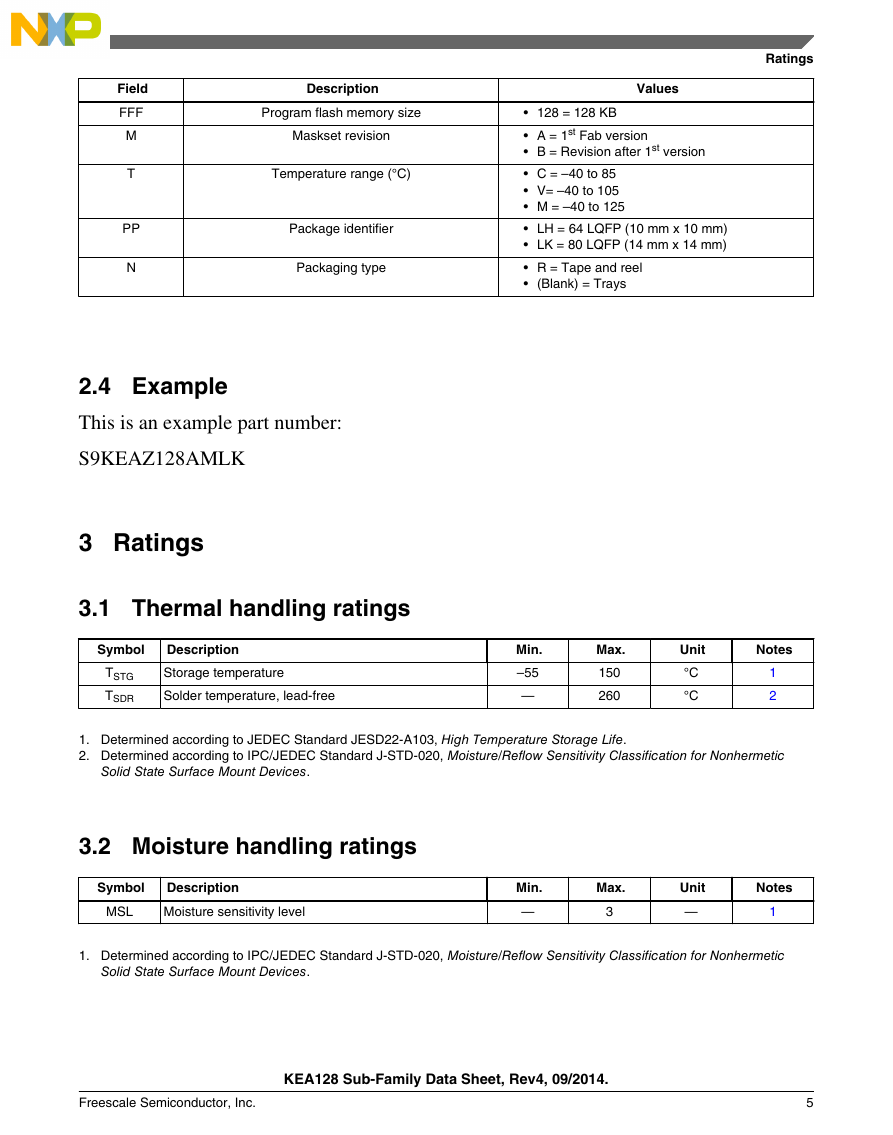

Field

FFF

M

T

PP

N

Description

Program flash memory size

Maskset revision

Temperature range (°C)

Package identifier

Packaging type

Ratings

Values

• 128 = 128 KB

• A = 1st Fab version

• B = Revision after 1st version

• C = –40 to 85

• V= –40 to 105

• M = –40 to 125

• LH = 64 LQFP (10 mm x 10 mm)

• LK = 80 LQFP (14 mm x 14 mm)

• R = Tape and reel

• (Blank) = Trays

2.4 Example

This is an example part number:

S9KEAZ128AMLK

3

Ratings

3.1 Thermal handling ratings

Symbol

TSTG

TSDR

Description

Storage temperature

Solder temperature, lead-free

Min.

–55

—

Max.

150

260

Unit

°C

°C

Notes

1

2

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

3.2 Moisture handling ratings

Symbol

Description

MSL

Moisture sensitivity level

Min.

—

Max.

3

Unit

—

Notes

1

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

Freescale Semiconductor, Inc.

5

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

Ratings

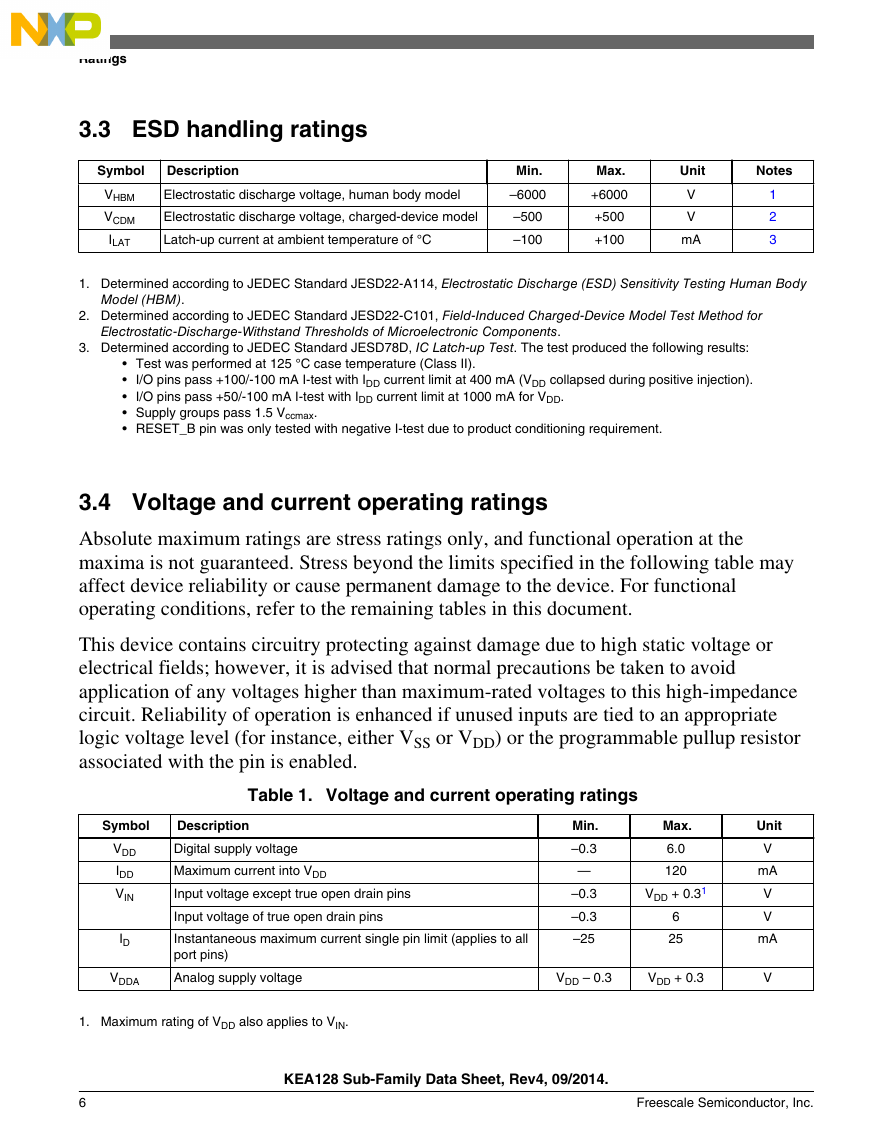

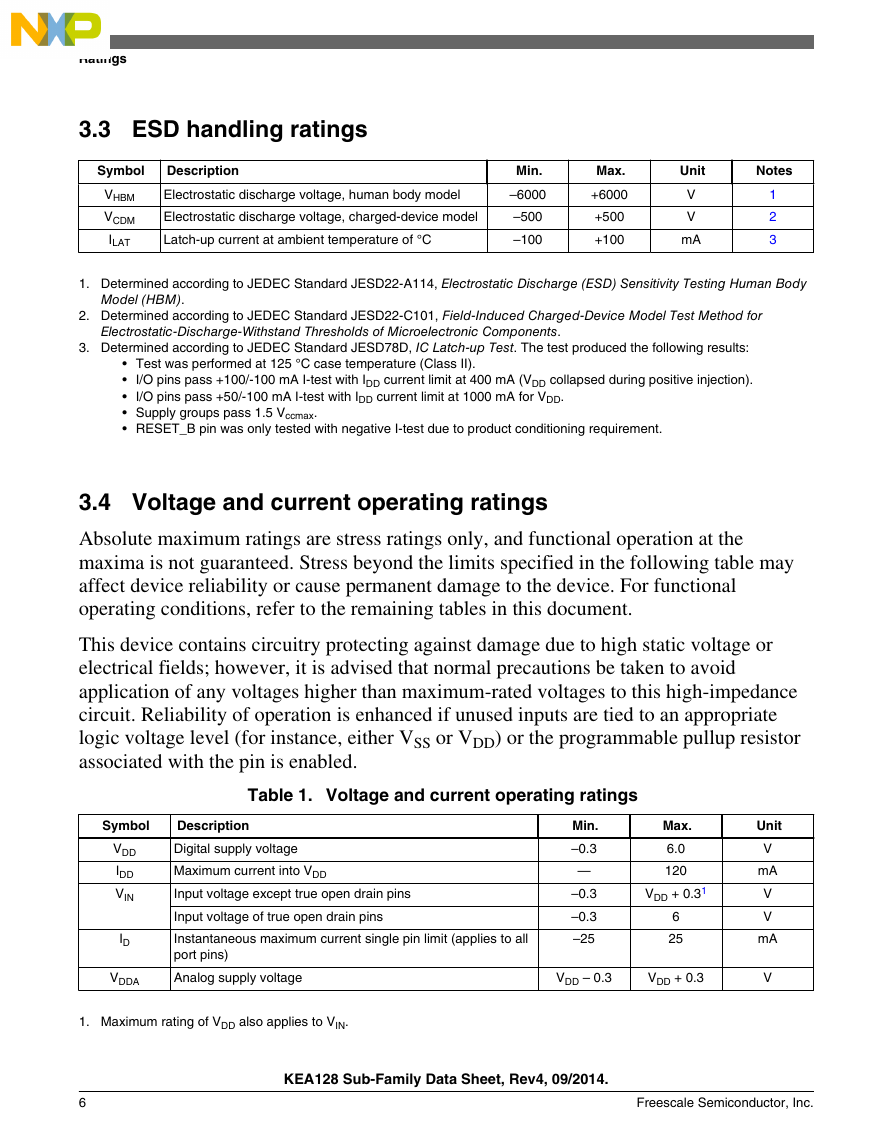

3.3 ESD handling ratings

Symbol

VHBM

VCDM

ILAT

Description

Electrostatic discharge voltage, human body model

Electrostatic discharge voltage, charged-device model

Latch-up current at ambient temperature of °C

Min.

–6000

–500

–100

Max.

+6000

+500

+100

Unit

V

V

mA

Notes

1

2

3

1. Determined according to JEDEC Standard JESD22-A114, Electrostatic Discharge (ESD) Sensitivity Testing Human Body

Model (HBM).

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for

Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78D, IC Latch-up Test. The test produced the following results:

• Test was performed at 125 °C case temperature (Class II).

• I/O pins pass +100/-100 mA I-test with IDD current limit at 400 mA (VDD collapsed during positive injection).

• I/O pins pass +50/-100 mA I-test with IDD current limit at 1000 mA for VDD.

• Supply groups pass 1.5 Vccmax.

• RESET_B pin was only tested with negative I-test due to product conditioning requirement.

3.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the

maxima is not guaranteed. Stress beyond the limits specified in the following table may

affect device reliability or cause permanent damage to the device. For functional

operating conditions, refer to the remaining tables in this document.

This device contains circuitry protecting against damage due to high static voltage or

electrical fields; however, it is advised that normal precautions be taken to avoid

application of any voltages higher than maximum-rated voltages to this high-impedance

circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate

logic voltage level (for instance, either VSS or VDD) or the programmable pullup resistor

associated with the pin is enabled.

Table 1. Voltage and current operating ratings

Symbol

Description

VDD

IDD

VIN

ID

VDDA

Digital supply voltage

Maximum current into VDD

Input voltage except true open drain pins

Input voltage of true open drain pins

Instantaneous maximum current single pin limit (applies to all

port pins)

Analog supply voltage

Min.

–0.3

—

–0.3

–0.3

–25

Max.

6.0

120

VDD + 0.31

6

25

VDD – 0.3

VDD + 0.3

Unit

V

mA

V

V

mA

V

1. Maximum rating of VDD also applies to VIN.

6

Freescale Semiconductor, Inc.

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

General

4

General

4.1

Nonswitching electrical specifications

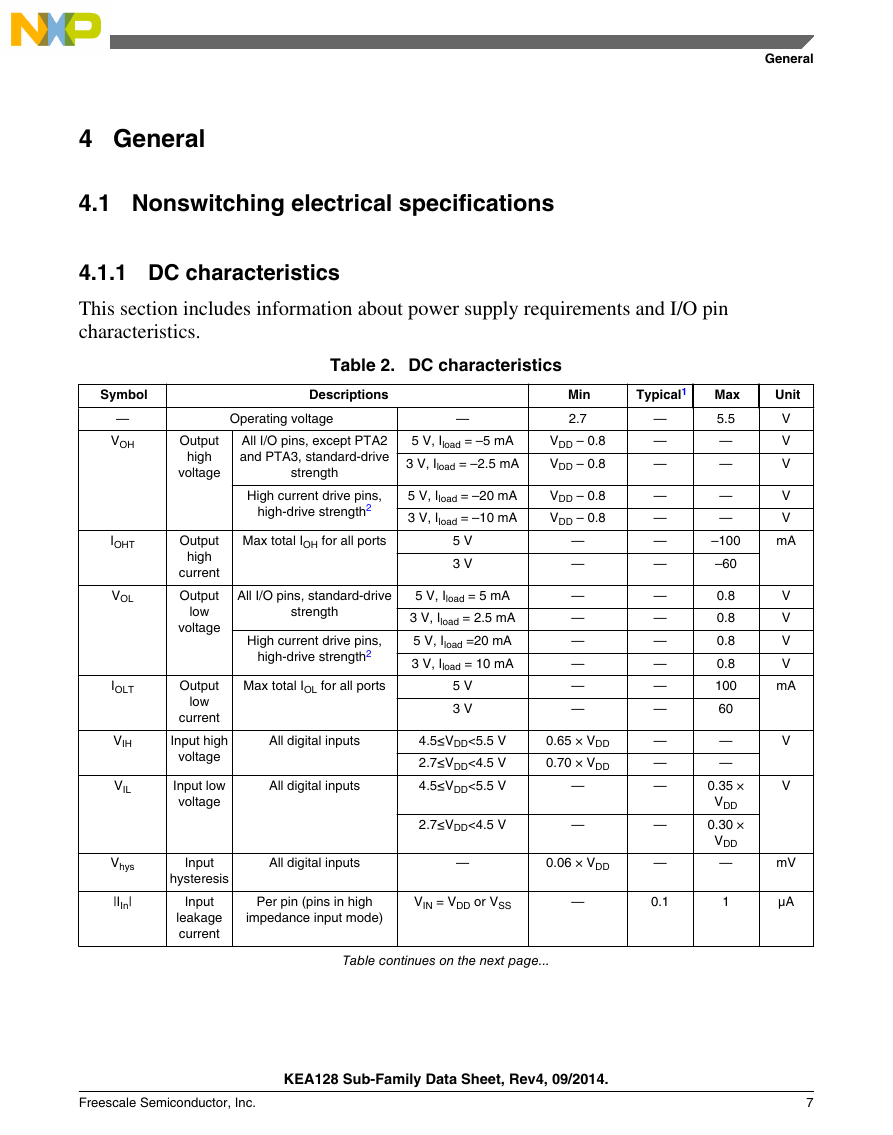

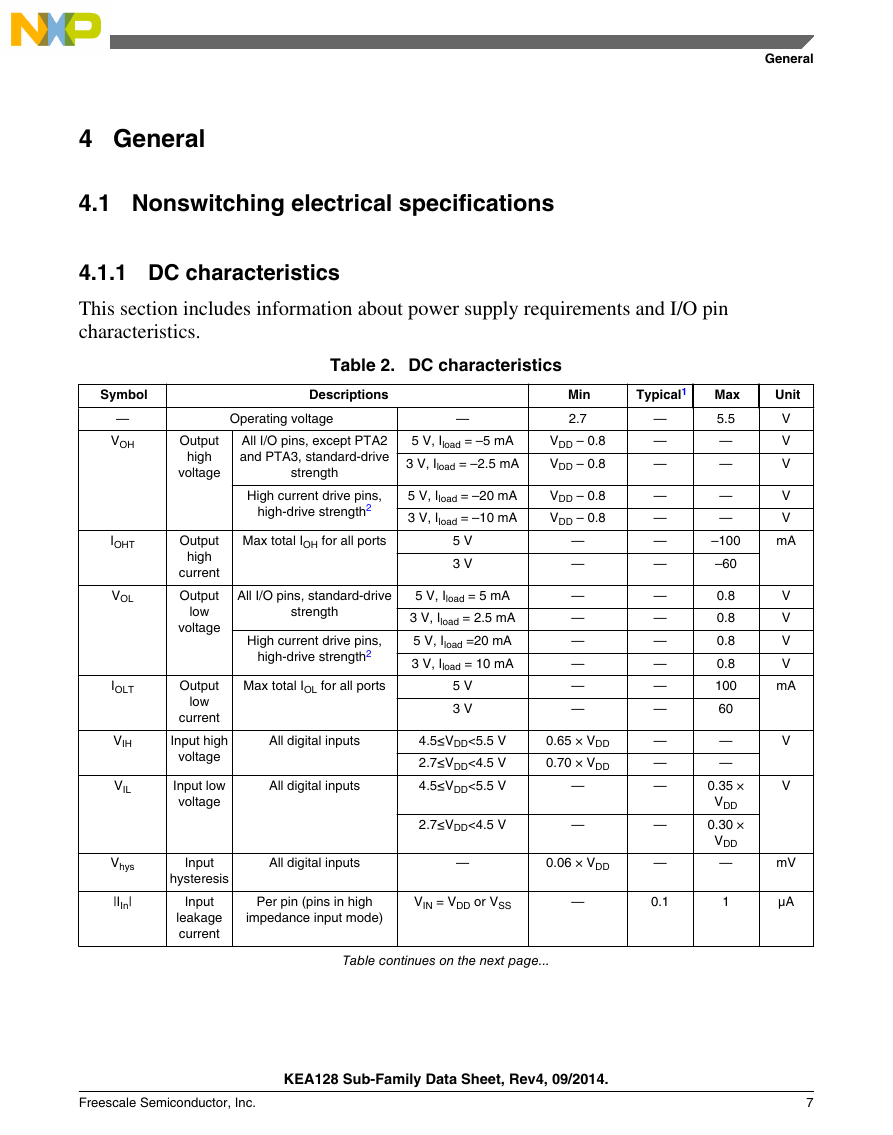

4.1.1 DC characteristics

This section includes information about power supply requirements and I/O pin

characteristics.

Table 2. DC characteristics

Symbol

—

VOH

Descriptions

Operating voltage

—

Output

high

voltage

All I/O pins, except PTA2

and PTA3, standard-drive

strength

5 V, Iload = –5 mA

3 V, Iload = –2.5 mA

High current drive pins,

high-drive strength2

5 V, Iload = –20 mA

3 V, Iload = –10 mA

Min

2.7

VDD – 0.8

VDD – 0.8

VDD – 0.8

VDD – 0.8

Max total IOH for all ports

All I/O pins, standard-drive

strength

High current drive pins,

high-drive strength2

Max total IOL for all ports

All digital inputs

All digital inputs

5 V

3 V

5 V, Iload = 5 mA

3 V, Iload = 2.5 mA

5 V, Iload =20 mA

3 V, Iload = 10 mA

5 V

3 V

4.5≤VDD<5.5 V

2.7≤VDD<4.5 V

4.5≤VDD<5.5 V

2.7≤VDD<4.5 V

—

—

—

—

—

—

—

—

0.65 × VDD

0.70 × VDD

—

—

All digital inputs

—

0.06 × VDD

IOHT

VOL

IOLT

VIH

VIL

Vhys

|IIn|

Output

high

current

Output

low

voltage

Output

low

current

Input high

voltage

Input low

voltage

Input

hysteresis

Input

leakage

current

Typical1

Max

Unit

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

5.5

—

—

—

—

–100

–60

0.8

0.8

0.8

0.8

100

60

—

—

0.35 ×

VDD

0.30 ×

VDD

—

V

V

V

V

V

mA

V

V

V

V

mA

V

V

mV

µA

Per pin (pins in high

impedance input mode)

VIN = VDD or VSS

—

0.1

1

Table continues on the next page...

Freescale Semiconductor, Inc.

7

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

Nonswitching electrical specifications

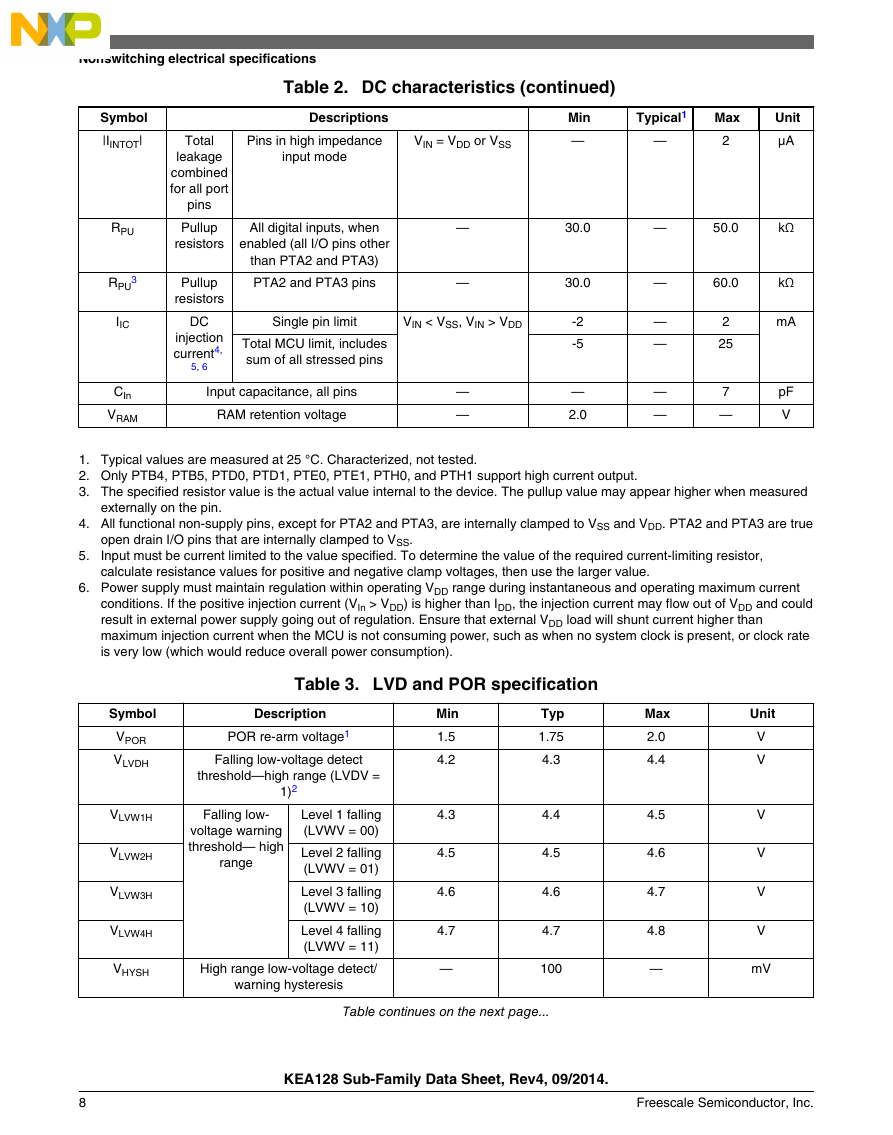

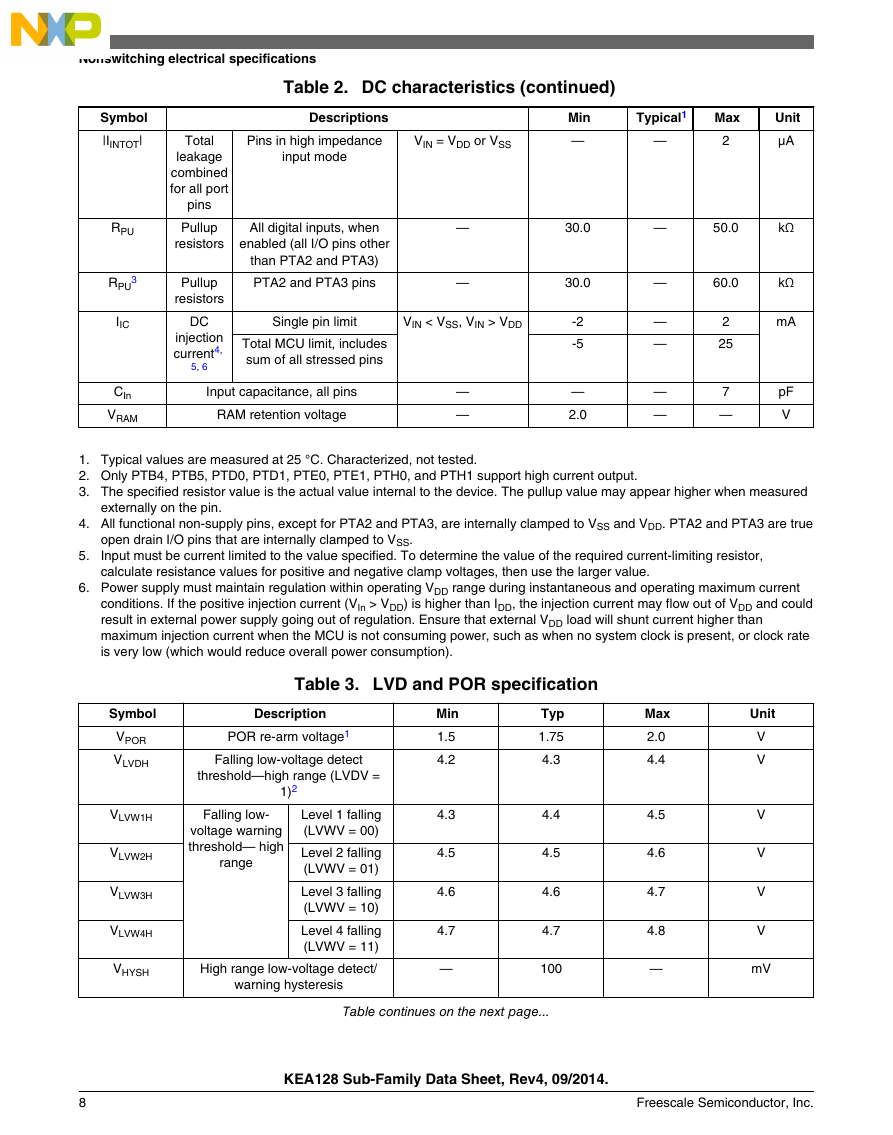

Table 2. DC characteristics (continued)

Symbol

|IINTOT|

Total

leakage

combined

for all port

pins

Descriptions

Pins in high impedance

input mode

VIN = VDD or VSS

RPU

3

RPU

IIC

CIn

VRAM

Pullup

resistors

All digital inputs, when

enabled (all I/O pins other

than PTA2 and PTA3)

PTA2 and PTA3 pins

—

—

Pullup

resistors

DC

injection

current4,

5, 6

Single pin limit

VIN < VSS, VIN > VDD

Total MCU limit, includes

sum of all stressed pins

Input capacitance, all pins

RAM retention voltage

—

—

Min

—

30.0

30.0

-2

-5

—

2.0

Typical1

—

—

—

—

—

—

—

Max

2

Unit

µA

50.0

kΩ

60.0

2

25

7

—

kΩ

mA

pF

V

1. Typical values are measured at 25 °C. Characterized, not tested.

2. Only PTB4, PTB5, PTD0, PTD1, PTE0, PTE1, PTH0, and PTH1 support high current output.

3. The specified resistor value is the actual value internal to the device. The pullup value may appear higher when measured

externally on the pin.

4. All functional non-supply pins, except for PTA2 and PTA3, are internally clamped to VSS and VDD. PTA2 and PTA3 are true

5.

open drain I/O pins that are internally clamped to VSS.

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor,

calculate resistance values for positive and negative clamp voltages, then use the larger value.

6. Power supply must maintain regulation within operating VDD range during instantaneous and operating maximum current

conditions. If the positive injection current (VIn > VDD) is higher than IDD, the injection current may flow out of VDD and could

result in external power supply going out of regulation. Ensure that external VDD load will shunt current higher than

maximum injection current when the MCU is not consuming power, such as when no system clock is present, or clock rate

is very low (which would reduce overall power consumption).

Table 3. LVD and POR specification

Symbol

VPOR

VLVDH

VLVW1H

VLVW2H

VLVW3H

VLVW4H

VHYSH

Description

POR re-arm voltage1

Falling low-voltage detect

threshold—high range (LVDV =

1)2

range

voltage warning

threshold— high

Falling low-

Level 1 falling

(LVWV = 00)

Level 2 falling

(LVWV = 01)

Level 3 falling

(LVWV = 10)

Level 4 falling

(LVWV = 11)

High range low-voltage detect/

Min

1.5

4.2

4.3

4.5

4.6

4.7

—

Typ

1.75

4.3

4.4

4.5

4.6

4.7

100

Max

2.0

4.4

4.5

4.6

4.7

4.8

—

Unit

V

V

V

V

V

V

mV

warning hysteresis

Table continues on the next page...

8

Freescale Semiconductor, Inc.

KEA128 Sub-Family Data Sheet, Rev4, 09/2014.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc