Developer Manual

宾 n

SiRFatlasIV

Developer Manual

0.1 Release (Preliminary)

August 2008

Document Number: CSM-00472

Revision A

SiRF Proprietary and Confidential

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

Table of Contents

Introduction ................................................................................................................... 1

Block Diagram....................................................................................................................................3

RISC Subsystem............................................................................................................ 4

Overview ............................................................................................................................................4

ARM1136JF .......................................................................................................................................4

RISC Interface....................................................................................................................................5

Feature List .............................................................................................................................5

Functional Descriptions...........................................................................................................5

Register Definitions .................................................................................................................9

DSP Subsystem........................................................................................................... 14

DSP Core .........................................................................................................................................14

Overview ...............................................................................................................................14

Feature List ...........................................................................................................................14

Functional Descriptions.........................................................................................................14

Register Definition.................................................................................................................14

GPS Baseband.................................................................................................................................14

Overview ...............................................................................................................................14

Feature List ...........................................................................................................................15

Functional Descriptions.........................................................................................................15

Register Definition.................................................................................................................15

Programming Guide ..............................................................................................................15

Memory Subsystem .................................................................................................... 16

System Arbiter..................................................................................................................................16

Overview ...............................................................................................................................16

Feature List ...........................................................................................................................16

Register Definitions ...............................................................................................................17

Memory Controller............................................................................................................................17

Overview ...............................................................................................................................17

Feature List ...........................................................................................................................17

Pin Descriptions ....................................................................................................................18

Register Definitions ...............................................................................................................18

System Control Modules ............................................................................................ 35

Mode Configuration Pins..................................................................................................................35

Clock PLL.........................................................................................................................................36

Overview ...............................................................................................................................36

Feature List ...........................................................................................................................36

Pin Description ......................................................................................................................36

Functional Descriptions.........................................................................................................37

Register Definitions ...............................................................................................................40

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

1

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

Power Management .........................................................................................................................47

Overview ...............................................................................................................................47

Feature List ...........................................................................................................................47

Pin Description ......................................................................................................................48

Functional Descriptions.........................................................................................................48

Register Definitions ...............................................................................................................48

RSC (Resource Sharing Control Module)........................................................................................61

Overview ...............................................................................................................................61

Feature List ...........................................................................................................................61

Register Definitions ...............................................................................................................61

Programming Guide ..............................................................................................................63

Reset Controller ...............................................................................................................................65

Overview ...............................................................................................................................65

Pin Descriptions ....................................................................................................................66

Functional Descriptions.........................................................................................................66

Register Definitions ...............................................................................................................68

Interrupt Controller ...........................................................................................................................72

Overview ...............................................................................................................................72

Feature List ...........................................................................................................................72

Functional Descriptions.........................................................................................................73

Register Definitions ...............................................................................................................74

OS Timer..........................................................................................................................................85

Overview ...............................................................................................................................85

Feature List ...........................................................................................................................85

Register Definitions ...............................................................................................................85

RTC… ..............................................................................................................................................89

Overview ...............................................................................................................................89

Feature List ...........................................................................................................................90

Pin Description ......................................................................................................................90

Functional Descriptions.........................................................................................................90

Register Definitions ...............................................................................................................92

RTC I/O Bridge.................................................................................................................................97

Overview ...............................................................................................................................97

Feature List ...........................................................................................................................97

Functional Descriptions.........................................................................................................97

Register Definitions ...............................................................................................................99

GPIO….............................................................................................................................................99

Overview ...............................................................................................................................99

Feature List .........................................................................................................................100

Pin Description ....................................................................................................................100

Functional Descriptions.......................................................................................................105

Register Definitions .............................................................................................................105

eFuse.. ...........................................................................................................................................115

Feature List .........................................................................................................................115

Pin Descriptions ..................................................................................................................115

Functional Descriptions.......................................................................................................116

Register Definitions .............................................................................................................120

Touch Screen Controller ................................................................................................................121

Overview .............................................................................................................................121

Feature List .........................................................................................................................121

Pin Description ....................................................................................................................121

Functional Descriptions.......................................................................................................122

Register Definitions .............................................................................................................137

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

2

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

Graphics and Multimedia Subsystem...................................................................... 145

LCD Controller................................................................................................................................145

Overview .............................................................................................................................145

Feature List .........................................................................................................................145

Pin Description ....................................................................................................................146

Functional Descriptions.......................................................................................................147

Register Definitions .............................................................................................................157

Video Post Processor.....................................................................................................................187

Feature List .........................................................................................................................187

Functional Descriptions.......................................................................................................190

Register Definitions .............................................................................................................194

Video Input Port .............................................................................................................................219

Overview .............................................................................................................................219

Feature List .........................................................................................................................219

Pin Description ....................................................................................................................220

Functional Descriptions.......................................................................................................221

Register Definitions .............................................................................................................230

PCI_COPY Data Engine ................................................................................................................240

Overview .............................................................................................................................240

Feature List .........................................................................................................................240

Register Definition...............................................................................................................241

Peripheral Control Modules ..................................................................................... 246

PCI Bridge (SYS2PCI) ...................................................................................................................246

Overview .............................................................................................................................246

Feature List .........................................................................................................................246

Functional Descriptions.......................................................................................................247

Register Definitions .............................................................................................................248

PCI Arbiter......................................................................................................................................254

Overview .............................................................................................................................254

Function Descriptions..........................................................................................................255

USB1 Controller .............................................................................................................................256

Overview .............................................................................................................................256

Pin Descriptions ..................................................................................................................256

ROM Interface................................................................................................................................256

Overview .............................................................................................................................256

Feature List .........................................................................................................................256

Pin Descriptions ..................................................................................................................257

Functional Descriptions.......................................................................................................257

Register Definition...............................................................................................................260

NAND Flash Controller...................................................................................................................262

Overview .............................................................................................................................262

Feature List .........................................................................................................................262

Pin Description ....................................................................................................................263

Functional Descriptions.......................................................................................................264

Register Definitions .............................................................................................................269

SD/MMC/MMC+.............................................................................................................................289

Overview .............................................................................................................................289

Feature List .........................................................................................................................289

Pin Description ....................................................................................................................289

I/O Bridge .......................................................................................................................................292

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

3

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

Overview .............................................................................................................................292

Register Definitions .............................................................................................................293

DMA Controller...............................................................................................................................294

Overview .............................................................................................................................294

Feature List .........................................................................................................................294

Functional Descriptions.......................................................................................................296

Register Definitions .............................................................................................................300

USP Controller ...............................................................................................................................307

Overview .............................................................................................................................307

Feature List .........................................................................................................................308

Pin Descriptions ..................................................................................................................308

Functional Descriptions.......................................................................................................310

Register Definitions .............................................................................................................313

Audio Codec Interface....................................................................................................................332

Overview .............................................................................................................................332

Feature List .........................................................................................................................333

Pin Descriptions ..................................................................................................................333

Functional Descriptions.......................................................................................................334

Register Definitions .............................................................................................................342

UART Controller.............................................................................................................................360

Overview .............................................................................................................................360

Feature List .........................................................................................................................360

Pin Descriptions ..................................................................................................................361

Functional Descriptions.......................................................................................................361

Register Definition...............................................................................................................362

SPI Controller.................................................................................................................................377

Overview .............................................................................................................................377

Feature List .........................................................................................................................378

Pin Descriptions ..................................................................................................................378

Functional Descriptions.......................................................................................................378

Register Definition...............................................................................................................382

PWM…...........................................................................................................................................393

Overview .............................................................................................................................393

Feature List .........................................................................................................................393

Pin Descriptions ..................................................................................................................394

Register Definitions .............................................................................................................394

I2C....... ...........................................................................................................................................399

Overview .............................................................................................................................399

Feature List .........................................................................................................................400

Pin Description ....................................................................................................................400

I2C Bus Descriptions ...........................................................................................................400

Register Definitions .............................................................................................................402

Package and Pin Specification ................................................................................ 408

Mechanical Drawing of Package....................................................................................................408

Pin Sequence and Ball Assignment...............................................................................................412

Pad Type Description.....................................................................................................................434

Power Pins Description ..................................................................................................................435

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

4

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

Electrical and Timing Characteristics ..................................................................... 436

Absolute Maximum Ratings ...........................................................................................................436

Recommended Operating Conditions............................................................................................437

Power-On and Power-Off Sequences............................................................................................438

Deep Sleep and Wakeup Sequences ............................................................................................440

Sleep and Wakeup Sequences......................................................................................................441

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

5

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

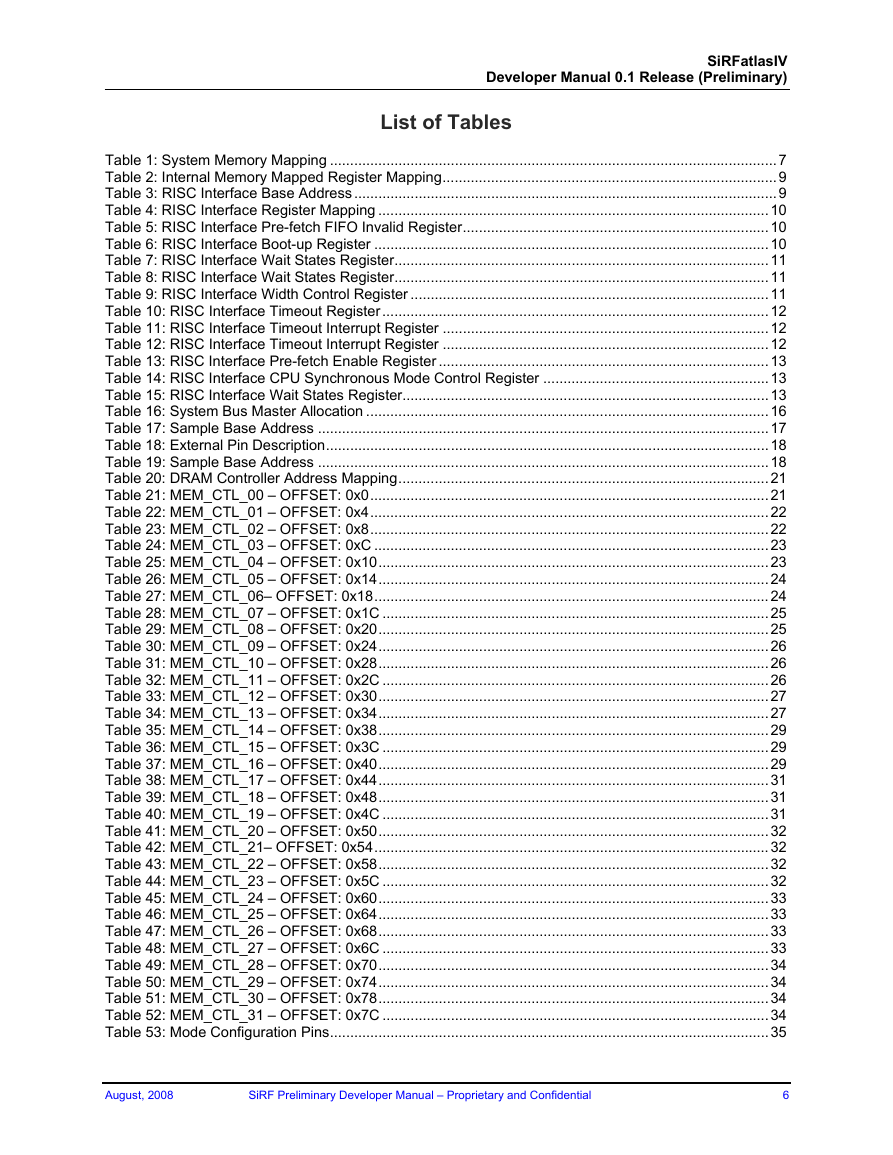

List of Tables

Table 1: System Memory Mapping ...............................................................................................................7

Table 2: Internal Memory Mapped Register Mapping...................................................................................9

Table 3: RISC Interface Base Address .........................................................................................................9

Table 4: RISC Interface Register Mapping .................................................................................................10

Table 5: RISC Interface Pre-fetch FIFO Invalid Register............................................................................10

Table 6: RISC Interface Boot-up Register ..................................................................................................10

Table 7: RISC Interface Wait States Register.............................................................................................11

Table 8: RISC Interface Wait States Register.............................................................................................11

Table 9: RISC Interface Width Control Register .........................................................................................11

Table 10: RISC Interface Timeout Register................................................................................................12

Table 11: RISC Interface Timeout Interrupt Register .................................................................................12

Table 12: RISC Interface Timeout Interrupt Register .................................................................................12

Table 13: RISC Interface Pre-fetch Enable Register ..................................................................................13

Table 14: RISC Interface CPU Synchronous Mode Control Register ........................................................13

Table 15: RISC Interface Wait States Register...........................................................................................13

Table 16: System Bus Master Allocation ....................................................................................................16

Table 17: Sample Base Address ................................................................................................................17

Table 18: External Pin Description..............................................................................................................18

Table 19: Sample Base Address ................................................................................................................18

Table 20: DRAM Controller Address Mapping............................................................................................21

Table 21: MEM_CTL_00 – OFFSET: 0x0...................................................................................................21

Table 22: MEM_CTL_01 – OFFSET: 0x4...................................................................................................22

Table 23: MEM_CTL_02 – OFFSET: 0x8...................................................................................................22

Table 24: MEM_CTL_03 – OFFSET: 0xC ..................................................................................................23

Table 25: MEM_CTL_04 – OFFSET: 0x10.................................................................................................23

Table 26: MEM_CTL_05 – OFFSET: 0x14.................................................................................................24

Table 27: MEM_CTL_06– OFFSET: 0x18..................................................................................................24

Table 28: MEM_CTL_07 – OFFSET: 0x1C ................................................................................................25

Table 29: MEM_CTL_08 – OFFSET: 0x20.................................................................................................25

Table 30: MEM_CTL_09 – OFFSET: 0x24.................................................................................................26

Table 31: MEM_CTL_10 – OFFSET: 0x28.................................................................................................26

Table 32: MEM_CTL_11 – OFFSET: 0x2C ................................................................................................26

Table 33: MEM_CTL_12 – OFFSET: 0x30.................................................................................................27

Table 34: MEM_CTL_13 – OFFSET: 0x34.................................................................................................27

Table 35: MEM_CTL_14 – OFFSET: 0x38.................................................................................................29

Table 36: MEM_CTL_15 – OFFSET: 0x3C ................................................................................................29

Table 37: MEM_CTL_16 – OFFSET: 0x40.................................................................................................29

Table 38: MEM_CTL_17 – OFFSET: 0x44.................................................................................................31

Table 39: MEM_CTL_18 – OFFSET: 0x48.................................................................................................31

Table 40: MEM_CTL_19 – OFFSET: 0x4C ................................................................................................31

Table 41: MEM_CTL_20 – OFFSET: 0x50.................................................................................................32

Table 42: MEM_CTL_21– OFFSET: 0x54..................................................................................................32

Table 43: MEM_CTL_22 – OFFSET: 0x58.................................................................................................32

Table 44: MEM_CTL_23 – OFFSET: 0x5C ................................................................................................32

Table 45: MEM_CTL_24 – OFFSET: 0x60.................................................................................................33

Table 46: MEM_CTL_25 – OFFSET: 0x64.................................................................................................33

Table 47: MEM_CTL_26 – OFFSET: 0x68.................................................................................................33

Table 48: MEM_CTL_27 – OFFSET: 0x6C ................................................................................................33

Table 49: MEM_CTL_28 – OFFSET: 0x70.................................................................................................34

Table 50: MEM_CTL_29 – OFFSET: 0x74.................................................................................................34

Table 51: MEM_CTL_30 – OFFSET: 0x78.................................................................................................34

Table 52: MEM_CTL_31 – OFFSET: 0x7C ................................................................................................34

Table 53: Mode Configuration Pins.............................................................................................................35

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

6

�

SiRFatlasIV

Developer Manual 0.1 Release (Preliminary)

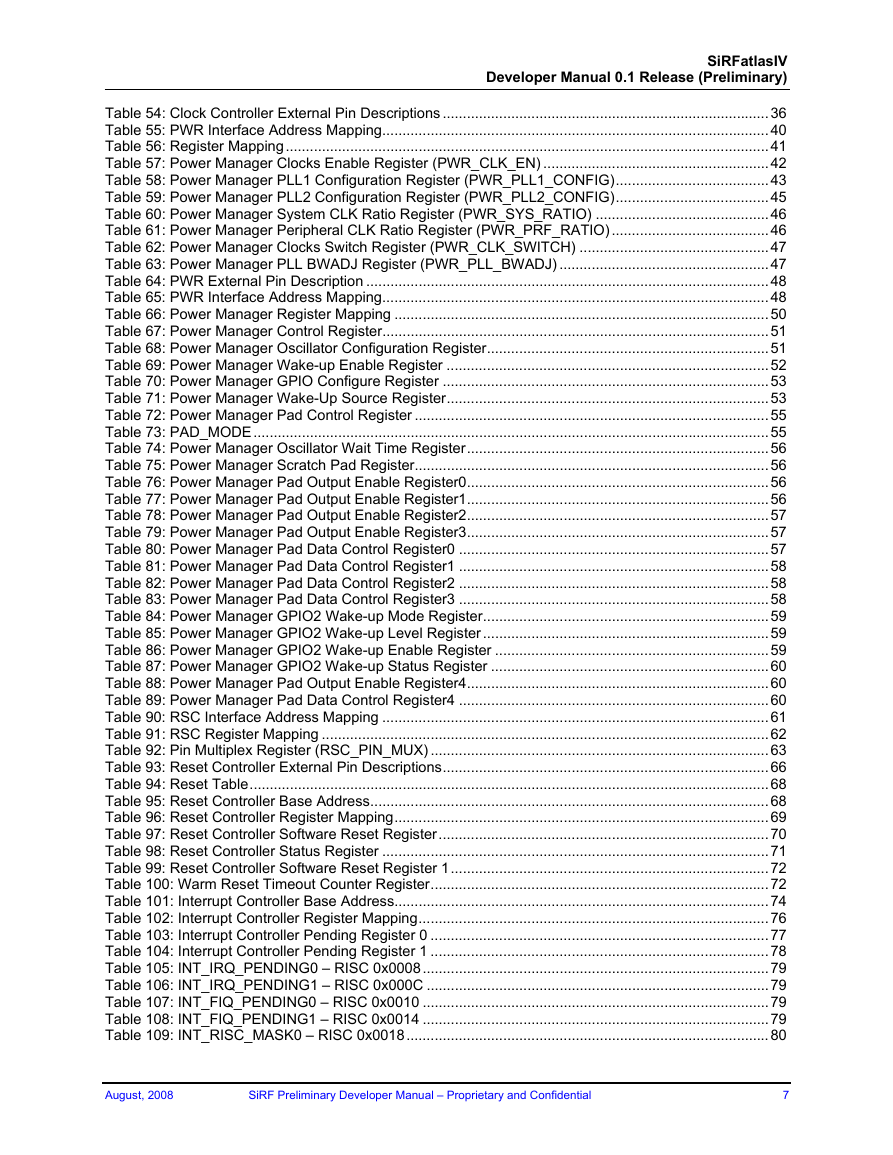

Table 54: Clock Controller External Pin Descriptions .................................................................................36

Table 55: PWR Interface Address Mapping................................................................................................40

Table 56: Register Mapping........................................................................................................................41

Table 57: Power Manager Clocks Enable Register (PWR_CLK_EN) ........................................................42

Table 58: Power Manager PLL1 Configuration Register (PWR_PLL1_CONFIG)......................................43

Table 59: Power Manager PLL2 Configuration Register (PWR_PLL2_CONFIG)......................................45

Table 60: Power Manager System CLK Ratio Register (PWR_SYS_RATIO) ...........................................46

Table 61: Power Manager Peripheral CLK Ratio Register (PWR_PRF_RATIO).......................................46

Table 62: Power Manager Clocks Switch Register (PWR_CLK_SWITCH) ...............................................47

Table 63: Power Manager PLL BWADJ Register (PWR_PLL_BWADJ) ....................................................47

Table 64: PWR External Pin Description ....................................................................................................48

Table 65: PWR Interface Address Mapping................................................................................................48

Table 66: Power Manager Register Mapping .............................................................................................50

Table 67: Power Manager Control Register................................................................................................51

Table 68: Power Manager Oscillator Configuration Register......................................................................51

Table 69: Power Manager Wake-up Enable Register ................................................................................52

Table 70: Power Manager GPIO Configure Register .................................................................................53

Table 71: Power Manager Wake-Up Source Register................................................................................53

Table 72: Power Manager Pad Control Register ........................................................................................55

Table 73: PAD_MODE................................................................................................................................55

Table 74: Power Manager Oscillator Wait Time Register...........................................................................56

Table 75: Power Manager Scratch Pad Register........................................................................................56

Table 76: Power Manager Pad Output Enable Register0...........................................................................56

Table 77: Power Manager Pad Output Enable Register1...........................................................................56

Table 78: Power Manager Pad Output Enable Register2...........................................................................57

Table 79: Power Manager Pad Output Enable Register3...........................................................................57

Table 80: Power Manager Pad Data Control Register0 .............................................................................57

Table 81: Power Manager Pad Data Control Register1 .............................................................................58

Table 82: Power Manager Pad Data Control Register2 .............................................................................58

Table 83: Power Manager Pad Data Control Register3 .............................................................................58

Table 84: Power Manager GPIO2 Wake-up Mode Register.......................................................................59

Table 85: Power Manager GPIO2 Wake-up Level Register.......................................................................59

Table 86: Power Manager GPIO2 Wake-up Enable Register ....................................................................59

Table 87: Power Manager GPIO2 Wake-up Status Register .....................................................................60

Table 88: Power Manager Pad Output Enable Register4...........................................................................60

Table 89: Power Manager Pad Data Control Register4 .............................................................................60

Table 90: RSC Interface Address Mapping ................................................................................................61

Table 91: RSC Register Mapping ...............................................................................................................62

Table 92: Pin Multiplex Register (RSC_PIN_MUX) ....................................................................................63

Table 93: Reset Controller External Pin Descriptions.................................................................................66

Table 94: Reset Table.................................................................................................................................68

Table 95: Reset Controller Base Address...................................................................................................68

Table 96: Reset Controller Register Mapping.............................................................................................69

Table 97: Reset Controller Software Reset Register..................................................................................70

Table 98: Reset Controller Status Register ................................................................................................71

Table 99: Reset Controller Software Reset Register 1...............................................................................72

Table 100: Warm Reset Timeout Counter Register....................................................................................72

Table 101: Interrupt Controller Base Address.............................................................................................74

Table 102: Interrupt Controller Register Mapping.......................................................................................76

Table 103: Interrupt Controller Pending Register 0 ....................................................................................77

Table 104: Interrupt Controller Pending Register 1 ....................................................................................78

Table 105: INT_IRQ_PENDING0 – RISC 0x0008......................................................................................79

Table 106: INT_IRQ_PENDING1 – RISC 0x000C .....................................................................................79

Table 107: INT_FIQ_PENDING0 – RISC 0x0010 ......................................................................................79

Table 108: INT_FIQ_PENDING1 – RISC 0x0014 ......................................................................................79

Table 109: INT_RISC_MASK0 – RISC 0x0018..........................................................................................80

August, 2008

SiRF Preliminary Developer Manual – Proprietary and Confidential

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc