1. DSP 的特点

DSP 作为可编程超大规模集成电路(VLSD)器件,是通过可下载的软件或固件来实现扩

展算法和数字信号处理功能的,其最典型的用途是实现数字图像处理算法。

在硬件上,DSP 最基本的构造单元是被称为 MAC 的乘加器。它通常被集成在数据通道

中,这使得指令周期时间可以跟硬件的算术周期时间相同。

DSP 芯片丰富的片内资源,大容量的 SRAM 作为系统的高速缓存,高达 64 位的数据

总线使系统具有很高带宽等。

在片外支持大容量存储器,图像处理中往往有大量数据需要处理,这就要求系统具有大

容量的存储器,实时处理图像时要求存储器有很高的存取速度,在这一点上 DSP 实现了与

目前流行的 SDRAM、SBSRAM 等高速大容量存储器的无缝连接,同时还支持 SRAM、FIFO

等各种类型的存储器。为满足便携式器件无电保存数据的要求,DSP 芯片还提供了诸闪速

存储器、铁电存储器等的无缝接口。

当前,大多数的 DSP 芯片采用改进的哈佛结构,即数据总线和地址总线相互分离,使

得处理指令和数据可以同时进行,提高了处理效率。

另外还采用了流水线技术,将取指、取操作数、执指等步骤的指令时间可以重叠起来,

大大提高运算速度。

1.1. 修正的哈佛结构

DSP 芯片采用修正的哈佛结构(Havardstructure),其特点是:

1) 程序和数据具有独立的存储空间、程序总线和数据总线,非常适合实时的数字信号

处理。

2) 同时,这种结构使指令存储在高速缓存器中(Cache),节约了从存储器中读取指令

的时间,提高了运行速度。

1.2. 专用的乘法器

一般的算术逻辑单元 ALU(Arithmetic and Logic Unit)的乘法(或除法)运算由加法和移位

实现,运算速度较慢。

DSP 设置了专用的硬件乘法器、多数能在半个指令周期内完成乘法运算,速度已达每

�

秒数千万次乃至数十亿次定点运算或浮点运算,非常适用于高度密集、重复运算及大数据流

量的信号处理。

1.3. 特殊的指令设置

DSP 在指令系统中设置了“循环寻址”(Circular addressing)及“位倒序”(bit—reversed)等

特殊指令,使寻址、排序及运算速度大大提高。

另外,DSP 指令系统的流水线操作与哈佛结构相配合,把指令周期减小到最小值,增

加了处理器的处理能力。

尽管如此,DSP 芯片的单机处理能力还是有限的,多个 DSP 芯片的并行处理已成为研

究的热点。

2. FPGA 与 DSP 之间的通信

�

�

3. 图像压缩/解压缩一 DCT/IDCT

目前数字视频系统中采用的主要视频压缩方案是 MPEG2。

它广泛用于数字电视、机顶盒、数字卫星系统、高分辨率电视(HDTV)解码器、DVD 播

放机、数字视频会议设备和 Web 电话等应用的核心部分

同时也有一些新标准已经或正在制定之中,包括最著名的 MPEG4 标准。

在 MPEG2 和 MPEG4 算法的核心是称为离散余弦变换(DCT)的功能。DCT 的目的是

取出一块像素点并去除其中人觉察不到的冗余信息。为解压缩数据,需要离散余弦变换反变

换功能。

4. FPGA Vs DSP

例如,Visicom 公司发现对中值过滤器应用,DSP 处理器需要 67 个周期完成该算法。

采用 FPGA 器件只需要运行在 25MHz,因为 FPGA 可并行实现该功能。而 DSP 要达到同

样的性能则需要运行在超过 1.5GHz 频率。在这一特定的应用中,FPGA 解决方案比一个

100MHz 的 DSP 处理器要强大约 17 倍。

范围广泛的实时图像和视频处理功能都适配采用 FPGA 器件实施,它们包括实时:

·图像放置

�

·缩放

·色彩和色差校正

·阴影增强

·边缘检测

·直方图功能

·锐化

·中值过滤器

·模糊分析

许多此类功能都是针对特定应用和系统的,并且与核心架构如 2D 一滤波器相关。

这些功能可利用 H DL 语言设计或利用象 Xilinx CoreGen 软件这样的高级核心设计工具

中提供的 DSP 构造模块快速实现。

还可利用 Matlabs Simulink 和 Xilinx 系统生成器工具等,通过采用系统级设计方法,同

时缩短设计和模拟时间。

5. TI--DSP

1997 年Ⅱ 公司发布的 TMS320C6X 系列.

运算速度高至 1600MIPS。

再加上灵活的 EMIF 和 HPI 接口,

以及 4 个 DMA 数据传输通道等,

都使得构建小型实时化的视频实时数字图像处理器成为可能。

6. DSP 视频图像数字处理电路 1

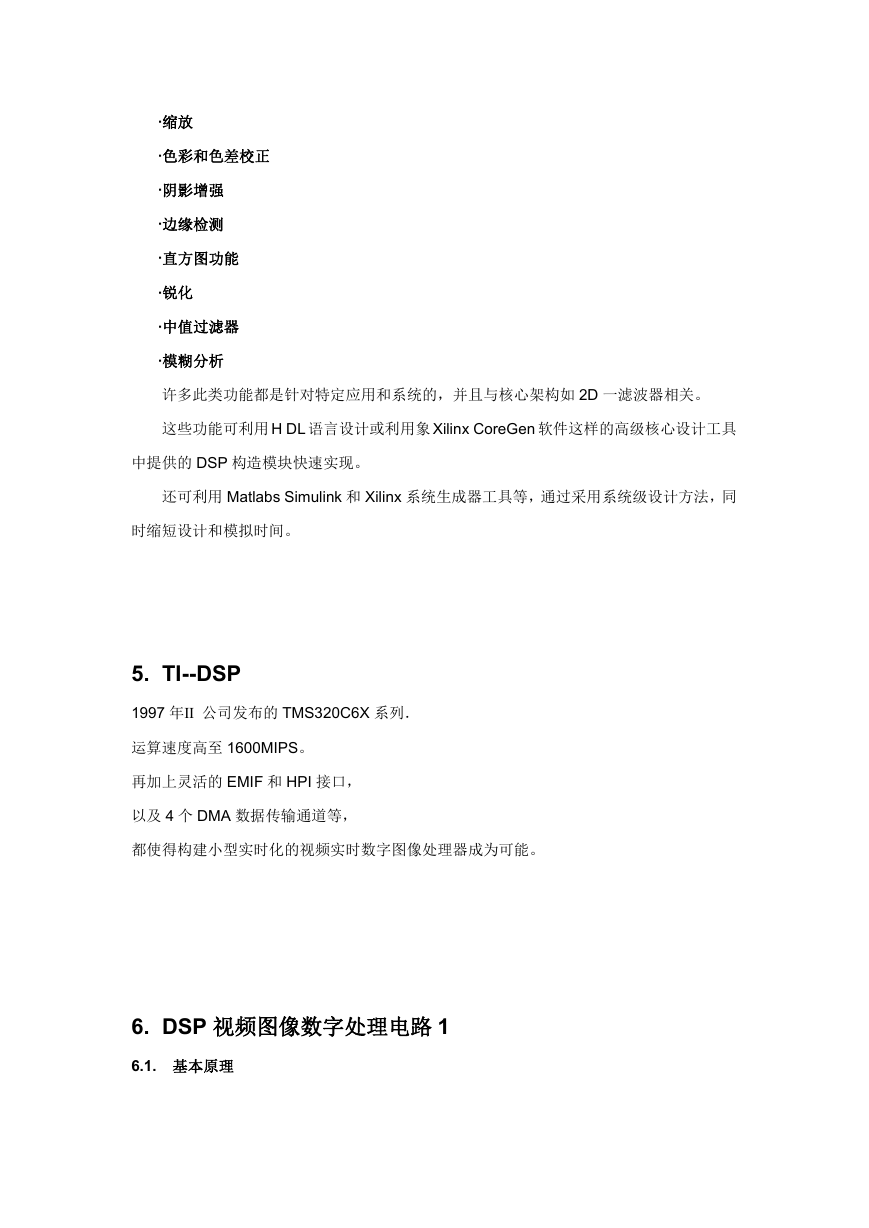

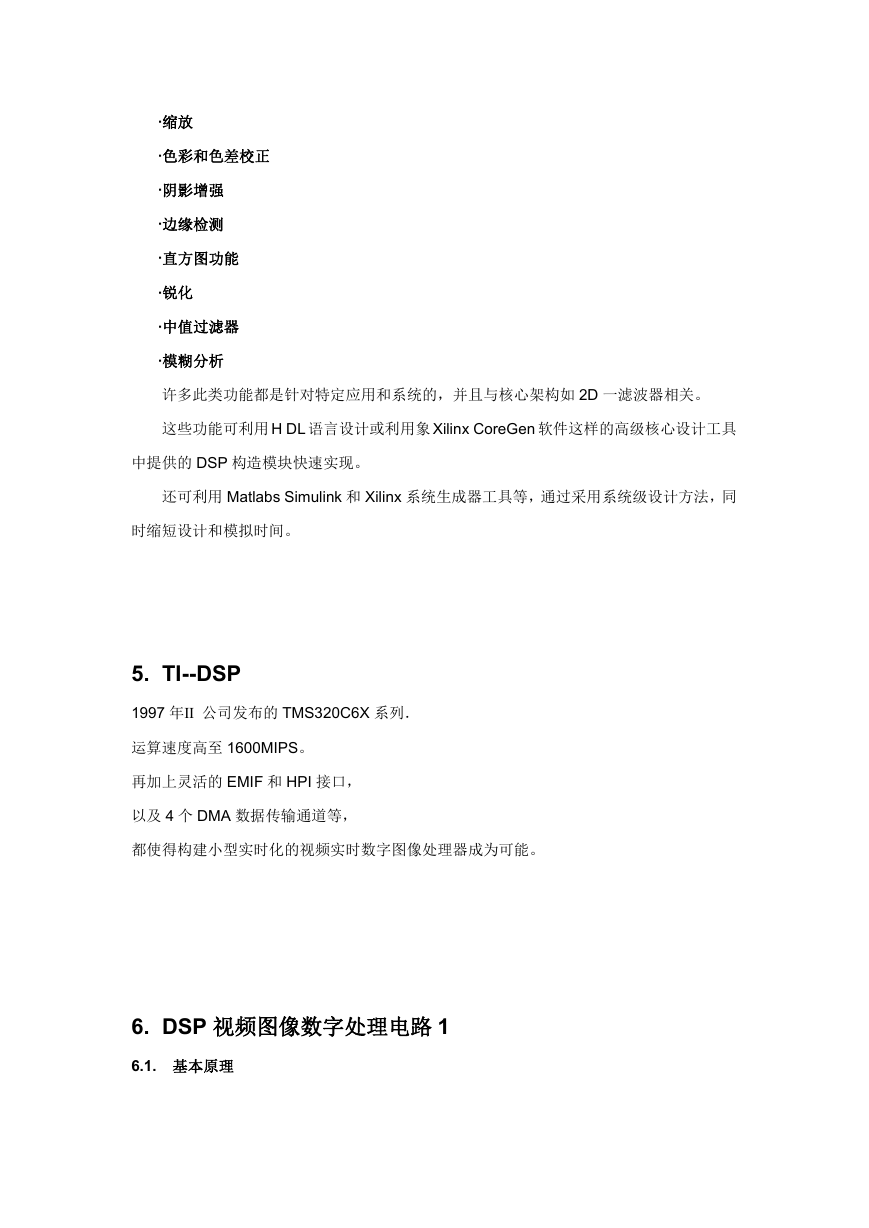

6.1. 基本原理

�

其基本原理与工作过程为:行消隐信号一结束,“时钟发生与控制”电路即输出采样(转换)

时钟信号使 A/D 和 D/A 转换器开始工作。A/D 采样的数据通过先人先出存储器(FIFO)

并经由 TMS320 的 DMA 通道存人帧数据存储器中;同时存在帧数据存储器中处理后的图像

数据经由 DMA 通道,并通过另一 FIFO 进入 DMA 转换器转换为模拟信号,该模拟信号在

复合同步时钟的控制下,转换为标准的视频信号。

在这个过程中,垂直同步和奇偶场信号通过中断的方式通知 DSP 一帧信号的开始。由

于 DMA 可以进行背景操作(background operation),因而整个采样和输出过程基本上不影

响 CPU 的数据运算,再加上外围采用高速的数据存储器芯片,故整个系统的处理速度得到

大大提高。

6.2. 设计需要考虑的关键问题

6.2.2 图像分辨率

图像分辨率即对一帧图像所采样的像素数目,通常用 M×N 表示。它的选取要注意到如

下几个条件与制约关系:

1) 必须满足香农采样定理,即采样波形的重复额率至少应为电视图像信号最高频率的

两倍。

�

2) 应考虑便于进行帧存储器的选取。

6.2.2 A/D 采样时钟

A/D 采样的时钟频率 f 主要由图像的水平分辨率 M 决定,即 f=M/51.5(us)。

当 M=512 时, f=10MHz。

6.2.3 实时性

6.2.4 连续性

�

6.3. 关键器件的选取

6.3.1 视频同步分离器的选择

6.3.1 A/D,D/A 转换器的选择

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc