Cadence Allegro V17.2 Back Drill Enhancement 上篇 -

Padstack Editor

在網通及伺服器產品,高速電路設計中越來越常使用 10/25 Gbps 的

信號,由於 PCB 材質、走線長度及 Via Stub 對於高頻信號所造成的

損耗則越顯得嚴重。因此,Backdrill 能夠針對 Via Stub 的問題做為

解決方案之一;V17.2 對 Backdrill 處理技術有多方面的提昇, 如:

經由 Padstack 設計即可帶入背鑽孔徑定義、處理後限制區及 Via 標

籤顯示等功能。藉由此篇介紹來了解 Backdrill 的使用時機,後續再

接著一篇文件來說明 Back Drill 的設定,相信是值得期待的。

.Date: 2016 / 12 / 19

.Author: Mark Wu

.Revision:

.Version:Allegro V17.2

.備註:

http://www.graser.com.tw

�

Back Drill 概說

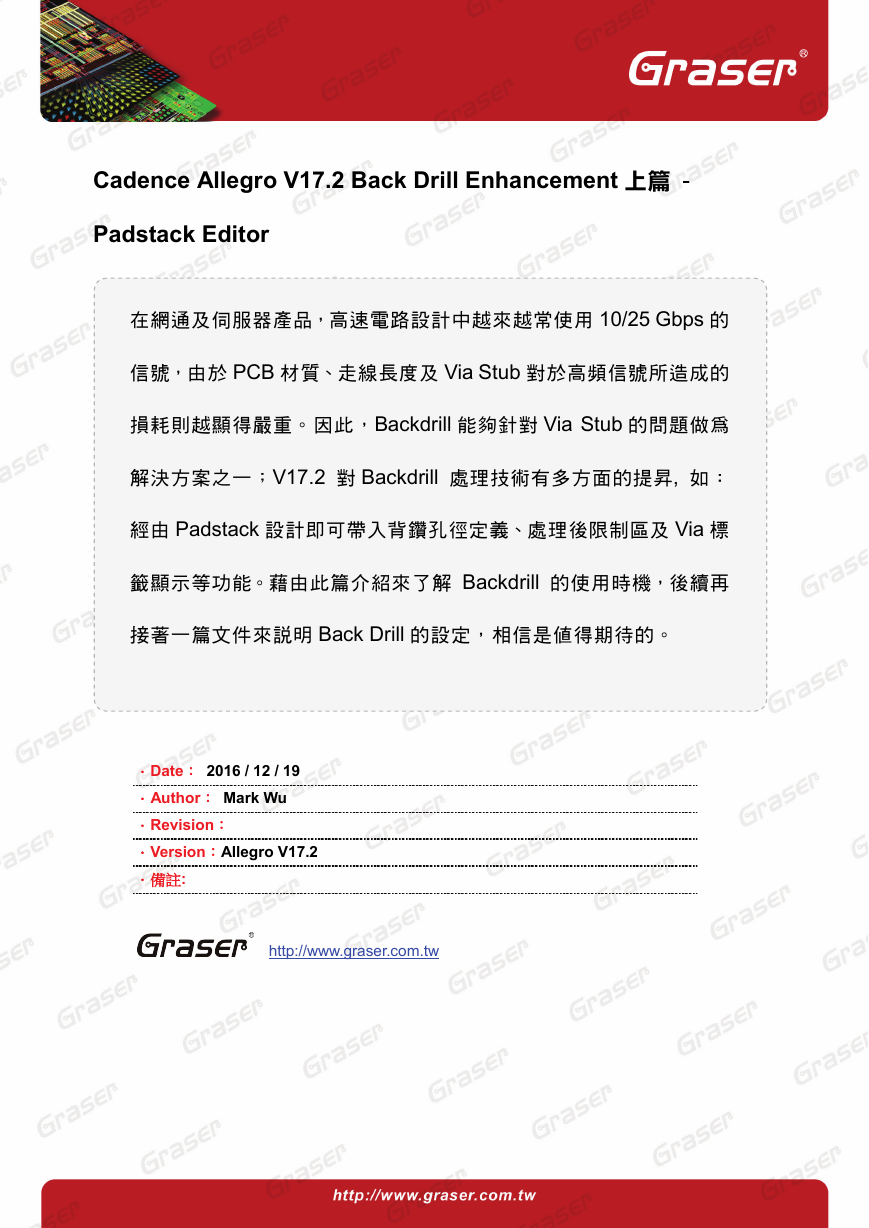

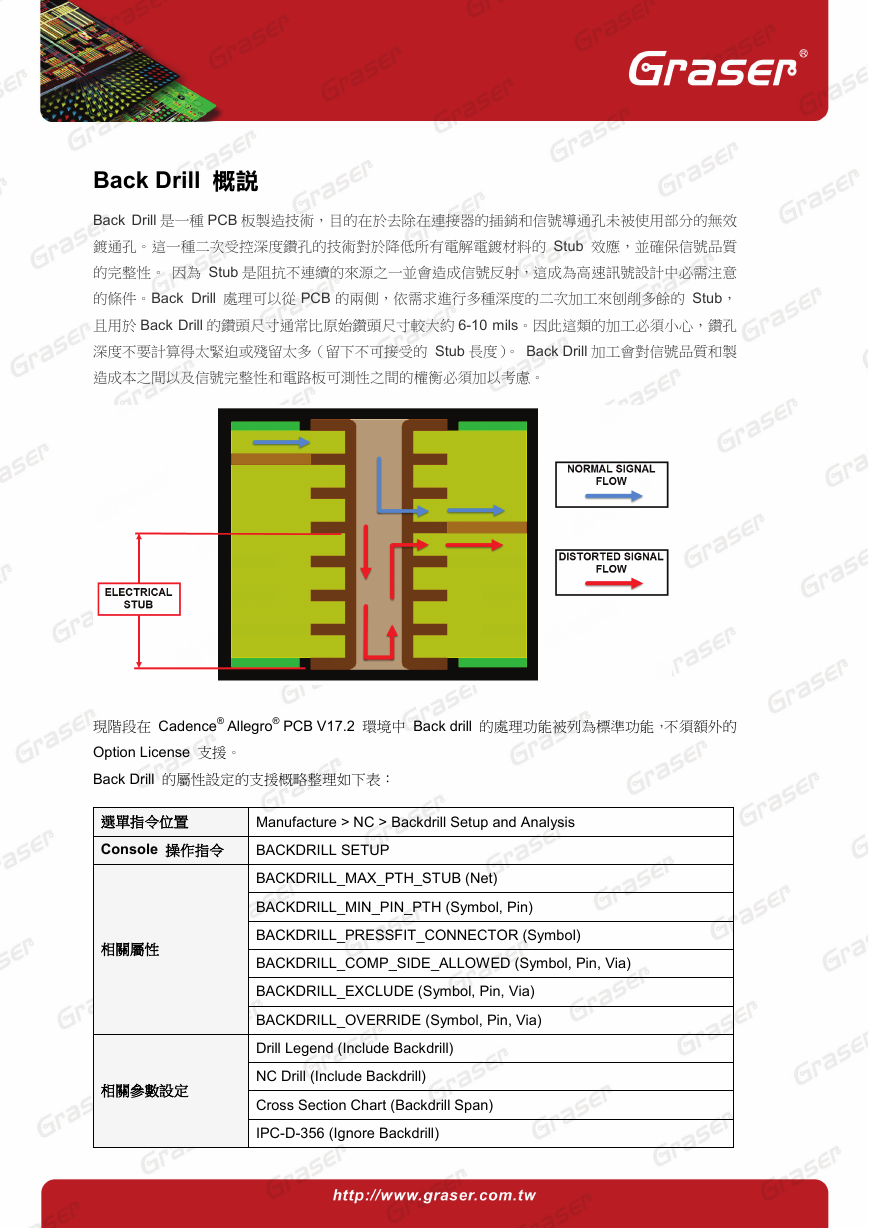

Back Drill 是一種 PCB 板製造技術,目的在於去除在連接器的插銷和信號導通孔未被使用部分的無效

鍍通孔。這一種二次受控深度鑽孔的技術對於降低所有電解電鍍材料的 Stub 效應,並確保信號品質

的完整性。 因為 Stub 是阻抗不連續的來源之一並會造成信號反射,這成為高速訊號設計中必需注意

的條件。Back Drill 處理可以從 PCB 的兩側,依需求進行多種深度的二次加工來刨削多餘的 Stub,

且用於 Back Drill 的鑽頭尺寸通常比原始鑽頭尺寸較大約 6-10 mils。因此這類的加工必須小心,鑽孔

深度不要計算得太緊迫或殘留太多(留下不可接受的 Stub 長度)。 Back Drill 加工會對信號品質和製

造成本之間以及信號完整性和電路板可測性之間的權衡必須加以考慮。

現階段在 Cadence® Allegro® PCB V17.2 環境中 Back drill 的處理功能被列為標準功能,不須額外的

Option License 支援。

Back Drill 的屬性設定的支援概略整理如下表:

選單指令位置

Console 操作指令

相關屬性

相關參數設定

Manufacture > NC > Backdrill Setup and Analysis

BACKDRILL SETUP

BACKDRILL_MAX_PTH_STUB (Net)

BACKDRILL_MIN_PIN_PTH (Symbol, Pin)

BACKDRILL_PRESSFIT_CONNECTOR (Symbol)

BACKDRILL_COMP_SIDE_ALLOWED (Symbol, Pin, Via)

BACKDRILL_EXCLUDE (Symbol, Pin, Via)

BACKDRILL_OVERRIDE (Symbol, Pin, Via)

Drill Legend (Include Backdrill)

NC Drill (Include Backdrill)

Cross Section Chart (Backdrill Span)

IPC-D-356 (Ignore Backdrill)

�

與 Manufacture 屬 性

相關的層面

BACKDRILL-FLAG-TOP (Top side violation flags)

BACKDRILL-FLAG-BOT (Bottom side violation flags)

BACKDRILL-FLAG-ANY (Internal layer violation flags)

NCBACKDRILL-- (Backdrill legends)

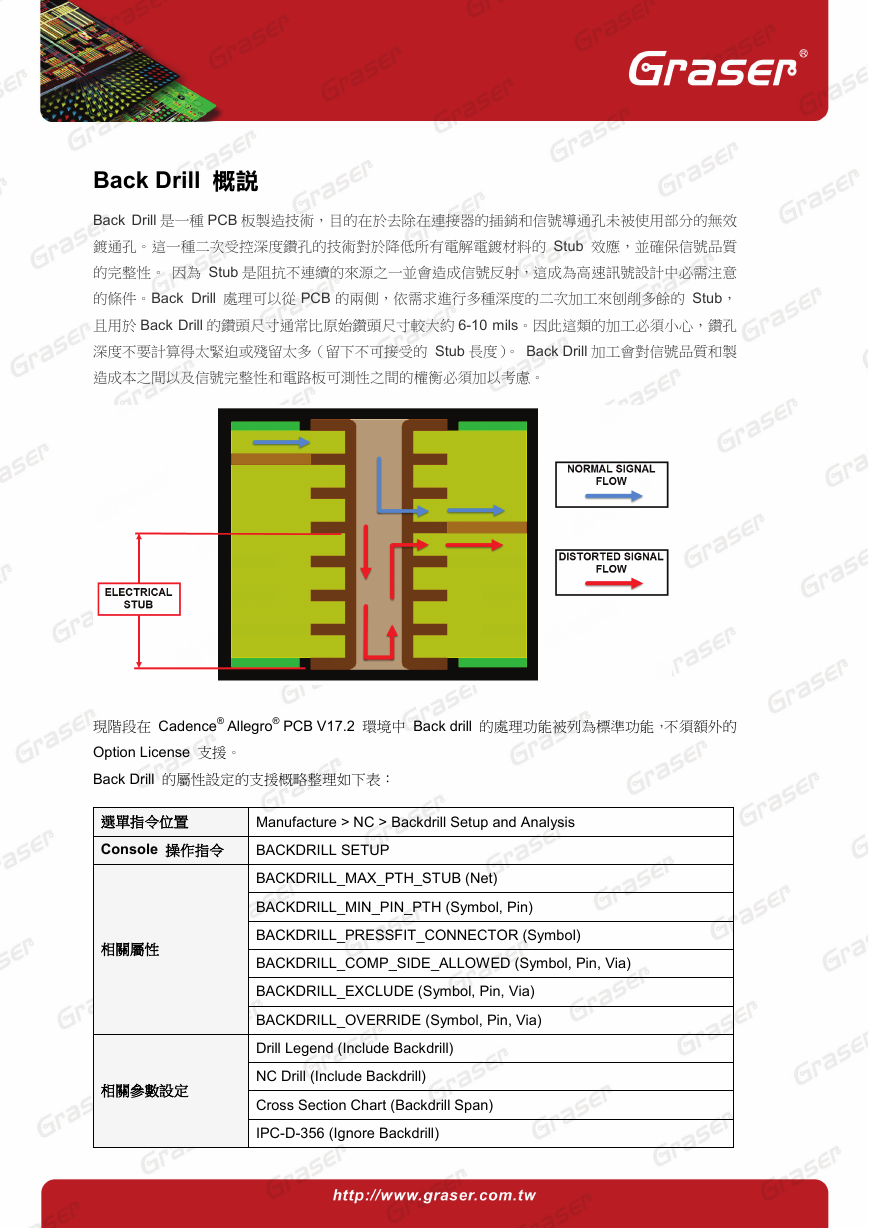

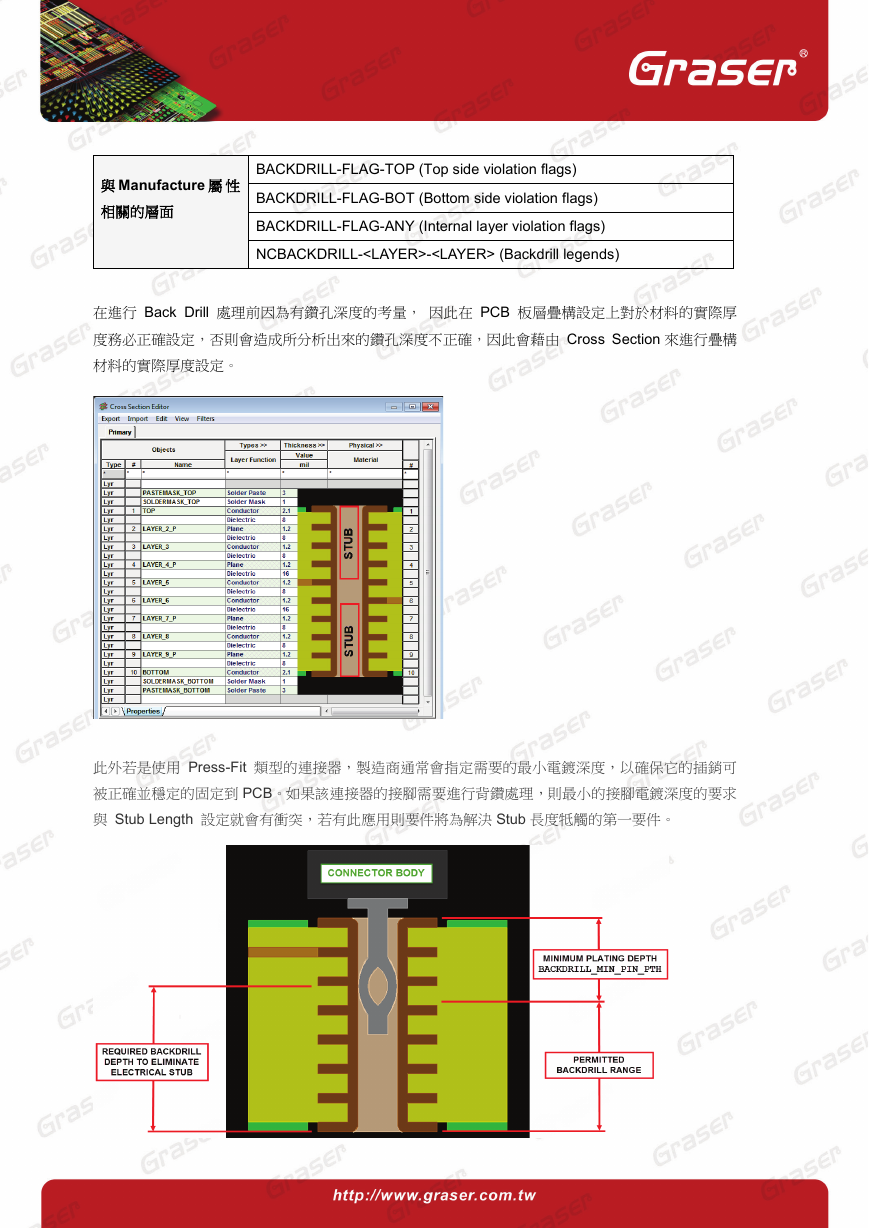

在進行 Back Drill 處理前因為有鑽孔深度的考量, 因此在 PCB 板層疊構設定上對於材料的實際厚

度務必正確設定,否則會造成所分析出來的鑽孔深度不正確,因此會藉由 Cross Section 來進行疊構

材料的實際厚度設定。

此外若是使用 Press-Fit 類型的連接器,製造商通常會指定需要的最小電鍍深度,以確保它的插銷可

被正確並穩定的固定到 PCB。如果該連接器的接腳需要進行背鑽處理,則最小的接腳電鍍深度的要求

與 Stub Length 設定就會有衝突,若有此應用則要件將為解決 Stub 長度牴觸的第一要件。

�

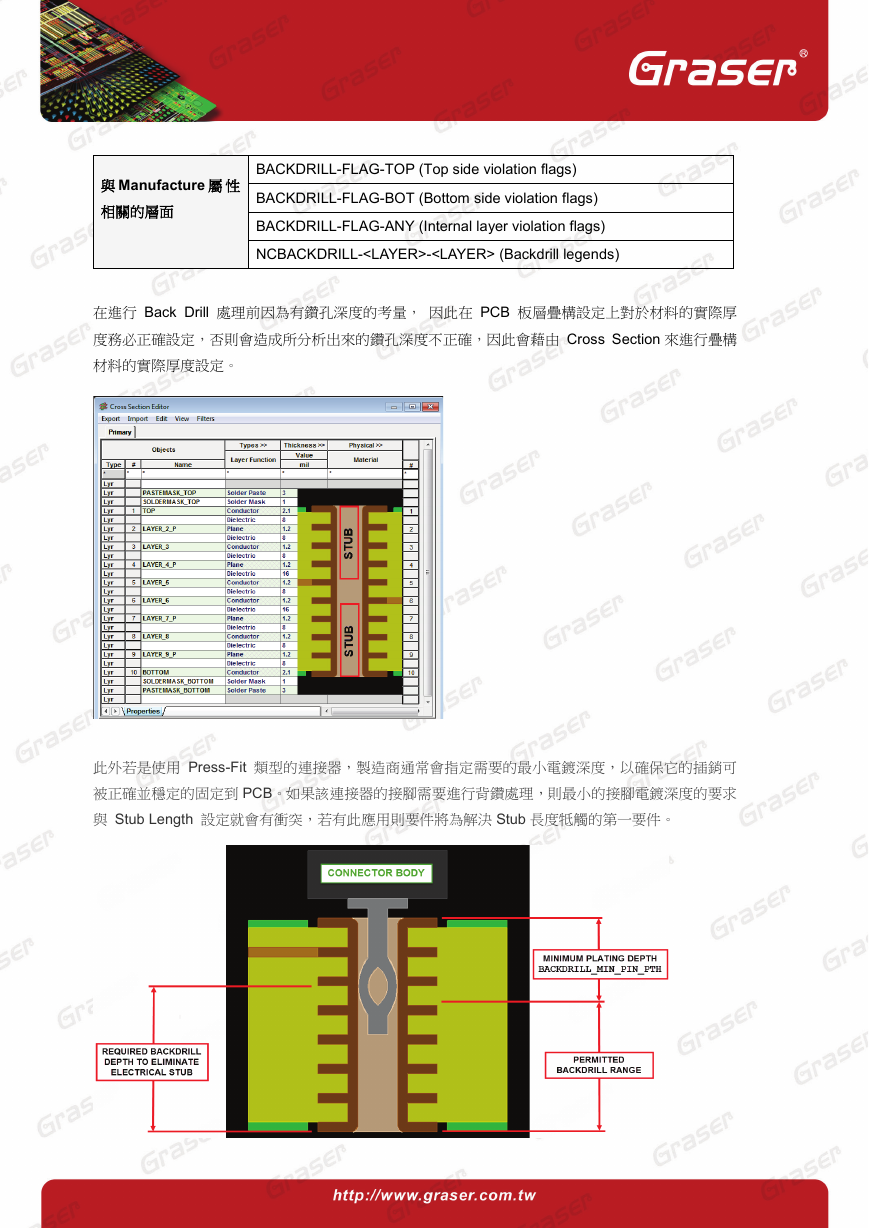

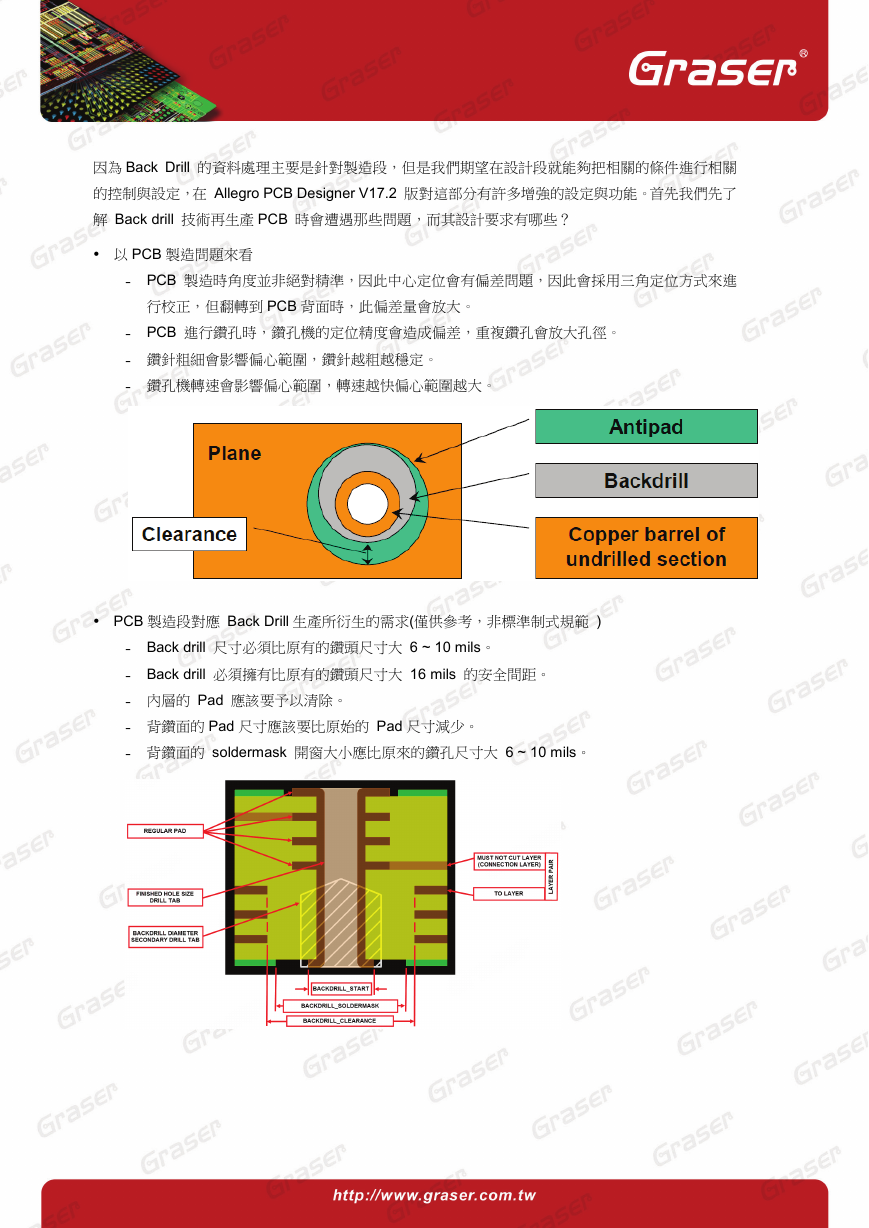

因為 Back Drill 的資料處理主要是針對製造段,但是我們期望在設計段就能夠把相關的條件進行相關

的控制與設定,在 Allegro PCB Designer V17.2 版對這部分有許多增強的設定與功能。首先我們先了

解 Back drill 技術再生產 PCB 時會遭遇那些問題,而其設計要求有哪些?

以 PCB 製造問題來看

̵ PCB 製造時角度並非絕對精準,因此中心定位會有偏差問題,因此會採用三角定位方式來進

行校正,但翻轉到 PCB 背面時,此偏差量會放大。

̵ PCB 進行鑽孔時,鑽孔機的定位精度會造成偏差,重複鑽孔會放大孔徑。

̵ 鑽針粗細會影響偏心範圍,鑽針越粗越穩定。

̵ 鑽孔機轉速會影響偏心範圍,轉速越快偏心範圍越大。

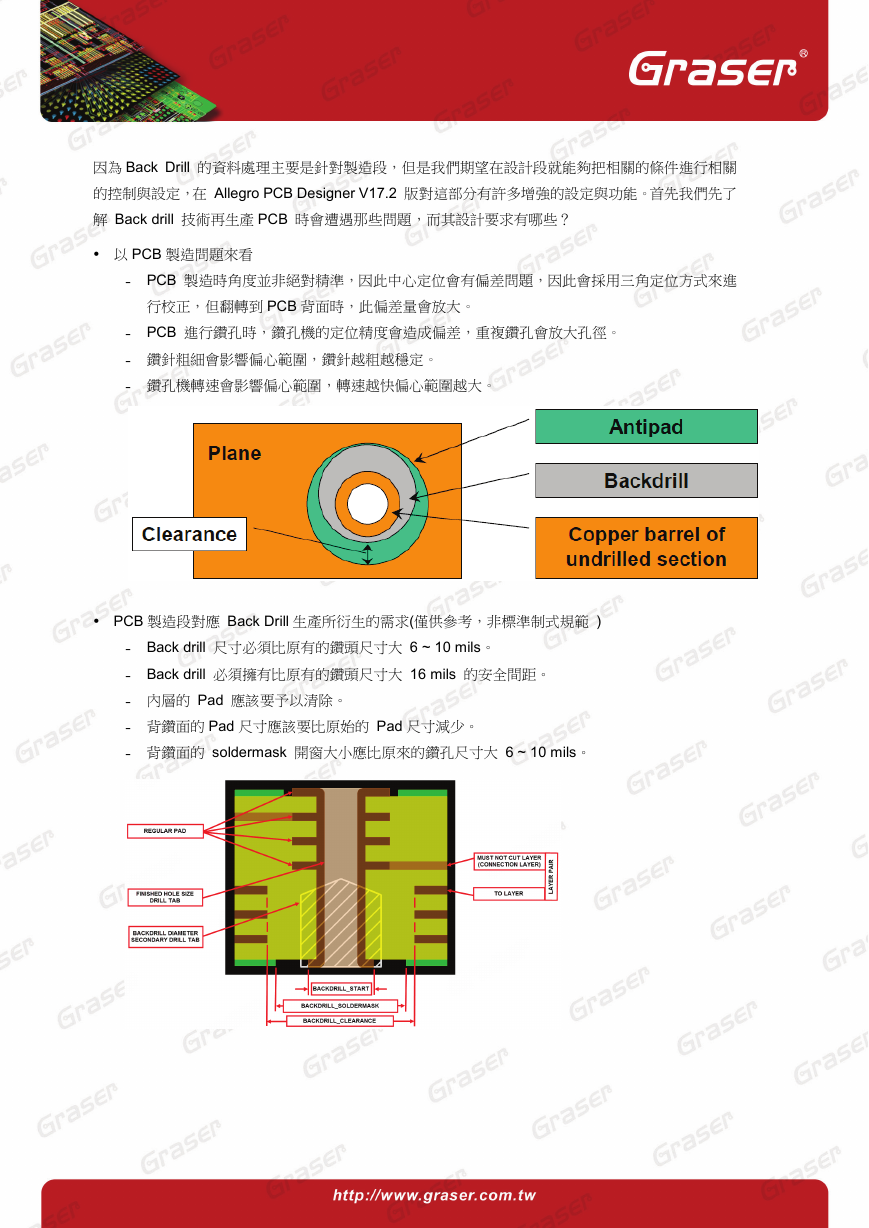

PCB 製造段對應 Back Drill 生產所衍生的需求(僅供參考,非標準制式規範 )

̵ Back drill 尺寸必須比原有的鑽頭尺寸大 6 ~ 10 mils。

̵ Back drill 必須擁有比原有的鑽頭尺寸大 16 mils 的安全間距。

̵ 內層的 Pad 應該要予以清除。

̵ 背鑽面的 Pad 尺寸應該要比原始的 Pad 尺寸減少。

̵ 背鑽面的 soldermask 開窗大小應比原來的鑽孔尺寸大 6 ~ 10 mils。

�

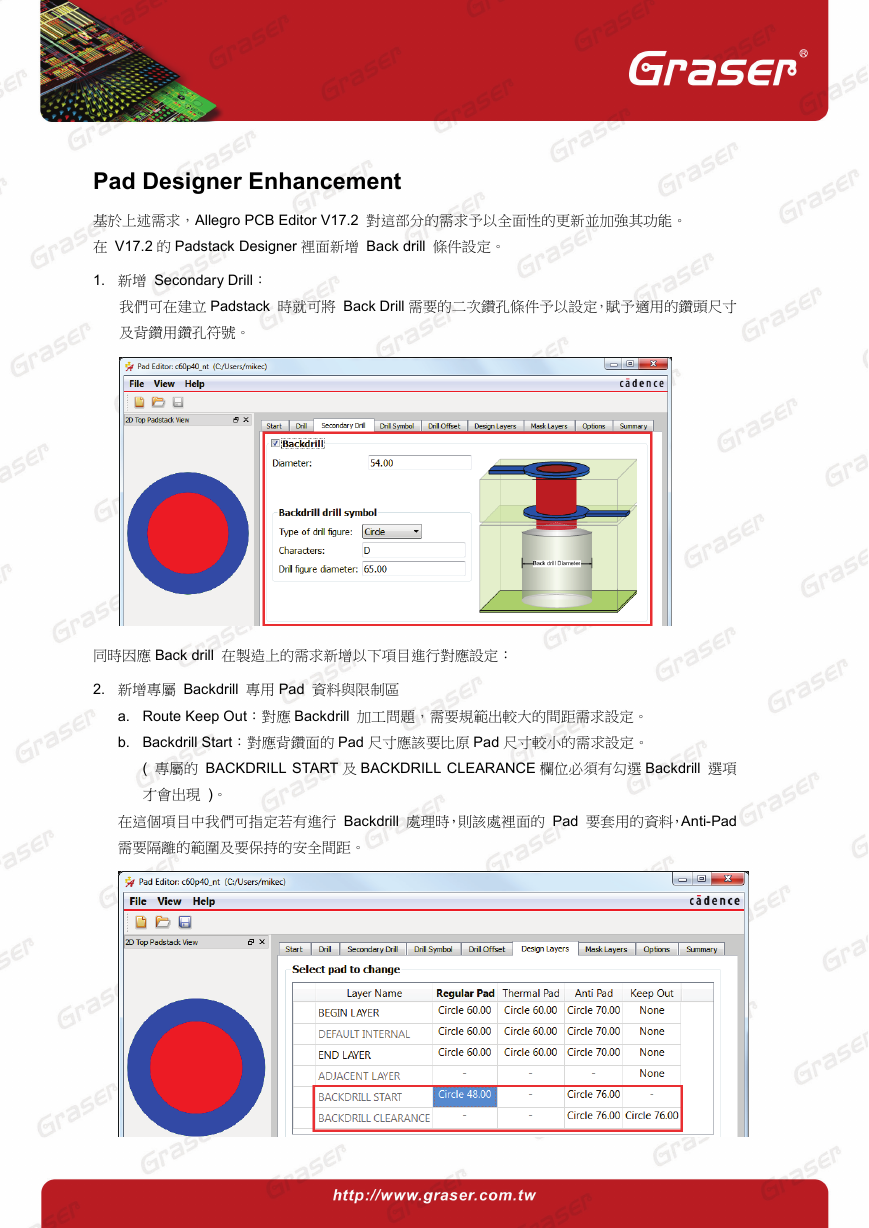

Pad Designer Enhancement

基於上述需求,Allegro PCB Editor V17.2 對這部分的需求予以全面性的更新並加強其功能。

在 V17.2 的 Padstack Designer 裡面新增 Back drill 條件設定。

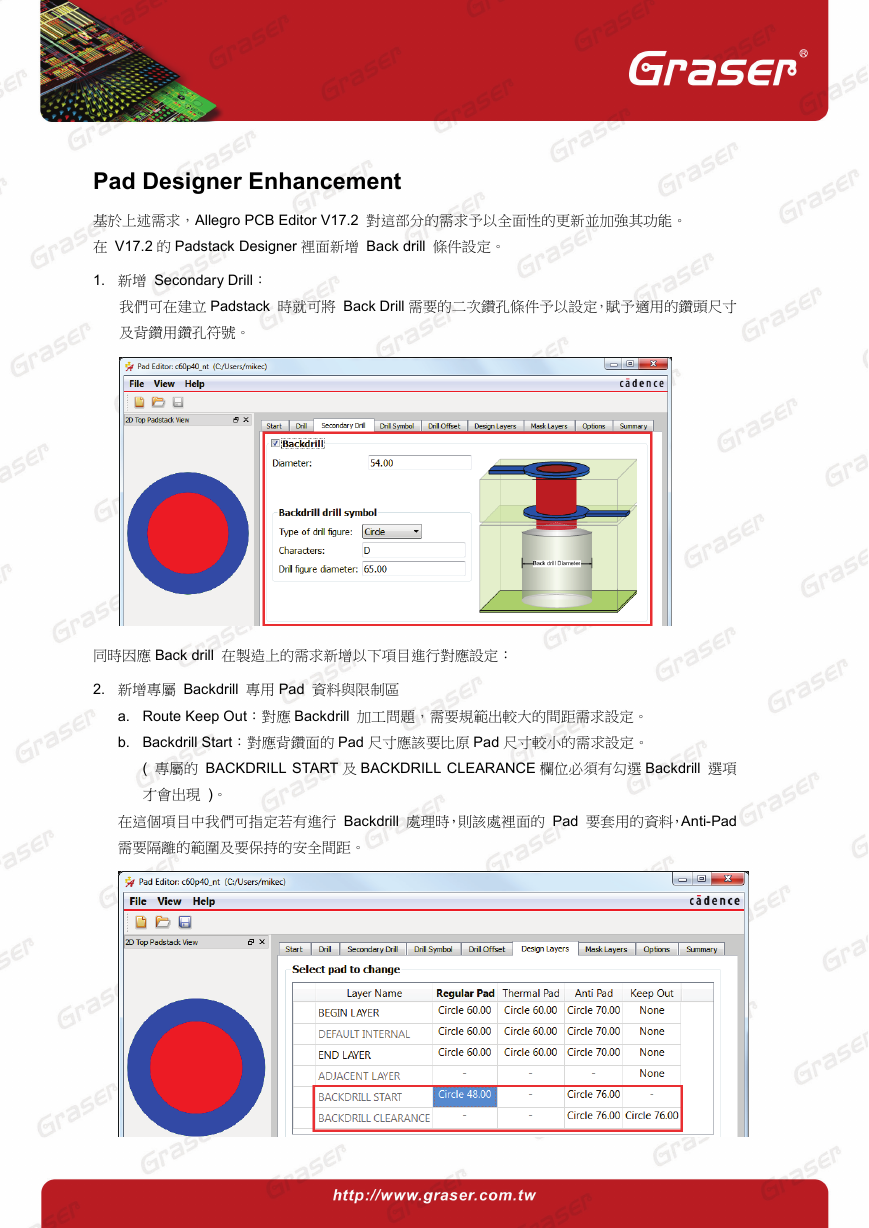

1. 新增 Secondary Drill:

我們可在建立 Padstack 時就可將 Back Drill 需要的二次鑽孔條件予以設定,賦予適用的鑽頭尺寸

及背鑽用鑽孔符號。

同時因應 Back drill 在製造上的需求新增以下項目進行對應設定:

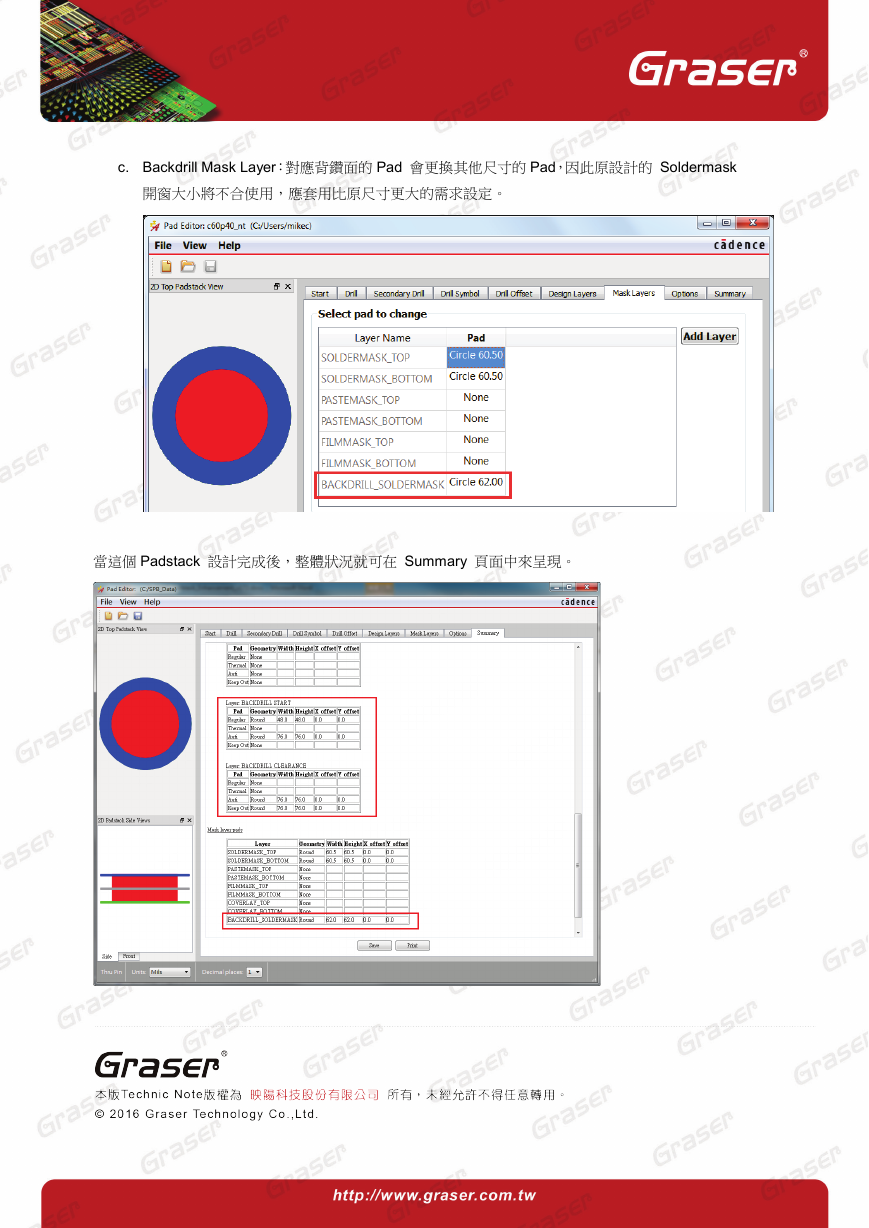

2. 新增專屬 Backdrill 專用 Pad 資料與限制區

a. Route Keep Out:對應 Backdrill 加工問題,需要規範出較大的間距需求設定。

b. Backdrill Start:對應背鑽面的 Pad 尺寸應該要比原 Pad 尺寸較小的需求設定。

( 專屬的 BACKDRILL START 及 BACKDRILL CLEARANCE 欄位必須有勾選 Backdrill 選項

才會出現 )。

在這個項目中我們可指定若有進行 Backdrill 處理時,則該處裡面的 Pad 要套用的資料,Anti-Pad

需要隔離的範圍及要保持的安全間距。

�

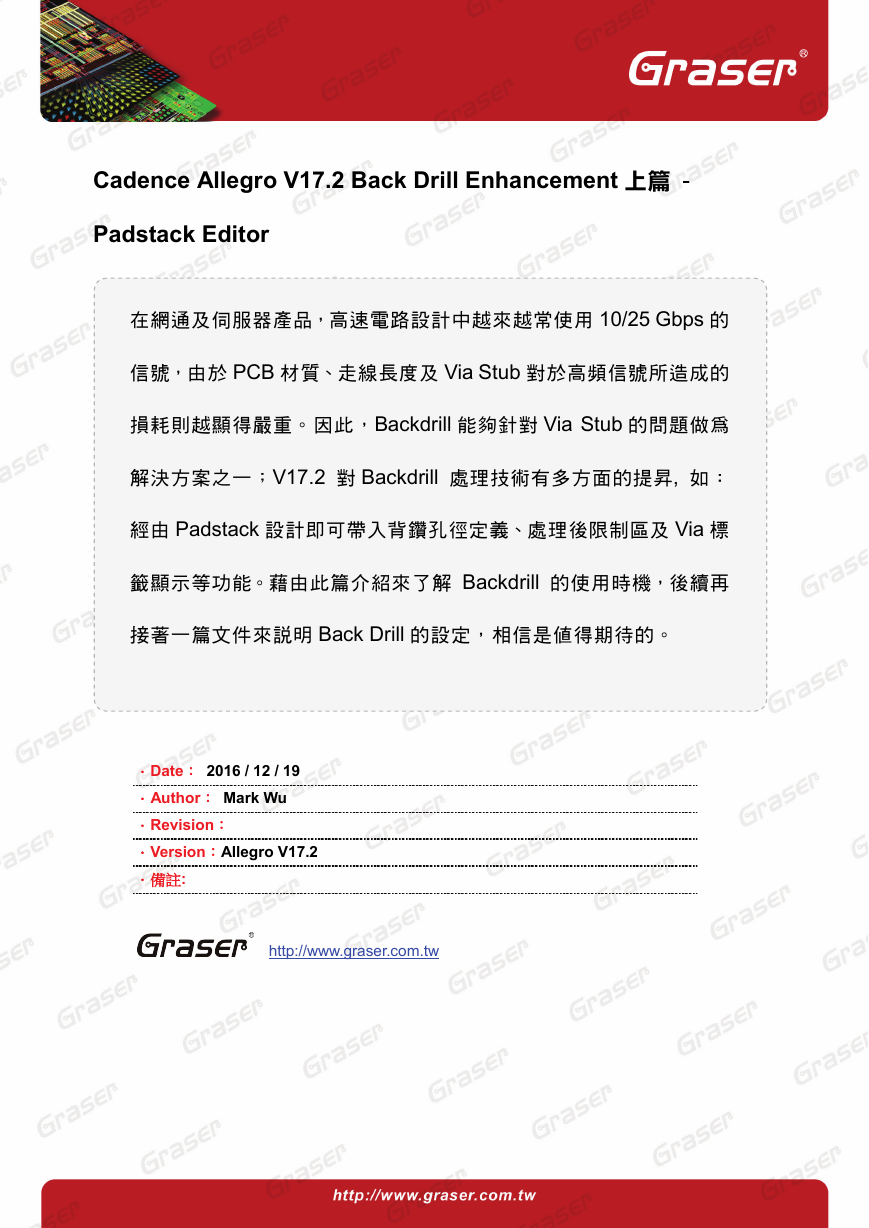

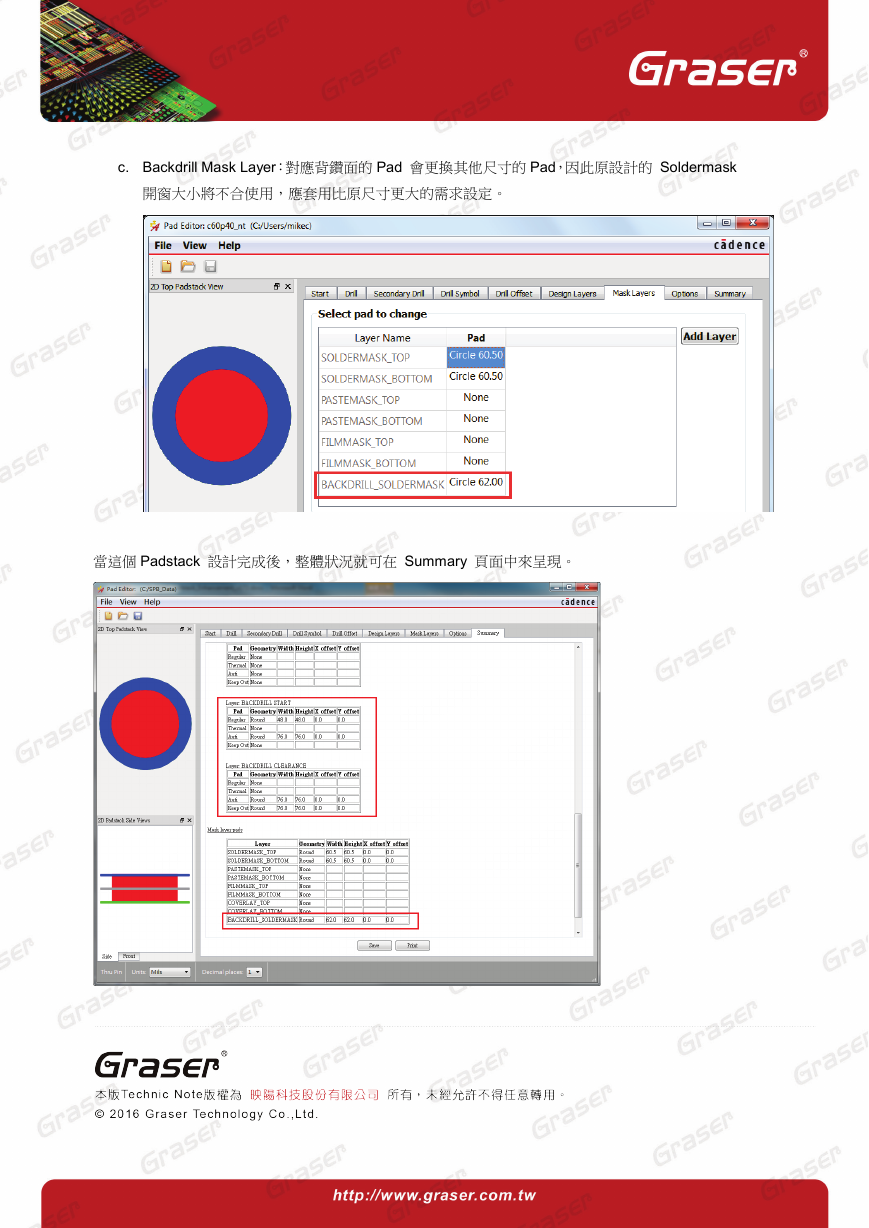

c. Backdrill Mask Layer:對應背鑽面的 Pad 會更換其他尺寸的 Pad,因此原設計的 Soldermask

開窗大小將不合使用,應套用比原尺寸更大的需求設定。

當這個 Padstack 設計完成後,整體狀況就可在 Summary 頁面中來呈現。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc