1、HFN

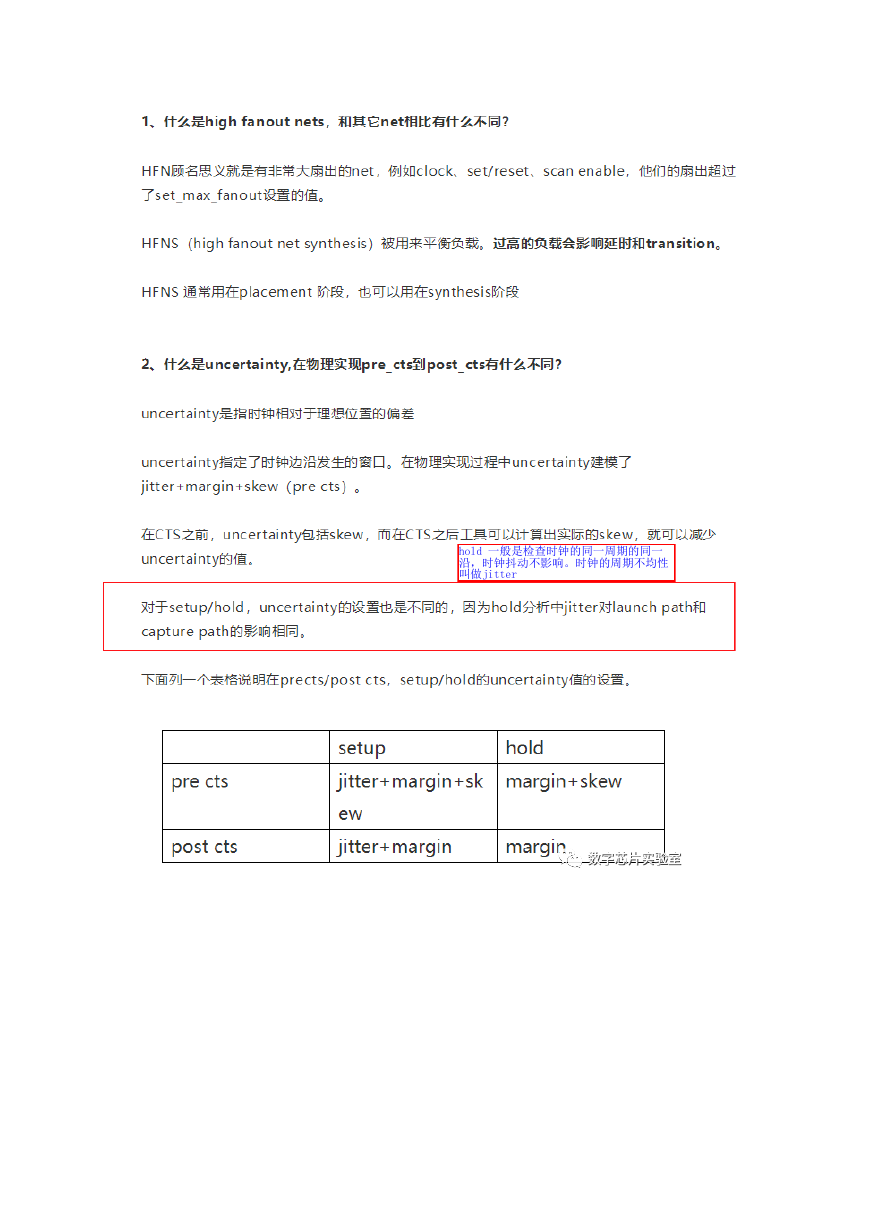

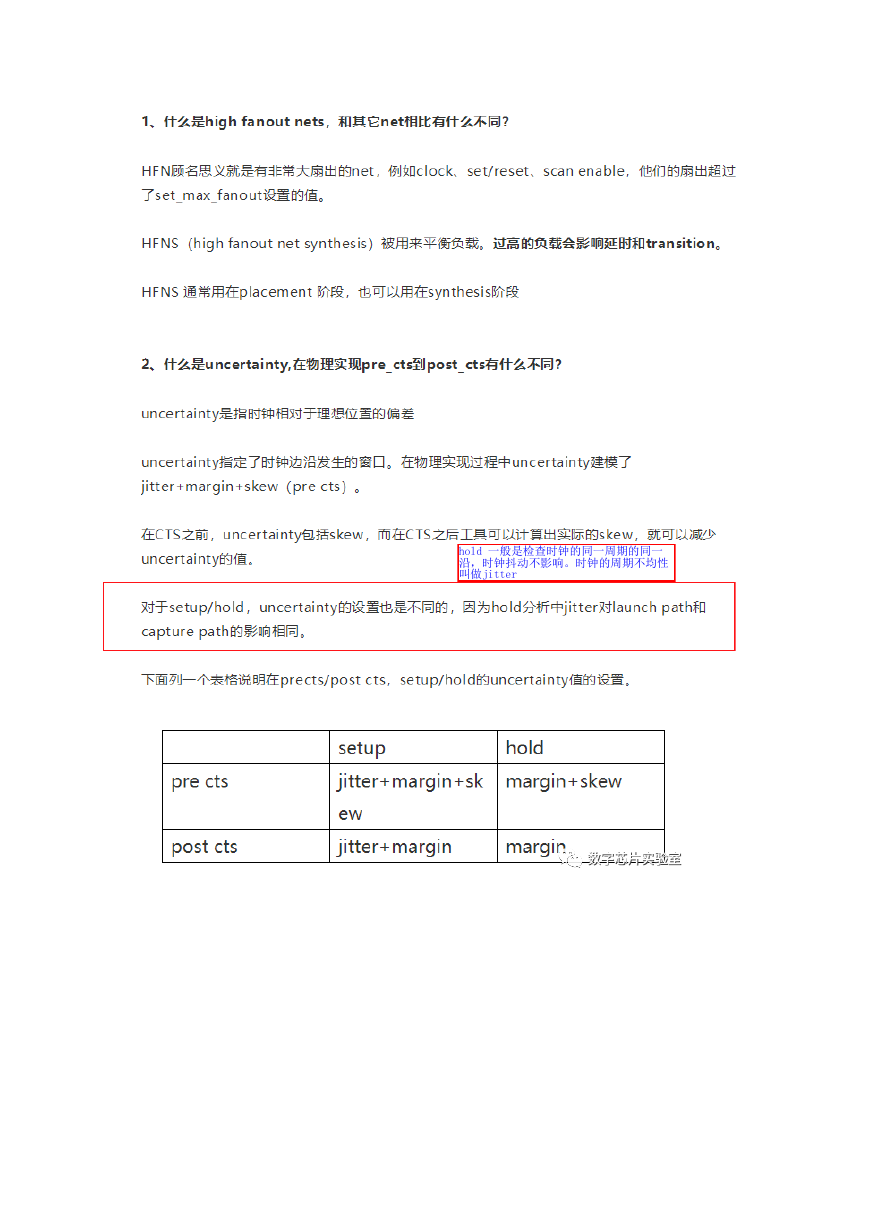

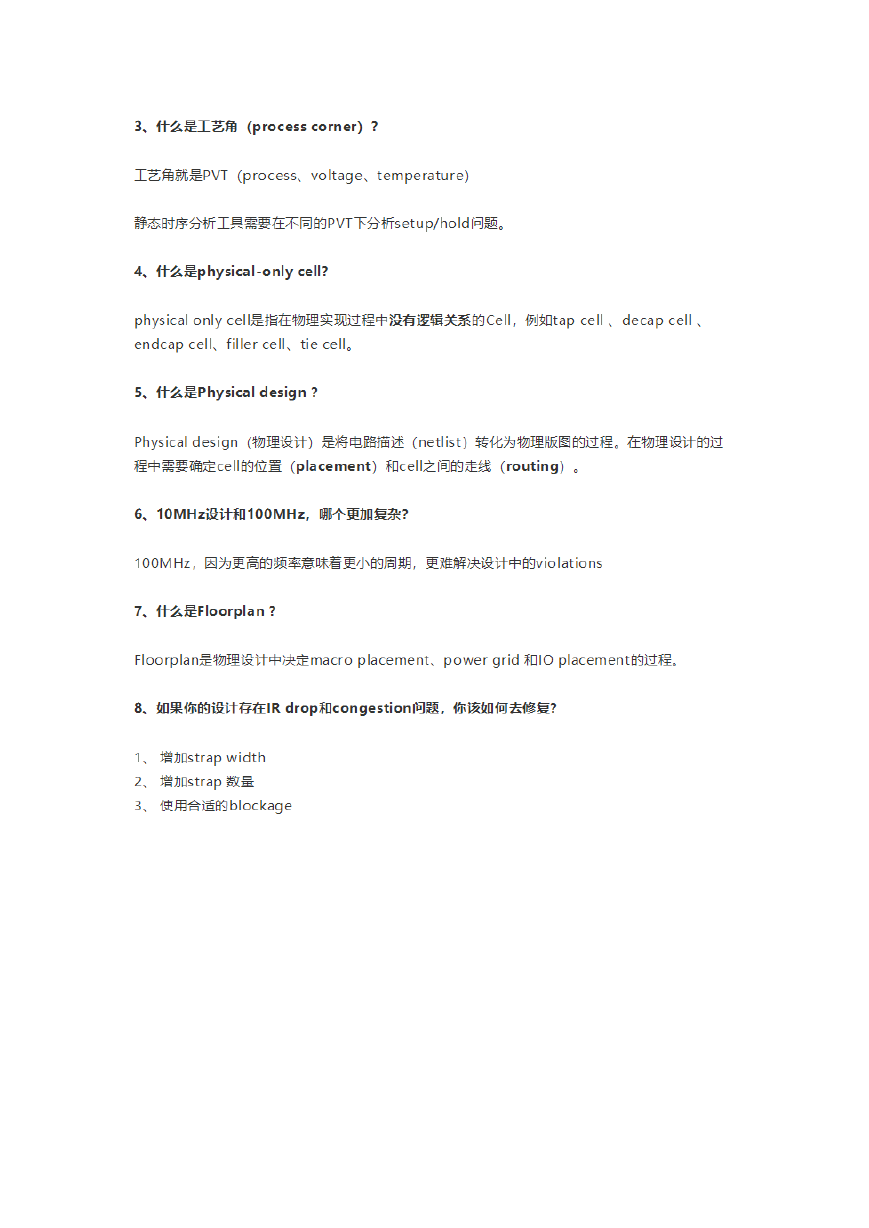

2、uncertainty

3、process corner

4、physical-only cell

5、physical design

6、10MHz和100MHz

7、Floorplan

8、IR drop

9、Tie cell

10、CTS前的检查

11、power gating cells

12、MCMM

13、virtual clock

14、EM

15、zero skew

16、cts之后

17、综合

18、7层金属哪层走时钟

19、天线效应

20、cloning和buffering

21 NAND和NOR

22、LVS定义

23、shielding

24、latch-up效应

25、isolaton cell

26、retention flop

27、CTS做什么

28、CTS目标

29、CTS的影响

30、tap cell等的作用

32、hard macro定义

33、soft macro

34、CTO定义

35、clock buffer

36、为什么在CTS之前解决setup,之后解决hold

37、global routing

38、detailed routing

39、cross talk的定义

40、线负载模型定义

41、hierarchical design和flat design

42、IR drop怎么解

43、body effect

44、glitch

45、SOI工艺

46、macro placement

47、pd阶段的检查

48、Halo和blockage的区别

49、NDR rules

50、blockage的类型

52、修congestion

53、PV包括

54、同时修复setup和hold

55、避免cross-talk

56、DRC类型

57、scan chain reordering

58、floorplan中的row

59、NDR的优点

60、在reg2reg路径上插buffer解决setup

61、partitioning

62、降动态电压

63、double via

64、Metal fill

65、功耗组成

66、placement blockage

67、global routing的类型

68、LVS解决的Vio

69、clock latency

70、修setup和hold

71、floorplan的输入

72、floorplan的输出

73、keep-out margin

74、IR drop

75、HVT和LVT

76、WLM

77、SI

78、负载电容对cell延时的影响

79、物理实现需要的文件

80、PVT对cell延时的影响

81、tech file

82、tlu +

83、.lib

84、.lef

85、cell和net的延时计算

86、sanity check

87、Floorplan的任务

88、模块级和芯片物理级设计有什么区别

89、macro很多如何摆放

90、初始利用率太高怎么办

100、power routing

101、power routing用哪些金属

102、PG ring PG stripe PG rail

103、IR drop的定义

104、时序路径分类

105、End Cap Cell

106、Tap cell

107、EDA在placement阶段做什么

108、.def文件

109、9T和12T

110、NLDM和CCS

111、低功耗设计方法

113、修EM

114、SOI工艺

115、placement后check什么

116、placement后修setup

117、follow pins

118、timing borrow

119、逻辑重组

120、coarse placement和legalization

121、MMMC

122、级联buffer驱动

123、插buffer修setup应该放在start point还是end point

124、标准单元高度是M2 pitch整数倍

125、多电压技术

126、placeopt阶段工具优化技术

127、WLM

128、cell density和pin density

129、blockage

130、HVT、LVT、SVT

131、SDC

132、false path

136、arrival time、required time和slack

143、clock latency和skew

149、clock gating

150、OCV的定义

153、CRPR

154、recovery time和removal time

157、多周期路径

158、scan reorder

160、逻辑DRC

161、cloning和buffering

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc