器的醇骥窭现

周类东南大学移动通信国家重点实验室

确_『B

参

1弓l言

匹配滤波器的提出愁有六十多年的历史,其具

有的许多优异性能健其谯信学检测、时延估计中获

得了广泛的应用。践配滤波器具有大的时间带宽积

TW;》I,j袁使樽它谯当今藏符的玛分多蛙遴信系统

中受嚣j了极大的重享见,不仅{乍为快速糖获鞫RAKE

接收等传统技术的城想方案。在多用户检测、智能

哭线等方面也都能艘挥其优势。鹦一方面,大的时

间带宽积却给畦配滤缝器的实现带来了困难。文献

【l】说明了滤波器的复杂度,即滤波器的阶数与时

间带宽积成正比。因此匹配滤波嚣的实现常常是复

杂而叉昂贵的。直到声袭面披延避线耥大婉模撰成

电路工艺抟发璇,芽较好地解决了这个阉磁。

袭奎斯特抽样定理为数字信号处理奠定了理论

基础。随着集成电路技术的发展,匹荫己滤波器也越

来越多地采用数字技术实现。文献[101指出,在

离鞒盘礤声下,当输人信曝比反《l,辕出信啭比

惑》l肘,简单的1比特量化非相干数字匹配滤波

器的输出信噪比与非相干平方律模拟匹配滤波嚣的

输出信噪比之间有如下关系,风n#(2所)Po.。Ⅷ,即

约有2dB的性能损失。然磊,数字滤波器的{芄势仍

然是十分明显的,相对于模拟滤渡器它不存在圈有

噪声.没有噪声的积累问蹈,同时具有可编程、实

或接序列扩频码分多址通信系统中。接收机必

须首先建立本地扩频序列与接收信号序列的同步。

粥序辫静嗣步遴常分成摊获秘跟踪两个过程。躺步

捕获负责将本地扩频序列与接收序列的相差调蔓整到

~个或几分之一个码片范围内.跟踪则进一步减小

瞄步的误麓,谯之犀可能小。匹配滤波嚣在每个时

闽点上都能输如一个据关毽,是一釉_I起速的相关器

件,因而适合用于码序列的快速捕获。考虑到捕获

时间和硬件规模的折衷,我们常采用串行搜索策

略。文献【11-13】提出了多种基于FPGA宓现的数

字匹配滤波器缝梅。这监实现方法都没有充分利用

现代FPGA芯片中的块存储资源的特点,豳而造成

了硬件资源的浪费。本文提出了数字艇配滤波嚣的

多稻粪现结掏,采增块存绪嚣俸垮存储空褥,在实

现具糖相魍复杂度的滤波器附具有较小的资源占用

糕求。

2匹配滤波器的特性

埘某一波形s(£)殴配的滤波器冲激响应定义

为h(丁,=ks(△一r)。这_里k和△都是任意常数。匹

葺己滤渡器的传递丽数由蘸可表示为;H(汹=kS4

(抽曲#一6。可以看出,除了幅度鞠时延相差一个固

定的常数因子外.匹配滤波器的传递函数仪是匹配

信号频谱的共轭。

现简单和对元器件参数熊化不敏感等优点。

对于一时阙有隈的信号+s 0),0《l《T物理可

万方数据

穆劫通建 2003簟增刊

�

sq)COS(1)of+n∽

——————————————————————————+

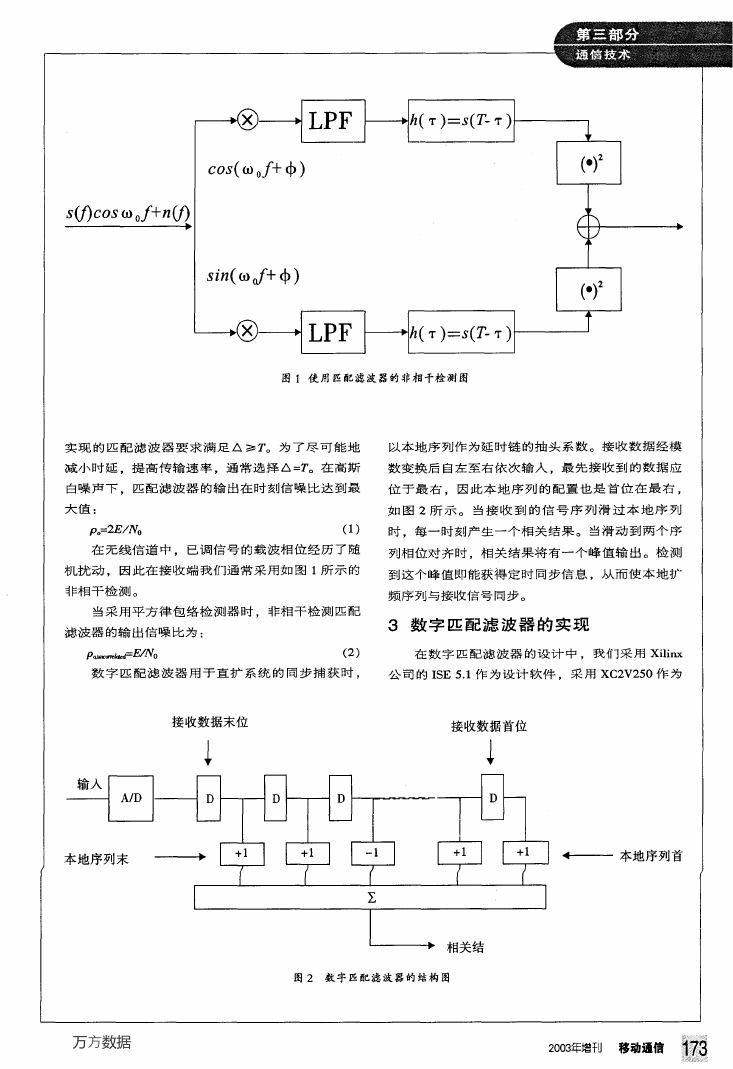

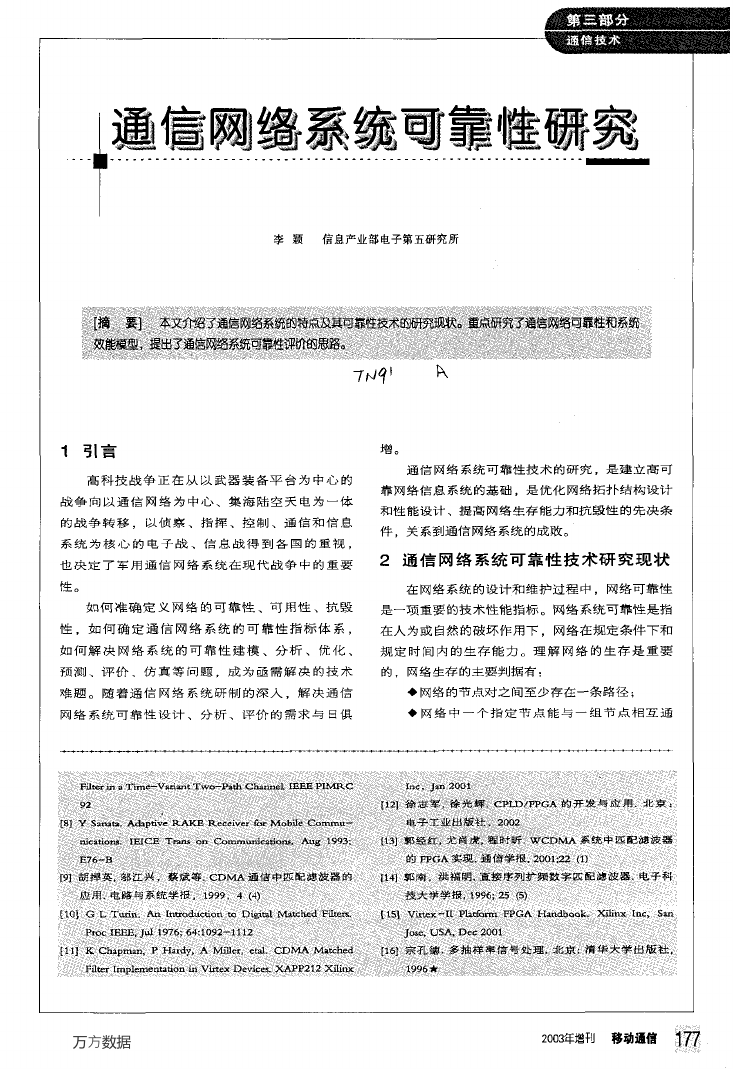

图1使用匹配滤波器的非相干检测图

实现的匹配滤波器要求满足△≥丁。为了尽可能地

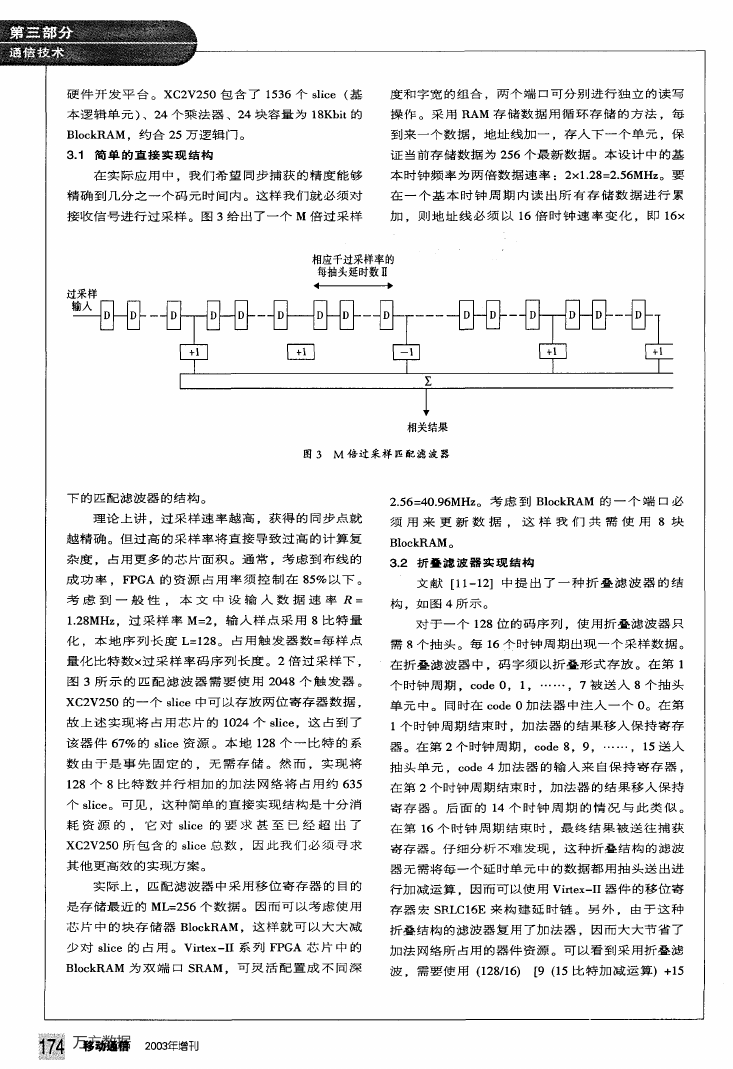

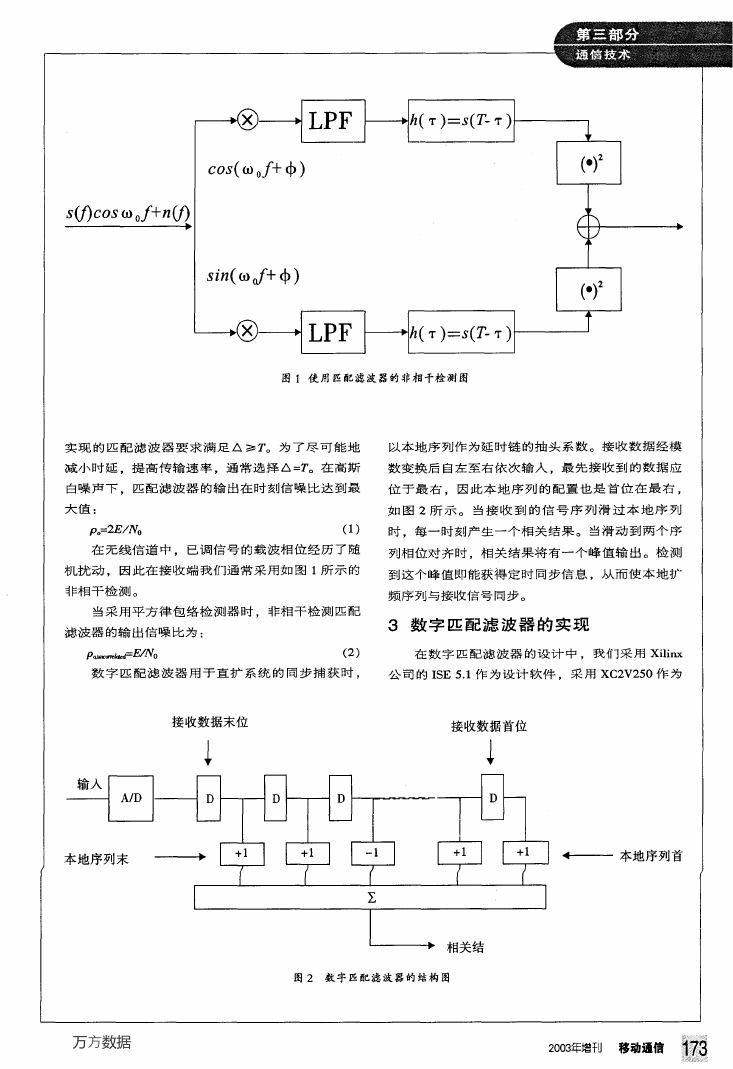

以本地序列作为延rt,,-t链的抽头系数。接收数据经模

减小时延,提高传输速率,通常选择△=咒在高斯

数变换后自左至右依次输入,最先接收到的数据应

白噪声下,匹配滤波器的输出在时刻信噪比达到最

大值:

位于最右,因此本地序列的配置也是首位在最右,

如图2所示。当接收到的信号序列滑过本地序列

po=2E/No

(1)

时,每一时刻产生一个相关结果。当滑动到两个序

在无线信道中。已调信号的载波相位经历了随

列相位对齐时,相关结果将有一个峰值输出。检测

机扰动,因此在接收端我们通常采用如图1所示的

到这个峰值即能获得定时同步信息。从而使本地扩

非卡目干检澳U。

当采用平方律包络检测器时,非相干检测匹配

频序列与接收信号同步。

3数字匹配滤波器的实现

滤波器的输出信噪比为:

风.I;F矾

(2)

在数字匹配滤波器的设计中,我们采用Xilinx

数字匹配滤波器用于直扩系统的同步捕获时,

公司的ISE 5.1作为设计软件,采用XC2V250作为

接收数据末位

接收数据首位

上

图2数字匹配滤波器的结构图

万方数据

2003年增刊 移动通信

�

硬件开发平台。XC2V250包含了1536个slice(基

度和字宽的组合,两个端口可分别进行独立的读写

本逻辑单元)、24个乘法器、24块容量为18Kbit的

操作。采用RAM存储数据用循环存储的方法,每

B10ckRAM,约合25万逻辑门。

3.1简单的直接实现结构

到来一个数据,地址线加一,存入下一个单元,保

证当前存储数据为256个最新数据。本设计中的基

在实际应用中。我们希望同步捕获的精度能够

本时钟频率为两倍数据速率:2x1.28=2.56MHz。要

精确到几分之一个码元时间内。这样我们就必须对

在一个基本时钟周期内读出所有存储数据进行累

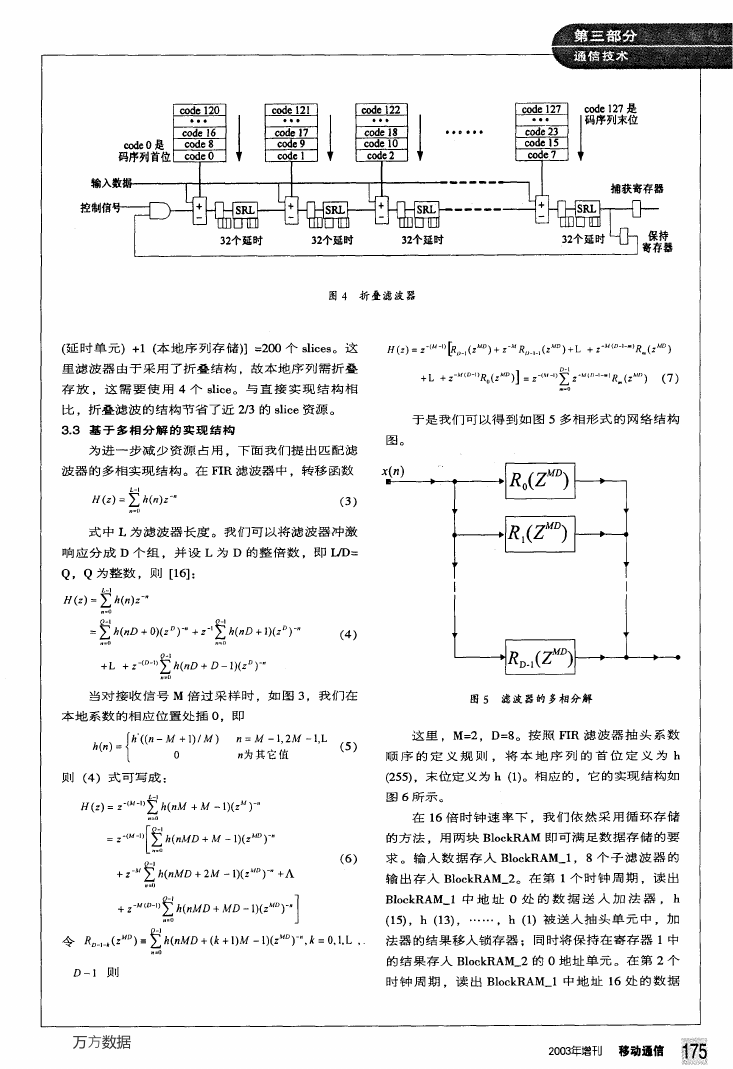

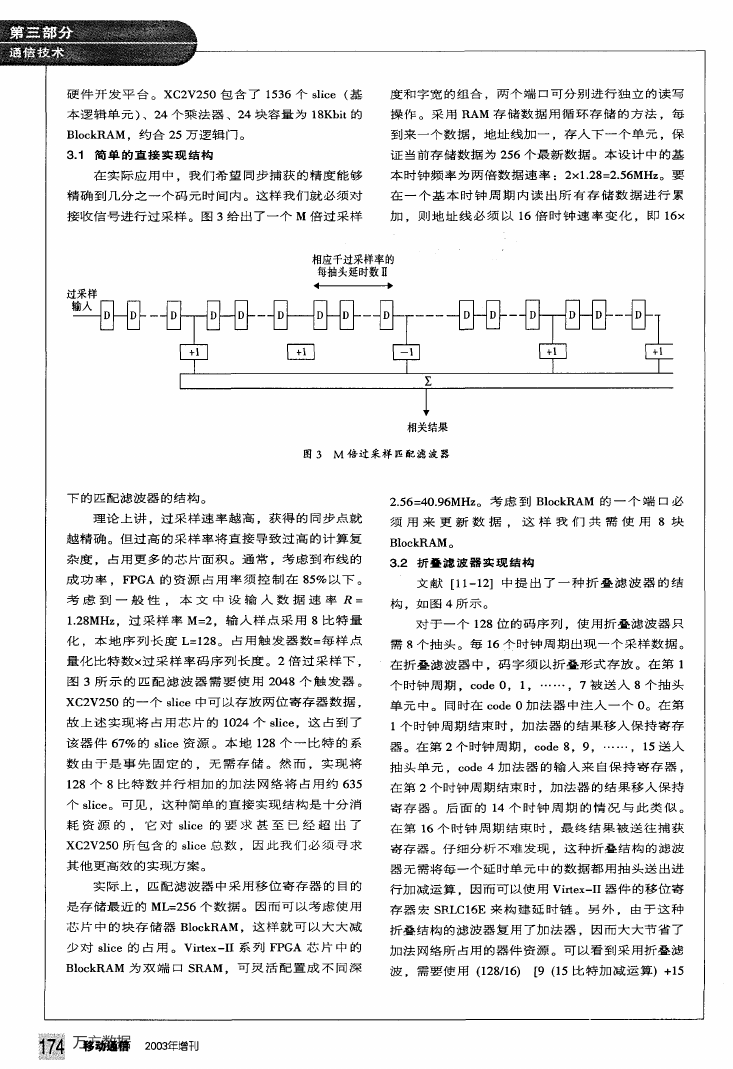

接收信号进行过采样。图3给出了一个M倍过采样

加,则地址线必须以16倍时钟速率变化,即16x

过采样珊D D一

————_{}_一卜-一

■‘一‘-一

相应千过采样率的

每抽头延时数Ⅱ

●h————————————斗

相关结果

图3 M倍过采样匹配滤波器

下的匹配滤波器的结构。

理论上讲,过采样速率越高,获得的同步点就

越精确。但过高的采样率将直接导致过高的计算复

杂度,占用更多的芯片面积。通常,考虑到布线的

成功率。FPGA的资源占用率须控制在85%以下。

2.56=40.96MHz。考虑到BlockRAM的一个端口必

须用来更新数据,这样我们共需使用8块

BloekRAM。

3.2折叠滤波器实现结构

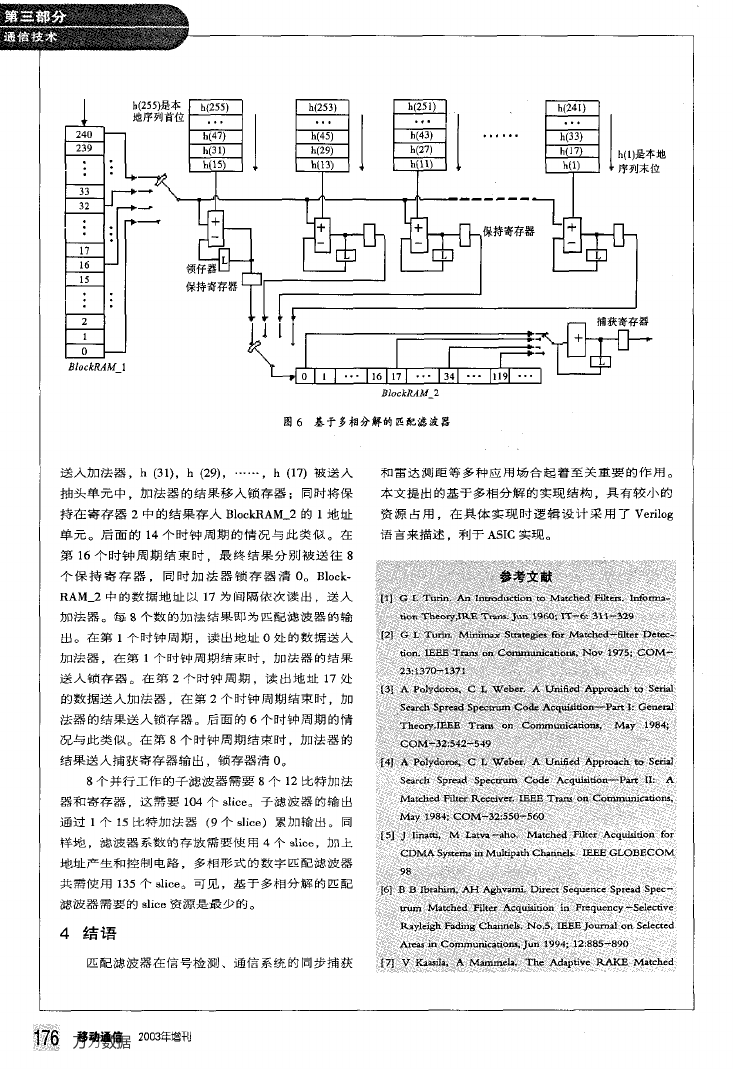

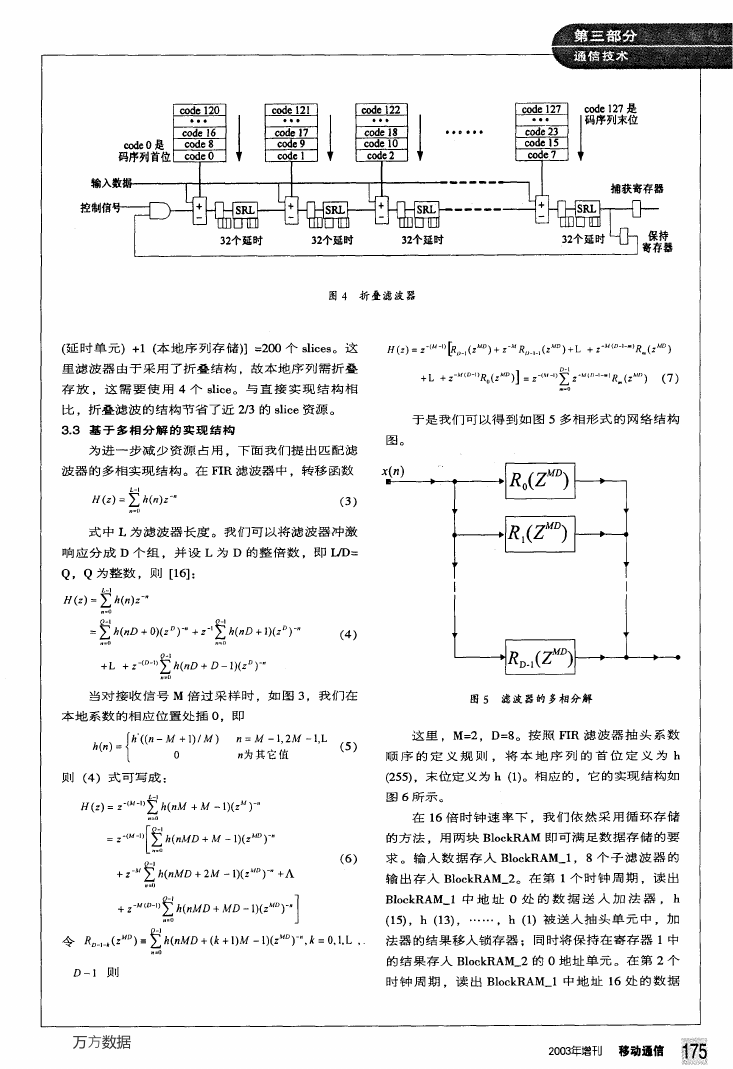

文献[11—12]中提出了一种折叠滤波器的结

考虑到一般性,本文中设输入数据速率R=

构。如图4所示。

1.28MHz,过采样率M=2,输入样点采用8比特量

化,本地序列长度L=128。占用触发器数=每样点

量化比特数×过采样率码序列长度。2倍过采样下,

图3所示的匹配滤波器需要使用2048个触发器。

XC2V250的一个slice中可以存放两位寄存器数据,

故上述实现将占用芯片的1024个slice,这占到了

该器件67%的slice资源。本地128个一比特的系

数由于是事先固定的,无需存储。然而,实现将

128个8比特数并行相加的加法网络将占用约635

个slice。可见,这种简单的直接实现结构是十分消

耗资源的,它对slice的要求甚至已经超出了

XC2V250所包含的slice总数,因此我们必须寻求

其他更高效的实现方案。

实际上,匹配滤波器中采用移位寄存器的目的

是存储最近的ML=256个数据。因而可以考虑使用

芯片中的块存储器BlockRAM,这样就可以大大减

少对slice的占用。Virtex—II系列FPGA芯片中的

BlockRAM为双端口SRAM。可灵活配置成不同深

对于一个128位的码序列.使用折叠滤波器只

需8个抽头。每16个时钟周期出现一个采样数据。

在折叠滤波器中,码字须以折叠形式存放。在第1

个时钟周期,code 0,1,……,7被送入8个抽头

单元中。同时在code 0加法器中注入一个0。在第

1个时钟周期结束时,加法器的结果移入保持寄存

器。在第2个时钟周期,code 8,9,……,15送入

抽头单元,code 4加法器的输入来自保持寄存器,

在第2个时钟周期结束时,加法器的结果移入保持

寄存器。后面的14个时钟周期的情况与此类似。

在第16个时钟周期结束时。最终结果被送往捕获

寄存器。仔细分析不难发现,这种折叠结构的滤波

器无需将每一个延时单元中的数据都用抽头送出进

行加减运算。因而可以使用Virtex—II器件的移位寄

存器宏SB.LCl6E来构建延时链。另外,由于这种

折叠结构的滤波器复用了加法器,因而大大节省了

加法网络所占用的器件资源。可以看到采用折叠滤

波,需要使用(128/16)[9(15比特加减运算)+15

万方数据

移动通信 2003年增刊

�

输入

控制信

图4折叠滤波器

(延时单元)+1(本地序列存储)】=200个slices。这

H(z)=:一(”圳k。,(=”)+z“Ro-H(:”)+L+:一“‘“…R(z”)

里滤波器由于采用了折叠结构,故本地序列需折叠

存放,这需要使用4个slice。与直接实现结构相

比,折叠滤波的结构节省了近2/3的slice资源。

3.3基于多相分解的实现结构

为进一步减少资源占用,下面我们提出匹配滤

波器的多相实现结构。在FIR滤波器中,转移函数

Jv(z)=∑h(n)z”

(3)

式中L为滤波器长度。我们可以将滤波器冲激

响应分成D个组。并设L为D的整倍数,即加=

Q,Q为整数,则[161:

JV(z)=∑h(n)z“

+L+:一c一,Ro(z^。)】::”一’∑D-t zwt—w尺,(:一)(7)

于是我们可以得到如图5多相形式的网络结构

图。

一逊她;l

臣圜

一

一j

p—I

Q—I

=艺h(nD+o)(=。)”+:“∑h(nD+1)(ZD)”

(4)

+L+Z-(D-I)∑h(nD+D一1)(z。)”

当对接收信号M倍过采样时,如图3,我们在

图5滤波器的多相分解

本地系数的相应位置处插0,即

^(")={^。(‘力一M。+1’7M’

:为=M其它-I值,2M一1’L

(5)

这里,M=2,D=8。按照FIR滤波器抽头系数

顺序的定义规则,将本地序列的首位定义为h

则(4)式可写成:

日(z)=z-(M-D∑h(nM+M—1)(z“)”

=Z-(M-I)l∑h(nMD+M一1)(z”)”

。.,

+z“∑h(nMD+2M—1)(z”)“+A

+z一”‘。。’∑h(nMD+MD一1)(z”。)一”l

(255),末位定义为h(1)。相应的,它的实现结构如

图6所示。

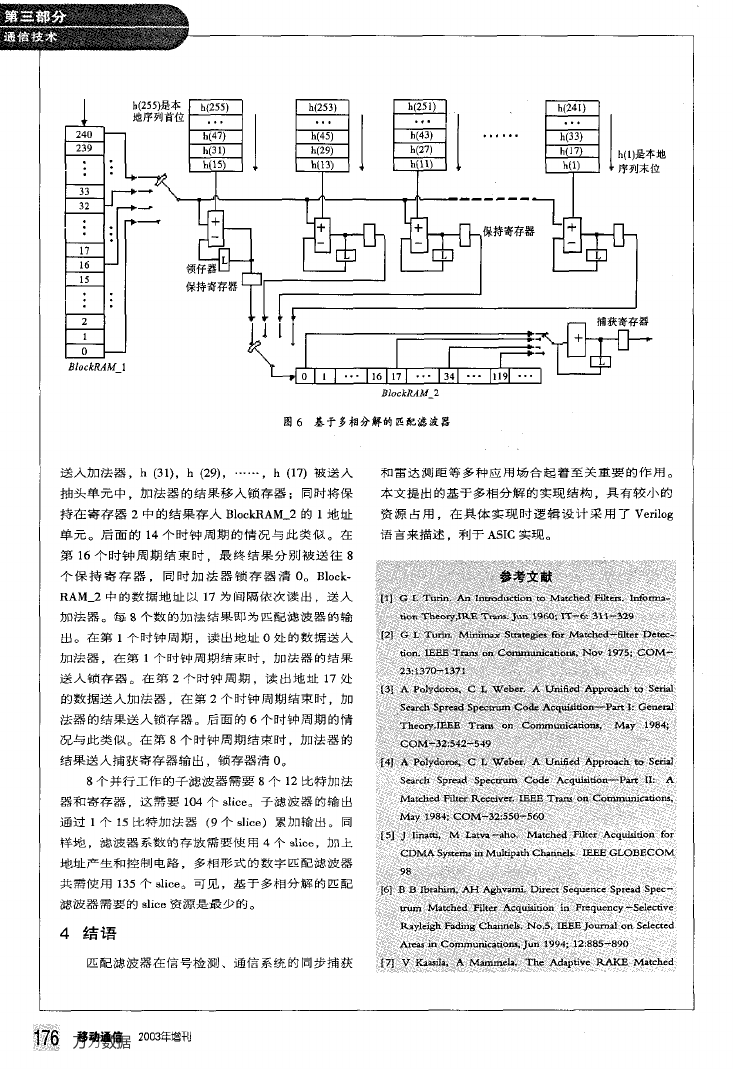

在16倍时钟速率下,我们依然采用循环存储

的方法。用两块BlockRAM即可满足数据存储的要

(6)

求。输入数据存入BlockRAM一1,8个子滤波器的

输出存入BlockRAM_2。在第1个时钟周期,读出

BlockRAM一1中地址0处的数据送入加法器,h

(15),h(13),……,h(1)被送入抽头单元中,加

令Ro-I-,(:”)=∑h(nMD+(≈+I)M—1)(z”)~,k=o,1,L,

法器的结果移入锁存器;同时将保持在寄存器1中

D一1贝U

万方数据

的结果存入BlockRAM_2的0地址单元。在第2个

时钟周期。读出BlockRAM一1中地址16处的数据

2003年增刊 移动通信

�

霪㈠l剐嚣甄酗娜黼栅妒

i 』

17

16

●。}}

…,·1.1…l117…ll3L… 11k…1斗铲

门捕获至存

——i—

240

239

I:

‘

33

32

15

i

2

l

0

Blockm

[五

Bloc☆见dⅣ2

图6基于多相分解的匹配滤波器

送人加法器,h(31),h(29),…一,h(17)被送入

抽头单元中,加法器的结果移入锁存器;同时将保

和雷达测距等多种应用场合起着至关重要的作用。

本文提出的基于多相分解的实现结构,具有较小的

资源占用,在具体实现时逻辑设计采用了Verilog

语言来描述,利于ASIC实现。

持在寄存器2中的结果存人BlockRAM一2的1地址

单元。后面的14个时钟周期的情况与此类似。在

第16个时钟周期结束时.最终结果分别被送往8

个保持寄存器.同时加法器锁存器清0。Block.

RAM一2中的数据地址以17为间隔依次读出,送人

加法器。每8个数的加法结果即为匹配滤波器的输

出。在第1个时钟周期.读出地址0处的数据送人

加法器,在第1个时钟周期结束时,加法器的结果

送人锁存器。在第2个时钟周期,读出地址17处

的数据送人加法器,在第2个时钟周期结束时,加

法器的结果送人锁存器。后面的6个时钟周期的情

况与此类似。在第8个时钟周期结束时,加法器的

结果送人捕获寄存器输出.锁存器清0。

8个并行工作的子滤波器需要8个12比特加法

器和寄存器.这需要104个slice。子滤波器的输出

通过1个15比特加法器(9个slice)累加输出。同

样地,滤波器系数的存放需要使用4个slice,加上

地址产生和控制电路,多相形式的数字匹配滤波器

共需使用135个Mice。可见,基于多相分解的匹配

滤波器需要的slice资源是最少的。

4结语

匹配滤波器在信号检测、通信系统的同步捕获

移动通信 2003年增刊

万方数据

�

逦~

鹰~

网缀蒸绫可曩憧礴巍

李颖 信息产业部电子第五研究所

1引言

增。

高科技战争正在从以武器装备平台为中心的

战争向以通信网络为中心、集海陆空天电为一体

的战争转移.以侦察、指挥、控制、通信和信息

系统为核心的电子战、信息战得到各国的重视,

也决定了军用通信网络系统在现代战争中的重要

性。

通信网络系统可靠性技术的研究,是建立高可

靠网络信息系统的基础,是优化网络拓扑结构设计

和性能设计、提高网络生存能力和抗毁性的先决条

件.关系到通信网络系统的成败。

2通信网络系统可靠性技术研究现状

在网络系统的设计和维护过程中。网络可靠性

如何准确定义网络的可靠性、可用性、抗毁

是一项重要的技术性能指标。网络系统可靠性是指

性.如何确定通信网络系统的可靠性指标体系,

在人为或自然的破坏作用下.网络在规定条件下和

如何解决网络系统的可靠性建模、分析、优化、

规定时间内的生存能力。理解网络的生存是重要

预测、评价、仿真等问题,成为亟需解决的技术

的,网络生存的主要判据有:

难题。随着通信网络系统研制的深人.解决通信

◆网络的节点对之间至少存在一条路径;

网络系统可靠性设计、分析、评价的需求与日俱

◆网络中一个指定节点能与一组节点相互通

tii幕ab靠t通t霭、雠毒q∞it6t疆荫西÷P谳e越电谶强鞋岛i篝驰以9@。%*目%誊^n毒豫X鼬2∞警。。4蟊。自P$窜0§。。j■n‰囊曩^E|∞E|

鬣强雠镰÷琶甓毪毫疆曩毯≯蟊曩∞t审骥强藿羲i强|缓·翦强镶曩羹旗强壤弹lX蕾罐糍氆甏i襟警啻麟嚣∞瓣e醚馘赫摭_I毫髓?鼹l龇蘸i

母筏壤警舔罐t辩鞲誊啭誉辑弛嗨瓣t垮舔磷《辑醚曦赣晒慨≮蘸魏鬻螽毪琵l麟罨黧鬻赣鞲麓睡l韵嗡l氇镶-毪薯簿尊j孽曩囊l。曩_·

豫弦垃|.矗链《l譬酿疆j蠢镒鼙舀醚镪岖确诲强猫毫鹾毫髓罐豳§矗毪嚆豫氆瓤l冁镬缝t甓赣蠛%器濑蹶薯黼镪箍KK誉臻粤碡配礴璇器

臻强糍i毪蕊|嚣麓譬蠹誉蠹强t誊《警壤懿燕鬣琵8琵魏簪毫镬·镶强强蕾i:。强整曩镪铺§懿÷赣壤l每钮镱警穰誊蛳鸹斡≈善·t睡ll譬曩i蠢强t。曩

娥l穗鞲蒜t镪簿麟毪饕豫奄|镑’峨酶礴鞲尊薅爵诲强器觏爨t|穗瓴都裁。攀摄黪潭鬻蹙熟碜鞣麟甍霉鼹诲激器l警鼍璐

。i2 7赶髓l¨龟_姆舄:豫镪攀壤瓤∞嚼誊酚断·虽氇强%强E%t甚i曩琏毫簪糍嫦攀摄辩99铸鹞鹎毪E峨氆臻to蟊j氆E j曩

|蛾{3℃矗谳。}虹蜥m诗沁“·哂D蝴M鞠:咄a甚缸酶。薯o|x蛾璃斌娃每强?碍j蹲油_I=L霭聱G娃H耥娟峨甚酗域,s1轧

::

1976 64.'109

唾诺毽,氆。诲溢i鼋鼍填b畿蠢鞋颈每÷雅t试。嘞壤蜂颡舔辫舔蛰旗褥襄戳镰曩羲鹣撩孽镰轰磷零t鹳藏棼鹋譬嚣甓避媾攀t

Filter

ces.XAPP212

罐强o

万方数据

2003年增刊 移动通信

�

匹配滤波器的FPGA实现

作者:

周奕

作者单位:

刊名:

东南大学移动通信国家重点实验室

移动通信

英文刊名:

MOBILE COMMUNICATIONS

2003,27(z2)

年,卷(期):

参考文献(16条)

1.G L Turin An Introduction to Matched Filters[外文期刊] 1960

2.G L Turin Minimax Strategies for Matched-filter Detection[外文期刊] 1975

3.A Polydoros;C L Weber A Unified Approach to Serial Search Spread Spectrum Code Acquisition-Part

Ⅰ: General Theory[外文期刊] 1984

4.A Polydoros;C L Weber A Unified Approach to Serial Search Spread Spectrum Code Acquisition-Part

Ⅱ: A Matched Filter R eceiver 1984

5.J linatti;M Latva-aho Matched Filter Acquisition for CDMA Systems in Multipath Channels

6.B B Ibrahim;AH Aghvami Direct Sequence Spread Spectrum Matched Filter Acquisition m Frequency-

Selective R ayleigh Fading Channels. No.5[外文期刊] 1994(5)

7.V Kaasila;A Mammela The Adaptive RAKE Matched Filter in a Time-Variant Two-Path Channel

8.Y Sanata Adaptive RAKE Peceiver for Mobile Communications 1993

9.胡捍英;邬江兴;蔡斌 CDMA通信中匹配滤波器的应用[期刊论文]-电路与系统学报 1999(04)

10.G L Turin An Introduction to Digital Matched Filters[外文期刊] 1976

11.K Chapman P Hardy;A Miller;etal CDMA Matched Filter Implementation in Virtex Devices 2001

12.徐志军;徐光辉 CPLD/FPGA的开发与应用 2002

13.郭经红;尤肖虎;程时昕 WCDMA系统中匹配滤波器的FPGA实现[期刊论文]-通信学报 2001(01)

14.郭南 洪福明直接序列扩频数字匹配滤波器 1996(05)

15.Virtex-Ⅱ Platform FPGA Handbook. Xilinx Inc. San Jose. USA 2001

16.宗孔德 多抽样率信号处理 1996

本文读者也读过(10条)

1. 余建宇.Yu Jianyu 基于FPGA的扩频接收机中数字匹配滤波器的设计[期刊论文]-火控雷达技术2009,38(3)

2. 帅涛.陈晓挺.刘会杰.梁旭文.SHUAI Tao.CHEN Xiao-ting.LIU Hui-jie.LIANG Xu-wen 一种用于PN码捕获的低

硬件消耗匹配滤波器设计[期刊论文]-上海航天2008,25(4)

3. 展放.张君昌 数字匹配滤波器在直序扩频快速捕获中的应用[期刊论文]-航空电子技术2003,34(3)

4. 周奕.ZHOU Yi 匹配滤波器的多相实现[期刊论文]-电路与系统学报2005,10(3)

5. 王俊花.崔永.WANG Jun-hua.CUI Yong 一种数字匹配滤波器的设计[期刊论文]-自动化技术与应用2009,28(4)

6. 何在民.胡永辉.魏敬法.蔡成林.武建锋.HE Zai-min.HU Yong-hui.WEI Jing-fa.CAI Cheng-lin.WU Jian-feng

基于FPGA的数字匹配滤波器的实现[期刊论文]-时间频率学报2008,31(2)

7. 陈洁媛.陈忠辉.Xu Yiwen.Chen Jieyuan.Chen Zhonghui.Xu Yiwen 数字匹配滤波器的改进及在伪码捕获中的应

用[期刊论文]-数字技术与应用2011(4)

8. 周平.薛敏彪.胡永红.陈铭 扩频数字接收机匹配滤波器的设计与实现[期刊论文]-微电子学与计算机2004,21(9)

9. 王真 扩频接收机中数字匹配滤波器的FPGA实现[期刊论文]-广东通信技术2008,28(6)

10. 李健.常青.毕存磊.金科 扩频接收机匹配滤波器的设计及其FPGA实现[会议论文]-

�

本文链接:http://d.wanfangdata.com.cn/Periodical_ydtx2003z2055.aspx

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc