数据传输中耦合电容的选择与应用

某次对于 SATA 数据传输耦合电容大小感兴趣,于是查找了一些文献对此进行

学习总结,AC 耦合电容在很多高速数字信号传输方面都有使用,网卡、SATA 以及

codec 甚至在我们并不特别熟悉的视频传输等等这些地方应用比较多,其选择过

大或者过小都会影响数据传输,出现丢包或者传输,或者数据出错的情况,在这个

时候我们需要综合考虑设计理念、成本因素以及品质因素来综合考虑耦合电容的

选择,前提是我们对于各种不同类型电容参数上的区别有一定了解.

1.AC 耦合电容的参数选择

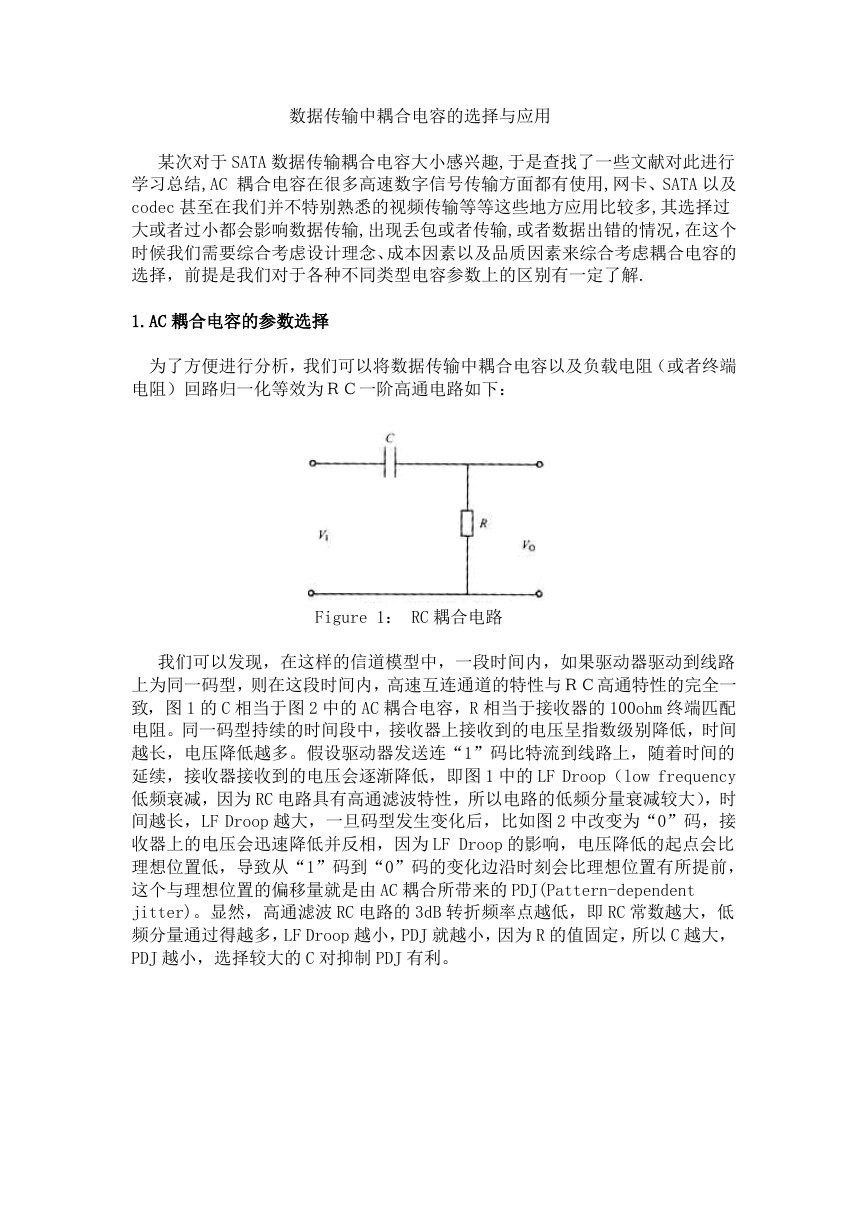

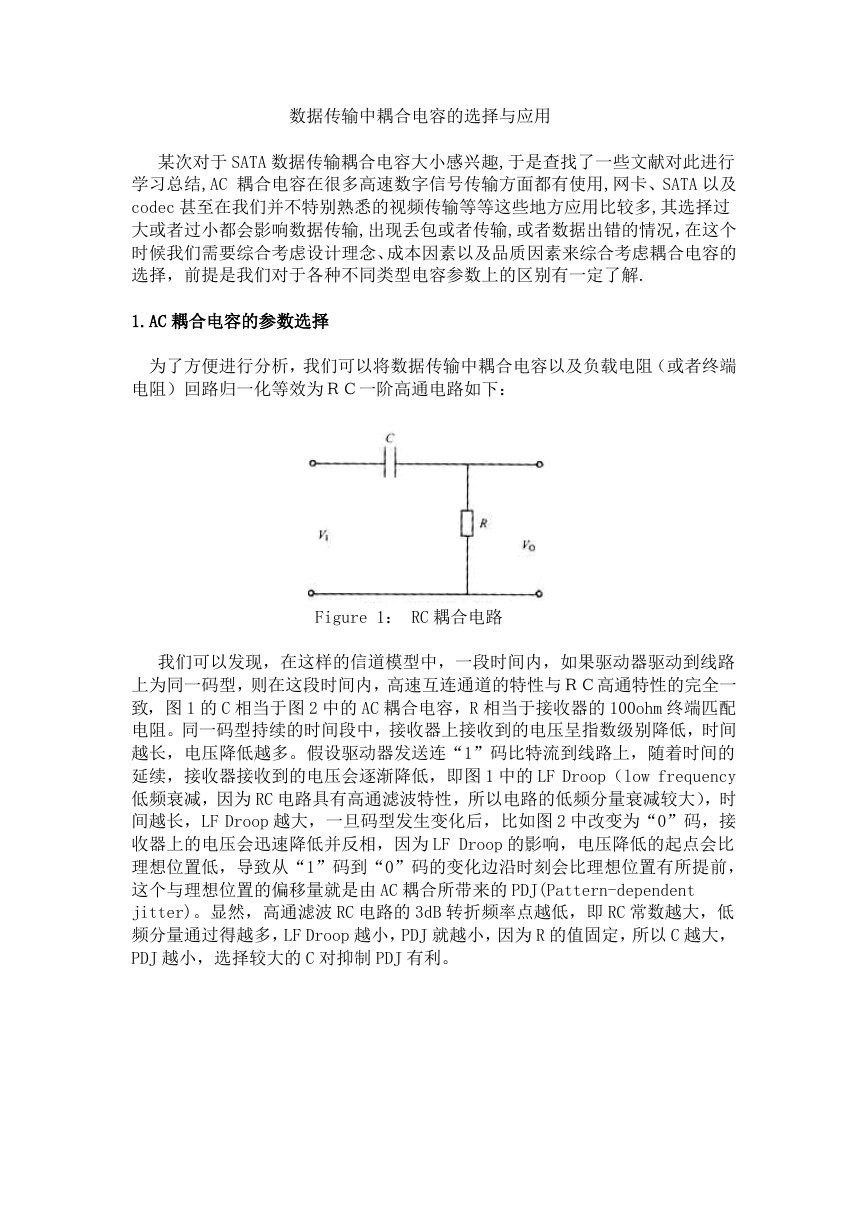

为了方便进行分析,我们可以将数据传输中耦合电容以及负载电阻(或者终端

电阻)回路归一化等效为RC一阶高通电路如下:

Figure 1: RC 耦合电路

我们可以发现,在这样的信道模型中,一段时间内,如果驱动器驱动到线路

上为同一码型,则在这段时间内,高速互连通道的特性与RC高通特性的完全一

致,图 1 的 C 相当于图 2 中的 AC 耦合电容,R 相当于接收器的 100ohm 终端匹配

电阻。同一码型持续的时间段中,接收器上接收到的电压呈指数级别降低,时间

越长,电压降低越多。假设驱动器发送连“1”码比特流到线路上,随着时间的

延续,接收器接收到的电压会逐渐降低,即图 1 中的 LF Droop(low frequency

低频衰减,因为 RC 电路具有高通滤波特性,所以电路的低频分量衰减较大),时

间越长,LF Droop 越大,一旦码型发生变化后,比如图 2 中改变为“0”码,接

收器上的电压会迅速降低并反相,因为 LF Droop 的影响,电压降低的起点会比

理想位置低,导致从“1”码到“0”码的变化边沿时刻会比理想位置有所提前,

这个与理想位置的偏移量就是由 AC 耦合所带来的 PDJ(Pattern-dependent

jitter)。显然,高通滤波 RC 电路的 3dB 转折频率点越低,即 RC 常数越大,低

频分量通过得越多,LF Droop 越小,PDJ 就越小,因为 R 的值固定,所以 C 越大,

PDJ 越小,选择较大的 C 对抑制 PDJ 有利。

�

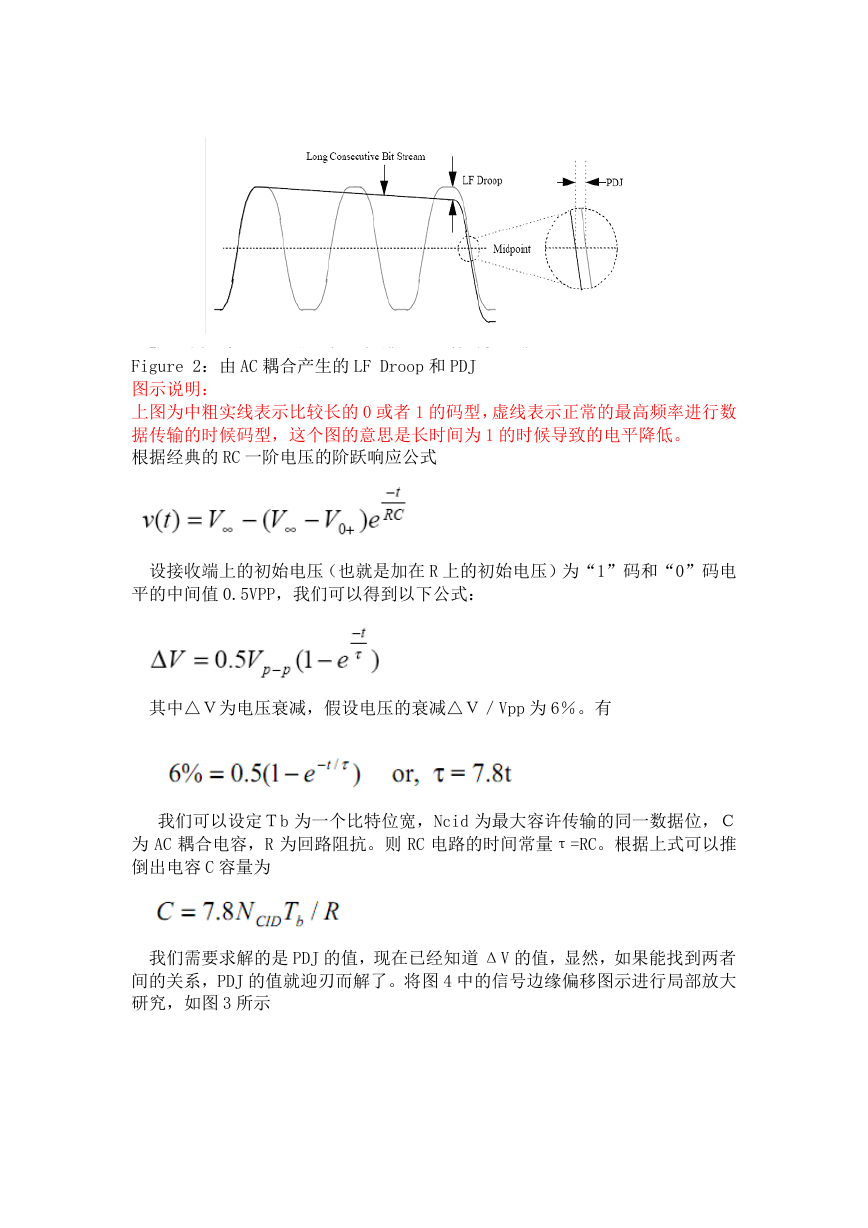

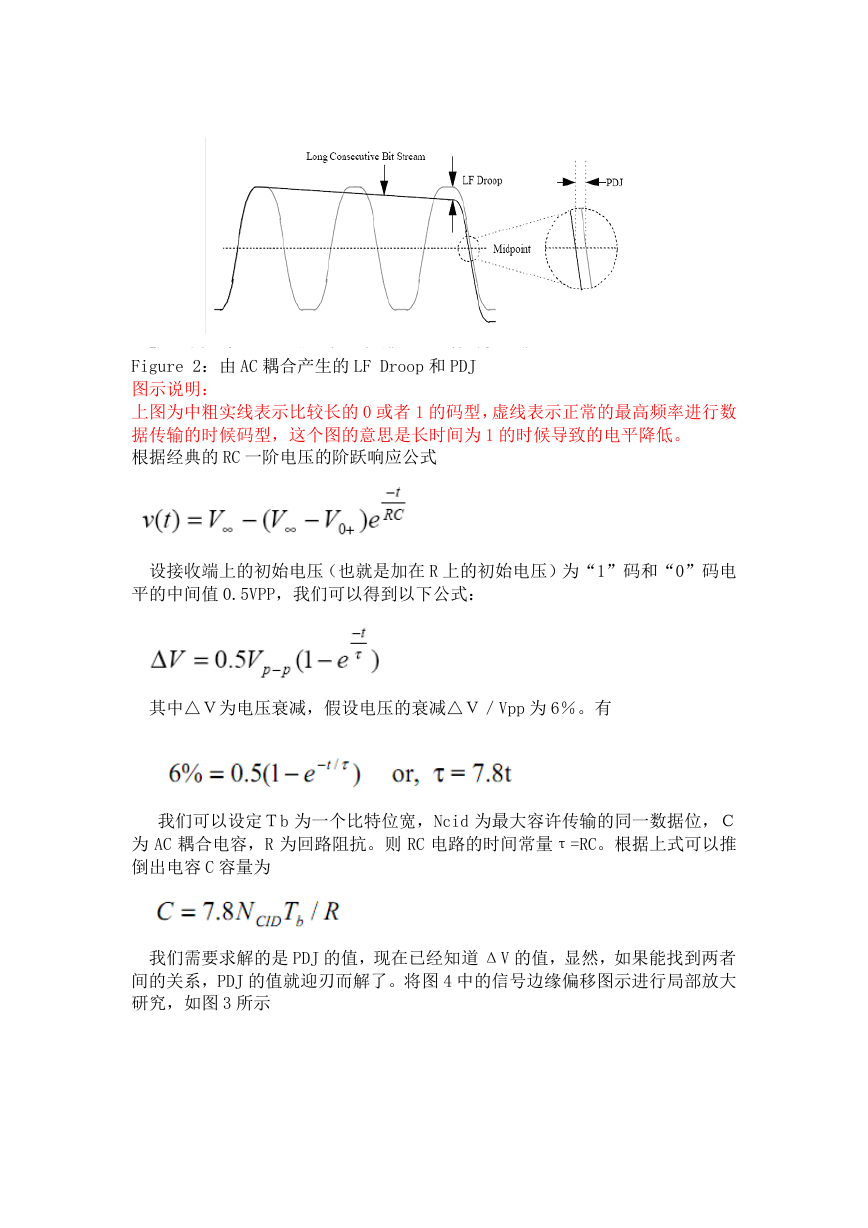

Figure 2:由 AC 耦合产生的 LF Droop 和 PDJ

图示说明:

上图为中粗实线表示比较长的 0 或者 1 的码型,虚线表示正常的最高频率进行数

据传输的时候码型,这个图的意思是长时间为 1 的时候导致的电平降低。

根据经典的 RC 一阶电压的阶跃响应公式

设接收端上的初始电压(也就是加在 R 上的初始电压)为“1”码和“0”码电

平的中间值 0.5VPP,我们可以得到以下公式:

其中△V为电压衰减,假设电压的衰减△V/Vpp 为 6%。有

我们可以设定Tb 为一个比特位宽,Ncid 为最大容许传输的同一数据位,C

为 AC 耦合电容,R 为回路阻抗。则 RC 电路的时间常量τ=RC。根据上式可以推

倒出电容 C 容量为

我们需要求解的是 PDJ 的值,现在已经知道 ΔV 的值,显然,如果能找到两者

间的关系,PDJ 的值就迎刃而解了。将图 4 中的信号边缘偏移图示进行局部放大

研究,如图 3 所示

�

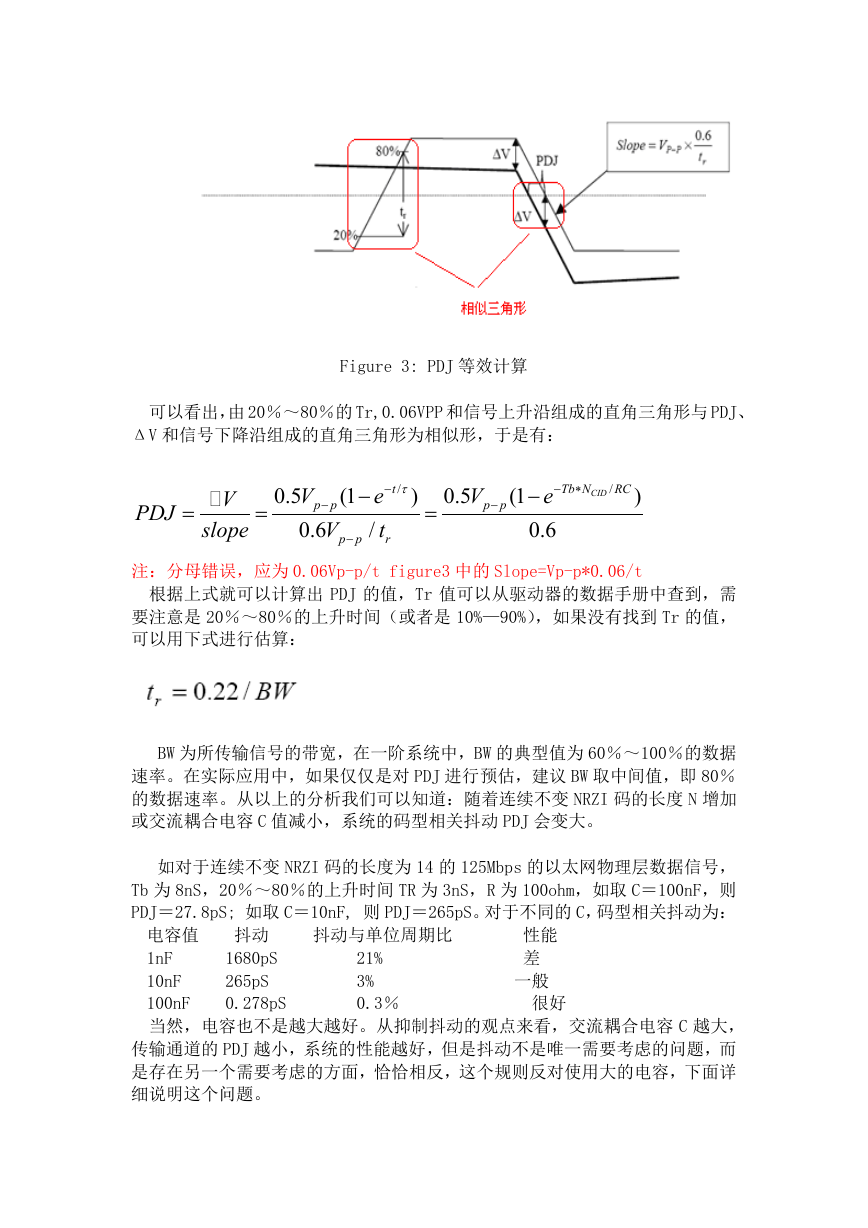

Figure 3: PDJ 等效计算

可以看出,由 20%~80%的 Tr,0.06VPP 和信号上升沿组成的直角三角形与 PDJ、

ΔV 和信号下降沿组成的直角三角形为相似形,于是有:

PDJ

=

V

slope

=

V

0.5

p p

−

V

0.6

(1

p p

−

e

−

t

/

−

r

t

/

τ

)

=

V

0.5

(1

p p

−

−

e

−

0.6

Tb N

∗

CID

/

RC

)

注:分母错误,应为 0.06Vp-p/t figure3 中的 Slope=Vp-p*0.06/t

根据上式就可以计算出 PDJ 的值,Tr 值可以从驱动器的数据手册中查到,需

要注意是 20%~80%的上升时间(或者是 10%—90%),如果没有找到 Tr 的值,

可以用下式进行估算:

BW 为所传输信号的带宽,在一阶系统中,BW 的典型值为 60%~100%的数据

速率。在实际应用中,如果仅仅是对 PDJ 进行预估,建议 BW 取中间值,即 80%

的数据速率。从以上的分析我们可以知道:随着连续不变 NRZI 码的长度 N 增加

或交流耦合电容 C 值减小,系统的码型相关抖动 PDJ 会变大。

如对于连续不变 NRZI 码的长度为 14 的 125Mbps 的以太网物理层数据信号,

Tb 为 8nS,20%~80%的上升时间 TR 为 3nS,R 为 100ohm,如取 C=100nF,则

PDJ=27.8pS; 如取 C=10nF, 则 PDJ=265pS。对于不同的 C,码型相关抖动为:

电容值 抖动 抖动与单位周期比 性能

1nF 1680pS 21% 差

10nF 265pS 3% 一般

100nF 0.278pS 0.3% 很好

当然,电容也不是越大越好。从抑制抖动的观点来看,交流耦合电容 C 越大,

传输通道的 PDJ 越小,系统的性能越好,但是抖动不是唯一需要考虑的问题,而

是存在另一个需要考虑的方面,恰恰相反,这个规则反对使用大的电容,下面详

细说明这个问题。

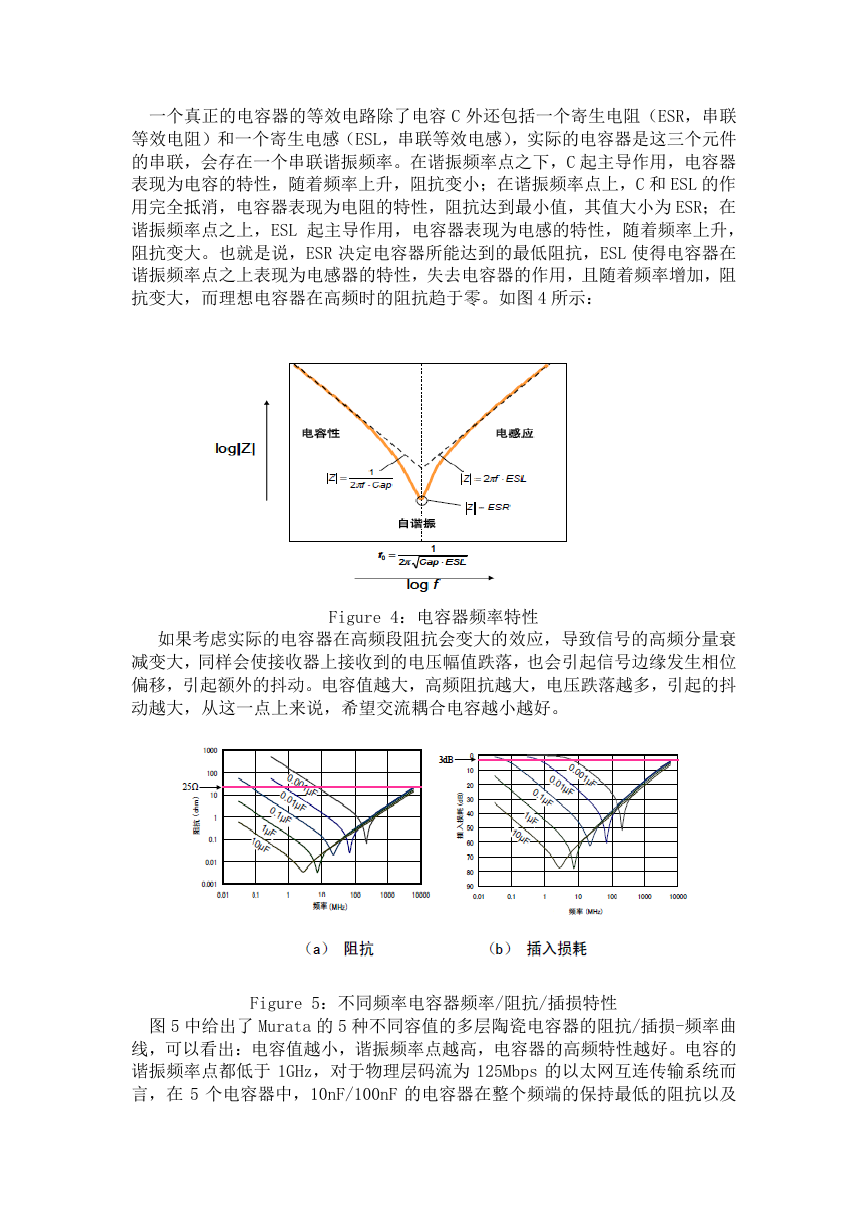

�

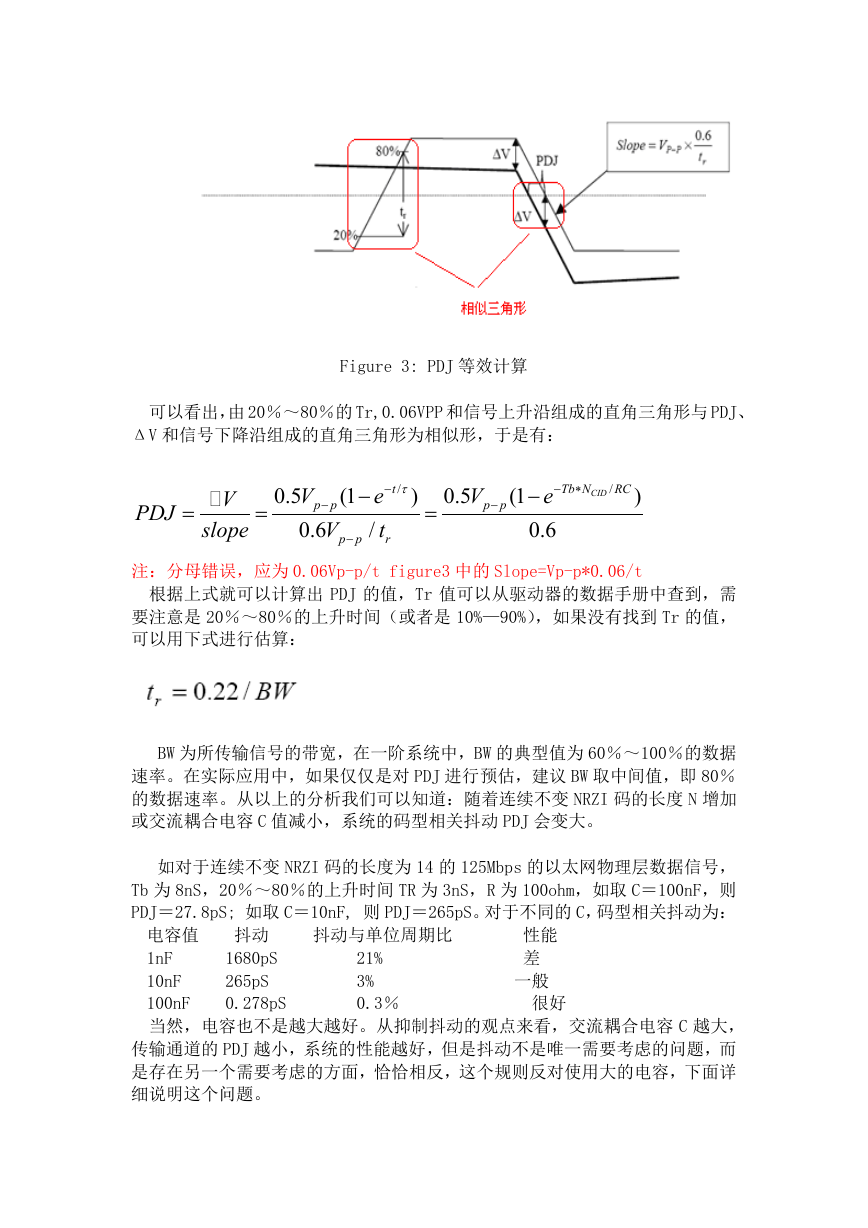

一个真正的电容器的等效电路除了电容 C 外还包括一个寄生电阻(ESR,串联

等效电阻)和一个寄生电感(ESL,串联等效电感),实际的电容器是这三个元件

的串联,会存在一个串联谐振频率。在谐振频率点之下,C 起主导作用,电容器

表现为电容的特性,随着频率上升,阻抗变小;在谐振频率点上,C 和 ESL 的作

用完全抵消,电容器表现为电阻的特性,阻抗达到最小值,其值大小为 ESR;在

谐振频率点之上,ESL 起主导作用,电容器表现为电感的特性,随着频率上升,

阻抗变大。也就是说,ESR 决定电容器所能达到的最低阻抗,ESL 使得电容器在

谐振频率点之上表现为电感器的特性,失去电容器的作用,且随着频率增加,阻

抗变大,而理想电容器在高频时的阻抗趋于零。如图 4 所示:

Figure 4:电容器频率特性

如果考虑实际的电容器在高频段阻抗会变大的效应,导致信号的高频分量衰

减变大,同样会使接收器上接收到的电压幅值跌落,也会引起信号边缘发生相位

偏移,引起额外的抖动。电容值越大,高频阻抗越大,电压跌落越多,引起的抖

动越大,从这一点上来说,希望交流耦合电容越小越好。

Figure 5:不同频率电容器频率/阻抗/插损特性

图 5 中给出了 Murata 的 5 种不同容值的多层陶瓷电容器的阻抗/插损-频率曲

线,可以看出:电容值越小,谐振频率点越高,电容器的高频特性越好。电容的

谐振频率点都低于 1GHz,对于物理层码流为 125Mbps 的以太网互连传输系统而

言,在 5 个电容器中,10nF/100nF 的电容器在整个频端的保持最低的阻抗以及

�

插入损耗,性能最好,低频端的阻抗优于 1nF 和 100pF 的电容器,高频段的阻抗

优于 1uF 的电容器。

尽管一般的多层陶瓷电容器在高数据速率的系统中工作时,对外表现出高达

5~10ohm 的阻抗,但是对于实现交流耦合的功能而言,仍然能工作得足够好,

高频下阻抗增大导致的电压跌落不大(一般<2%),导致的相移也小(一般小于

10º),所以完全没有必要选用特殊的射频电容器,一般的标准多层陶瓷电容器(陶

瓷介质可选 NPO 或 X7R)就能满足要求。

因此,我们在选择交流耦合电容器的时候,即不能单方面从高通滤波特性考虑

选小容量的电容器,也不能单方面从 LF Droop 的角度考虑选大容量的电容器,

应综合考虑电容的高通滤波特性和 LF Droop 影响,选择中间值的电容器,基本

原则如下:

a、电容器带来的码型相关抖动不超过单位周期的 5%;

b、尽量选用小封装的电容器,小封装的高频特性优于大封装的,推荐选用 0402

封装;

c、电容器的阻抗在整个低频段和高频段都能兼顾,有最低的整体表现阻抗,推

荐选用 10nF~100nF 间的电容。

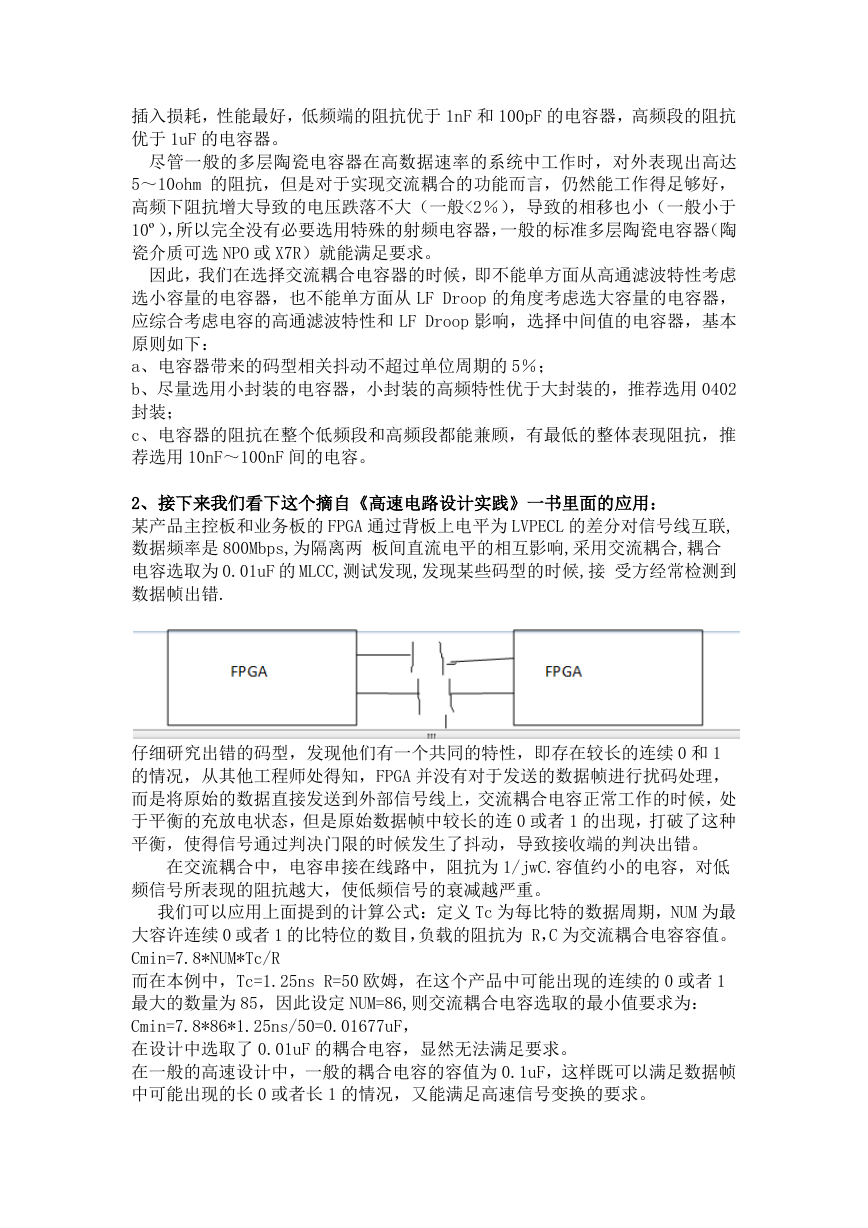

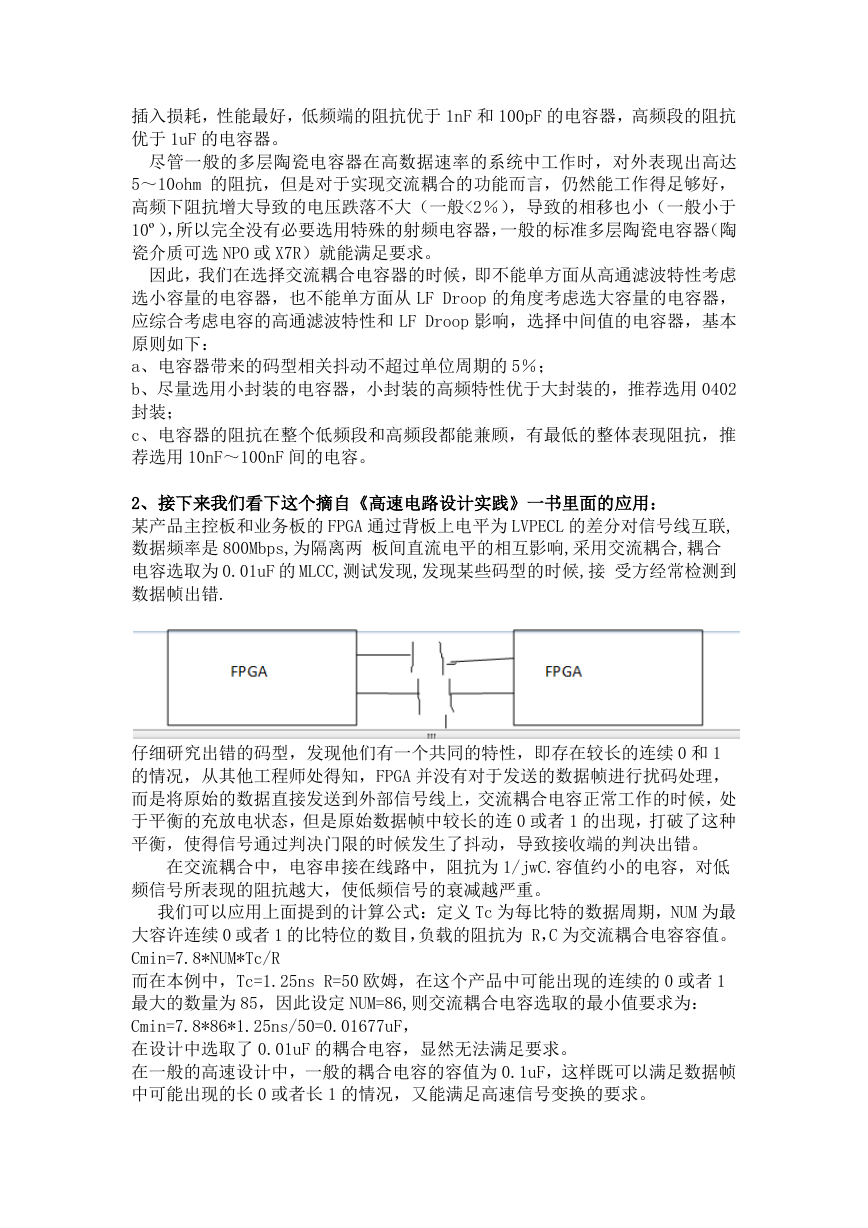

2、接下来我们看下这个摘自《高速电路设计实践》一书里面的应用:

某产品主控板和业务板的 FPGA 通过背板上电平为 LVPECL 的差分对信号线互联,

数据频率是 800Mbps,为隔离两 板间直流电平的相互影响,采用交流耦合,耦合

电容选取为 0.01uF 的 MLCC,测试发现,发现某些码型的时候,接 受方经常检测到

数据帧出错.

仔细研究出错的码型,发现他们有一个共同的特性,即存在较长的连续 0 和 1

的情况,从其他工程师处得知,FPGA 并没有对于发送的数据帧进行扰码处理,

而是将原始的数据直接发送到外部信号线上,交流耦合电容正常工作的时候,处

于平衡的充放电状态,但是原始数据帧中较长的连 0 或者 1 的出现,打破了这种

平衡,使得信号通过判决门限的时候发生了抖动,导致接收端的判决出错。

在交流耦合中,电容串接在线路中,阻抗为 1/jwC.容值约小的电容,对低

频信号所表现的阻抗越大,使低频信号的衰减越严重。

我们可以应用上面提到的计算公式:定义 Tc 为每比特的数据周期,NUM 为最

大容许连续 0 或者 1 的比特位的数目,负载的阻抗为 R,C 为交流耦合电容容值。

Cmin=7.8*NUM*Tc/R

而在本例中,Tc=1.25ns R=50 欧姆,在这个产品中可能出现的连续的 0 或者 1

最大的数量为 85,因此设定 NUM=86,则交流耦合电容选取的最小值要求为:

Cmin=7.8*86*1.25ns/50=0.01677uF,

在设计中选取了 0.01uF 的耦合电容,显然无法满足要求。

在一般的高速设计中,一般的耦合电容的容值为 0.1uF,这样既可以满足数据帧

中可能出现的长 0 或者长 1 的情况,又能满足高速信号变换的要求。

�

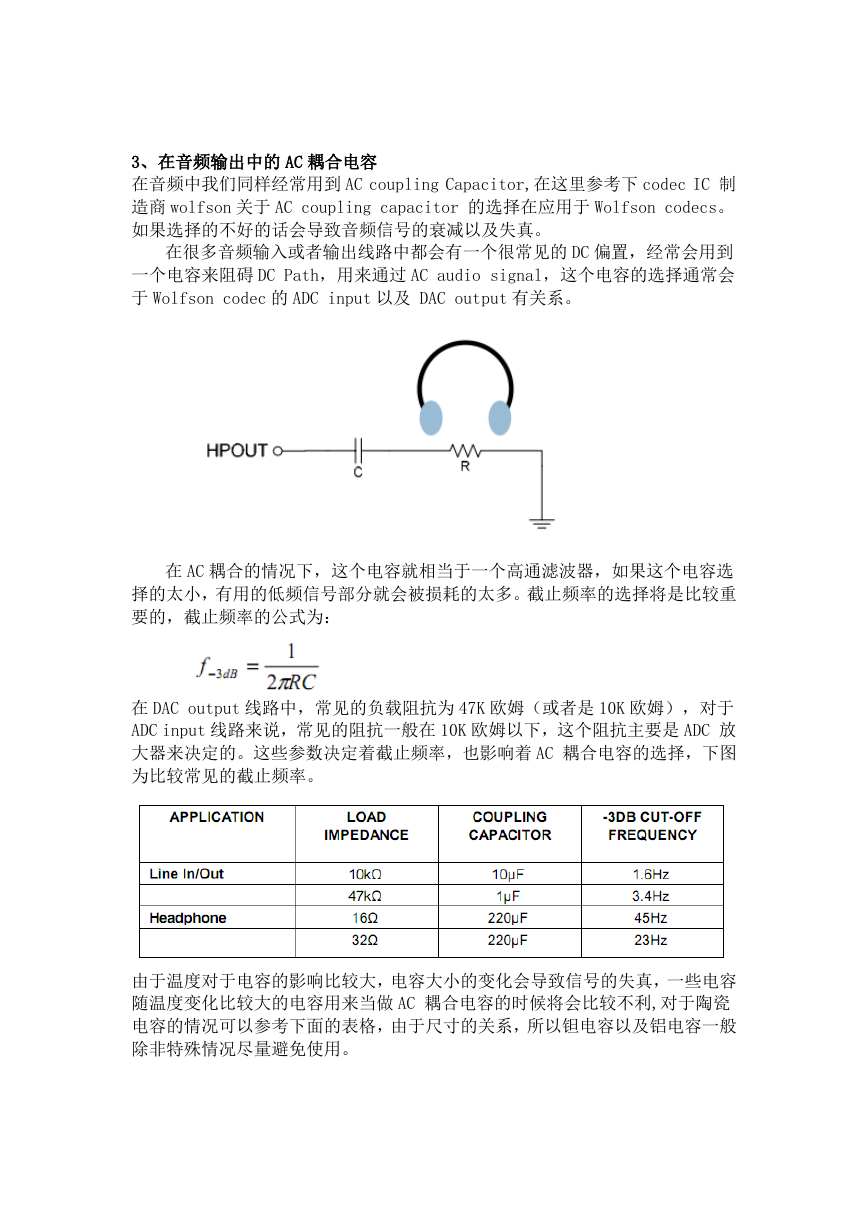

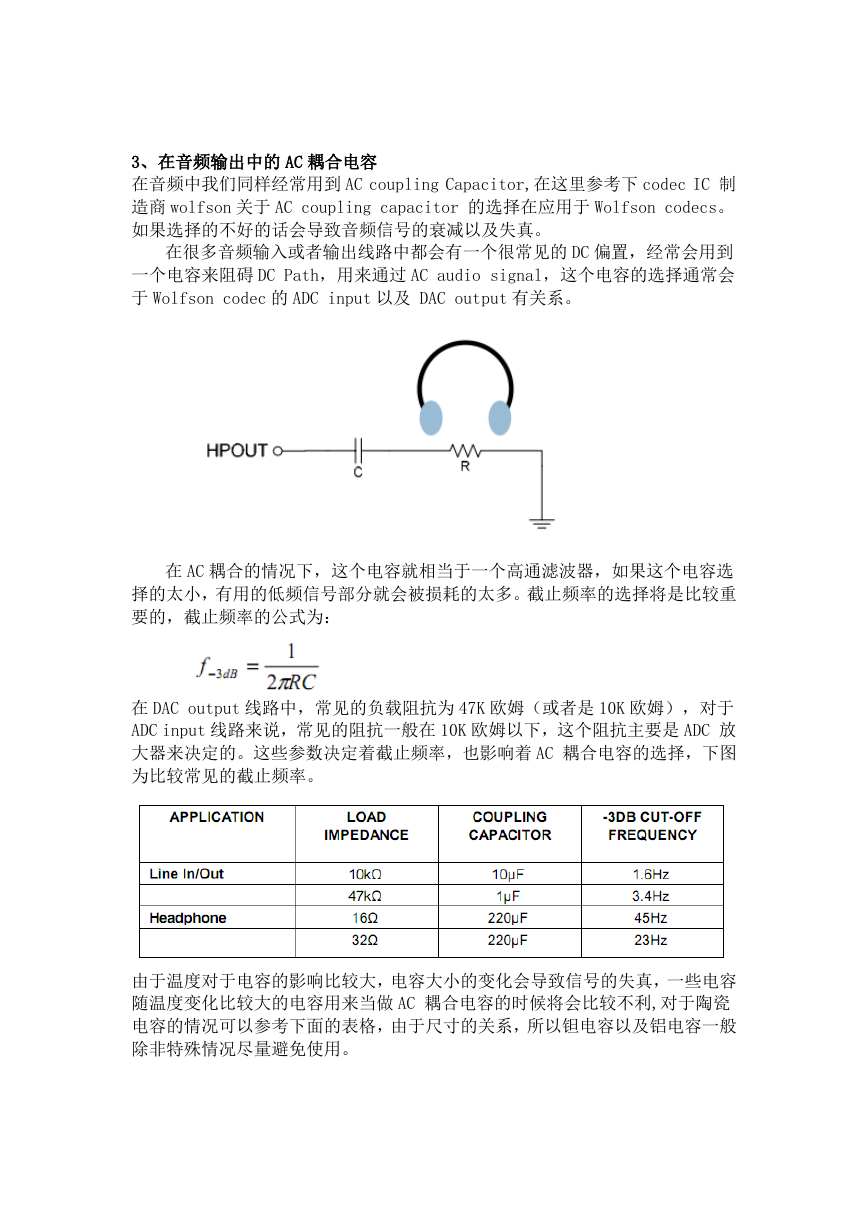

3、在音频输出中的 AC 耦合电容

在音频中我们同样经常用到 AC coupling Capacitor,在这里参考下 codec IC 制

造商 wolfson 关于 AC coupling capacitor 的选择在应用于 Wolfson codecs。

如果选择的不好的话会导致音频信号的衰减以及失真。

在很多音频输入或者输出线路中都会有一个很常见的 DC 偏置,经常会用到

一个电容来阻碍 DC Path,用来通过 AC audio signal,这个电容的选择通常会

于 Wolfson codec 的 ADC input 以及 DAC output 有关系。

在 AC 耦合的情况下,这个电容就相当于一个高通滤波器,如果这个电容选

择的太小,有用的低频信号部分就会被损耗的太多。截止频率的选择将是比较重

要的,截止频率的公式为:

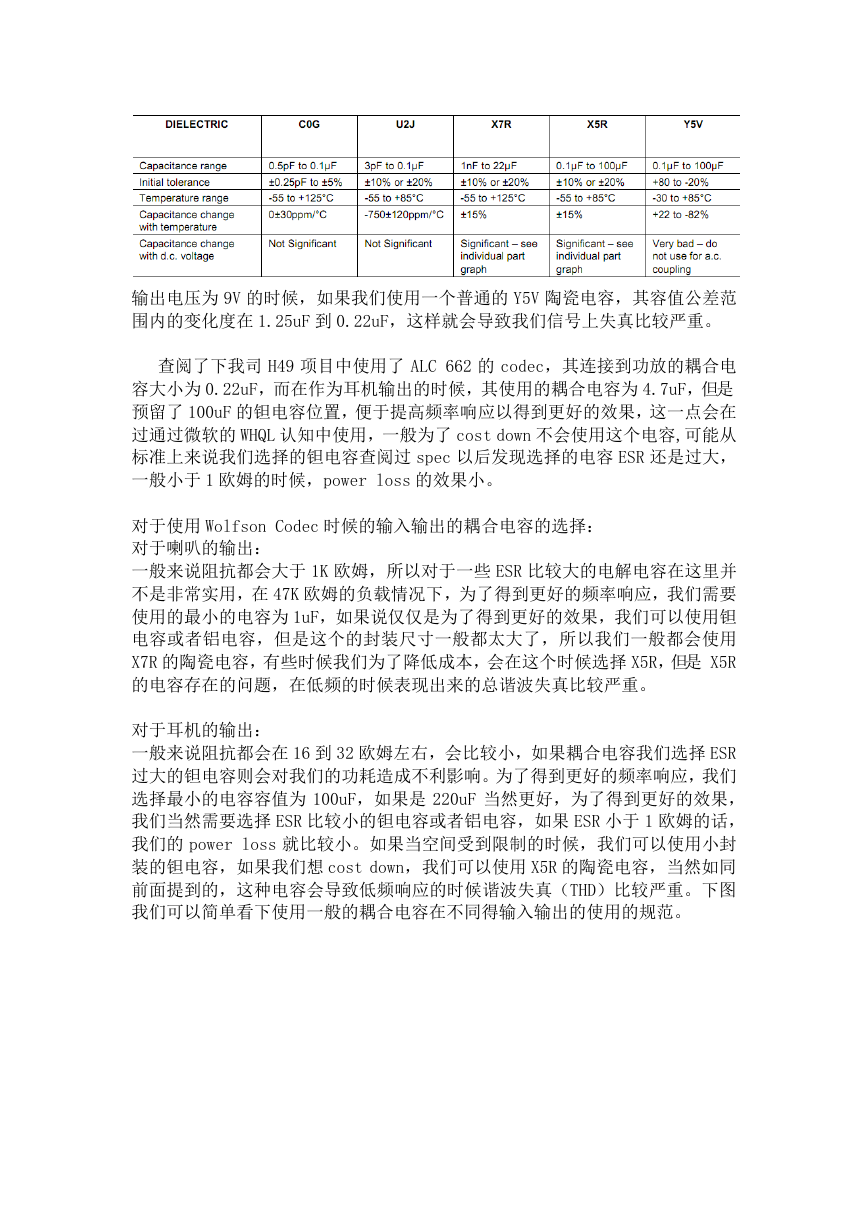

在 DAC output 线路中,常见的负载阻抗为 47K 欧姆(或者是 10K 欧姆),对于

ADC input 线路来说,常见的阻抗一般在 10K 欧姆以下,这个阻抗主要是 ADC 放

大器来决定的。这些参数决定着截止频率,也影响着 AC 耦合电容的选择,下图

为比较常见的截止频率。

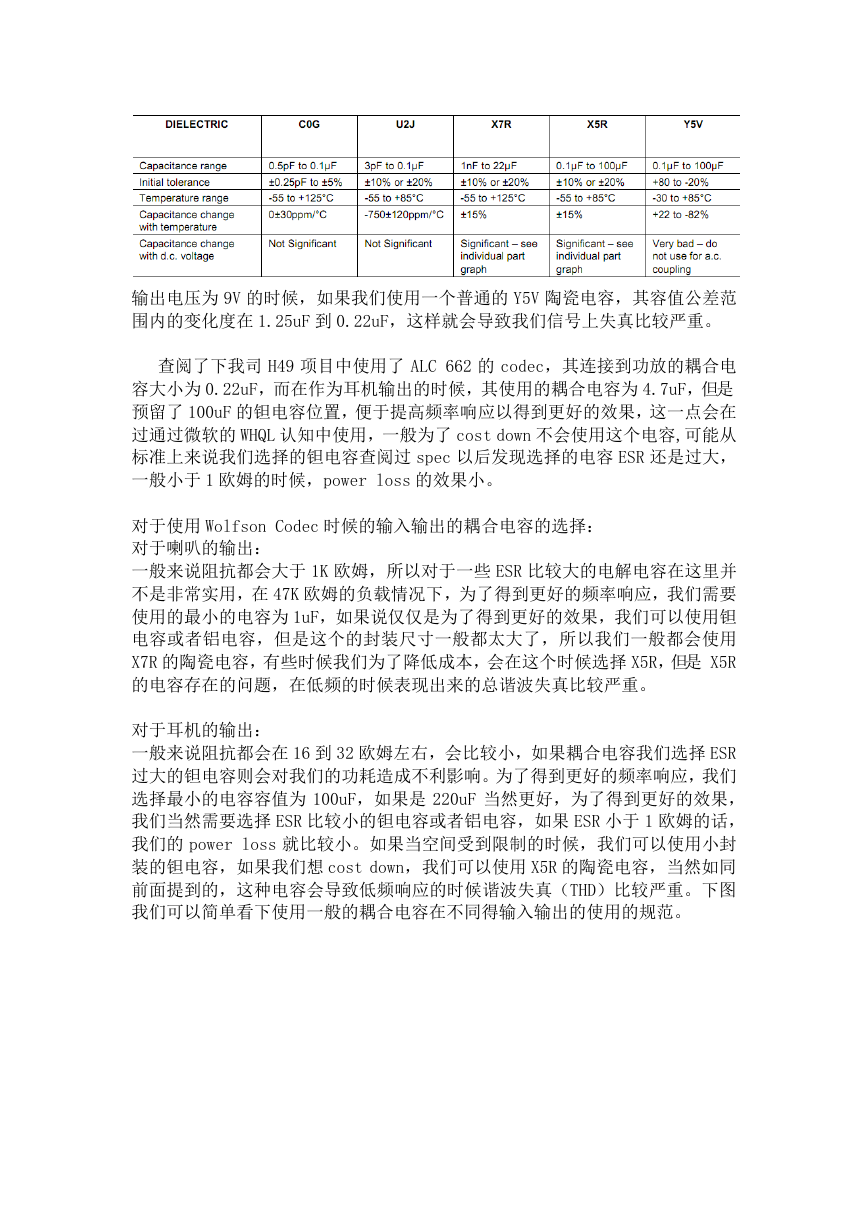

由于温度对于电容的影响比较大,电容大小的变化会导致信号的失真,一些电容

随温度变化比较大的电容用来当做 AC 耦合电容的时候将会比较不利,对于陶瓷

电容的情况可以参考下面的表格,由于尺寸的关系,所以钽电容以及铝电容一般

除非特殊情况尽量避免使用。

�

输出电压为 9V 的时候,如果我们使用一个普通的 Y5V 陶瓷电容,其容值公差范

围内的变化度在 1.25uF 到 0.22uF,这样就会导致我们信号上失真比较严重。

查阅了下我司 H49 项目中使用了 ALC 662 的 codec,其连接到功放的耦合电

容大小为 0.22uF,而在作为耳机输出的时候,其使用的耦合电容为 4.7uF,但是

预留了 100uF 的钽电容位置,便于提高频率响应以得到更好的效果,这一点会在

过通过微软的 WHQL 认知中使用,一般为了 cost down 不会使用这个电容,可能从

标准上来说我们选择的钽电容查阅过 spec 以后发现选择的电容 ESR 还是过大,

一般小于 1 欧姆的时候,power loss 的效果小。

对于使用 Wolfson Codec 时候的输入输出的耦合电容的选择:

对于喇叭的输出:

一般来说阻抗都会大于 1K 欧姆,所以对于一些 ESR 比较大的电解电容在这里并

不是非常实用,在 47K 欧姆的负载情况下,为了得到更好的频率响应,我们需要

使用的最小的电容为 1uF,如果说仅仅是为了得到更好的效果,我们可以使用钽

电容或者铝电容,但是这个的封装尺寸一般都太大了,所以我们一般都会使用

X7R 的陶瓷电容,有些时候我们为了降低成本,会在这个时候选择 X5R,但是 X5R

的电容存在的问题,在低频的时候表现出来的总谐波失真比较严重。

对于耳机的输出:

一般来说阻抗都会在 16 到 32 欧姆左右,会比较小,如果耦合电容我们选择 ESR

过大的钽电容则会对我们的功耗造成不利影响。为了得到更好的频率响应,我们

选择最小的电容容值为 100uF,如果是 220uF 当然更好,为了得到更好的效果,

我们当然需要选择 ESR 比较小的钽电容或者铝电容,如果 ESR 小于 1 欧姆的话,

我们的 power loss 就比较小。如果当空间受到限制的时候,我们可以使用小封

装的钽电容,如果我们想 cost down,我们可以使用 X5R 的陶瓷电容,当然如同

前面提到的,这种电容会导致低频响应的时候谐波失真(THD)比较严重。下图

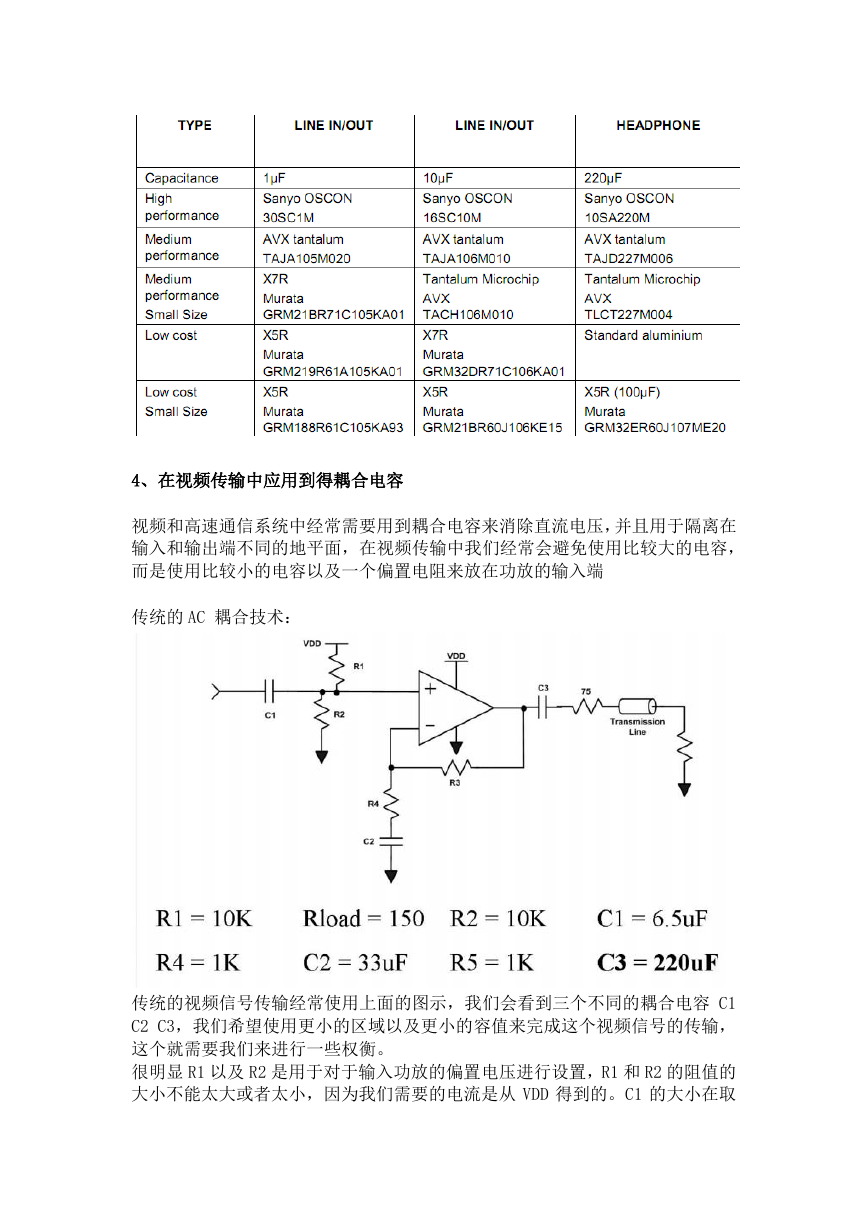

我们可以简单看下使用一般的耦合电容在不同得输入输出的使用的规范。

�

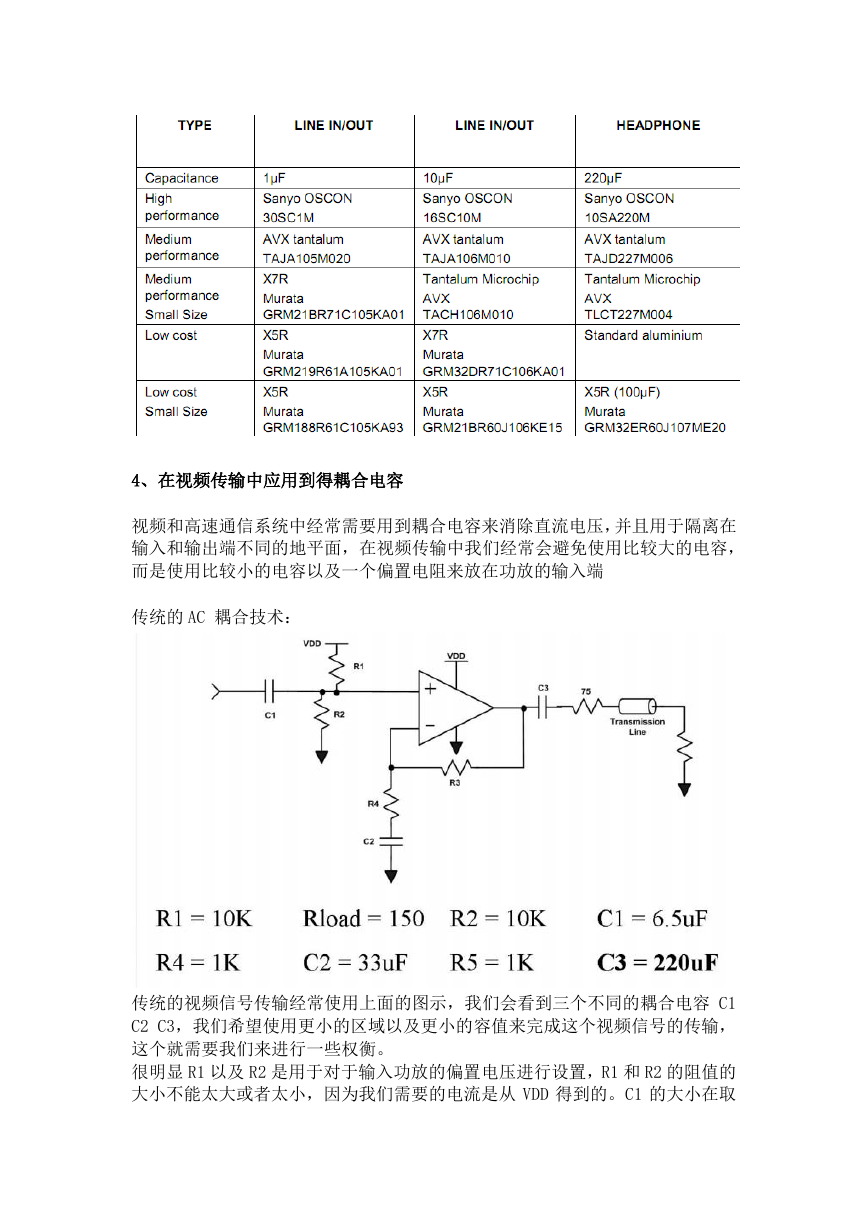

4、在视频传输中应用到得耦合电容

视频和高速通信系统中经常需要用到耦合电容来消除直流电压,并且用于隔离在

输入和输出端不同的地平面,在视频传输中我们经常会避免使用比较大的电容,

而是使用比较小的电容以及一个偏置电阻来放在功放的输入端

传统的 AC 耦合技术:

传统的视频信号传输经常使用上面的图示,我们会看到三个不同的耦合电容 C1

C2 C3,我们希望使用更小的区域以及更小的容值来完成这个视频信号的传输,

这个就需要我们来进行一些权衡。

很明显 R1 以及 R2 是用于对于输入功放的偏置电压进行设置,R1 和 R2 的阻值的

大小不能太大或者太小,因为我们需要的电流是从 VDD 得到的。C1 的大小在取

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc