DP83640 手册

DP83640 芯片手册

1.0 总体描述............................................................................................................................................................................................... 1

2.0 应用....................................................................................................................................................................................................... 1

3.0 特点....................................................................................................................................................................................................... 1

4.0 系统框图............................................................................................................................................................................................... 1

5.0 功能框图............................................................................................................................................................................................... 2

6.0 关键 IEEE1588 特色.............................................................................................................................................................................2

6.1 IEEE1588 同步时钟........................................................................................................................................................................2

6.1.1 IEEE1588 时钟输出..............................................................................................................................................................3

6.1.2 IEEE1588 时钟输入..............................................................................................................................................................3

6.2 打包时间戳.................................................................................................................................................................................... 3

6.2.1 IEEE1588 传输包分析(parser)和时间戳............................................................................................................................. 3

6.2.2 IEEE1588 接收包分析(parser)和时间戳............................................................................................................................. 3

6.2.3 NTP 包时间戳.......................................................................................................................................................................3

6.3 事件触发和加盖时间戳................................................................................................................................................................ 3

6.3.1 IEEE1588 事件触发..............................................................................................................................................................3

6.3.2 IEEE1588 加盖时间戳..........................................................................................................................................................3

6.4 PTP 中断......................................................................................................................................................................................... 3

6.5GPIO .................................................................................................................................................................................................3

7.0 管脚输出............................................................................................................................................................................................... 3

8.0 管脚....................................................................................................................................................................................................... 3

9.0 配置....................................................................................................................................................................................................... 5

9.2.2 自动协商寄存器控制........................................................................................................................................................... 5

9.2.4 自动协商复位...................................................................................................................................................................... 6

9.2.5 通过软件使能自动协商...................................................................................................................................................... 6

9.2.6 自动协商完成时间............................................................................................................................................................... 6

9.3 自动翻转-介质无关接口 MDIX(Medium Dependent Interface cross-over).................................................................................6

9.4 PHY 地址....................................................................................................................................................................................... 6

9.4.1 MII 孤立模式.....................................................................................................................................................................6

9.4.2 广播模式............................................................................................................................................................................ 6

9.5 LED 接口..................................................................................................................................................................................... 6

9.6 半双工/全双工............................................................................................................................................................................. 6

9.7 内部回环...................................................................................................................................................................................... 6

9.8 掉电/中断..................................................................................................................................................................................... 6

9.9 能量检测模式.............................................................................................................................................................................. 6

9.10 连接分析.................................................................................................................................................................................... 6

9.11 BIST............................................................................................................................................................................................6

10.0 MAC 接口......................................................................................................................................................................................... 6

10.2 RMII .............................................................................................................................................................................................. 6

10.2.1 RMII 主模式....................................................................................................................................................................... 7

10.2.2 RMII 从模式....................................................................................................................................................................... 7

10.3 SCMII 模式................................................................................................................................................................................... 7

10.4

IEEE 802.3u MII 串行管理接口............................................................................................................................................... 7

10.4.1 串行管理寄存器访问......................................................................................................................................................... 7

10.4.2 串行管理访问协议............................................................................................................................................................. 7

10.4.3 串行管理前导码抑制(Supression).....................................................................................................................................7

10.5 PHY 控制帧(PCF)..................................................................................................................................................................... 8

10.6 PHY 状态帧(PSF)......................................................................................................................................................................8

1.0 总体描述

2.0 应用

·工厂自动化: 以太网/IP; CIP 同步

·电讯: 基站

·测试和测量: LXI 标准

·实时网络

3.0 特点

■ 支持 IEEE1588 V1 和 V2

■ IEEE1588 时钟同步

■ 允许子 sub 10ns 同步于主时钟参考

■ 低传输和接收延时

■ dynamic link quality monitoring

■ 10/100Mb/s 包 BIST(built in self test)

■ ESD 保护 – 8kV 人体模式

■ auto-MDIX for 10/100Mbps

■ 25MHz MDC 和 MDIO 串行管理接口

■ IEEE1149.1 JTAG

■ 可选 100BASE-TX 快速链接丢失检测

■ 48 管脚 LQFP 封装 7mm×7mm

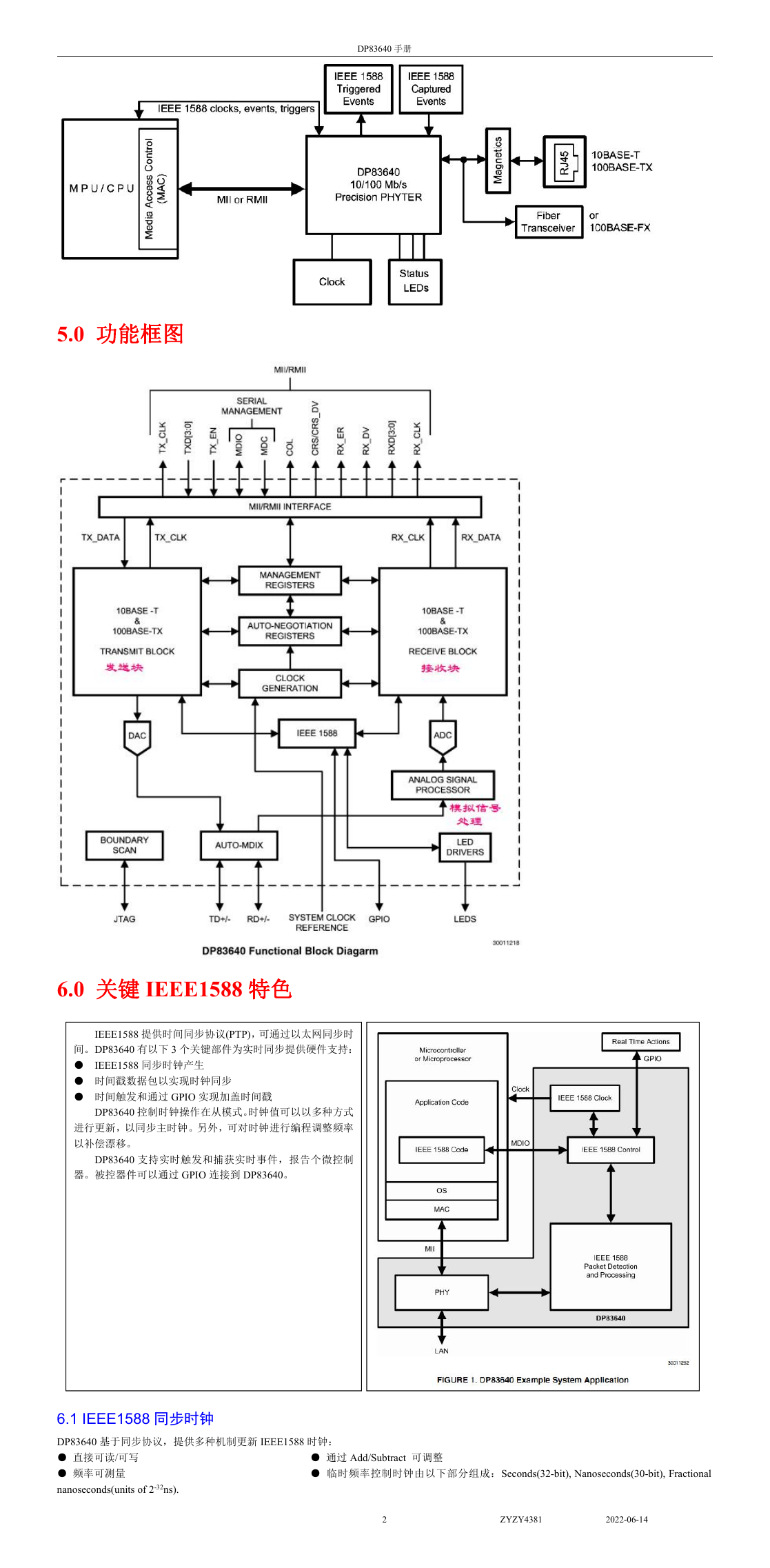

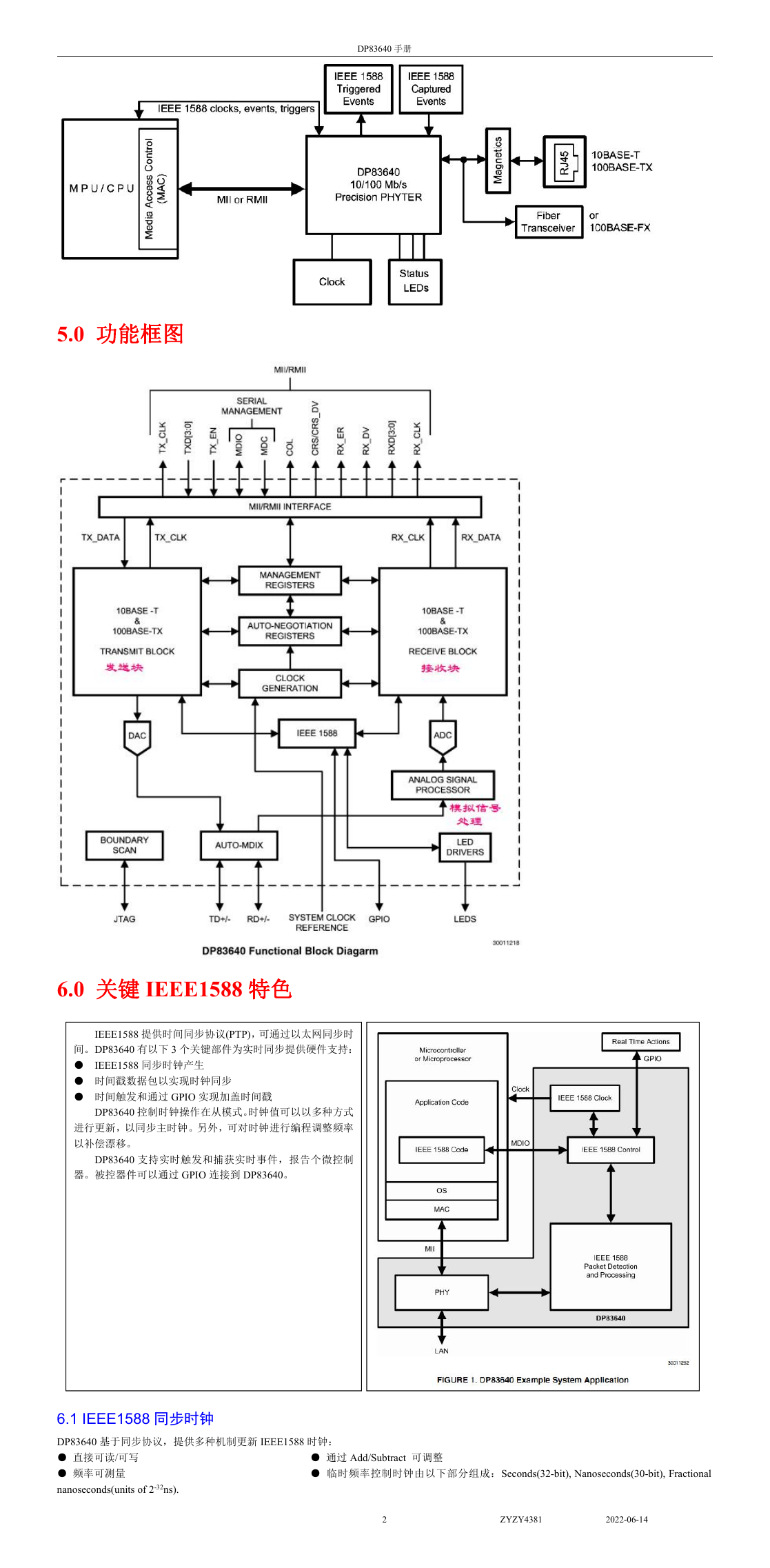

4.0 系统框图

■ UDP/IPv4, UDP/Ipv6, 并支持第二层以太网包 Layer2 Ethernet packets。

■ 时间戳精确度 8ns

■ 12 个 IEEE1588 GPIO,可触发或捕获

■ 可选频率同步时钟输出

■ 基于 TDR 的电缆诊断和电缆长度检测

■ error-free 操作科大 150 米 CAT5 电缆

■ 2.5V 和 3.3V I/O 和 MAC 接口

■ RMII V1.2 和 MII MAC 接口

■ IEEE802.3u 100BASE-FX 光纤接口

■ 可编程 LED,支持 Link,10/100Mb/s 双工,动态指示(activity)和碰撞检测。

■ 工业温度范围

1

ZYZY4381

2022-06-14

�

DP83640 手册

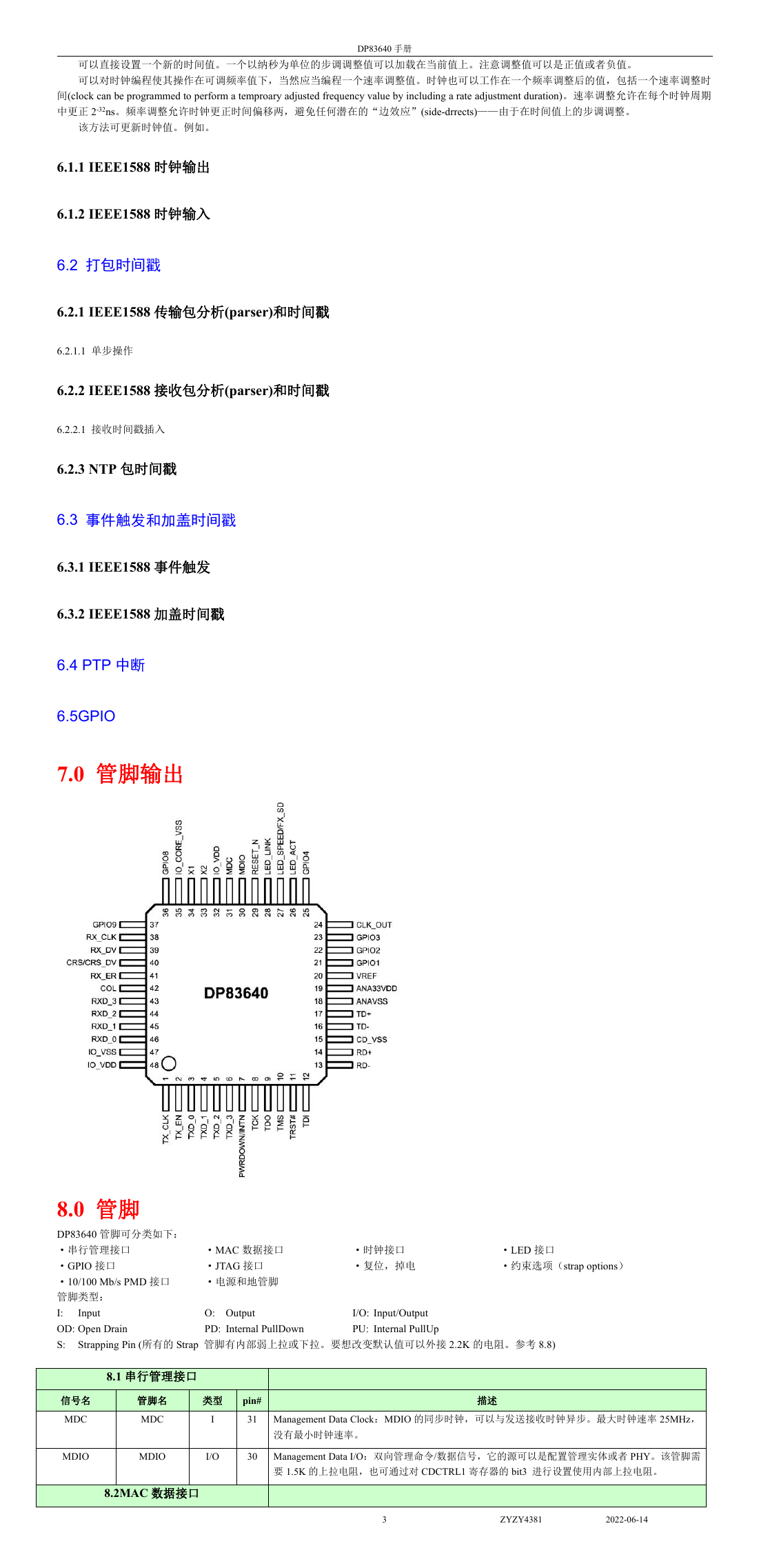

5.0 功能框图

6.0 关键 IEEE1588 特色

IEEE1588 提供时间同步协议(PTP),可通过以太网同步时

间。DP83640 有以下 3 个关键部件为实时同步提供硬件支持:

● IEEE1588 同步时钟产生

● 时间戳数据包以实现时钟同步

● 时间触发和通过 GPIO 实现加盖时间戳

DP83640 控制时钟操作在从模式。时钟值可以以多种方式

进行更新,以同步主时钟。另外,可对时钟进行编程调整频率

以补偿漂移。

DP83640 支持实时触发和捕获实时事件,报告个微控制

器。被控器件可以通过 GPIO 连接到 DP83640。

6.1 IEEE1588 同步时钟

DP83640 基于同步协议,提供多种机制更新 IEEE1588 时钟:

● 直接可读/可写

● 频率可测量

nanoseconds(units of 2-32ns).

● 通过 Add/Subtract 可调整

● 临时频率控制时钟由以下部分组成:Seconds(32-bit), Nanoseconds(30-bit), Fractional

2

ZYZY4381

2022-06-14

�

可以直接设置一个新的时间值。一个以纳秒为单位的步调调整值可以加载在当前值上。注意调整值可以是正值或者负值。

可以对时钟编程使其操作在可调频率值下,当然应当编程一个速率调整值。时钟也可以工作在一个频率调整后的值,包括一个速率调整时

间(clock can be programmed to perform a temproary adjusted frequency value by including a rate adjustment duration)。速率调整允许在每个时钟周期

中更正 2-32ns。频率调整允许时钟更正时间偏移两,避免任何潜在的“边效应”(side-drrects)——由于在时间值上的步调调整。

DP83640 手册

该方法可更新时钟值。例如。

6.1.1 IEEE1588 时钟输出

6.1.2 IEEE1588 时钟输入

6.2 打包时间戳

6.2.1 IEEE1588 传输包分析(parser)和时间戳

6.2.1.1 单步操作

6.2.2 IEEE1588 接收包分析(parser)和时间戳

6.2.2.1 接收时间戳插入

6.2.3 NTP 包时间戳

6.3 事件触发和加盖时间戳

6.3.1 IEEE1588 事件触发

6.3.2 IEEE1588 加盖时间戳

6.4 PTP 中断

6.5GPIO

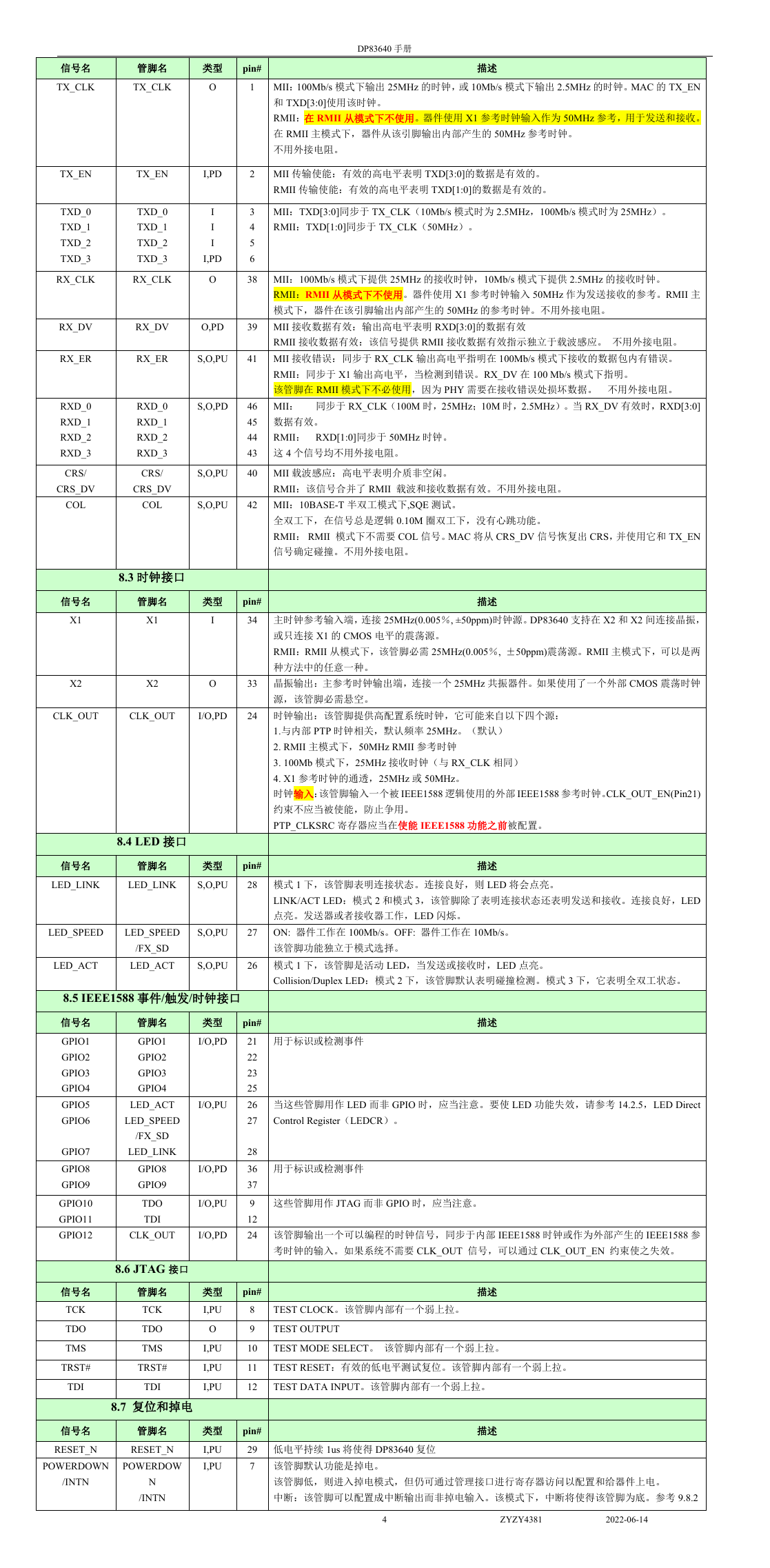

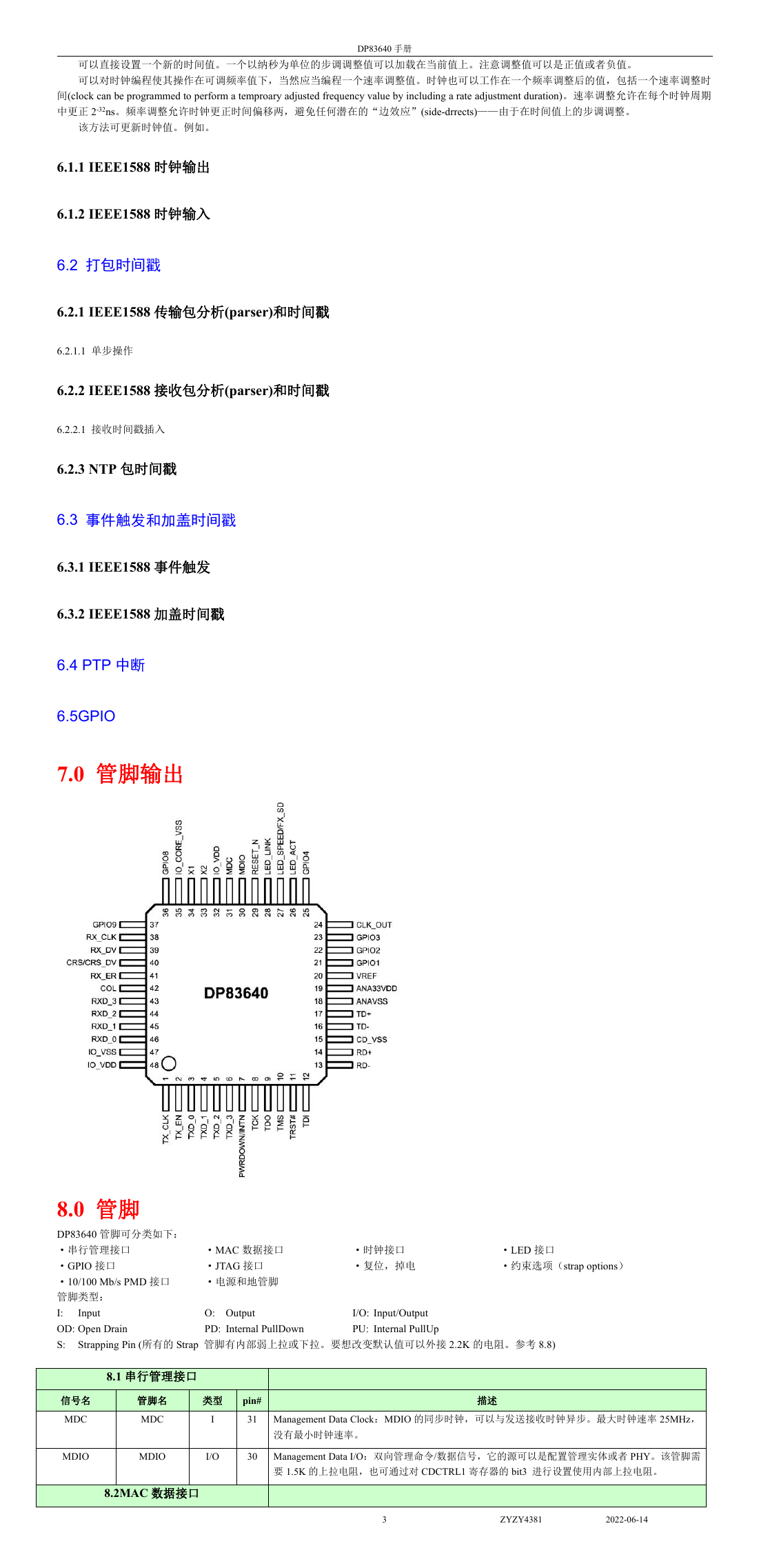

7.0 管脚输出

8.0 管脚

DP83640 管脚可分类如下:

·串行管理接口

·GPIO 接口

·10/100 Mb/s PMD 接口

管脚类型:

I:

OD: Open Drain

S:

Input

·MAC 数据接口

·JTAG 接口

·电源和地管脚

·时钟接口

·复位,掉电

·LED 接口

·约束选项(strap options)

O: Output

PD: Internal PullDown

I/O: Input/Output

PU: Internal PullUp

Strapping Pin (所有的 Strap 管脚有内部弱上拉或下拉。要想改变默认值可以外接 2.2K 的电阻。参考 8.8)

8.1 串行管理接口

信号名

MDC

管脚名

MDC

类型

I

pin#

31 Management Data Clock:MDIO 的同步时钟,可以与发送接收时钟异步。最大时钟速率 25MHz,

描述

没有最小时钟速率。

MDIO

MDIO

I/O

30 Management Data I/O:双向管理命令/数据信号,它的源可以是配置管理实体或者 PHY。该管脚需

要 1.5K 的上拉电阻,也可通过对 CDCTRL1 寄存器的 bit3 进行设置使用内部上拉电阻。

8.2MAC 数据接口

3

ZYZY4381

2022-06-14

�

信号名

TX_CLK

管脚名

TX_CLK

类型

O

pin#

1

TX_EN

TX_EN

I,PD

TXD_0

TXD_1

TXD_2

TXD_3

TXD_0

TXD_1

TXD_2

TXD_3

RX_CLK

RX_CLK

I

I

I

I,PD

O

2

3

4

5

6

DP83640 手册

描述

MII:100Mb/s 模式下输出 25MHz 的时钟,或 10Mb/s 模式下输出 2.5MHz 的时钟。MAC 的 TX_EN

和 TXD[3:0]使用该时钟。

RMII:在 RMII 从模式下不使用。器件使用 X1 参考时钟输入作为 50MHz 参考,用于发送和接收。

在 RMII 主模式下,器件从该引脚输出内部产生的 50MHz 参考时钟。

不用外接电阻。

MII 传输使能:有效的高电平表明 TXD[3:0]的数据是有效的。

RMII 传输使能:有效的高电平表明 TXD[1:0]的数据是有效的。

MII:TXD[3:0]同步于 TX_CLK(10Mb/s 模式时为 2.5MHz,100Mb/s 模式时为 25MHz)。

RMII:TXD[1:0]同步于 TX_CLK(50MHz)。

RXD_0

RXD_1

RXD_2

RXD_3

CRS/

CRS_DV

COL

信号名

X1

X2

RX_DV

RX_DV

O,PD

39 MII 接收数据有效:输出高电平表明 RXD[3:0]的数据有效

RX_ER

RX_ER

S,O,PU

38 MII:100Mb/s 模式下提供 25MHz 的接收时钟,10Mb/s 模式下提供 2.5MHz 的接收时钟。

RMII:RMII 从模式下不使用。器件使用 X1 参考时钟输入 50MHz 作为发送接收的参考。RMII 主

模式下,器件在该引脚输出内部产生的 50MHz 的参考时钟。不用外接电阻。

RMII 接收数据有效:该信号提供 RMII 接收数据有效指示独立于载波感应。 不用外接电阻。

41 MII 接收错误:同步于 RX_CLK 输出高电平指明在 100Mb/s 模式下接收的数据包内有错误。

RMII:同步于 X1 输出高电平,当检测到错误。RX_DV 在 100 Mb/s 模式下指明。

该管脚在 RMII 模式下不必使用,因为 PHY 需要在接收错误处损坏数据。 不用外接电阻。

MII: 同步于 RX_CLK(100M 时,25MHz;10M 时,2.5MHz)。当 RX_DV 有效时,RXD[3:0]

数据有效。

RMII: RXD[1:0]同步于 50MHz 时钟。

这 4 个信号均不用外接电阻。

46

45

44

43

40 MII 载波感应:高电平表明介质非空闲。

RMII:该信号合并了 RMII 载波和接收数据有效。不用外接电阻。

S,O,PD

S,O,PU

RXD_0

RXD_1

RXD_2

RXD_3

CRS/

CRS_DV

COL

S,O,PU

42 MII:10BASE-T 半双工模式下,SQE 测试。

全双工下,在信号总是逻辑 0.10M 圈双工下,没有心跳功能。

RMII: RMII 模式下不需要 COL 信号。MAC 将从 CRS_DV 信号恢复出 CRS,并使用它和 TX_EN

信号确定碰撞。不用外接电阻。

8.3 时钟接口

管脚名

类型

X1

X2

I

O

pin#

34 主时钟参考输入端,连接 25MHz(0.005%, ±50ppm)时钟源。DP83640 支持在 X2 和 X2 间连接晶振,

描述

或只连接 X1 的 CMOS 电平的震荡源。

RMII:RMII 从模式下,该管脚必需 25MHz(0.005%, ±50ppm)震荡源。RMII 主模式下,可以是两

种方法中的任意一种。

33 晶振输出:主参考时钟输出端,连接一个 25MHz 共振器件。如果使用了一个外部 CMOS 震荡时钟

源,该管脚必需悬空。

CLK_OUT

CLK_OUT

I/O,PD

24 时钟输出:该管脚提供高配置系统时钟,它可能来自以下四个源:

1.与内部 PTP 时钟相关,默认频率 25MHz。(默认)

2. RMII 主模式下,50MHz RMII 参考时钟

3. 100Mb 模式下,25MHz 接收时钟(与 RX_CLK 相同)

4. X1 参考时钟的通透,25MHz 或 50MHz。

时钟输入:该管脚输入一个被 IEEE1588 逻辑使用的外部 IEEE1588 参考时钟。CLK_OUT_EN(Pin21)

约束不应当被使能,防止争用。

PTP_CLKSRC 寄存器应当在使能 IEEE1588 功能之前被配置。

8.4 LED 接口

信号名

管脚名

类型

LED_LINK

LED_LINK

S,O,PU

pin#

28 模式 1 下,该管脚表明连接状态。连接良好,则 LED 将会点亮。

描述

LINK/ACT LED:模式 2 和模式 3,该管脚除了表明连接状态还表明发送和接收。连接良好,LED

点亮。发送器或者接收器工作,LED 闪烁。

ON: 器件工作在 100Mb/s。OFF: 器件工作在 10Mb/s。

该管脚功能独立于模式选择。

S,O,PU

26 模式 1 下,该管脚是活动 LED,当发送或接收时,LED 点亮。

Collision/Duplex LED:模式 2 下,该管脚默认表明碰撞检测。模式 3 下,它表明全双工状态。

LED_SPEED

LED_SPEED

S,O,PU

27

LED_ACT

/FX_SD

LED_ACT

8.5 IEEE1588 事件/触发/时钟接口

信号名

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

信号名

TCK

TDO

TMS

TRST#

TDI

管脚名

GPIO1

GPIO2

GPIO3

GPIO4

LED_ACT

LED_SPEED

/FX_SD

LED_LINK

GPIO8

GPIO9

TDO

TDI

类型

I/O,PD

I/O,PU

I/O,PD

I/O,PU

CLK_OUT

I/O,PD

8.6 JTAG 接口

管脚名

TCK

TDO

TMS

TRST#

TDI

类型

I,PU

O

I,PU

I,PU

I,PU

类型

I,PU

I,PU

8.7 复位和掉电

信号名

RESET_N

管脚名

RESET_N

POWERDOWN

POWERDOW

/INTN

N

/INTN

pin#

21

22

23

25

26

27

用于标识或检测事件

描述

当这些管脚用作 LED 而非 GPIO 时,应当注意。要使 LED 功能失效,请参考 14.2.5,LED Direct

Control Register(LEDCR)。

用于标识或检测事件

28

36

37

9

12

24 该管脚输出一个可以编程的时钟信号,同步于内部 IEEE1588 时钟或作为外部产生的 IEEE1588 参

这些管脚用作 JTAG 而非 GPIO 时,应当注意。

考时钟的输入。如果系统不需要 CLK_OUT 信号,可以通过 CLK_OUT_EN 约束使之失效。

pin#

8

9

10

11

12

描述

TEST CLOCK。该管脚内部有一个弱上拉。

TEST OUTPUT

TEST MODE SELECT。 该管脚内部有一个弱上拉。

TEST RESET:有效的低电平测试复位。该管脚内部有一个弱上拉。

TEST DATA INPUT。该管脚内部有一个弱上拉。

pin#

29 低电平持续 1us 将使得 DP83640 复位

7 该管脚默认功能是掉电。

描述

该管脚低,则进入掉电模式,但仍可通过管理接口进行寄存器访问以配置和给器件上电。

中断:该管脚可以配置成中断输出而非掉电输入。该模式下,中断将使得该管脚为底。参考 9.8.2

4

ZYZY4381

2022-06-14

�

8.8 约束选项

管脚名

COL

RXD_3

RXD_2

RXD_1

RXD_0

S, O, PU

S, O, PU

S, O, PU

S, O, PU

S, O, PU

LED_LINK

LED_SPEED

S, O, PU

S, O, PU

/FX_SD

LED_ACT

S, O, PU

DP83640 手册

Interrupt Mechanisms

DP83640 使用很多功能管脚作为约束选项,将器件配置为特殊的操作模式下。

这些管脚在

上电或硬件复位时被采样。软件复位时,约束选项内部重新加载采样值。 一个 2.2K 的电阻应当

用于上拉或者下拉来改变默认的约束选项。如果需要默认选择,那么不需要外部上拉或下拉。因

为这些管脚在复位后功能会变化,他们不可直接连接到 Vcc 或 GND。

类型

pin#

描述

42

43

44

45

46

28

27

26

PHY 地址[4:0]。DP83640 提供 5 个 PHY 地址引脚。硬件复位时将他们的状态锁存入 PHYCTRL

寄存器。

DP83640 支持地址约束值 0~31。地址 0 将器件设为 MII 独立模式。MII 独立模式必须通过约束 PHY

地址为 0 来实现,通过寄存器写实现地址 0 不会将器件设为 MII 模式。

PHYAD[0]管脚有弱内部上拉电阻。

PHYAD[1:4]管脚有弱内部下拉电阻。

Auto-Negotiation Enable。通过将 AN0 和 AN1 管脚设置为高,可实现自动协商。设置为低,则进入

强制模式。

AN0/AN1:它们可以通过 2.2K 电阻连接 GND(0)或 VCC(1)。绝对不允许直接接地或接 VCC。它

们的值在硬件复位时锁存入 DP83640。它们的悬空或下拉状态将在硬件复位时锁存入 Basic Mode

Control Register 和 Auto Negotiation Advertisement Register.

这 3 个信号默认是 111(内部有上拉电阻)。

Fiber 模式双工选择:令 FX_EN_Z=0,以约束选定 Fiber 模式,AN0 约束值用于选择半双工还是全

双工。AN_EN 和 AN1 将被忽略因为仅仅是 100Mb 并且不支持自动协商。在 Fiber 模式下,AN1

不应连接任何系统部件除了 fiber 传送接收器。

AN0

Forced 模式

FX_EN_Z

AN_EN

AN1

信号名

PHYAD0

PHYAD1

PHYAD2

PHYAD3

PHYAD4

AN_EN

AN1

AN0

1

1

1

1

0

0

0

0

0

0

X

X

FX_EN_Z

AN_EN

1

1

1

1

1

1

1

1

0

0

1

1

X

X

AN1

0

0

1

1

0

1

0

1

0

1

AN0

0

1

0

1

10BASE-T,半双工

10BASE-T,全双工

100BASE-TX,半双工

100BASE-TX,全双工

100BASE-FX,半双工

100BASE-FX,全双工

Advertised 模式

10BASE-T,半/全双工

100BASE-TX,半/全双工

100BASE-TX,全双工

10BASE-T,半/全双工

100BASE-TX,半/全双工

CLK_OUT_EN

FX_EN_Z

GPIO1

RX_ER

S, I, PD

S, O, PU

21 若为高电平,在上电时刻使能时钟输出在 CLK_OUT 引脚。

41 该约束选项使能 100BASE-FX(Fiber)模式,该模式默认是不可用的。外部下拉电阻将使能

LED_CFG

MII_MODE

PCF_EN

RMII_MAS

CRS/

CRS_DV

RX_DV

GPIO2

TXD_3

100BASE-FX 模式。

S, O, PU

40 该约束选项决定了 LED 引脚的运行模式。默认是模式 1。模式 1 和模式 2 是可以通过约束选项控

S, I, PD

S, I, PD

S, I, PD

制的。所有的模式通过寄存器访问进行配置。参考表 3: LED 模式选择。

22

6

39 MII 模式选择:该约束选项控制 MAC 数据接口的运行模式。由于内部下拉电阻,该引脚默认为 0,

即选择 MII 模式。约束该引脚为高将使器件运行在 RMII 模式。(0=MII Mode)(1=RMII Mode)

PHY Control Enable:高电平时,允许 DP83640 对 PHY 控制帧做出反应。

RMII Master Enable:MII_MODE 为高时,使能 RMII 模式,此时 DP83640 使用一个连接 X1/X2 的

25MHz 的晶振从而产生 50MHz RMII 参考时钟。当 MII_MODE 为高时,如果选择 RMII_MAS 为低,

默认的 RMII 操作(RMII Slave)使能,此时 DP83640 使用一个 50MHz 振荡器输入在 X1 作为 RMII

参考时钟。该约束选项被忽略如果 MII_MODE 为低。

8.9

10Mb/s 和 100Mb/sPMD 接口

pin#

16

17

13

14

27

描述

差分共模驱动传输输出(PMD 输出对)。他们自动配置以发送 10BASE-T 或者 100BASE-TX 信号。

在 Auto-MDIX 模式下,该对也可用作接收输入对。

在 100BASE-FX 模式下,该对变为 100BASE-FX 传输对,这些管脚需要 3.3V 偏置。

差分接收输入(PMD 输入对)。这些差分输入自动配置以接收 100BASE-TX 或 10BASE-T 信号。

在 Auto-MDIX 模式下,该对也可用作发送输出对。

在 100BASE-FX 模式下,该对变为 100BASE-FX 接收对,这些管脚需要 3.3V 偏置。

Fiber Mode Signal Detect:这些管脚为 100BASE-FX 模式提供信号检测输入。

pin

18 模拟地

19 模拟 VDD

15 模拟地

35 数字地

描述

I/O VDD

32

48

47 数字地

20 偏置电阻连接。一个 1%,4.87k 的电阻应当从 VREF 连接到 GND

信号名

管脚名

TD-

TD+

RD-

RD+

TD-

TD+

RD-

RD+

FX_SD

FX_SD

8.10 电源管脚

信号名

ANAVSS

ANA33VDD

CD_VSS

IO_CORE_VSS

IO_VDD

IO_VSS

VREF

管脚名

ANAVSS

ANA33VDD

CD_VSS

IO_CORE_

VSS

IO_VDD

IO_VSS

VREF

类型

I/O

I/O

S, I/O,

PU

类型

Ground

Supply

Ground

Ground

Supply

Ground

X

9.0 配置

9.2.2 自动协商寄存器控制

当自动协商使能时,DP83640 传输具有 ANAR(Auto-Negotiation Advertisement register)的能力,ANAR 在 04h 地址,通过 FLP Brusts。可

以选择 10Mb/s,100Mb/s,半双工,全双工的任何组合。

自动协商优先级:

1.

2.

3.

4.

100BASE-TX 全双工(优先级最高)

100BASE-TX 半双工

10BASE-T 全双工

10BASE-T 半双工(优先级最低)

地址处于 00h 的基本模式控制寄存器 BMCR(Basic Mode Control Register)为自动协商提供使能,非使能和重启等功能。当禁止自动协商

功能时,BMCR 中的 SPEED SELECTION bit 可进行 10Mb/s 和 100Mb/s 的转换,DUPLEX MODE bit 进行全双工和半双工的转换。当自动协商

使能是,以上这两个 bit 位不起作用。

建立连接后,可以通过 PHY 状态寄存器(地址在 10h)检测链接速度。基本模式状态寄存器(Basic Mode Status Register)可以设置技术类

型,自动协商能力和扩展寄存器能力。这些 bit 位是永久有效的,以对 DP83640 的全部功能进行设定。(DP83640 不支持 100BASE-T4,所以对

应的 bit 位是不能设定的)。

BMSR 同时提供如下状态:

5

ZYZY4381

2022-06-14

�

· 自动协商是否彻底

· 是否建立了一个远程链接 · 支持管理帧报头压制。

· 是否链接伙伴宣称发生了一个远程错误

DP83640 手册

自动协商宣传寄存器(Auto-Negotiation Advertisement Register ANAR)指示了 DP83640 的自动协商能力。默认情况下,所有的能力都可以

传输,同过写 ANAR 寄存器都可以将其禁止。更新 ANAR 可以限制部分功能。

自动协商链接伙伴能力寄存器(Auto-Negotiation Link Partner Ability Register ANLPAR)地址是 05h,它用于在协商时接收基本链接代码字

和下页代码字。ANLPAR 可通过更新为 0081h 或者 0020h 分别进行 100Mb/s 或 10Mb/s 的并行检测。

自动协商扩展寄存器(Auto-Negotiation Expansion Register ANER)用于指示附加的自动协商状态:

· 是否发生并行检测错误

· 是否 DP83640 支持下一页功能

· 是否链接伙伴支持自动协商功能

9.2.3 自动协商并行检测

· 是否链接伙伴支持下一页功能

· 当前正在通过自动协商实现交换的页是否已经被接收

DP83640 支持 802.3u 定义的并行检测功能。并行检测功能需要 10Mb/s 和 100Mb/s 接收器检测接收信号,报告链接状态给自动协商函数。

当链接伙伴不支持自动协商但是却正在传输 100BASE-TX 或 10BASE-T PMAs 认为有效的信号时,自动协商使用这个信息以配置正确的技术。

如果 DP83640 完成自动协商,ANLPAR 寄存器的 bit 位 5 和 7 将被设置以反映当前链接伙伴的操作模式。并行检测成功后,ANLPAR 的

Bit4:0 也将被设置成 0001 以表明一个有效的 802.3 选择域。一旦 auto-negotiation complete bit 被设置,软件可以通过读取 link partner auto-negotation

able bit 为 0 来确定自动协商是否完成。当配置并行检测并且并未建立好的链接时,parallel detect fault bit 经被设置。

9.2.4 自动协商复位

9.2.5 通过软件使能自动协商

9.2.6 自动协商完成时间

9.3 自动翻转-介质无关接口 MDIX(Medium Dependent Interface cross-over)

该功能使能时,自动协商决定合适的配置以传送或接收数据,最终选合适的 MDI 对.Auto-MDIX 默认使能,并可以通过 19h 的 PHYCR 寄

存器的 bits【15:14】进行设置。强制交叉可以通过 FORCE_MDIX (PHYCR 的 bit14)的设置来实现。

注意:Auto-MDIX 在强制模式下不工作。

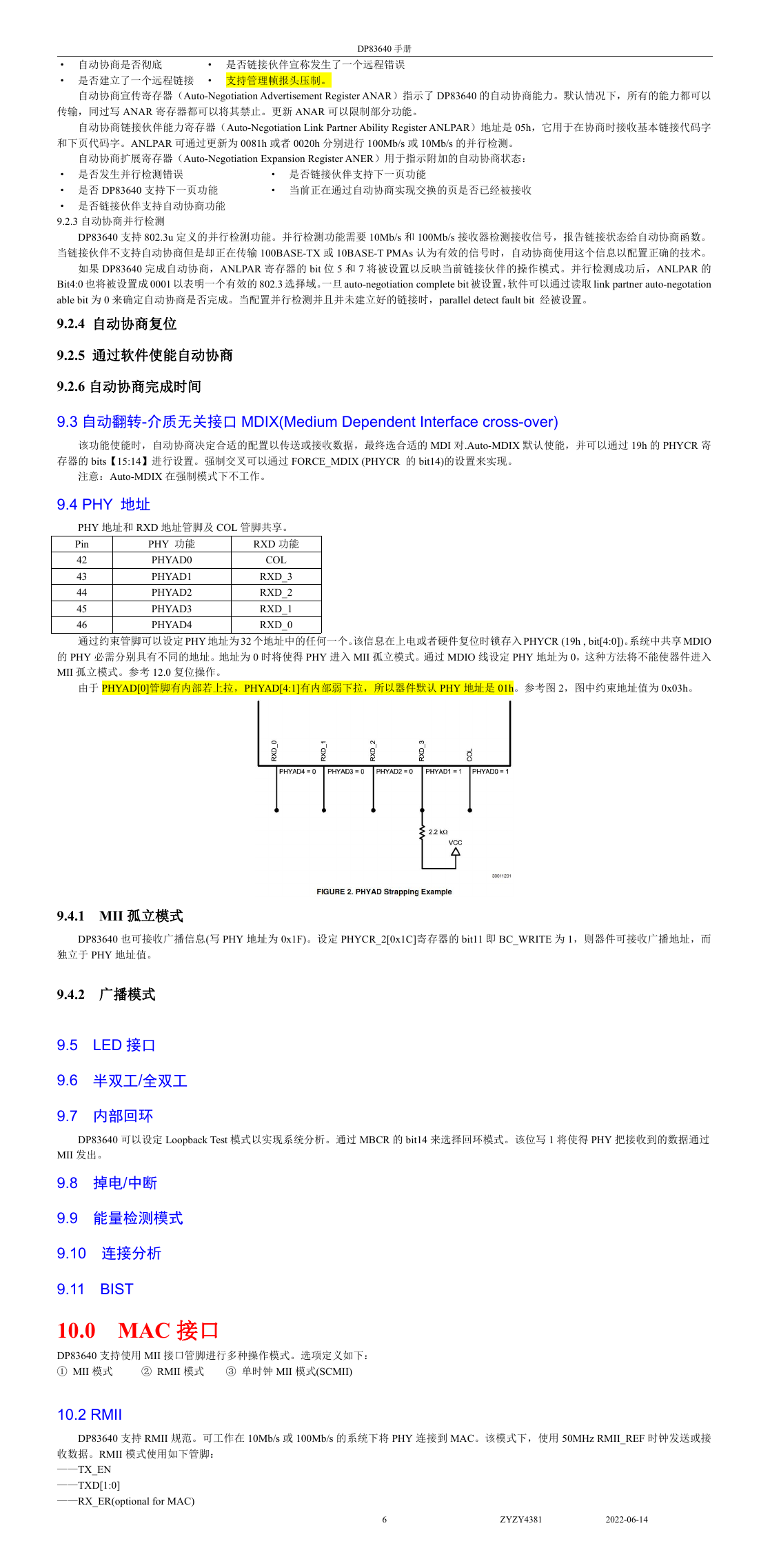

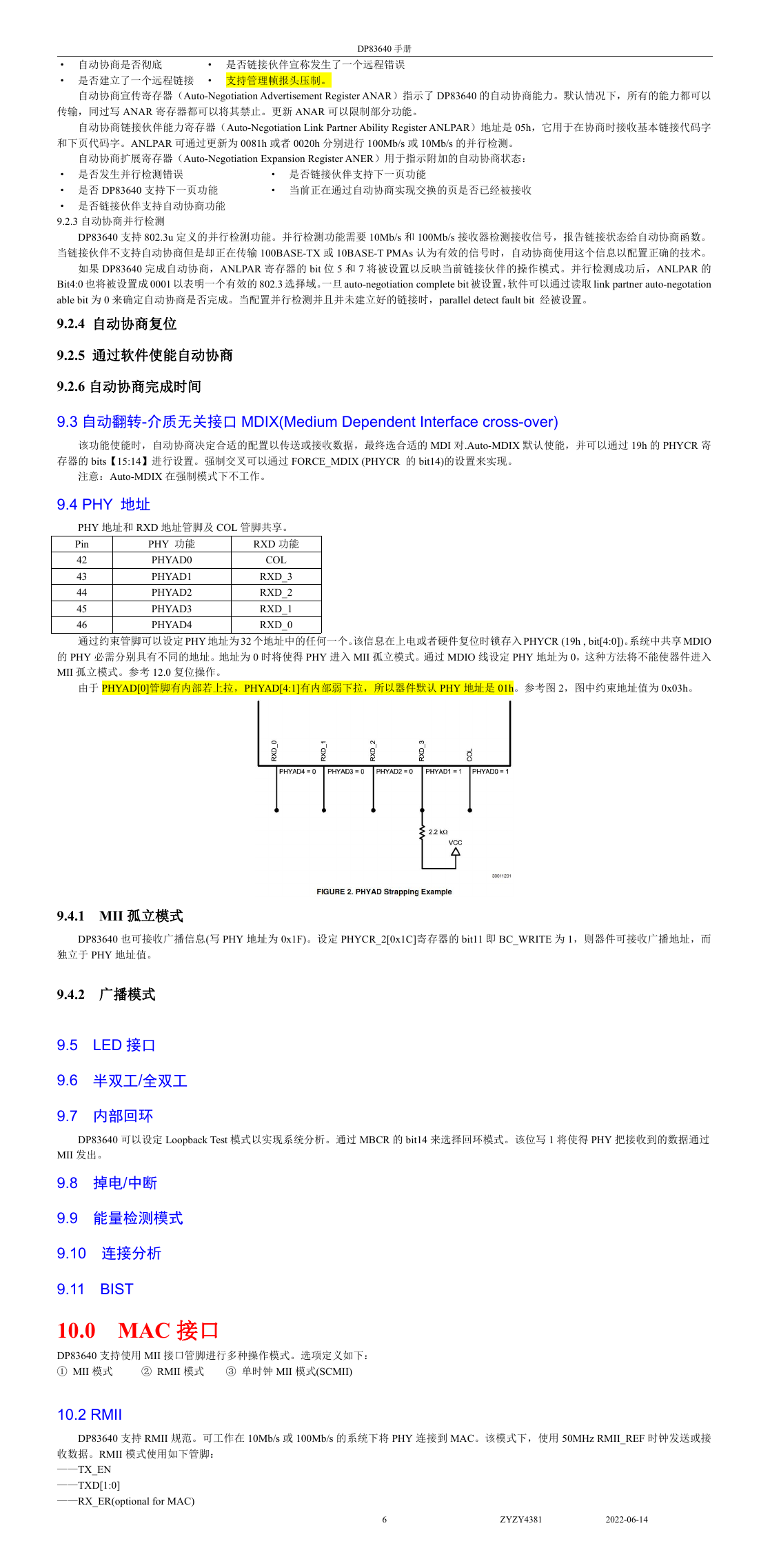

9.4 PHY 地址

PHY 功能

PHYAD0

PHYAD1

PHYAD2

PHYAD3

PHYAD4

PHY 地址和 RXD 地址管脚及 COL 管脚共享。

Pin

RXD 功能

42

43

44

45

46

通过约束管脚可以设定 PHY 地址为 32 个地址中的任何一个。该信息在上电或者硬件复位时锁存入 PHYCR (19h , bit[4:0])。系统中共享 MDIO

的 PHY 必需分别具有不同的地址。地址为 0 时将使得 PHY 进入 MII 孤立模式。通过 MDIO 线设定 PHY 地址为 0,这种方法将不能使器件进入

MII 孤立模式。参考 12.0 复位操作。

COL

RXD_3

RXD_2

RXD_1

RXD_0

由于 PHYAD[0]管脚有内部若上拉,PHYAD[4:1]有内部弱下拉,所以器件默认 PHY 地址是 01h。参考图 2,图中约束地址值为 0x03h。

9.4.1 MII 孤立模式

DP83640 也可接收广播信息(写 PHY 地址为 0x1F)。设定 PHYCR_2[0x1C]寄存器的 bit11 即 BC_WRITE 为 1,则器件可接收广播地址,而

独立于 PHY 地址值。

9.4.2 广播模式

9.5 LED 接口

9.6 半双工/全双工

9.7 内部回环

DP83640 可以设定 Loopback Test 模式以实现系统分析。通过 MBCR 的 bit14 来选择回环模式。该位写 1 将使得 PHY 把接收到的数据通过

MII 发出。

9.8 掉电/中断

9.9 能量检测模式

9.10 连接分析

9.11 BIST

10.0 MAC 接口

DP83640 支持使用 MII 接口管脚进行多种操作模式。选项定义如下:

① MII 模式

③ 单时钟 MII 模式(SCMII)

② RMII 模式

10.2 RMII

DP83640 支持 RMII 规范。可工作在 10Mb/s 或 100Mb/s 的系统下将 PHY 连接到 MAC。该模式下,使用 50MHz RMII_REF 时钟发送或接

收数据。RMII 模式使用如下管脚:

——TX_EN

——TXD[1:0]

——RX_ER(optional for MAC)

6

ZYZY4381

2022-06-14

�

——CRS/CRS_DV

——RXD[1:0]

——X1(RMII 主模式下 25MHz,RMII 从模式下 50MHz )

——RX_CLK, TX_CLK, CLK_OUT (仅在 RMII 主模式下的 50MHz 参考时钟)

DP83640 手册

另外,RMII 模式下提供 RX_DV 信号,这样简化了原来从 CRS_DV 中分离 RX_DV 的过程。这对于不需要 CRS 信号的系统是很有用的(如

那些仅支持全双工操作的系统)。当实现将接收的 RMII 数据直接发送出去形成回环以达到分析测试时也是有用的。

RX_ER 输出可被 MAC 用于检测错误条件。它宣称接收的符号错误,在包、False Carrier 事件、FIFO 低产或者超支情况下。由于在错误处

需要 PHY 更正接收数据,MAC 不需要使用 RX_ER。在 10Mb/s 操作下,参考时钟运行在 10 倍的数据速率,所以传送数据每 10 个时钟采样一

次。同样,也是每隔 10 个时钟产生一个接收数据。

RMII 从模式需要一个 50MHz 振荡器连接到 X1。RMII 从模式不支持 50MHz 晶振。RMII 主模式可用 25MHz 振荡器连接到 X1,也可用 25MHz

晶振连接 X1 和 X2。为克服 50MHz 参考时钟和恢复的接收时钟的差异,接收 RMII 功能包括一个可编程的弹性缓冲。该弹性缓冲可编程以最小

化传播延时基于预期的包大小和时钟准确度。这允许支持一定范围的包大小,包括巨型帧。

弹性缓冲将促使包的 Frame Check Sequence 错误,这个包 overrun or underrun the FIFO。overrun or underrun 可以被报告在 RMII 和 Bypass 寄

存器(RBR)。表 5 指明了如何编程弹性缓冲 FIFO(以 4bit 增加)基于最大的包大小和时钟准确度。它假设 RMII 参考时钟和 far-end 传送时钟有同

样的准确度。

表 5 在±50ppm 频率准确度下支持的包大小

Start Threshold RBR[1:0]

延迟容限

推荐的包大小

100Mb

10Mb

100Mb

10Mb

01 默认

2 bits

8 bits

2400 bytes

9600 bytes

10

11

00

6 bits

4 bits

7200 bytes

4800 bytes

10 bits

8 bits

12000 bytes

9600 bytes

14 bits 12 bits 16800 bytes 14400 bytes

包长度可以线性测量,基于准确度(+/-25ppm would allow packets twice as large)。如果阈值设定必需支持 10Mb/s 和 100Mb/s 操作,应当设定

支持两种速率。

10.2.1 RMII 主模式

10.2.2 RMII 从模式

RMII 从模式下,DP83640 使用 50MHz 参考时钟输入 X1,参考时钟可以是外部振荡器或者另一片处于 RMII 从模式下的 DP83640。50MHz

内部被分为 25MHz,用于非 RMII 逻辑的参考时钟。从模式下 RX_CLK, TX_CLK, 和 CLK_OUT 不应用作 RMII 参考时钟,但可用于其他系统

器件。

10.3 SCMII 模式

10.4 IEEE 802.3u MII 串行管理接口

10.4.1 串行管理寄存器访问

串行管理 MII 规范定义了一组 32 个 16bit 的状态和丛植寄存器,这些寄存器可以通过管理接口引脚 MDC 和 MDIO 进行访问。参考 14 部

分寄存器块。

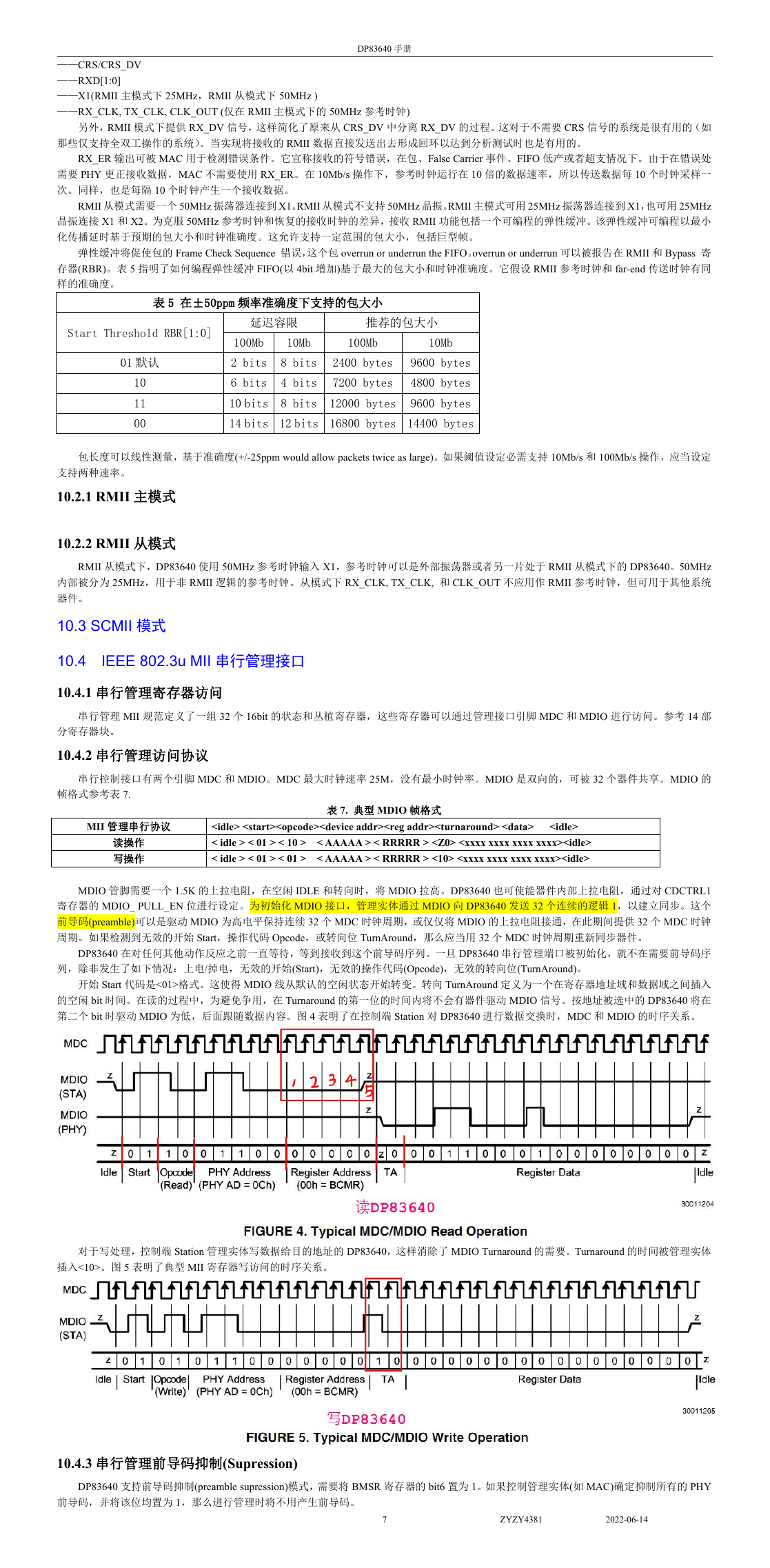

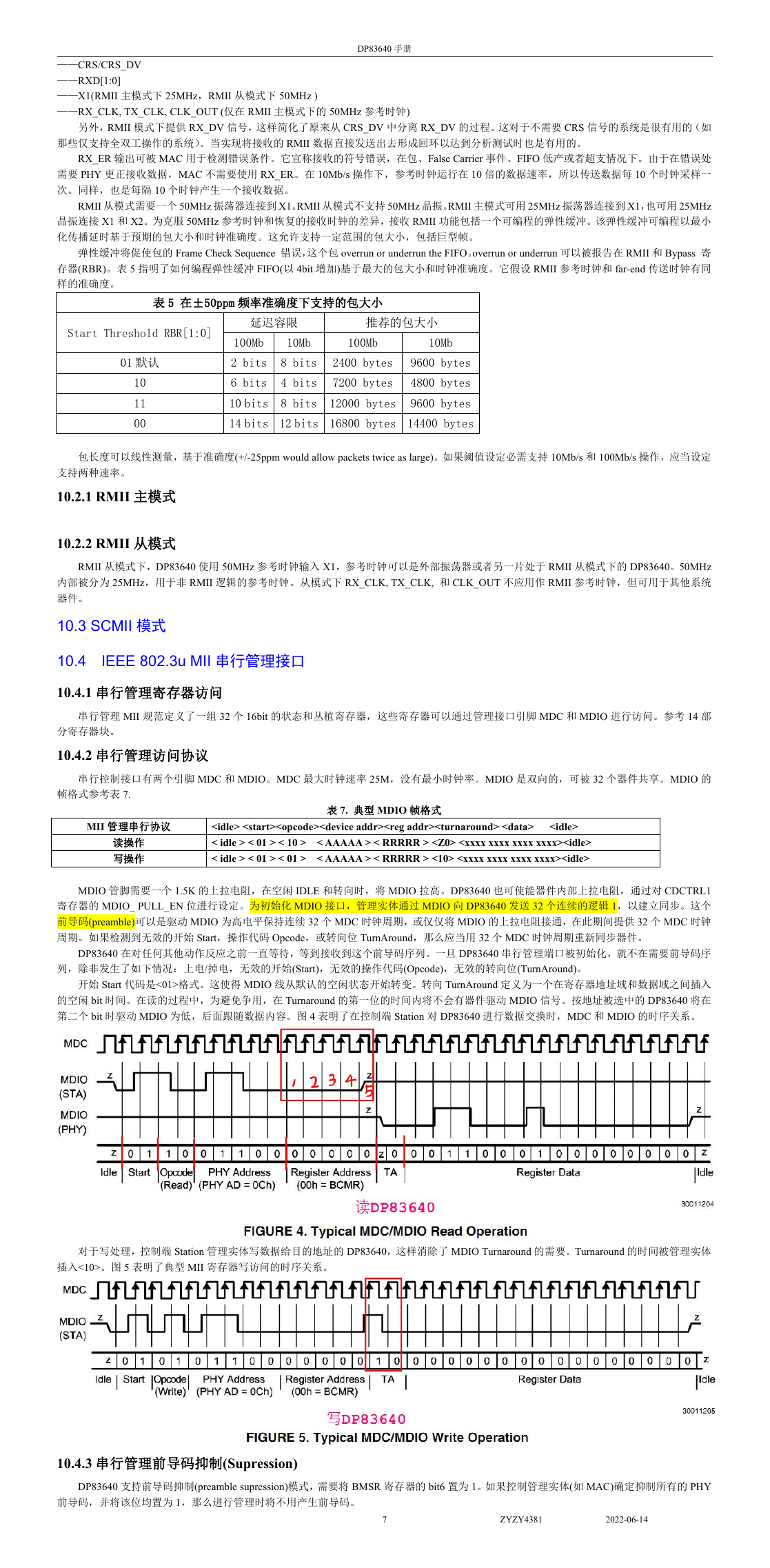

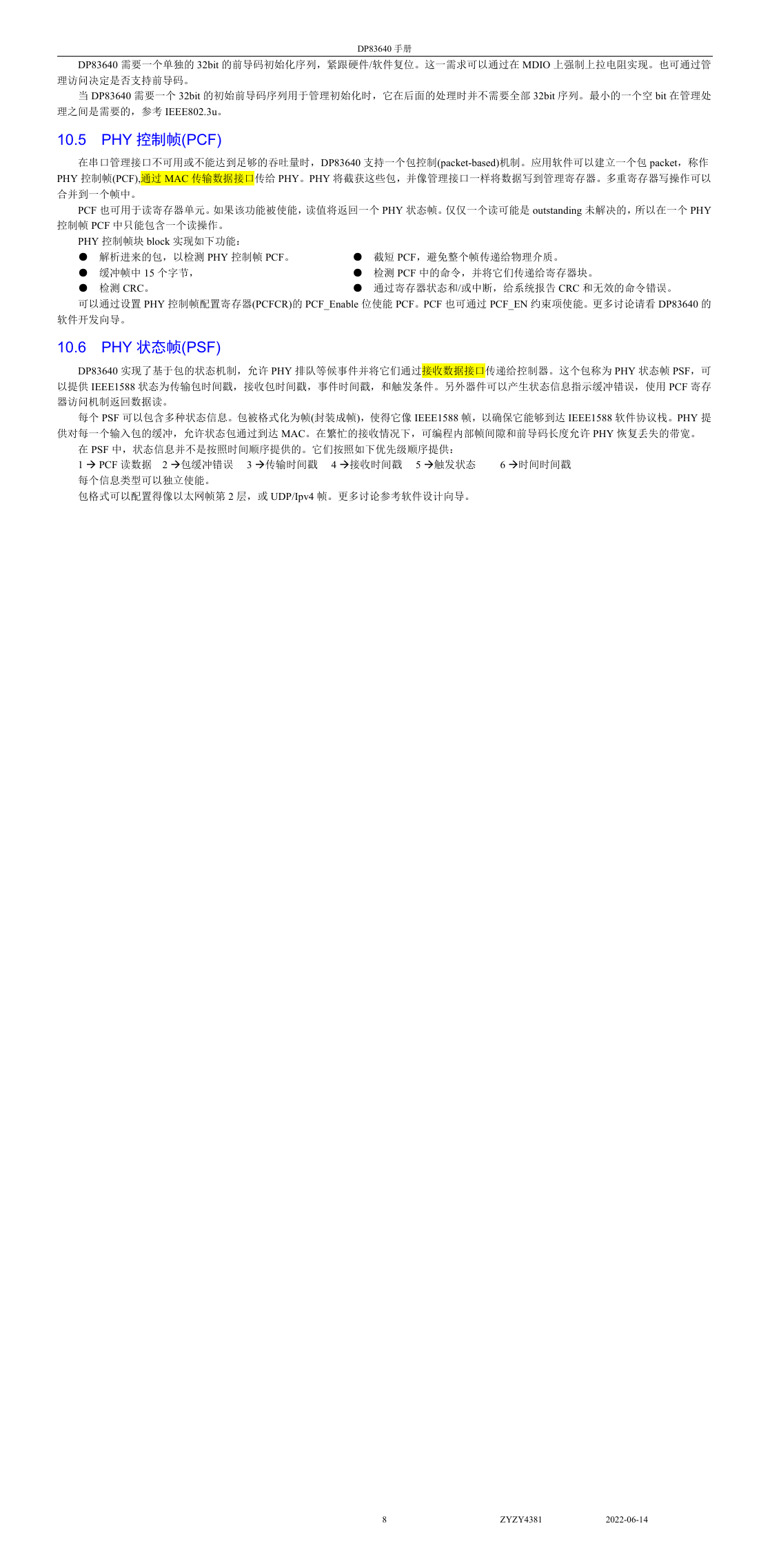

10.4.2 串行管理访问协议

串行控制接口有两个引脚 MDC 和 MDIO。MDC 最大时钟速率 25M,没有最小时钟率。MDIO 是双向的,可被 32 个器件共享。MDIO 的

帧格式参考表 7.

MII 管理串行协议

读操作

写操作

< idle > < 01 > < 10 > < AAAAA > < RRRRR >

< idle > < 01 > < 01 > < AAAAA > < RRRRR > <10>

表 7. 典型 MDIO 帧格式

MDIO 管脚需要一个 1.5K 的上拉电阻,在空闲 IDLE 和转向时,将 MDIO 拉高。DP83640 也可使能器件内部上拉电阻,通过对 CDCTRL1

寄存器的 MDIO_ PULL_EN 位进行设定。为初始化 MDIO 接口,管理实体通过 MDIO 向 DP83640 发送 32 个连续的逻辑 1,以建立同步。这个

前导码(preamble)可以是驱动 MDIO 为高电平保持连续 32 个 MDC 时钟周期,或仅仅将 MDIO 的上拉电阻接通,在此期间提供 32 个 MDC 时钟

周期。如果检测到无效的开始 Start,操作代码 Opcode,或转向位 TurnAround,那么应当用 32 个 MDC 时钟周期重新同步器件。

DP83640 在对任何其他动作反应之前一直等待,等到接收到这个前导码序列。一旦 DP83640 串行管理端口被初始化,就不在需要前导码序

列,除非发生了如下情况:上电/掉电,无效的开始(Start),无效的操作代码(Opcode),无效的转向位(TurnAround)。

开始 Start 代码是<01>格式。这使得 MDIO 线从默认的空闲状态开始转变。转向 TurnAround 定义为一个在寄存器地址域和数据域之间插入

的空闲 bit 时间。在读的过程中,为避免争用,在 Turnaround 的第一位的时间内将不会有器件驱动 MDIO 信号。按地址被选中的 DP83640 将在

第二个 bit 时驱动 MDIO 为低,后面跟随数据内容。图 4 表明了在控制端 Station 对 DP83640 进行数据交换时,MDC 和 MDIO 的时序关系。

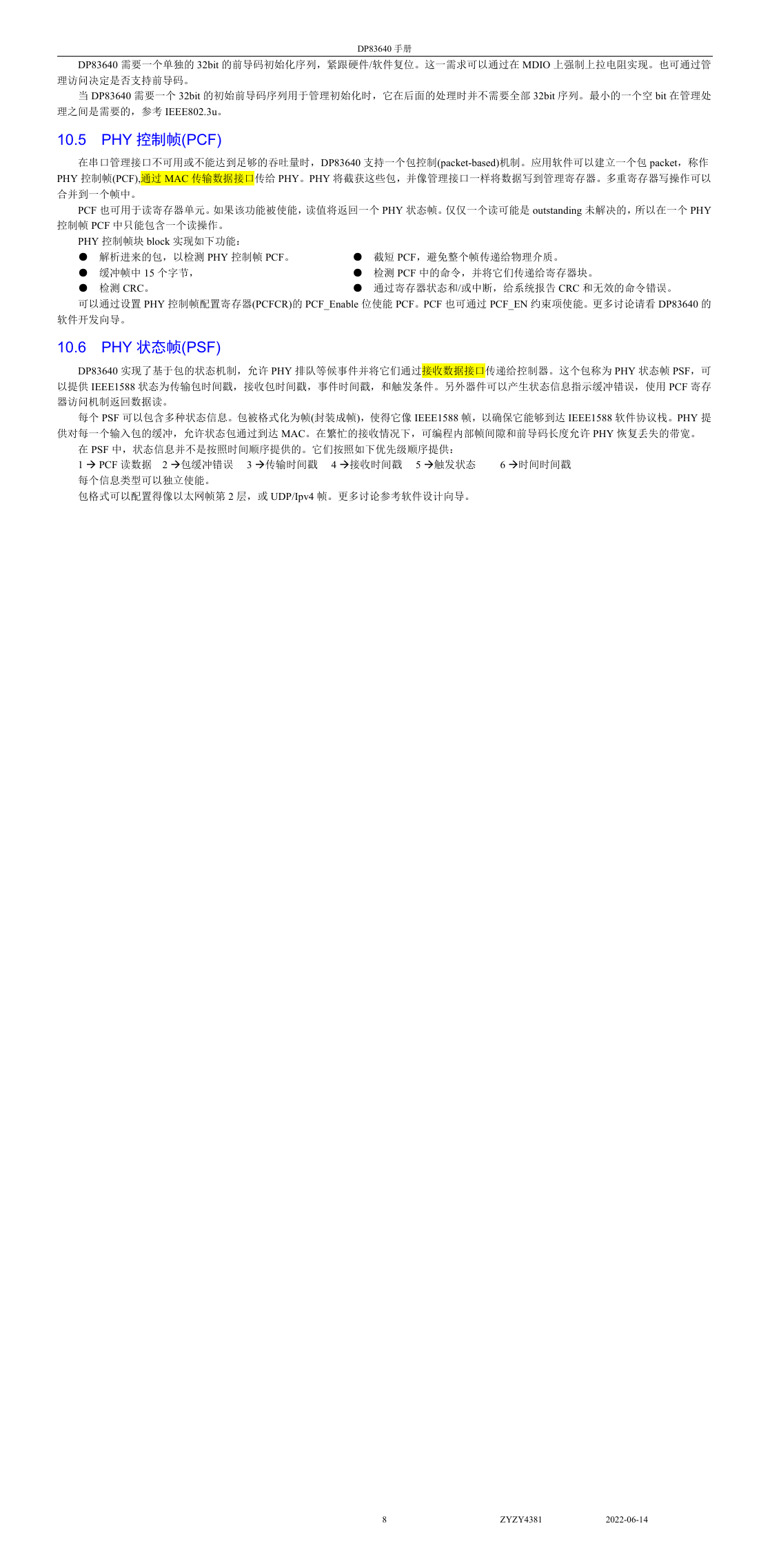

对于写处理,控制端 Station 管理实体写数据给目的地址的 DP83640,这样消除了 MDIO Turnaround 的需要。Turnaround 的时间被管理实体

插入<10>。图 5 表明了典型 MII 寄存器写访问的时序关系。

10.4.3 串行管理前导码抑制(Supression)

DP83640 支持前导码抑制(preamble supression)模式,需要将 BMSR 寄存器的 bit6 置为 1。如果控制管理实体(如 MAC)确定抑制所有的 PHY

前导码,并将该位均置为 1,那么进行管理时将不用产生前导码。

7

ZYZY4381

2022-06-14

�

DP83640 需要一个单独的 32bit 的前导码初始化序列,紧跟硬件/软件复位。这一需求可以通过在 MDIO 上强制上拉电阻实现。也可通过管

理访问决定是否支持前导码。

当 DP83640 需要一个 32bit 的初始前导码序列用于管理初始化时,它在后面的处理时并不需要全部 32bit 序列。最小的一个空 bit 在管理处

DP83640 手册

理之间是需要的,参考 IEEE802.3u。

10.5 PHY 控制帧(PCF)

在串口管理接口不可用或不能达到足够的吞吐量时,DP83640 支持一个包控制(packet-based)机制。应用软件可以建立一个包 packet,称作

PHY 控制帧(PCF),通过 MAC 传输数据接口传给 PHY。PHY 将截获这些包,并像管理接口一样将数据写到管理寄存器。多重寄存器写操作可以

合并到一个帧中。

PCF 也可用于读寄存器单元。如果该功能被使能,读值将返回一个 PHY 状态帧。仅仅一个读可能是 outstanding 未解决的,所以在一个 PHY

控制帧 PCF 中只能包含一个读操作。

PHY 控制帧块 block 实现如下功能:

● 解析进来的包,以检测 PHY 控制帧 PCF。

● 缓冲帧中 15 个字节,

● 检测 CRC。

可以通过设置 PHY 控制帧配置寄存器(PCFCR)的 PCF_Enable 位使能 PCF。PCF 也可通过 PCF_EN 约束项使能。更多讨论请看 DP83640 的

● 截短 PCF,避免整个帧传递给物理介质。

● 检测 PCF 中的命令,并将它们传递给寄存器块。

● 通过寄存器状态和/或中断,给系统报告 CRC 和无效的命令错误。

软件开发向导。

10.6 PHY 状态帧(PSF)

DP83640 实现了基于包的状态机制,允许 PHY 排队等候事件并将它们通过接收数据接口传递给控制器。这个包称为 PHY 状态帧 PSF,可

以提供 IEEE1588 状态为传输包时间戳,接收包时间戳,事件时间戳,和触发条件。另外器件可以产生状态信息指示缓冲错误,使用 PCF 寄存

器访问机制返回数据读。

每个 PSF 可以包含多种状态信息。包被格式化为帧(封装成帧),使得它像 IEEE1588 帧,以确保它能够到达 IEEE1588 软件协议栈。PHY 提

供对每一个输入包的缓冲,允许状态包通过到达 MAC。在繁忙的接收情况下,可编程内部帧间隙和前导码长度允许 PHY 恢复丢失的带宽。

在 PSF 中,状态信息并不是按照时间顺序提供的。它们按照如下优先级顺序提供:

1 PCF 读数据 2 包缓冲错误 3 传输时间戳 4 接收时间戳 5 触发状态

每个信息类型可以独立使能。

包格式可以配置得像以太网帧第 2 层,或 UDP/Ipv4 帧。更多讨论参考软件设计向导。

6 时间时间戳

8

ZYZY4381

2022-06-14

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc