操作:文档是属于实操性的文档,不会有很多图,但都是验证过的,绝对通过。

安装 git :apt_get install git

下载 u-boot 源码:https://github.com/Xilinx/u-boot-xlnx.git(在 release 中下载对应

的版本)

下载 linux kernel 源码: https://github.com/Xilinx/linux-xlnx.git(在 release 中下载对

应的版本)

下载 arm_ramdisk.image.gz 根文件系统:https://xilinx-

wiki.atlassian.net/wiki/spaces/A/pages/18842473/Build+and+Modify+a+Rootfs

管理员权限下:

source /opt/Xilinx/Vivado/2017.04/settings64.sh

制作 u-boot.elf:(CROSS_COMPILE=arm-linux-gnueabihf-参数在不同的版本

下是不同的)( zynq_zybo_defconfig 这个参数是公板信息,从./configs 文件夹中

寻找,找到于自己手中开发板一样或者相近的型号)

cd u-boot 源码

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf-

zynq_zybo_defconfig

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- (生成 uboot)

制作 uImage:

cd kernel 源码

�

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- xilinx_zynq_defconfig

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf-

make ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf-

UIMAGE_LOADADDR=0x8000 uImage(生成 uImage)

错误信息

U-Boot images will not be built

原因

apt-get install u-boot-tools(缺少这个会报错:U-Boot images will not be built)

制作 uramdisk.image.gz:(arm_ramdisk.image.gz 下载和制作的方法见文档头

部)

cd u-boot 源码

./tools/mkimage -A arm -T ramdisk -c gzip -d ../arm_ramdisk.image.gz

uramdisk.image.gz(生成 uramdisk.image.gz)

制作 devicetree.dtb:(zynq-zybo.dts 这个参数是公板信息,从./

arch/arm/boot/dts 文件夹中寻找,找到于自己手中开发板一样或者相近的型号)

cd kernel 源码

./scripts/dtc/dtc -I dts –O dtb -o devicetree.dtb arch/arm/boot/dts/zynq-zybo.dts

(生成 devicetree.dtb)

错误信息

$ ./scripts/dtc/dtc -I dts -O dtb -o devicetree.dtb ./arch/arm/boot/dts/zynq-zed.dts

Error: ./arch/arm/boot/dts/zynq-zed.dts:15.1-9 syntax error

FATAL ERROR: Unable to parse input tree

原因

根据提示,是 zynq-zed.dts 这个文件的 15 行出错。

将该行修改为 /include/ “zynq-7000.dtsi”

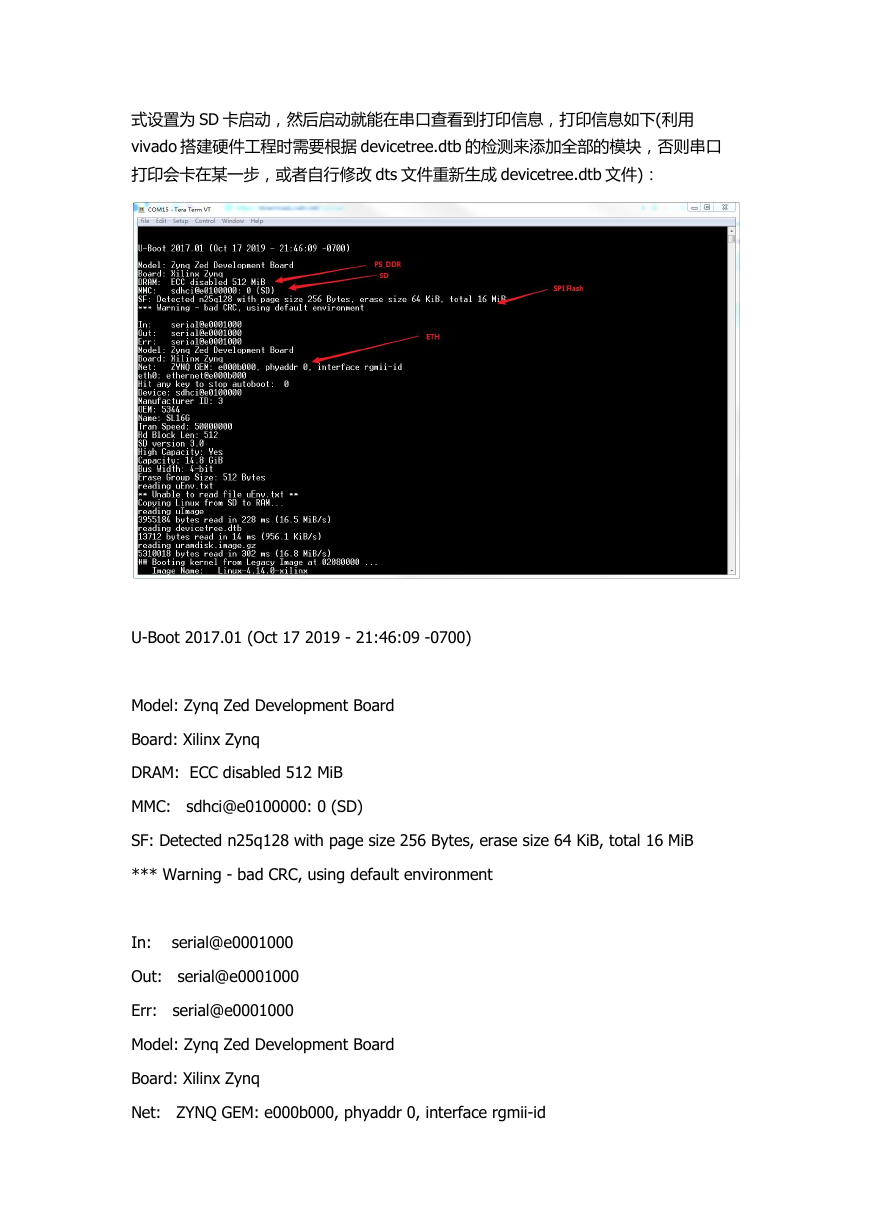

启动 zynq:

制作 BOOT.bin(网上找一下吧,这个很简单搭建完成工程后,导出硬件信息,生成

sdk,创建 BOOT.bin(加入 fsbl.elf,*.bit,之前生成的 u-boot.elf 即可)),并将

BOOT.bin,uImage,uramdisk.image.gz,devicetree.dtb 拷贝进入 sd 卡中将启动方

�

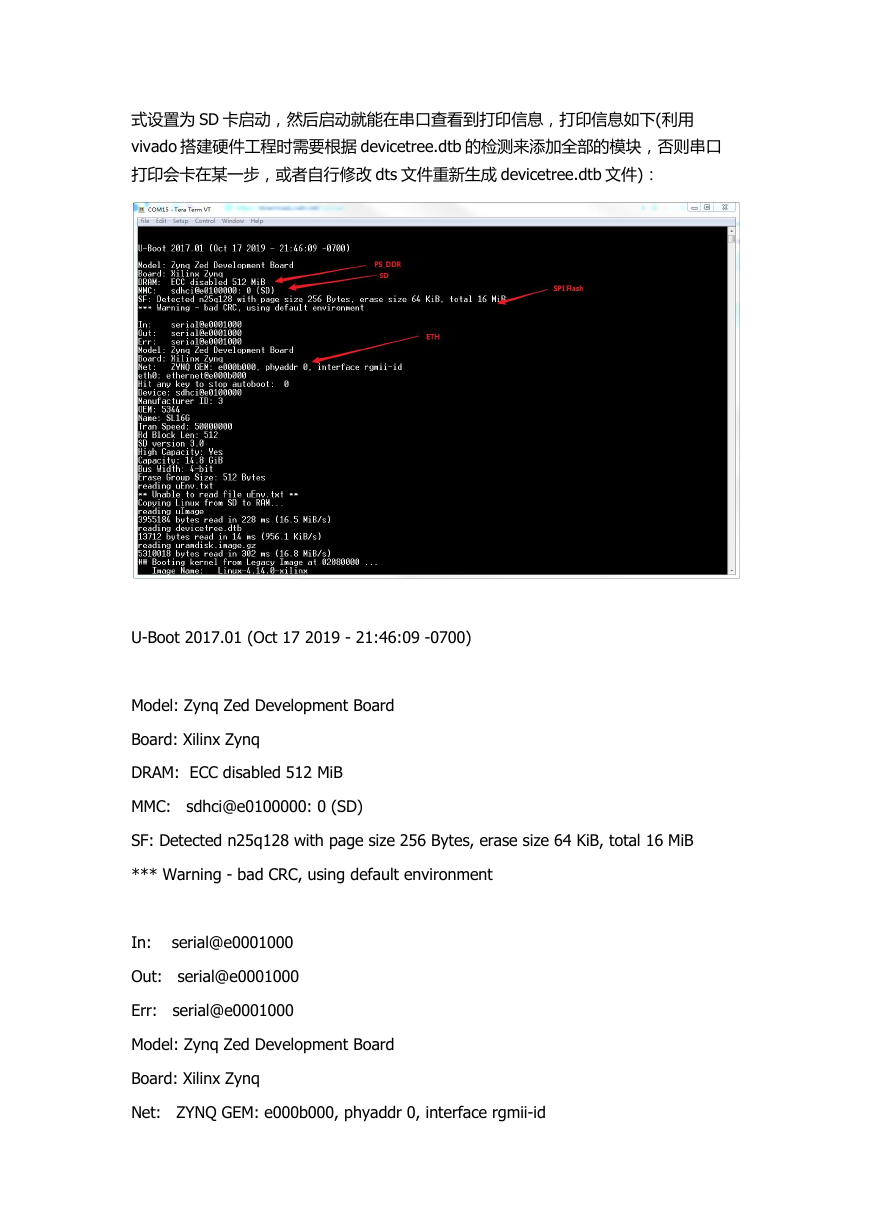

式设置为 SD 卡启动,然后启动就能在串口查看到打印信息,打印信息如下(利用

vivado 搭建硬件工程时需要根据 devicetree.dtb 的检测来添加全部的模块,否则串口

打印会卡在某一步,或者自行修改 dts 文件重新生成 devicetree.dtb 文件):

U-Boot 2017.01 (Oct 17 2019 - 21:46:09 -0700)

Model: Zynq Zed Development Board

Board: Xilinx Zynq

DRAM: ECC disabled 512 MiB

MMC:

SF: Detected n25q128 with page size 256 Bytes, erase size 64 KiB, total 16 MiB

*** Warning - bad CRC, using default environment

sdhci@e0100000: 0 (SD)

serial@e0001000

serial@e0001000

serial@e0001000

In:

Out:

Err:

Model: Zynq Zed Development Board

Board: Xilinx Zynq

Net: ZYNQ GEM: e000b000, phyaddr 0, interface rgmii-id

�

eth0: ethernet@e000b000

Hit any key to stop autoboot: 0

Device: sdhci@e0100000

Manufacturer ID: 3

OEM: 5344

Name: SL16G

Tran Speed: 50000000

Rd Block Len: 512

SD version 3.0

High Capacity: Yes

Capacity: 14.8 GiB

Bus Width: 4-bit

Erase Group Size: 512 Bytes

reading uEnv.txt

** Unable to read file uEnv.txt **

Copying Linux from SD to RAM...

reading uImage

3955184 bytes read in 228 ms (16.5 MiB/s)

reading devicetree.dtb

13712 bytes read in 14 ms (956.1 KiB/s)

reading uramdisk.image.gz

5310018 bytes read in 302 ms (16.8 MiB/s)

## Booting kernel from Legacy Image at 02080000 ...

3955120 Bytes = 3.8 MiB

Image Name: Linux-4.14.0-xilinx

Image Type: ARM Linux Kernel Image (uncompressed)

Data Size:

Load Address: 00008000

Entry Point: 00008000

Verifying Checksum ... OK

## Loading init Ramdisk from Legacy Image at 04000000 ...

�

5309954 Bytes = 5.1 MiB

Image Name:

Image Type: ARM Linux RAMDisk Image (gzip compressed)

Data Size:

Load Address: 00000000

Entry Point: 00000000

Verifying Checksum ... OK

## Flattened Device Tree blob at 02000000

Booting using the fdt blob at 0x2000000

Loading Kernel Image ... OK

Loading Ramdisk to 1e614000, end 1eb24602 ... OK

Loading Device Tree to 1e60d000, end 1e61358f ... OK

Starting kernel ...

Booting Linux on physical CPU 0x0

Linux version 4.14.0-xilinx (root@ubuntu) (gcc version 6.2.1 20161114 (Linaro GCC

Snapshot 6.2-2016.11)) #1 SMP PREEMPT Wed Oct 16 20:05:41 PDT 2019

CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=18c5387d

CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

OF: fdt: Machine model: Zynq ZC706 Development Board

Memory policy: Data cache writealloc

cma: Reserved 16 MiB at 0x1f000000

percpu: Embedded 16 pages/cpu @debc3000 s34764 r8192 d22580 u65536

Built 1 zonelists, mobility grouping on. Total pages: 130048

Kernel command line:

PID hash table entries: 2048 (order: 1, 8192 bytes)

Dentry cache hash table entries: 65536 (order: 6, 262144 bytes)

Inode-cache hash table entries: 32768 (order: 5, 131072 bytes)

Memory: 487852K/524288K available (6144K kernel code, 238K rwdata, 1560K

rodata, 1024K init, 153K bss, 20052K reserved, 16384K cma-reserved, 0K highmem)

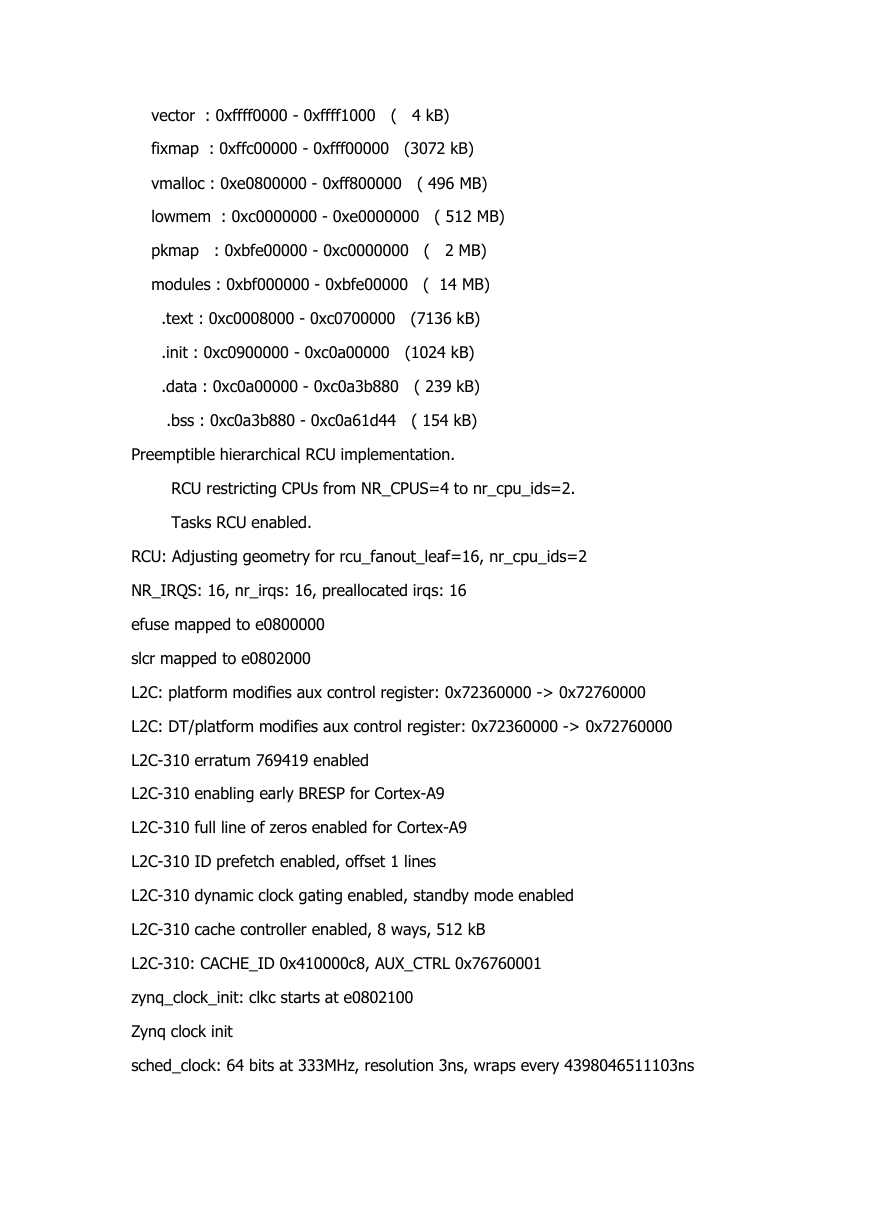

Virtual kernel memory layout:

�

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

vmalloc : 0xe0800000 - 0xff800000 ( 496 MB)

lowmem : 0xc0000000 - 0xe0000000 ( 512 MB)

pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

.text : 0xc0008000 - 0xc0700000 (7136 kB)

.init : 0xc0900000 - 0xc0a00000 (1024 kB)

.data : 0xc0a00000 - 0xc0a3b880 ( 239 kB)

.bss : 0xc0a3b880 - 0xc0a61d44 ( 154 kB)

Preemptible hierarchical RCU implementation.

RCU restricting CPUs from NR_CPUS=4 to nr_cpu_ids=2.

Tasks RCU enabled.

RCU: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2

NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

efuse mapped to e0800000

slcr mapped to e0802000

L2C: platform modifies aux control register: 0x72360000 -> 0x72760000

L2C: DT/platform modifies aux control register: 0x72360000 -> 0x72760000

L2C-310 erratum 769419 enabled

L2C-310 enabling early BRESP for Cortex-A9

L2C-310 full line of zeros enabled for Cortex-A9

L2C-310 ID prefetch enabled, offset 1 lines

L2C-310 dynamic clock gating enabled, standby mode enabled

L2C-310 cache controller enabled, 8 ways, 512 kB

L2C-310: CACHE_ID 0x410000c8, AUX_CTRL 0x76760001

zynq_clock_init: clkc starts at e0802100

Zynq clock init

sched_clock: 64 bits at 333MHz, resolution 3ns, wraps every 4398046511103ns

�

clocksource: arm_global_timer: mask: 0xffffffffffffffff max_cycles: 0x4ce07af025,

max_idle_ns: 440795209040 ns

Switching to timer-based delay loop, resolution 3ns

clocksource: ttc_clocksource: mask: 0xffff max_cycles: 0xffff, max_idle_ns:

537538477 ns

timer #0 at e080a000, irq=17

Console: colour dummy device 80x30

console [tty0] enabled

Calibrating delay loop (skipped), value calculated using timer frequency.. 666.66

BogoMIPS (lpj=3333333)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

CPU: Testing write buffer coherency: ok

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x100000 - 0x100060

Hierarchical SRCU implementation.

smp: Bringing up secondary CPUs ...

CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

smp: Brought up 1 node, 2 CPUs

SMP: Total of 2 processors activated (1333.33 BogoMIPS).

CPU: All CPU(s) started in SVC mode.

devtmpfs: initialized

random: get_random_u32 called from bucket_table_alloc+0x1e0/0x220 with

crng_init=0

VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns:

19112604462750000 ns

futex hash table entries: 512 (order: 3, 32768 bytes)

pinctrl core: initialized pinctrl subsystem

NET: Registered protocol family 16

random: fast init done

�

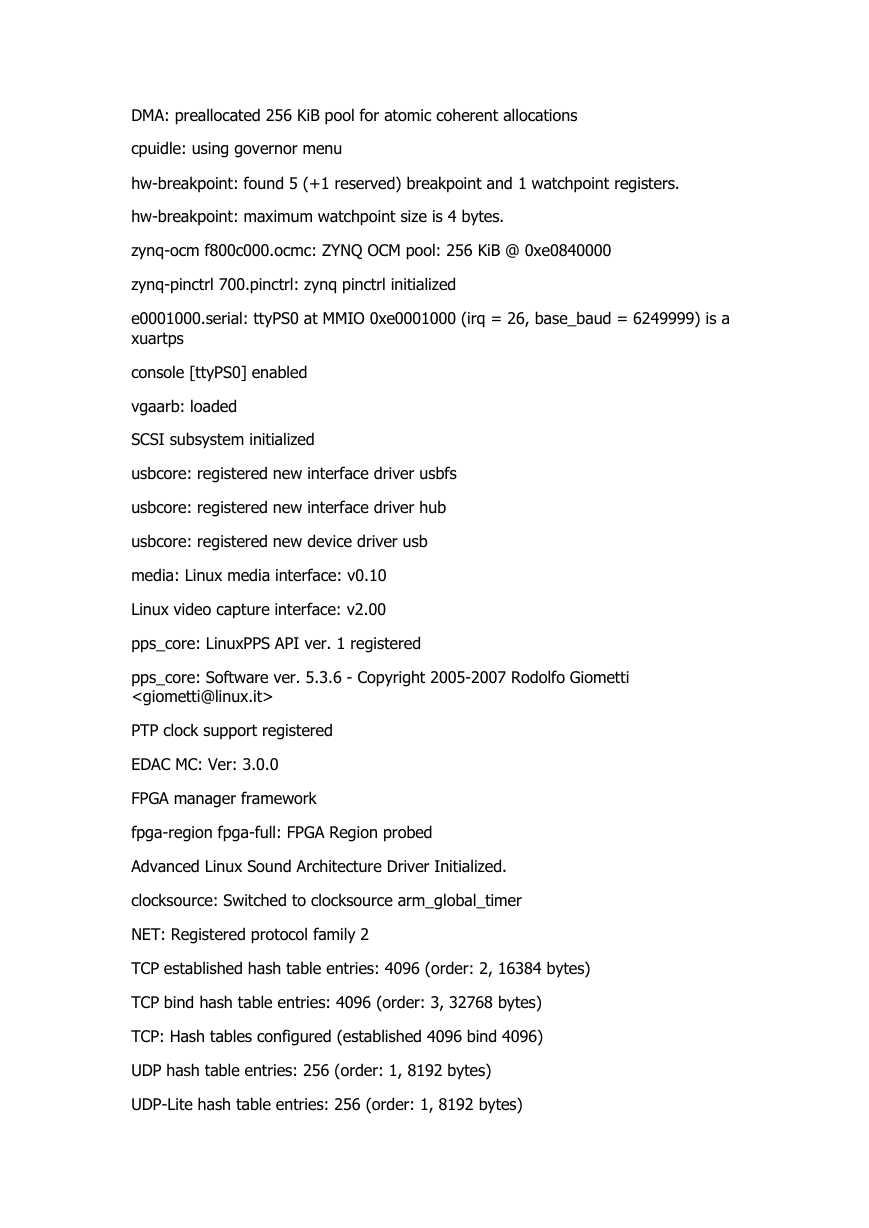

DMA: preallocated 256 KiB pool for atomic coherent allocations

cpuidle: using governor menu

hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

hw-breakpoint: maximum watchpoint size is 4 bytes.

zynq-ocm f800c000.ocmc: ZYNQ OCM pool: 256 KiB @ 0xe0840000

zynq-pinctrl 700.pinctrl: zynq pinctrl initialized

e0001000.serial: ttyPS0 at MMIO 0xe0001000 (irq = 26, base_baud = 6249999) is a

xuartps

console [ttyPS0] enabled

vgaarb: loaded

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

media: Linux media interface: v0.10

Linux video capture interface: v2.00

pps_core: LinuxPPS API ver. 1 registered

pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti

PTP clock support registered

EDAC MC: Ver: 3.0.0

FPGA manager framework

fpga-region fpga-full: FPGA Region probed

Advanced Linux Sound Architecture Driver Initialized.

clocksource: Switched to clocksource arm_global_timer

NET: Registered protocol family 2

TCP established hash table entries: 4096 (order: 2, 16384 bytes)

TCP bind hash table entries: 4096 (order: 3, 32768 bytes)

TCP: Hash tables configured (established 4096 bind 4096)

UDP hash table entries: 256 (order: 1, 8192 bytes)

UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc