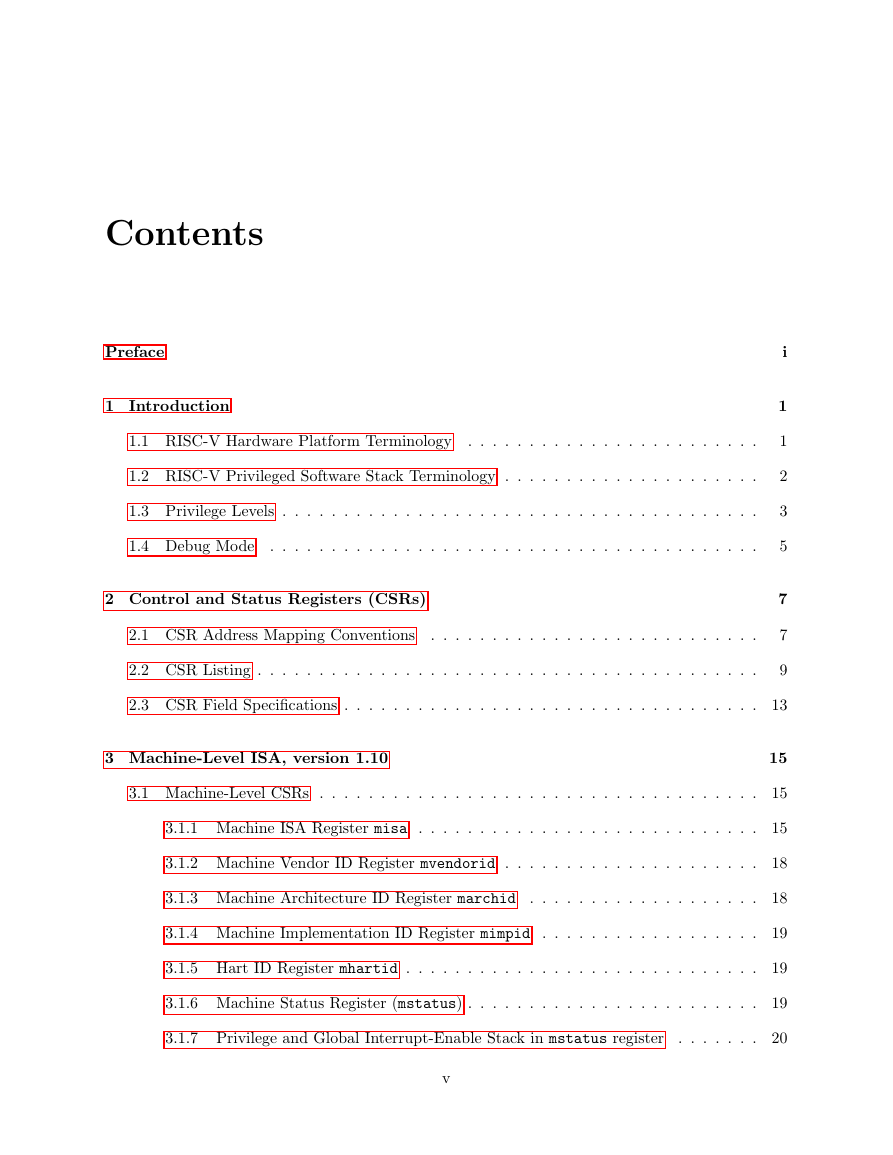

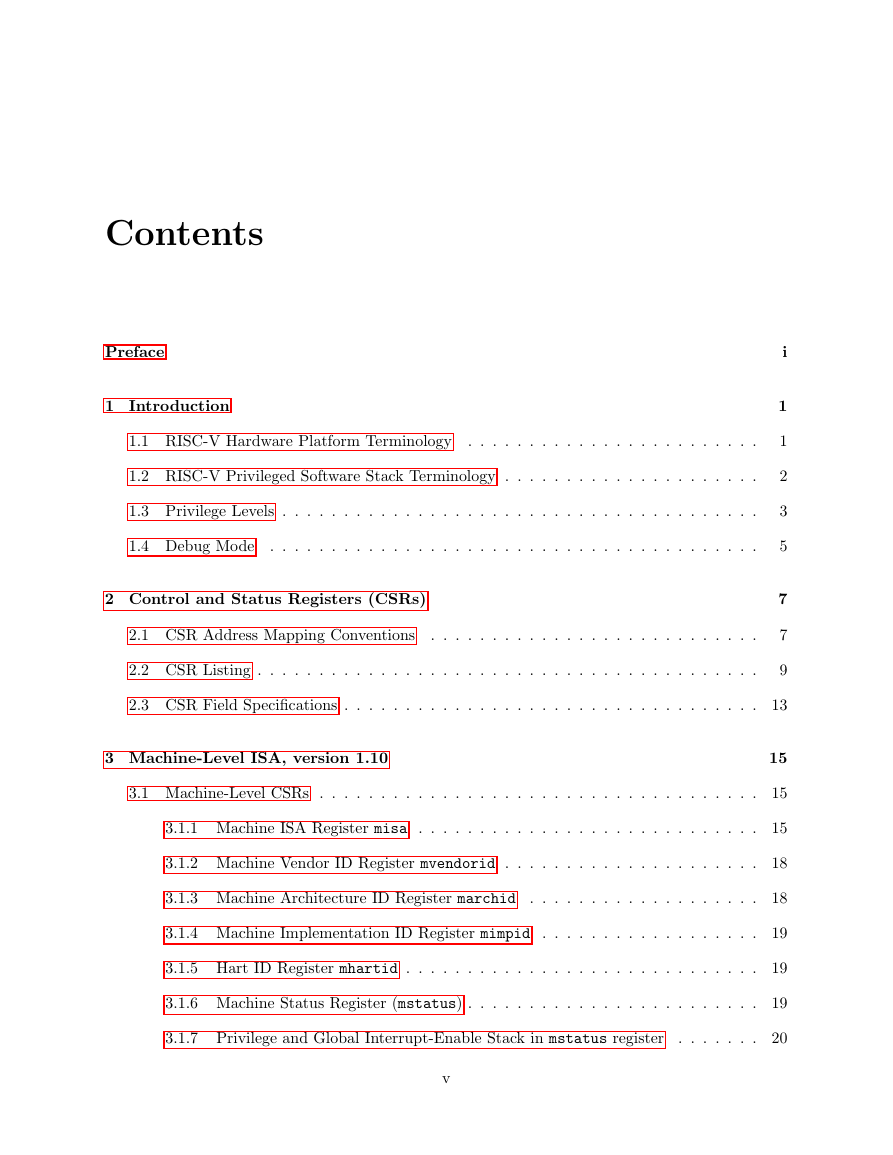

Preface

Introduction

RISC-V Hardware Platform Terminology

RISC-V Privileged Software Stack Terminology

Privilege Levels

Debug Mode

Control and Status Registers (CSRs)

CSR Address Mapping Conventions

CSR Listing

CSR Field Specifications

Machine-Level ISA, version 1.10

Machine-Level CSRs

Machine ISA Register misa

Machine Vendor ID Register mvendorid

Machine Architecture ID Register marchid

Machine Implementation ID Register mimpid

Hart ID Register mhartid

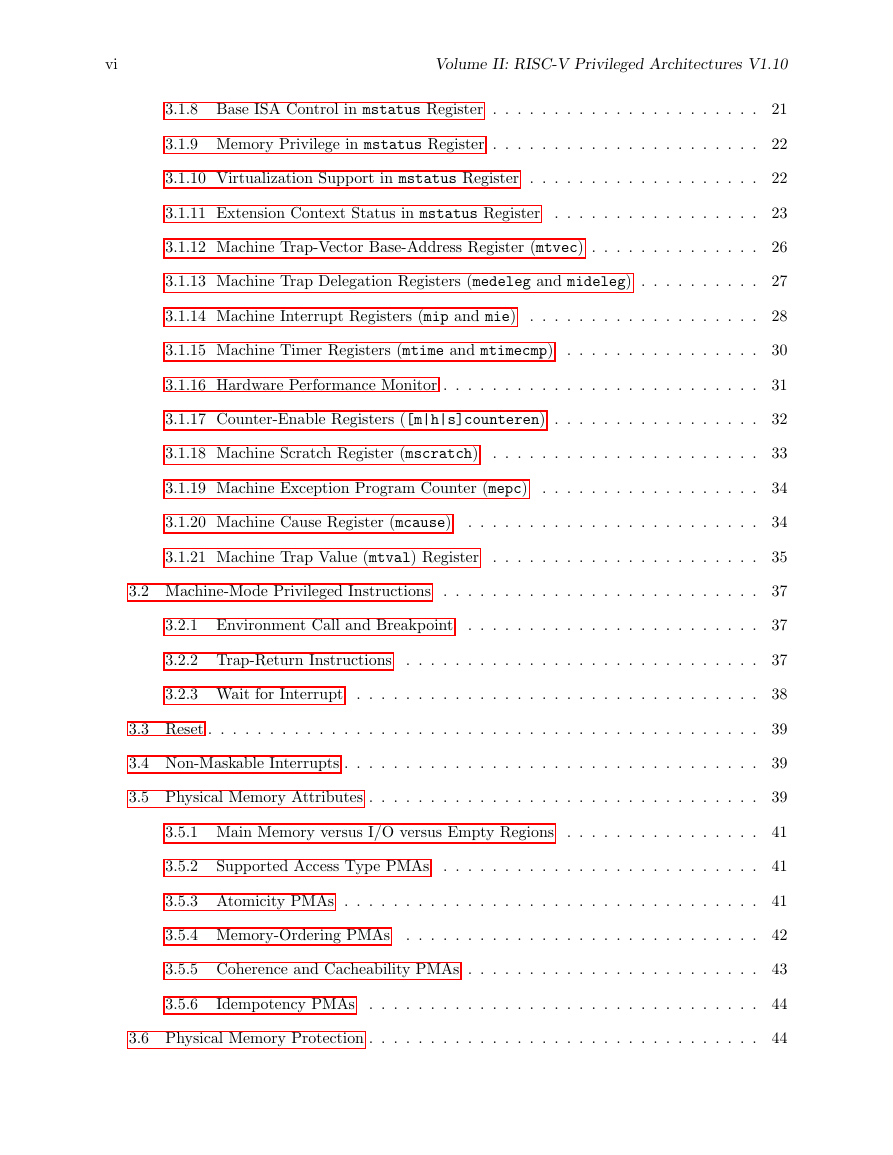

Machine Status Register (mstatus)

Privilege and Global Interrupt-Enable Stack in mstatus register

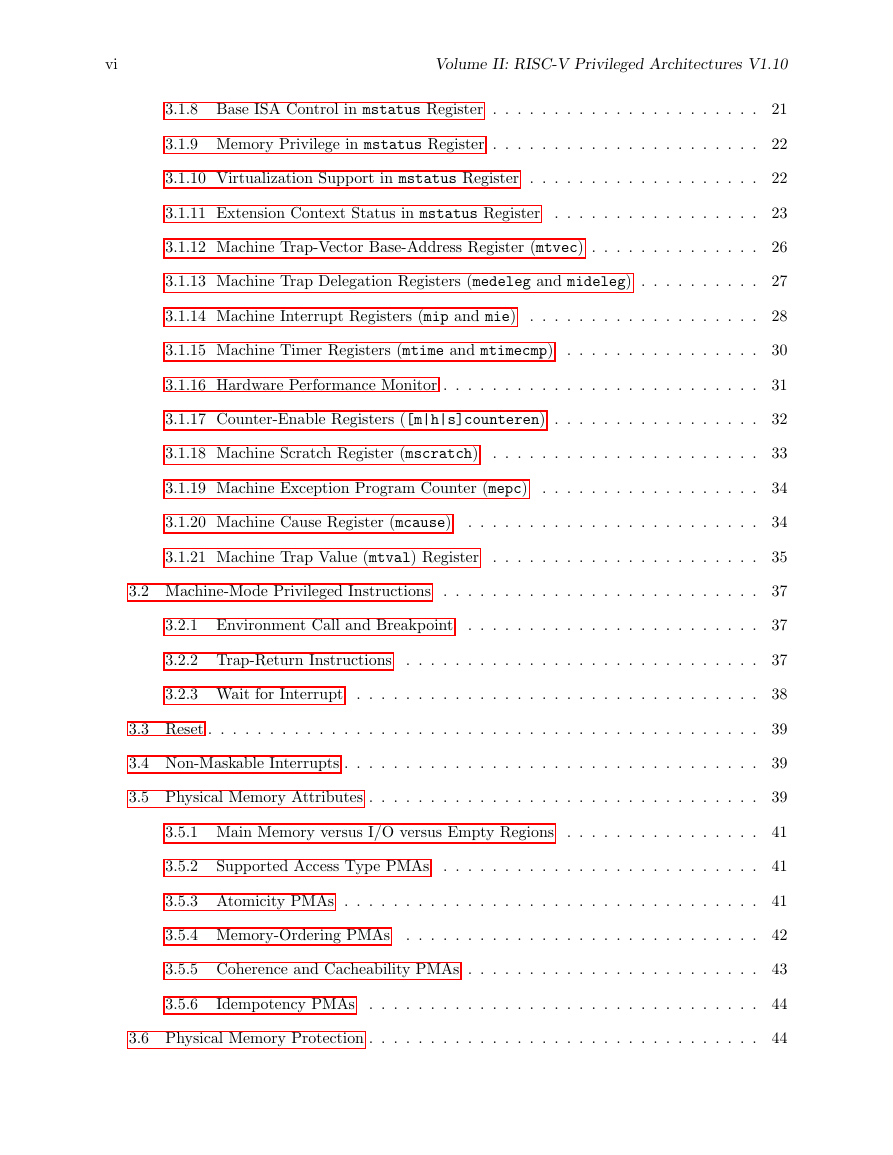

Base ISA Control in mstatus Register

Memory Privilege in mstatus Register

Virtualization Support in mstatus Register

Extension Context Status in mstatus Register

Machine Trap-Vector Base-Address Register (mtvec)

Machine Trap Delegation Registers (medeleg and mideleg)

Machine Interrupt Registers (mip and mie)

Machine Timer Registers (mtime and mtimecmp)

Hardware Performance Monitor

Counter-Enable Registers ([m|h|s]counteren)

Machine Scratch Register (mscratch)

Machine Exception Program Counter (mepc)

Machine Cause Register (mcause)

Machine Trap Value (mtval) Register

Machine-Mode Privileged Instructions

Environment Call and Breakpoint

Trap-Return Instructions

Wait for Interrupt

Reset

Non-Maskable Interrupts

Physical Memory Attributes

Main Memory versus I/O versus Empty Regions

Supported Access Type PMAs

Atomicity PMAs

Memory-Ordering PMAs

Coherence and Cacheability PMAs

Idempotency PMAs

Physical Memory Protection

Physical Memory Protection CSRs

Supervisor-Level ISA, Version 1.10

Supervisor CSRs

Supervisor Status Register (sstatus)

Base ISA Control in sstatus Register

Memory Privilege in sstatus Register

Supervisor Trap Vector Base Address Register (stvec)

Supervisor Interrupt Registers (sip and sie)

Supervisor Timers and Performance Counters

Counter-Enable Register (scounteren)

Supervisor Scratch Register (sscratch)

Supervisor Exception Program Counter (sepc)

Supervisor Cause Register (scause)

Supervisor Trap Value (stval) Register

Supervisor Address Translation and Protection (satp) Register

Supervisor Instructions

Supervisor Memory-Management Fence Instruction

Sv32: Page-Based 32-bit Virtual-Memory Systems

Addressing and Memory Protection

Virtual Address Translation Process

Sv39: Page-Based 39-bit Virtual-Memory System

Addressing and Memory Protection

Sv48: Page-Based 48-bit Virtual-Memory System

Addressing and Memory Protection

Hypervisor Extensions, Version 0.0

RISC-V Privileged Instruction Set Listings

Platform-Level Interrupt Controller (PLIC)

PLIC Overview

Interrupt Sources

Local Interrupt Sources

Global Interrupt Sources

Interrupt Targets and Hart Contexts

Interrupt Gateways

Interrupt Identifiers (IDs)

Interrupt Priorities

Interrupt Enables

Interrupt Priority Thresholds

Interrupt Notifications

Interrupt Claims

Interrupt Completion

Interrupt Flow

PLIC Core Specification

Controlling Access to the PLIC

Machine Configuration Description

Configuration String Search Procedure

History

Research Funding at UC Berkeley

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc