GD32F4xx 系列硬件开发指南

GigaDevice Semiconductor Inc.

GD32F4xx 系列硬件开发指南

ARM® Cortex™-M4 32-bit MCU

1.0 版本

( 2019 年 12 月)

1

�

GD32F4xx 系列硬件开发指南

目 录

目 录 ..................................................................................................................................... 2

图索引 ................................................................................................................................... 3

表索引 ................................................................................................................................... 4

1. 前言 ................................................................................................................................ 5

2. 硬件设计 ......................................................................................................................... 6

2.1. 电源 .................................................................................................................................... 6

2.1.1. 备份域 ................................................................................................................................................... 6

VDD/VDDA 电源域 ................................................................................................................................... 7

2.1.2.

2.1.3. 供电设计 ............................................................................................................................................... 7

2.1.4. 复位及电源管理 ................................................................................................................................... 8

2.2. 时钟 .................................................................................................................................. 12

2.2.1. 外部高速晶体振荡时钟(HXTAL) ................................................................................................. 13

2.2.2. 外部低速晶体振荡时钟(LXTAL) ................................................................................................. 14

2.2.3. 时钟输出能力(CKOUT) ............................................................................................................... 15

HXTAL 时钟监视器(CKM) ........................................................................................................... 16

2.2.4.

PLL 展频(SSCG) .......................................................................................................................... 16

2.2.5.

2.3. 启动配置 ........................................................................................................................... 17

2.4. 典型外设模块 .................................................................................................................... 18

2.4.1. GPIO 电路 .......................................................................................................................................... 18

ADC 电路 ........................................................................................................................................... 19

2.4.2.

DAC 电路 ........................................................................................................................................... 20

2.4.3.

USB 电路 ............................................................................................................................................ 21

2.4.4.

Standby 模式唤醒电路 ..................................................................................................................... 22

2.4.5.

2.5. 下载调试电路 .................................................................................................................... 22

2.6. 参考原理图设计 ................................................................................................................ 25

3. PCB Layout 设计 ........................................................................................................ 26

3.1. 电源去耦电容 .................................................................................................................... 26

3.2. 时钟电路 ........................................................................................................................... 26

3.3. 复位电路 ........................................................................................................................... 27

3.4. USB 电路 ........................................................................................................................... 28

4. 封装说明 ....................................................................................................................... 29

5. 版本历史 ....................................................................................................................... 30

2

�

GD32F4xx 系列硬件开发指南

图索引

图 2-1. GD32F4xx 系列电源域概览 .................................................................................................................... 6

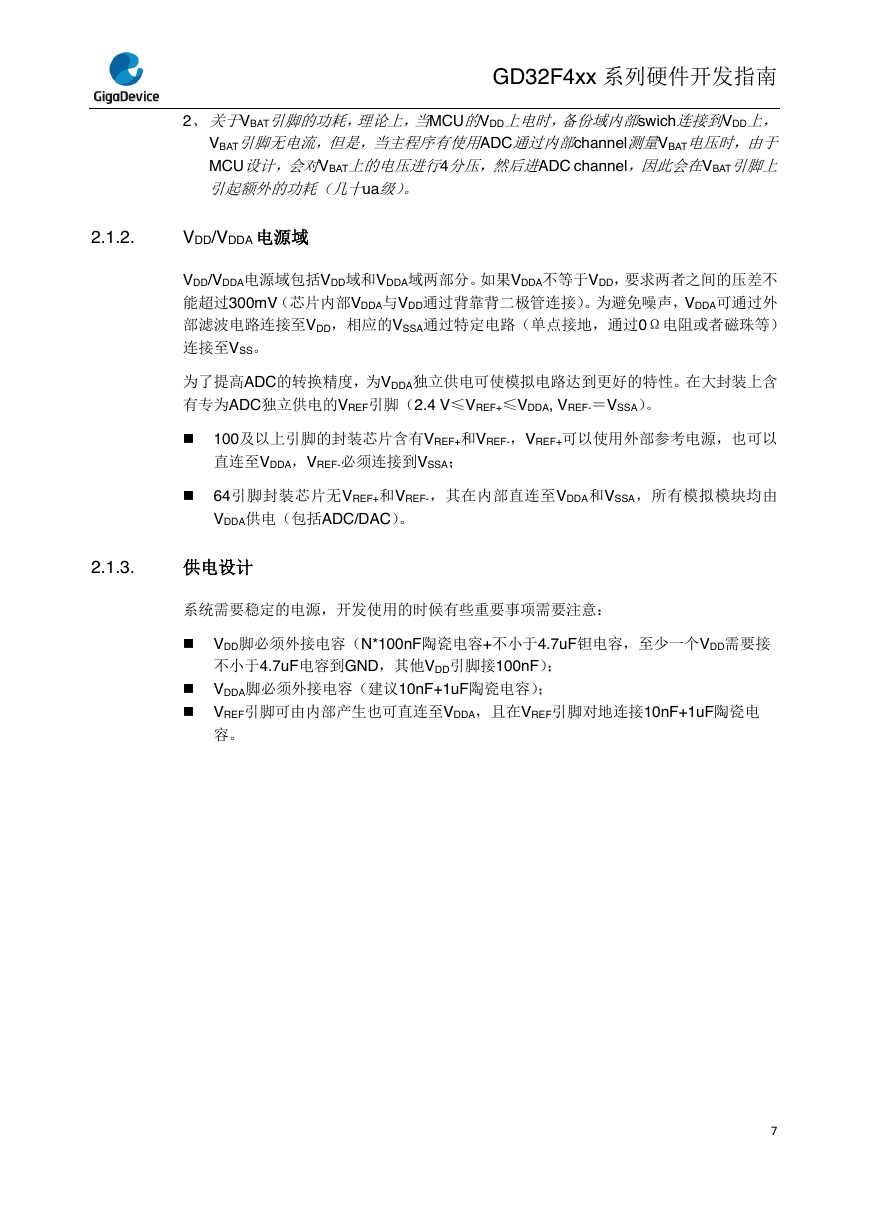

图 2-2. GD32F4xx 系列推荐供电设计 ................................................................................................................. 8

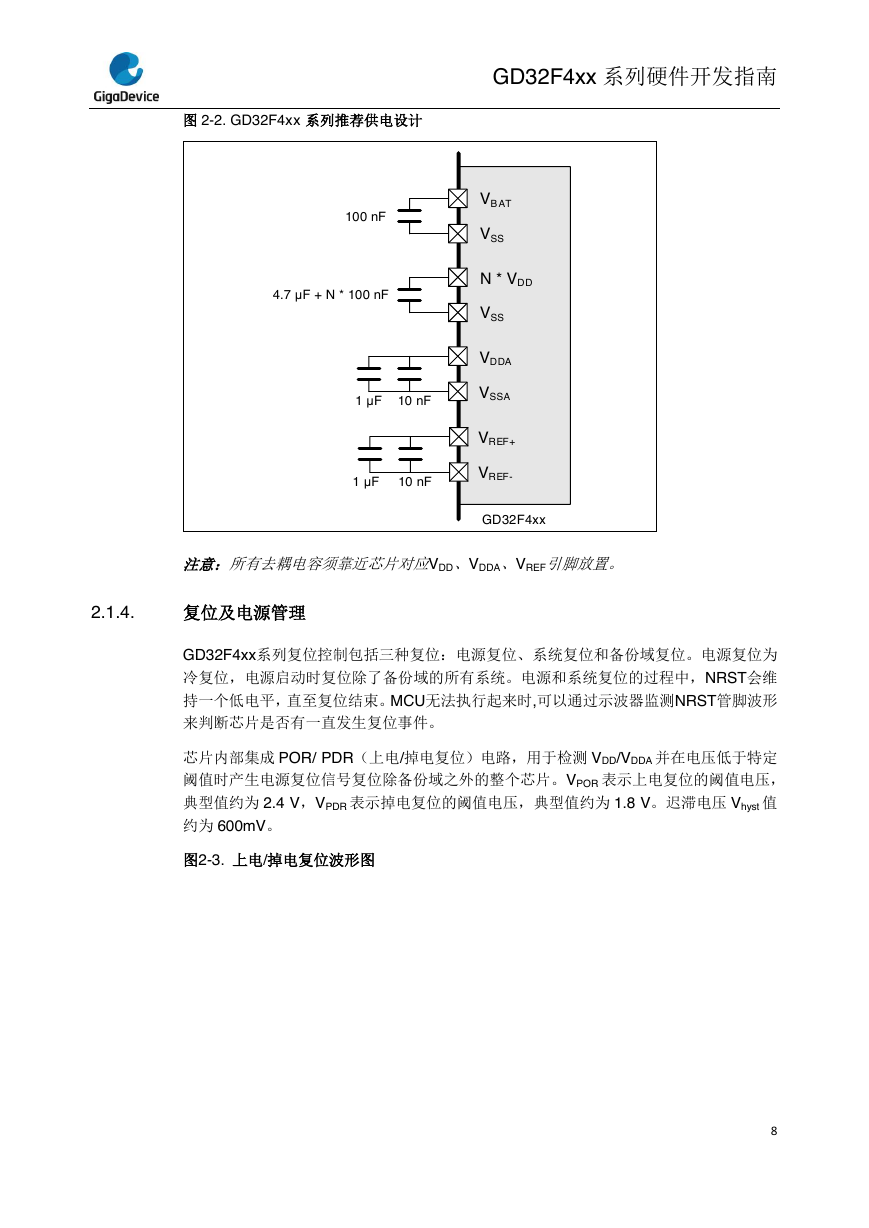

图 2-3. 上电/掉电复位波形图 .............................................................................................................................. 8

图 2-4. LVD 阈值波形图 ....................................................................................................................................... 9

图 2-5. BOR 阈值波形图 .................................................................................................................................... 10

图 2-6. 推荐 PDR_ON 引脚电路设计 ................................................................................................................ 11

图 2-7. RCU_RSTSCK 寄存器 .......................................................................................................................... 11

图 2-8. 系统复位电路 ......................................................................................................................................... 11

图 2-9. 推荐外部复位电路 ................................................................................................................................. 12

图 2-10. 时钟树 .................................................................................................................................................. 13

图 2-11 HXTAL 外部晶体电路 ............................................................................................................................ 14

图 2-12 HXTAL 外部时钟电路 ........................................................................................................................... 14

图 2-13. LXTAL 外部晶体电路 ........................................................................................................................... 15

图 2-14. LXTAL 外部时钟电路 ........................................................................................................................... 15

图 2-15. 中心扩频方式展频 ............................................................................................................................... 17

图 2-16. 向下扩频方式展频 ............................................................................................................................... 17

图 2-17. 推荐 BOOT 电路设计 .......................................................................................................................... 18

图 2-18. 标准 IO 的基本结构 ............................................................................................................................. 19

图 2-19. ADC 采集电路设计 ............................................................................................................................... 20

图 2-20. 推荐 USB-Device 参考电路 ............................................................................................................... 21

图 2-21. 推荐 USB-Host 参考电路 ................................................................................................................... 22

图 2-22. 推荐 Standby 外部唤醒引脚电路设计 ............................................................................................... 22

图 2-23. 推荐 JTAG 接线参考设计 ................................................................................................................... 23

图 2-24. 推荐 SWD 接线参考设计 .................................................................................................................... 24

图 2-25. GD32F4xx 推荐参考原理图设计 ......................................................................................................... 25

图 2-1. 推荐电源引脚去耦 Layout 设计 ........................................................................................................... 26

图 3-2. 推荐时钟引脚 Layout 设计(无源晶体) ............................................................................................ 27

图 3-3. 推荐 NRST 走线 Layout 设计 .............................................................................................................. 27

图 3-4. 推荐 DM、DP 差分走线 Layout 设计 .................................................................................................. 28

图 3-5. 推荐 MCU 与 PHY Layout 设计 ........................................................................................................... 29

3

�

GD32F4xx 系列硬件开发指南

表索引

表 1-1. 适用产品 .................................................................................................................................................. 5

表 2-1. VBOR 阈值电压设置 .............................................................................................................................. 10

表 2-2. CKOUT0SEL[1:0]控制位 ...................................................................................................................... 16

表 2-3. CKOUT1SEL[1:0]控制位 ...................................................................................................................... 16

表 2-4. BOOT 模式 ............................................................................................................................................. 18

表 2-5. fADC=40MHz 采样周期与外部输入阻抗关系 ........................................................................................ 20

表 2-6. DAC 相关引脚描述 ................................................................................................................................. 20

表 2-7. JTAG 下载调试接口分配 ....................................................................................................................... 23

表 2-8. SWD 下载调试接口分配 ........................................................................................................................ 24

表 4-1. 封装型号说明 ........................................................................................................................................ 30

表 5-1. 版本历史 ................................................................................................................................................ 30

4

�

GD32F4xx 系列硬件开发指南

1. 前言

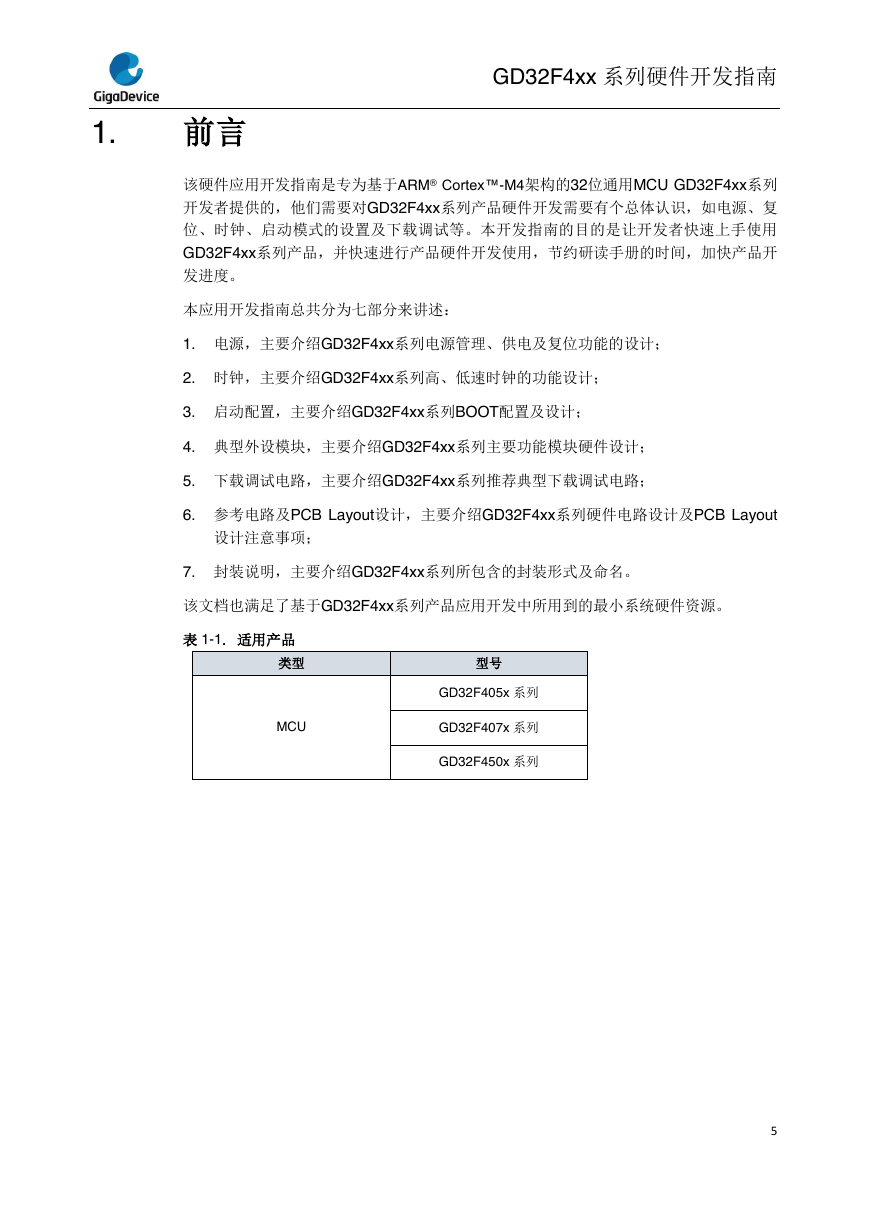

该硬件应用开发指南是专为基于ARM® Cortex™-M4架构的32位通用MCU GD32F4xx系列

开发者提供的,他们需要对GD32F4xx系列产品硬件开发需要有个总体认识,如电源、复

位、时钟、启动模式的设置及下载调试等。本开发指南的目的是让开发者快速上手使用

GD32F4xx系列产品,并快速进行产品硬件开发使用,节约研读手册的时间,加快产品开

发进度。

本应用开发指南总共分为七部分来讲述:

1. 电源,主要介绍GD32F4xx系列电源管理、供电及复位功能的设计;

2. 时钟,主要介绍GD32F4xx系列高、低速时钟的功能设计;

3. 启动配置,主要介绍GD32F4xx系列BOOT配置及设计;

4. 典型外设模块,主要介绍GD32F4xx系列主要功能模块硬件设计;

5. 下载调试电路,主要介绍GD32F4xx系列推荐典型下载调试电路;

6. 参考电路及PCB Layout设计,主要介绍GD32F4xx系列硬件电路设计及PCB Layout

设计注意事项;

7. 封装说明,主要介绍GD32F4xx系列所包含的封装形式及命名。

该文档也满足了基于GD32F4xx系列产品应用开发中所用到的最小系统硬件资源。

表 1-1. 适用产品

类型

MCU

型号

GD32F405x 系列

GD32F407x 系列

GD32F450x 系列

5

�

GD32F4xx 系列硬件开发指南

2. 硬件设计

2.1.

电源

GD32F4xx系列VDD/VDDA工作电压范围为2.6 V ~ 3.6 V。如下图2-1所示,GD32F4xx系列

设备有三个电源域,包括VDD/VDDA域,1.2 V域和备份域。VDD/VDDA域由电源直接供电,且

在VDD/VDDA域中嵌入了一个LDO,用来为1.2 V域供电。备份域供电VBAK可通过电源切换器

Power Switch切换由VDD或VBAT供电,当VDD电源关闭时,电源切换器可以将备份域的电源

切换到VBAT引脚,此时备份域由VBAT引脚(电池)供电。

图2-1. GD32F4xx系列电源域概览

2.1.1.

备份域

备份域供电电压范围为1.8 V ~ 3.6 V。电池备份域由内部电源切换器来选择VDD供电或

VBAT(电池)供电,然后由VBAK为备份域供电。为了确保备份域中寄存器的内容及RTC正

常工作,当VDD关闭时,VBAT引脚可以连接至电池或其他电源等备份源供电。如果外部没有

电池供电的应用,建议将VBAT引脚通过100nF电容对地后接至VDD引脚上。

关于VBAT电源有以下注意事项:

1、 由于在VDD上电阶段,芯片内部备份域电源仍然连接VBAT脚,如果此时VDD>VBAT+0.6V,

电流可能通过VDD与VBAT之间的内部二极管注入到VBAT,引起VBAT的脉冲;

6

PMUCTLFWDGTIRC32KLDOLXTALRTCWKUPFIRC16MHXTALPLLsPOR/PDRBPORADCBackup DomainNRSTPA0VDD DomainWKUPWKUPRVDDVBATPower Switch3.3VVBAKCortex-M4AHB IPs1.2V DomainAPB IPsSLEEPINGSLEEPDEEP1.2VLVD:低压检测器LDO:电压调节器POR:上电复位PDR:掉电复位BPOR:备份域上电复位WKUPNLVDDACVDDA3.3VVDDA DomainBLDOBSRAM1.2VBLDO:备份SRAM LDO输出1.2V电压�

GD32F4xx 系列硬件开发指南

2、 关于VBAT引脚的功耗,理论上,当MCU的VDD上电时,备份域内部swich连接到VDD上,

VBAT引脚无电流,但是,当主程序有使用ADC通过内部channel测量VBAT电压时,由于

MCU设计,会对VBAT上的电压进行4分压,然后进ADC channel,因此会在VBAT引脚上

引起额外的功耗(几十ua级)。

2.1.2.

VDD/VDDA 电源域

VDD/VDDA电源域包括VDD域和VDDA域两部分。如果VDDA不等于VDD,要求两者之间的压差不

能超过300mV(芯片内部VDDA与VDD通过背靠背二极管连接)。为避免噪声,VDDA可通过外

部滤波电路连接至VDD,相应的VSSA通过特定电路(单点接地,通过0Ω电阻或者磁珠等)

连接至VSS。

为了提高ADC的转换精度,为VDDA独立供电可使模拟电路达到更好的特性。在大封装上含

有专为ADC独立供电的VREF引脚(2.4 V≤VREF+≤VDDA, VREF-=VSSA)。

100及以上引脚的封装芯片含有VREF+和VREF-,VREF+可以使用外部参考电源,也可以

直连至VDDA,VREF-必须连接到VSSA;

64引脚封装芯片无VREF+和VREF-,其在内部直连至VDDA和VSSA,所有模拟模块均由

VDDA供电(包括ADC/DAC)。

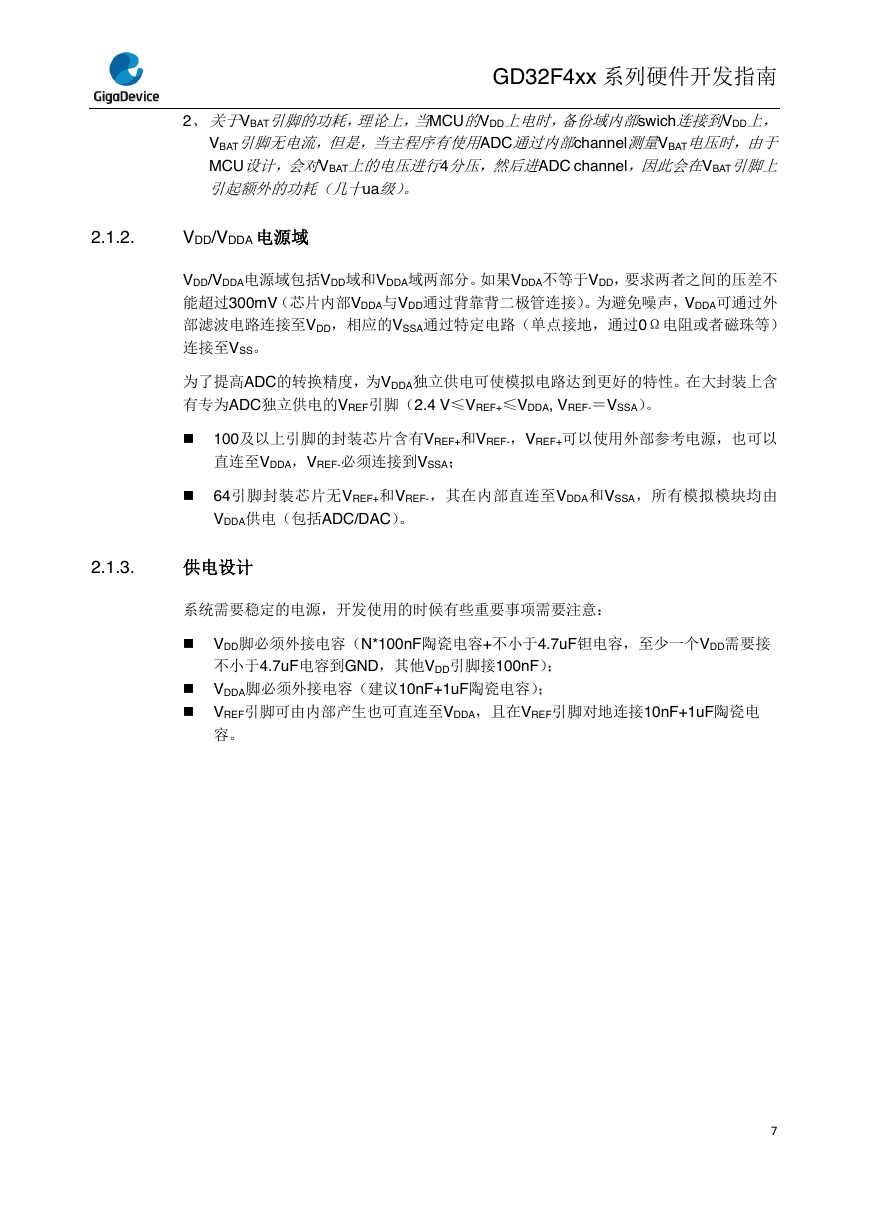

2.1.3.

供电设计

系统需要稳定的电源,开发使用的时候有些重要事项需要注意:

VDD脚必须外接电容(N*100nF陶瓷电容+不小于4.7uF钽电容,至少一个VDD需要接

不小于4.7uF电容到GND,其他VDD引脚接100nF);

VDDA脚必须外接电容(建议10nF+1uF陶瓷电容);

VREF引脚可由内部产生也可直连至VDDA,且在VREF引脚对地连接10nF+1uF陶瓷电

容。

7

�

GD32F4xx 系列硬件开发指南

图 2-2. GD32F4xx 系列推荐供电设计

注意:所有去耦电容须靠近芯片对应VDD、VDDA、VREF引脚放置。

2.1.4.

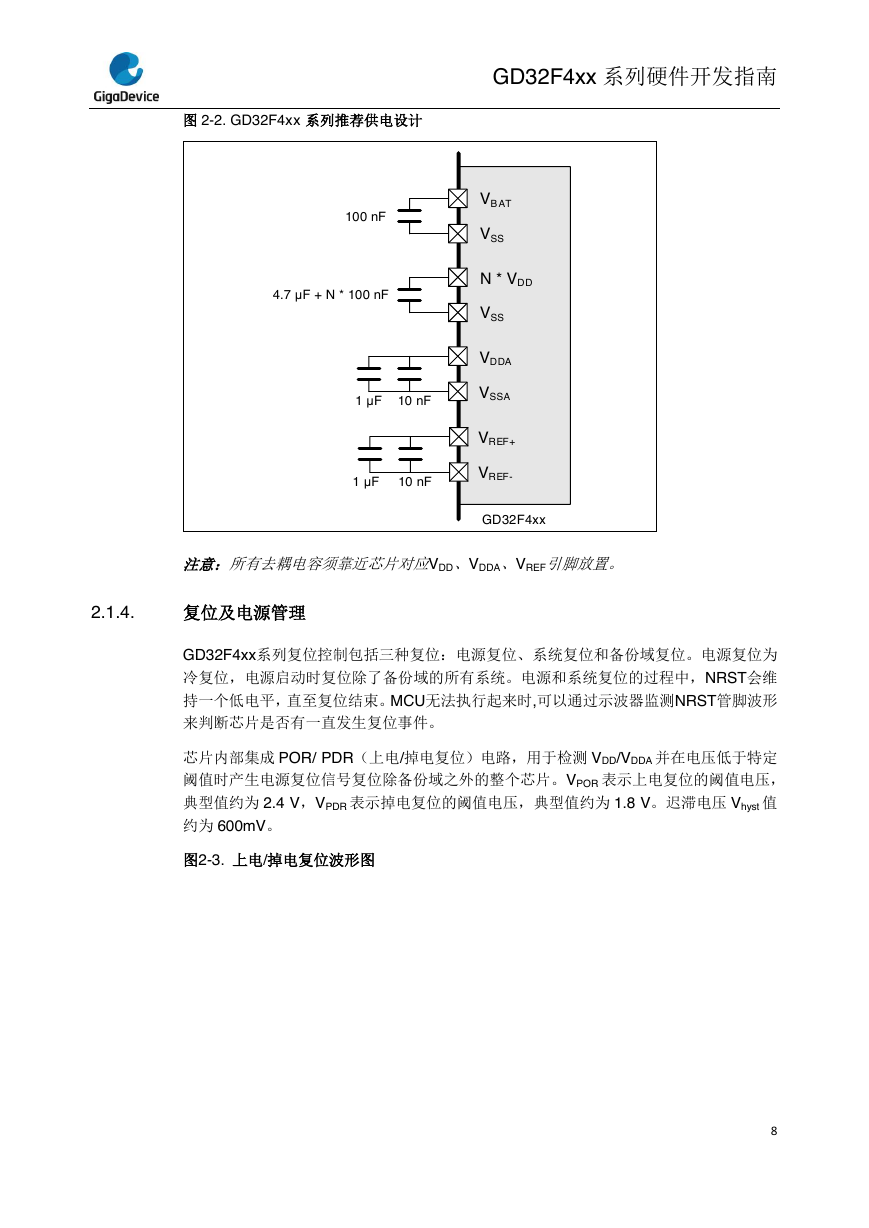

复位及电源管理

GD32F4xx系列复位控制包括三种复位:电源复位、系统复位和备份域复位。电源复位为

冷复位,电源启动时复位除了备份域的所有系统。电源和系统复位的过程中,NRST会维

持一个低电平,直至复位结束。MCU无法执行起来时,可以通过示波器监测NRST管脚波形

来判断芯片是否有一直发生复位事件。

芯片内部集成 POR/ PDR(上电/掉电复位)电路,用于检测 VDD/VDDA 并在电压低于特定

阈值时产生电源复位信号复位除备份域之外的整个芯片。VPOR 表示上电复位的阈值电压,

典型值约为 2.4 V,VPDR 表示掉电复位的阈值电压,典型值约为 1.8 V。迟滞电压 Vhyst 值

约为 600mV。

图2-3. 上电/掉电复位波形图

8

100 nFVBATVSSN * VDDVSS4.7 μF + N * 100 nF10 nFVDDAVSSA1 μF10 nFVREF+VREF-1 μFGD32F4xx�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc