�

目录

前言 ................................................................................................................................... 3

第一章:TimeQuest 静态时序分析模型 ........................................................................... 4

1.1 模型的基础单位 ................................................................................................... 4

1.2 理想的建立关系值和保持关系值 ......................................................................... 6

1.3 物理中的建立关系过程和建立余量 .................................................................... 9

1.4 令人误会的 建立关系 和 建立余量。 .............................................................14

1.5 建立余量 ............................................................................................................15

1.6 保持余量 ............................................................................................................22

总结: .......................................................................................................................32

第二章:模型角色,网表概念,时序报告 ......................................................................34

2.1 TimeQuest 模型的努力 ........................................................................................34

2.2 SDC 的网表(Net Lists)基本单位 .....................................................................35

2.3 TimeQuest 模型的简单实例 .................................................................................38

实验一: 入门实验...........................................................................................38

2.4 进一步看看 TimeQuest 模型如何分析时序 ........................................................42

2.5 建立 sdc 文件与网表 ..........................................................................................47

2.6 约束时钟 ............................................................................................................56

2.7 时序报告 ............................................................................................................60

总结: .......................................................................................................................68

第三章:TimeQuest 扫盲文 .............................................................................................69

3.1 余量的概念.........................................................................................................69

3.2 延迟因数:内部延迟因数 ..................................................................................73

3.3 延迟因数:外部延迟因数 ..................................................................................77

3.4 第一层与第二层时间要求 ..................................................................................81

3.5 山寨 TimeQuest 模型 ..........................................................................................87

3.6 约束命令和约束行为..........................................................................................90

总结: .......................................................................................................................91

第四章:内部延迟与其他 ................................................................................................92

4.1 PLL 与约束命令 ..................................................................................................92

4.2 约束 PLL 时钟 ....................................................................................................94

实验二 vga 模块的物理时序分析 .....................................................................94

4.3 延迟怪兽①....................................................................................................... 101

实验三 延迟怪兽的暴动 ................................................................................. 103

Delay_monster.v ............................................................................................... 104

4.4 延迟怪兽②....................................................................................................... 112

实验四 约束延迟怪兽 ..................................................................................... 112

4.5 Set Multicycle Path 的噩梦 ............................................................................. 122

4.6 不可理喻的 Set False Path ................................................................................ 128

实验五 延迟怪兽受死吧! ............................................................................. 129

1

总结: ..................................................................................................................... 132

第五章:网表质量与外部模型 ....................................................................................... 133

5.1 网表质量的概念 ............................................................................................... 133

5.2 Fmax 评估值...................................................................................................... 140

5.3 外部模型①....................................................................................................... 145

5.4 外部模型②....................................................................................................... 155

5.5 推导外包资料的公式........................................................................................ 164

5.6 外部模型的 input/ouput 约束指令.................................................................... 171

实验六 假想实验 input/output delay 约束....................................................... 172

总结: ..................................................................................................................... 179

第六章:物理时钟与外部模型 ....................................................................................... 180

6.1 物理时钟①....................................................................................................... 180

实验七:set_clock_latency 告诉 TimeQuest 外部时钟延迟信息 ...................... 184

6.2 物理时钟②....................................................................................................... 191

实验八 时钟抖动与 set_clock_latency ............................................................ 191

6.3 物理时钟③....................................................................................................... 195

实验九 时钟抖动与 input/output 约束命令 ................................................... 203

6.4 物理时钟④....................................................................................................... 207

实验十 时间抖动与 set_clock_uncertainly ...................................................... 207

6.5 无奈的 set_max_delay 与 set_min_delay ........................................................... 213

总结: ..................................................................................................................... 216

第七章:供源时钟与其他 .............................................................................................. 217

7.1 供源时钟①....................................................................................................... 217

实验十一 供源时钟与 Create Generated Clock ............................................... 217

7.2 供源时钟②....................................................................................................... 224

实验十二: 供源时钟与寄存器与 create_generated_clock ............................. 225

7.3 供源时钟③....................................................................................................... 230

实验十三 供源时钟与 pll 与 create generated clock ........................................ 231

7.4 引脚电容性与上下坡信号 ................................................................................ 236

7.5 介电参数与延迟时间........................................................................................ 241

7.6 IO 口 .................................................................................................................. 242

实验十四 分析和约束 io 口外部模型 ............................................................. 242

7.7 SDRAM 实例..................................................................................................... 247

实验十五 SDRAM 约束实例 .......................................................................... 249

总结: ..................................................................................................................... 260

后语 ................................................................................................................................ 261

2

�

前言

这是笔者用两年构思准备一年之久的笔记,其实这也是笔者的另一种挑战。写《工具篇

I》不像写《Verilog HDL 那些事儿》系列的笔记一样,只要针对原理和 HDL 内容作出

解释即可,虽然《Verilog HDL 那些事儿》夹杂着许多笔者对 Verilog 的独特见解,不过

这些内容都可以透过想象力来弥补。然而《工具篇 I》需要一定的基础才能书写。

两年前,编辑《时序篇》之际,笔者忽然对 TimeQuest 产生兴趣,可是笔者当时却就连

时序是什么也不懂,更不明白时序有理想和物理之分,为此笔者先着手理想时序的研究。

一年后,虽然已掌握解理想时序,但是笔者始终觉得理想时序和 TimeQuest 之间缺少什

么,这种感觉就像磁极不会没有原因就相互吸引着?于是漫长的思考就开始了 ... 在不

知不觉中就写出《整合篇》。

HDL 描述的模块是软模型,modelsim 仿真的软模型是理想时序。换之,软模型经过综

合器总综合以后就会成为硬模型,也是俗称的网表。而 TimeQuest 分析的对象就是硬模

型的物理时序。理想时序与物理时序虽然与物理时序有显明的区别,但它们却有黏糊的

关系,就像南极和北极的磁性一样相互作用着。

编辑《工具篇 I》的过程不也是一番风顺,其中也有搁浅或者灵感耗尽的情况。《工具篇

I》给笔者最具挑战的地方就是如何将抽象的概念,将其简化并且用语言和图形表达出

来。读者们可要知道《工具篇 I》使用许多不曾出现在常规书的用词与概念 ... 但是,

不曾出现并不代表它们不复存在,反之如何定义与实例化它们让笔者兴奋到夜夜失眠。

《工具篇 I》的书写方式依然继承笔者往常的笔记风格,内容排版方面虽然给人次序不

一的感觉,不过笔者认为这种次序对学习有最大的帮助。编辑《工具篇 I》辛苦归辛苦,

但是笔者却很热衷,心情好比小时候研究新玩具一般,一边好奇一边疑惑,一边学习一

边记录。完成它让笔者有莫民的愉快感,想必那是笔者久久不失的童心吧!?

(akuei2 上 30-09-2013)

3

�

第一章:TimeQuest 静态时序分析模型

兜兜转转,然后又转转兜兜,最终还是需要站在 TimeQuest 的大门口。先自白一下,

接下来的故事都是一位傻子对 TimeQuest 的理解,这个傻子的脑容量有限,处理能力不

好,空白的地方都会用想象力自园。

TimeQuest 是 Altera - Quartus II 旗下的东西,其中它(TimeQuest)用了一个“时序分

析模型”作为物理时序的分析“框子”或者“数学模型”。在这里笔者需要强调一下,

TimeQuest 中的“时序”和 Verilog HDL 中出现的时序是两个东西。所谓 HDL 的时序是

指“模块的活动记录”等理想的波形;反之 TimeQuest 中出现的时序是指“物理上路

径,各种延迟问题”的不理想波形。

让我们暂时把 Verilog HDL 忘了吧 ... 一般上分析物理时序有用一套方法称为“静态时

序分析”的方法,关于静态时序分析网上有太多的解释了,但是 TimeQuest 有属于自己

一套“分析时序的模型”,所以我们可以“无视”其它。

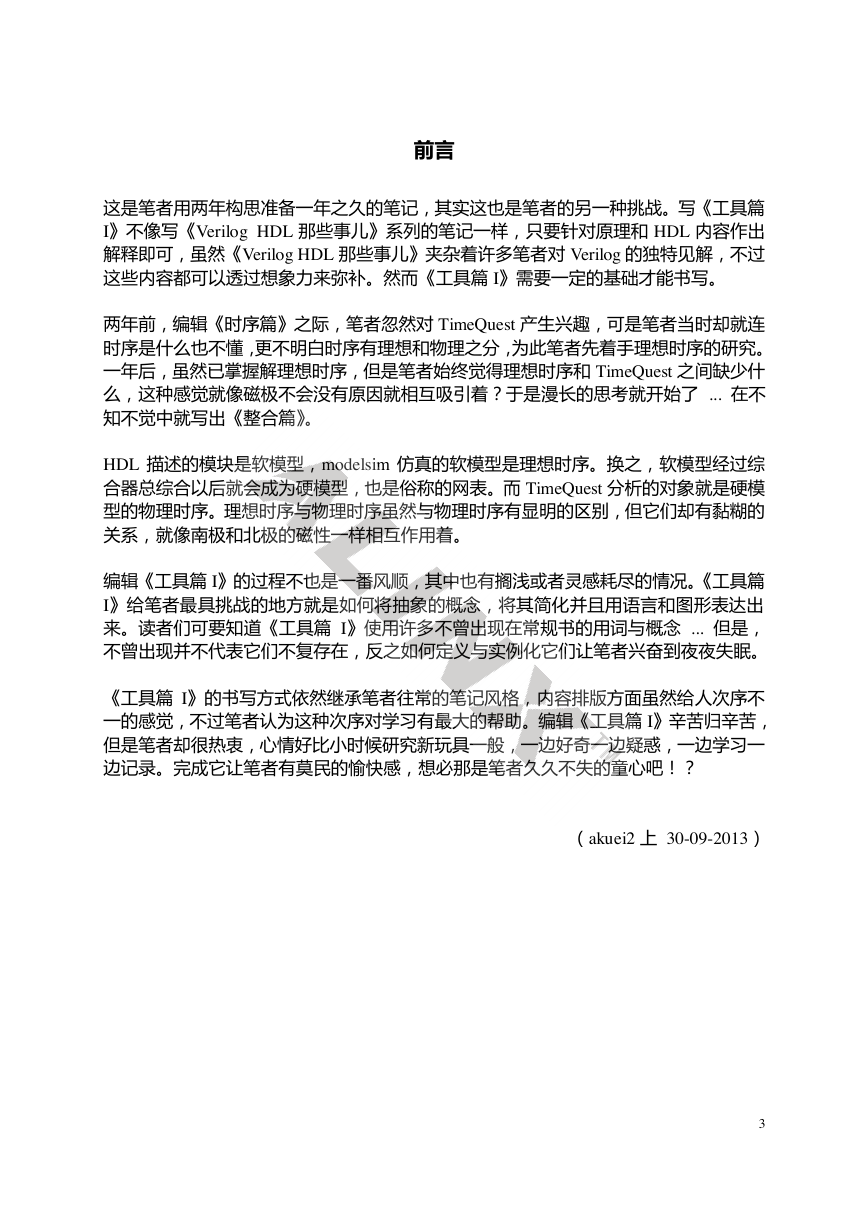

1.1 模型的基础单位

图 1.1.1 模型的基础

TimeQuest 的时序分析模型(以下简称模型)的基础,基本上需要两个节点才能发挥,

如图 1.1.1 所示。节点的定义很模糊,因为节点本身没有个性,它处在什么就变什么 ... 如

果用 TimeQuest 的话来讲,将一对节点放在 fpga 内部,节点就会化身成为寄存器。这也

节点最常见的姿态。所以说,暂时让我们把节点看成寄存器吧!

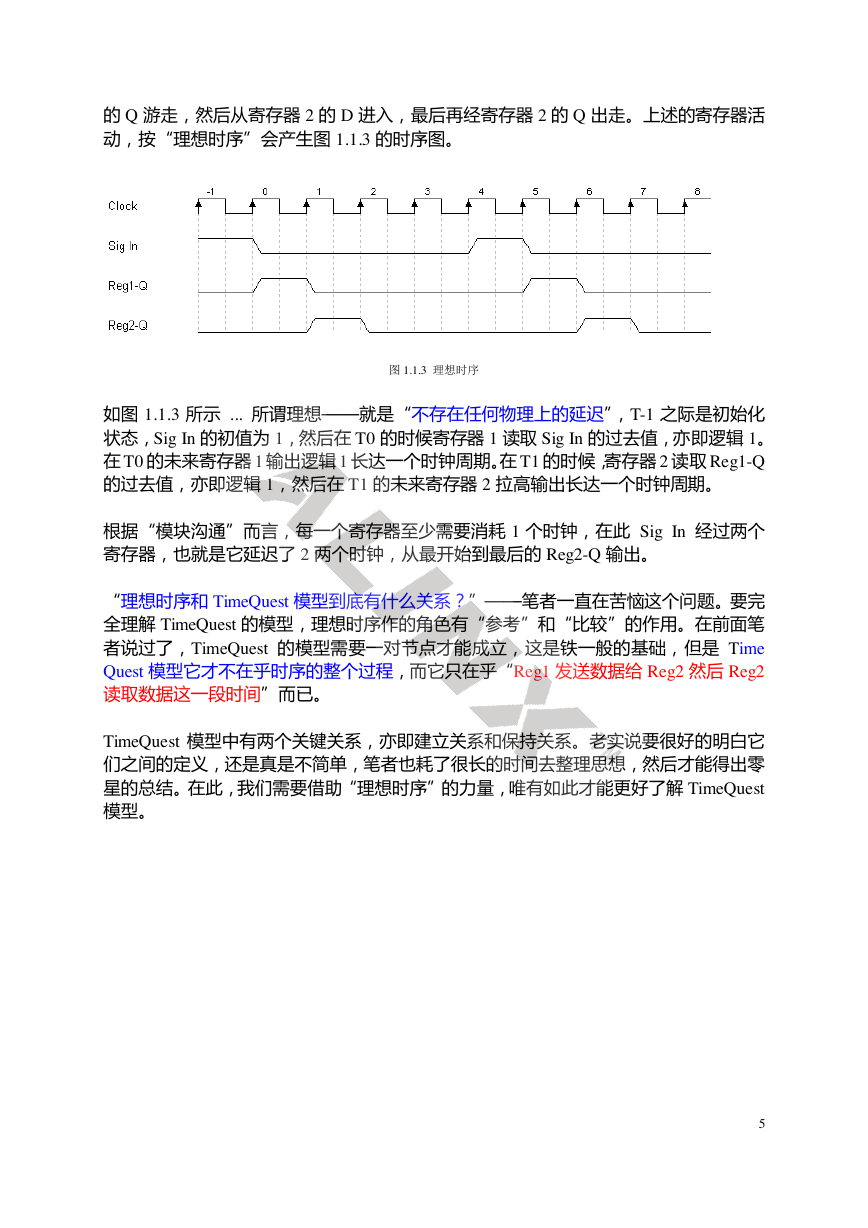

图 1.1.2 寄存器为节点

图 1.1.2 是把另个节点看成寄存器,亦即寄存器 1(reg1)和寄存器 2(reg2)。寄存器 1

和寄存器 2 共享同样的时钟信号。Signal(信号)从寄存器 1 的 D 进入,再由寄存器 1

4

�

的 Q 游走,然后从寄存器 2 的 D 进入,最后再经寄存器 2 的 Q 出走。上述的寄存器活

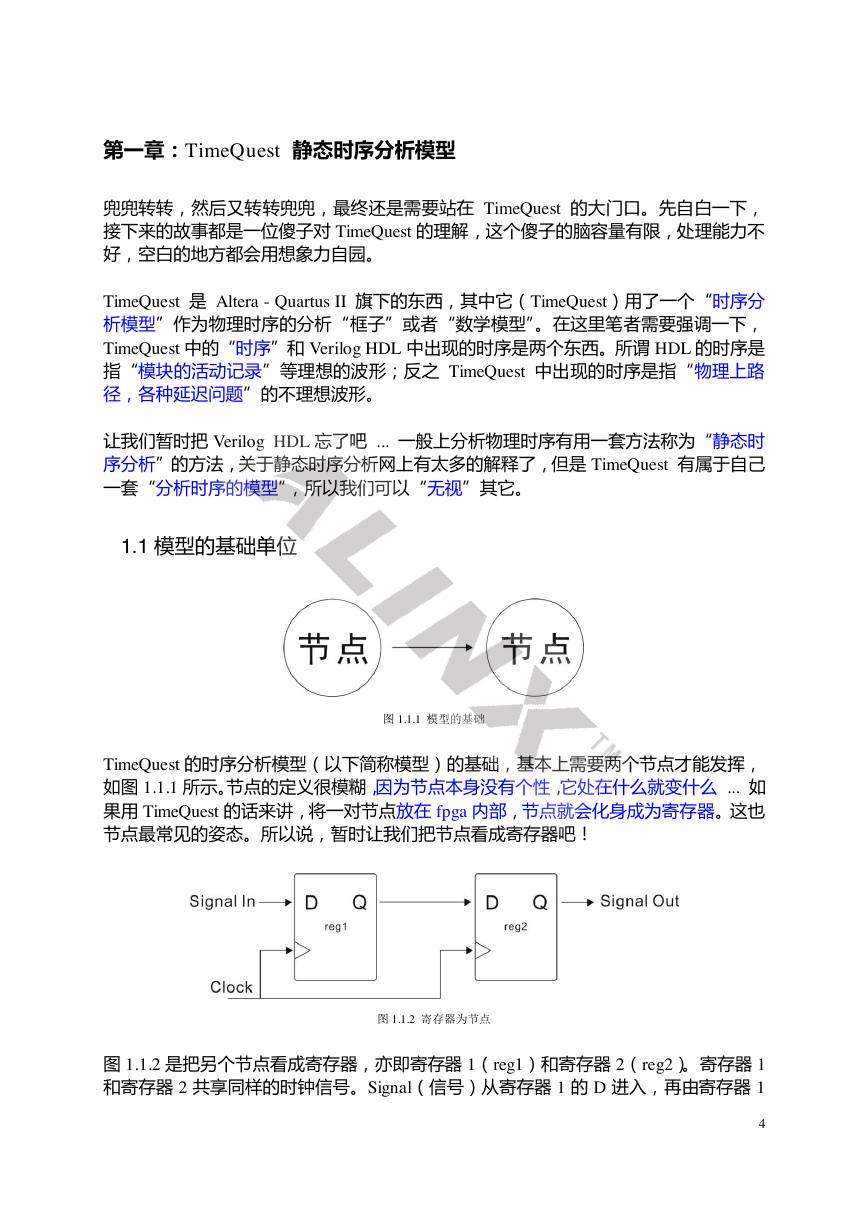

动,按“理想时序”会产生图 1.1.3 的时序图。

图 1.1.3 理想时序

如图 1.1.3 所示 ... 所谓理想——就是“不存在任何物理上的延迟”,T-1 之际是初始化

状态,Sig In 的初值为 1,然后在 T0 的时候寄存器 1 读取 Sig In 的过去值,亦即逻辑 1。

在 T0 的未来寄存器 1 输出逻辑 1 长达一个时钟周期。在 T1 的时候,寄存器 2 读取 Reg1-Q

的过去值,亦即逻辑 1,然后在 T1 的未来寄存器 2 拉高输出长达一个时钟周期。

根据“模块沟通”而言,每一个寄存器至少需要消耗 1 个时钟,在此 Sig In 经过两个

寄存器,也就是它延迟了 2 两个时钟,从最开始到最后的 Reg2-Q 输出。

“理想时序和 TimeQuest 模型到底有什么关系?”——笔者一直在苦恼这个问题。要完

全理解 TimeQuest 的模型,理想时序作的角色有“参考”和“比较”的作用。在前面笔

者说过了,TimeQuest 的模型需要一对节点才能成立,这是铁一般的基础,但是 Time

Quest 模型它才不在乎时序的整个过程,而它只在乎“Reg1 发送数据给 Reg2 然后 Reg2

读取数据这一段时间”而已。

TimeQuest 模型中有两个关键关系,亦即建立关系和保持关系。老实说要很好的明白它

们之间的定义,还是真是不简单,笔者也耗了很长的时间去整理思想,然后才能得出零

星的总结。在此,我们需要借助“理想时序”的力量,唯有如此才能更好了解 TimeQuest

模型。

5

�

1.2 理想的建立关系值和保持关系值

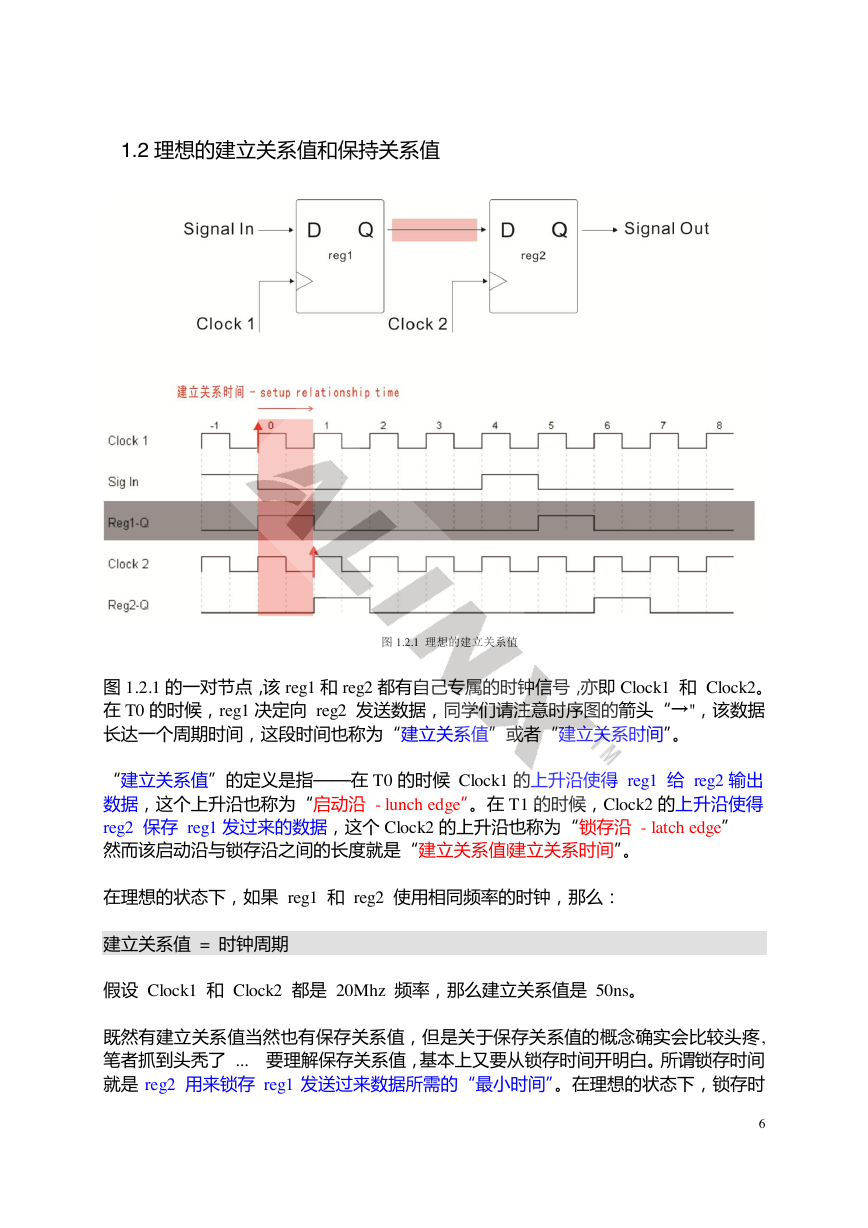

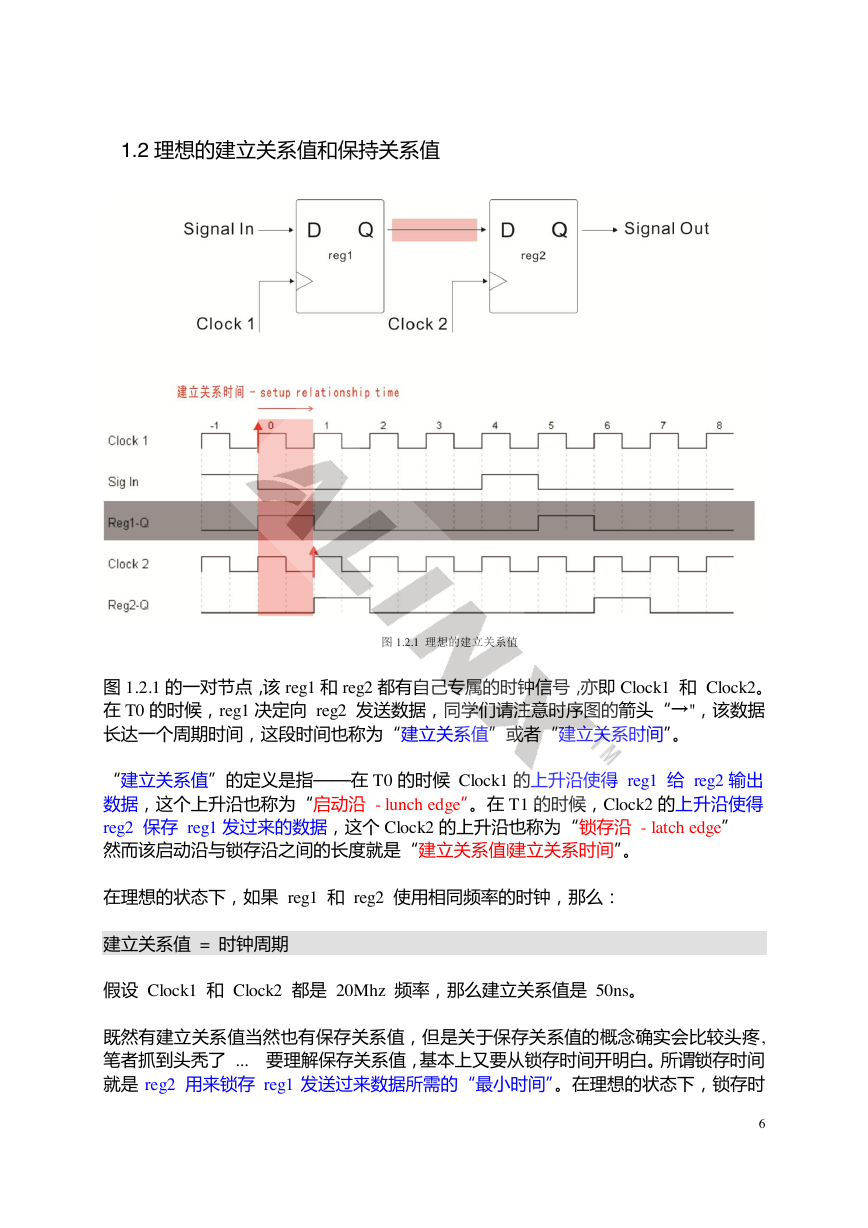

图 1.2.1 理想的建立关系值

图 1.2.1 的一对节点,该 reg1 和 reg2 都有自己专属的时钟信号,亦即 Clock1 和 Clock2。

在 T0 的时候,reg1 决定向 reg2 发送数据,同学们请注意时序图的箭头“→",该数据

长达一个周期时间,这段时间也称为“建立关系值”或者“建立关系时间”。

“建立关系值”的定义是指——在 T0 的时候 Clock1 的上升沿使得 reg1 给 reg2 输出

数据,这个上升沿也称为“启动沿 - lunch edge”。在 T1 的时候,Clock2 的上升沿使得

reg2 保存 reg1 发过来的数据,这个 Clock2 的上升沿也称为“锁存沿 - latch edge”

然而该启动沿与锁存沿之间的长度就是“建立关系值|建立关系时间”。

在理想的状态下,如果 reg1 和 reg2 使用相同频率的时钟,那么:

建立关系值 = 时钟周期

假设 Clock1 和 Clock2 都是 20Mhz 频率,那么建立关系值是 50ns。

既然有建立关系值当然也有保存关系值,但是关于保存关系值的概念确实会比较头疼,

笔者抓到头秃了 ... 要理解保存关系值,基本上又要从锁存时间开明白。所谓锁存时间

就是 reg2 用来锁存 reg1 发送过来数据所需的“最小时间”。在理想的状态下,锁存时

6

�

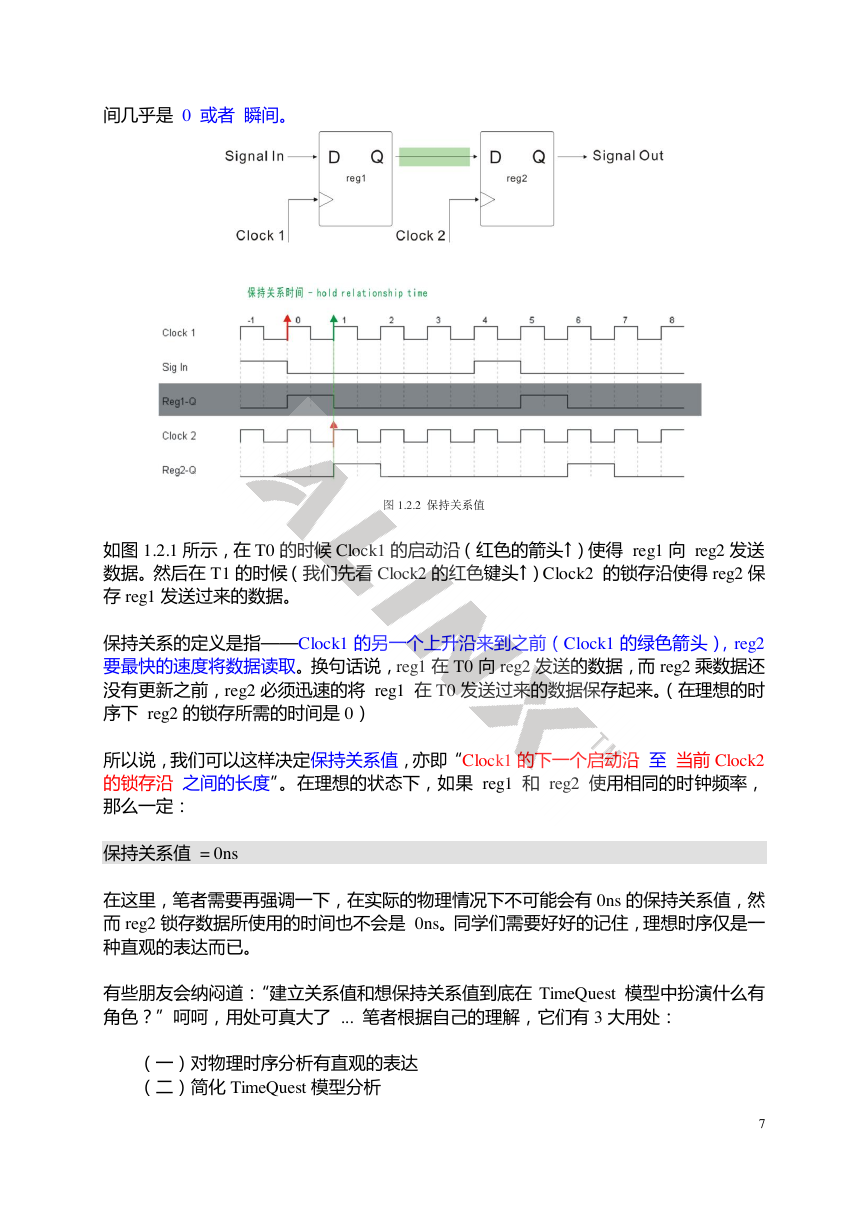

间几乎是 0 或者 瞬间。

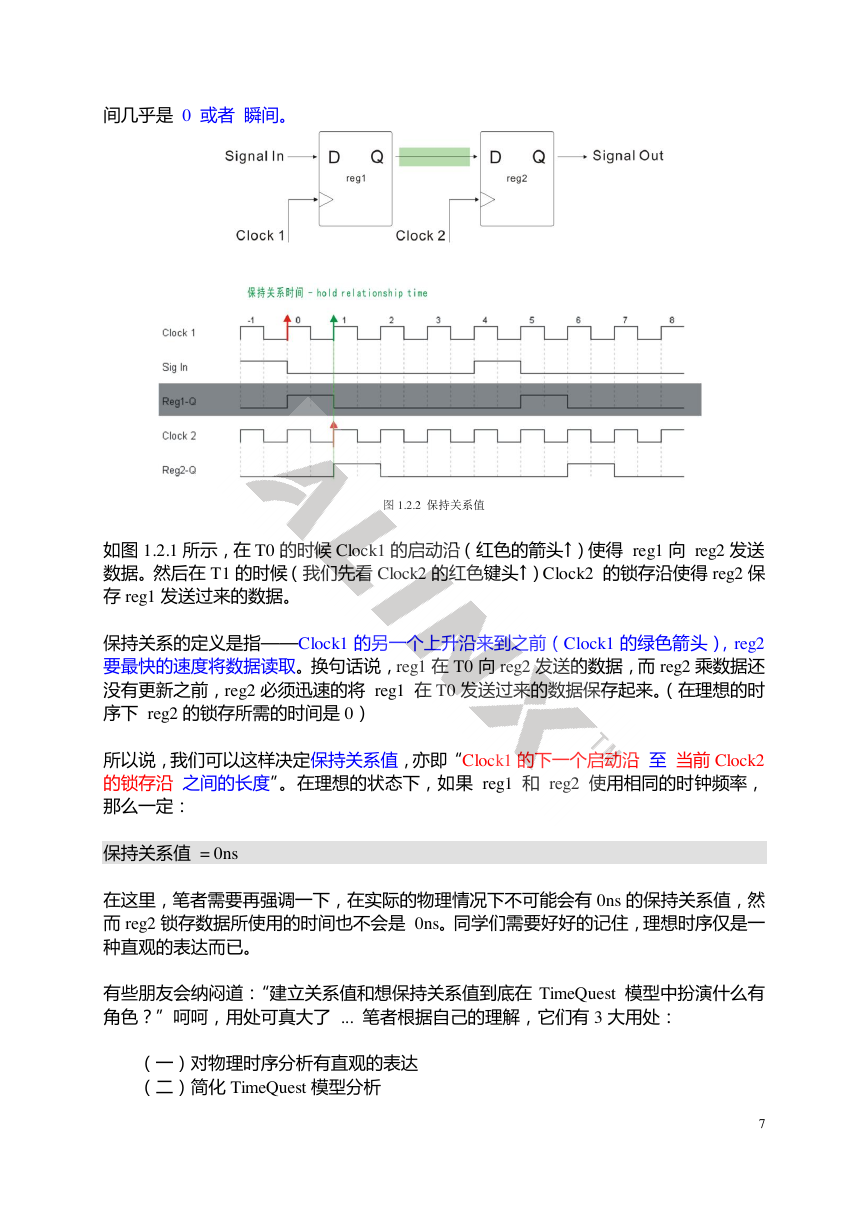

图 1.2.2 保持关系值

如图 1.2.1 所示,在 T0 的时候 Clock1 的启动沿(红色的箭头↑)使得 reg1 向 reg2 发送

数据。然后在 T1 的时候(我们先看 Clock2 的红色键头↑)Clock2 的锁存沿使得 reg2 保

存 reg1 发送过来的数据。

保持关系的定义是指——Clock1 的另一个上升沿来到之前(Clock1 的绿色箭头),reg2

要最快的速度将数据读取。换句话说,reg1 在 T0 向 reg2 发送的数据,而 reg2 乘数据还

没有更新之前,reg2 必须迅速的将 reg1 在 T0 发送过来的数据保存起来。(在理想的时

序下 reg2 的锁存所需的时间是 0)

所以说,我们可以这样决定保持关系值,亦即“Clock1 的下一个启动沿 至 当前 Clock2

的锁存沿 之间的长度”。在理想的状态下,如果 reg1 和 reg2 使用相同的时钟频率,

那么一定:

保持关系值 = 0ns

在这里,笔者需要再强调一下,在实际的物理情况下不可能会有 0ns 的保持关系值,然

而 reg2 锁存数据所使用的时间也不会是 0ns。同学们需要好好的记住,理想时序仅是一

种直观的表达而已。

有些朋友会纳闷道:“建立关系值和想保持关系值到底在 TimeQuest 模型中扮演什么有

角色?”呵呵,用处可真大了 ... 笔者根据自己的理解,它们有 3 大用处:

(一)对物理时序分析有直观的表达

(二)简化 TimeQuest 模型分析

7

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc