2

2

2

2

第 29 卷 第 4 期

2006 年 12 月

2

电 子 器 件

Chinese J ournal Of Elect ron Devices

Vol . 29 No. 4

Dec. 2006

System Level Simulation of Pipelined ADC

Z H E N G X i ao

y an , W A N G Hon g

li , Q I U Y u

li n

( I nstit ute of M icroelect ronics of Chi nese A ca dem y of S ciences , B ei j i ng 100029 , Chi na)

Abstract :According to t he idea of top

down design flow , a behavior model of pipelined ADC is built wit h

MA TL AB software to confirm t he st ruct ure of t he system and t he performance target of each block. Non

ideal factors and t hermal noise of analog blocks are f ully considered so t hat t he simulation result s are refer

ential in circuit level. Finally , t hermal noise and non

ideal factors of a 10 bit , 80M Hz , 1. 5 bit/ stage pipe

lined ADC are set and some important performance parameters are comp uted.

Key words :behavior model ;pipelined ADC ;MA TL AB

EEACC :1290B;1280

流水线 ADC 的系统级仿真

郑晓燕 ,王洪利 ,仇玉林

(中国科学院微电子研究所 ,北京 100029)

摘 要 :应用模拟电路自顶向下的设计思想 ,用 MA TL AB 建立了一个流水线型模数转换器的行为模型 ,从而可以有效确定

系统结构及相关模块参数 。为了对实际电路有较好的指导作用 ,充分考虑了电路的非理想特性和噪声 。最后通过设定一个

分辨率为 10 bit ,采样频率为 80 M Hz ,1. 5 bit/ 级的经典流水线型数模转换器模型的非理想参数值和噪声参数 ,对 ADC 模型

的主要性能参数进行了仿真计算 。

关键词 :行为模型 ;流水线 ADC ;MA TL AB

中图分类号 :TN402

文献标识码 :A 文章编号 :1005

9490( 2006) 04

1288

04

目前 ,随着半导体技术的发展 ,模数转换器向着

更高速和高精度的方向发展 ,对模数转换器进行晶

体管级的仿真所需时间越来越长 。为了减少迭代次

数 ,提高设计效率 ,行为级仿真变得越来越重要 。一

方面在考虑非理想特性和电路噪声的情况下 ,通过

行为级仿真可以对整个系统的结构或算法进行分析

验证 ,并对它的静态指标和动态指标进行评估 ;另一

方面允许设计者判断基本模块在转换性能中的效果

和限制 ,帮助确定各模块的性能指标 ,从而指导后面

的电路级设计 。

A 、V ERIL O G

行为模型的描述可以使用不同的高级语言 ,例

如 , C、V HDL

A 和 S YS TEMC[ 1 - 3 ]

等 。由于 Matalab 中的 Simulink 模型简单直观 ,易

于观测各模块的输入输出波形 ,而且仿真数据易于

在 Matalab 中进行处理和统计 ,以对系统的性能进

行评估 ,因此本文选 Matalab 作为行为级仿真工具 。

本文对一个分辨率为 10 bit , 采样频率为 80

M Hz ,1. 5 bit/ 级的经典流水线型数模转换器[ 4 ] 进

行了建模 。主要包括采样保持电路 、MDAC 电路 、

子 ADC、数字纠错编码等模块 。为了对实际电路有

较好的指导意义 ,本文中的每个模块都充分考虑了

实际电路中存在的非理想效应 ,而且模型采用全差

分的形式 ,以保证每个模块的输出波形与实际电路

一致 。

1 采样保持电路

采样保持电路是模数转换器的关键模块 ,直接

决定整个转换器的精度和速度 。运放是采样保持电

路中最重要的部分 ,其性能好坏对整个系统的性能

影响很大 。运放的主要参数 ,包括有限直流增益 、单

收稿日期 :2005

作者简介 :郑晓燕 (1981

12

13

) ,女 ,硕博连读生 ,主要研究方向为低功耗流水线型 ADC ,xyzheng @126. com

�

第 4 期

郑晓燕 ,王洪利等 :流水线 ADC 的系统级仿真

9821

位增益带宽 、压摆率 、建立时间 、以及寄生电容等 ,在

建模中都进行了考虑 。

在采样保持电路的保持相 ,运放工作在闭环状

态 ,若反馈系数为β,运放直流增益为 A ,

β(1 - 1

βA

V out = V m · A

≈ V in ·1

1 +βA

)

由于有限直流增益 A ,系统引入一个非线性增益误

差 。本设计对翻转围绕采样保持放大器电路建模 ,

考虑运放的输入寄生电容 Cp ,反馈系数为

β =

Cs

Cs + Cp

采样相结束时运放的建立包括大信号建立和小

信号建立 。在大信号建立时间内 ,运放工作在压摆

状态 ,输出受到压摆率的限制 ,采用 simulink 的斜

率限制器进行建模 ,这时运放的输出为

V out ( t) = S R ·t t < t0

其中 , t0 为大信号建立和小信号建立的临界时间点 ,

可近似认为

t0 =

V s

β·S R

在进行小信号建立时 ,运放工作在线形区 ,输出

随输入小信号变化 。为了建模与电路仿真结果相

符 ,对运放的极点和零点进行了描述建模[ 5 ] 。小信

号建立时间范围内 ,运放的输出为大信号建立结束

时的输出电压加上输入信号通过一个用 MA TL AB

描述的运放传输函数 f ( s) 的模型得到的电压值 。

这样就比较准确地模拟实际电路的建立过程 。

运放自身会引入噪声 , 主要包括 1/ f 噪声和热

噪声 ,1/ f 噪声与频率成反比 ,频率越高 ,影响越小 。

如果忽略 1/ f 噪声仅考虑热噪声 ,那么运放的均方

根输入参考噪声电压 V n 可表示为

V n =ξ·k T

CL

·β式中 :ξ是与电路结构相关的系

数 ,β为运算放大器的反馈系数 , CL 为运放的负载

电容 。本文中用一个随机信号来产生噪声 , 将噪声

加在闭环电路的输入端 。除去运放的非理想因素 ,

影响采样保持电路性能的主要因素还有时钟抖动 、

开关热噪声 、电容不匹配 、寄生电容等 。时钟抖动[6 ]

是由于时钟不理想 , 它的时钟沿与理想的时钟沿有

一定偏差 。这个偏差是随机发生的 , 并且它的大小

在一定范围内也是随机的 。采样/ 保持电路的时钟

抖动对数据转换的信噪比有较大的影响 。当输入一

个振幅为 A ,频率为 f 的正弦信号 x ( t) 时 ,如果该

正弦信号在采样时刻有一个随机的采样时间误差

δ,这将会产生时钟抖动误差 ,

x ( t +δ) - x ( t) ≈ 2πf A co s (2πf t) = δ d

dt

x ( t)

开关热噪声可等效为白噪声 , 假设开关的导通

电阻为 Ron ,电容为 Cs ,那么导通电阻的噪声频谱密

度为 : S v ( f ) = 4 k T Ron

开关热噪声的总噪声功耗为

P2

T =∫∞

0

4 k T R on

1 + (2πf R on Cs ) 2 d f =

k T

Cs

式中 : k 为玻尔茨曼常数 , T 为绝对温度 。当开关电

容周期性采样时 ,开关热噪声和输入信号发生叠加 ,

并被保存在采样电容上 。整个采样保持电路的模型

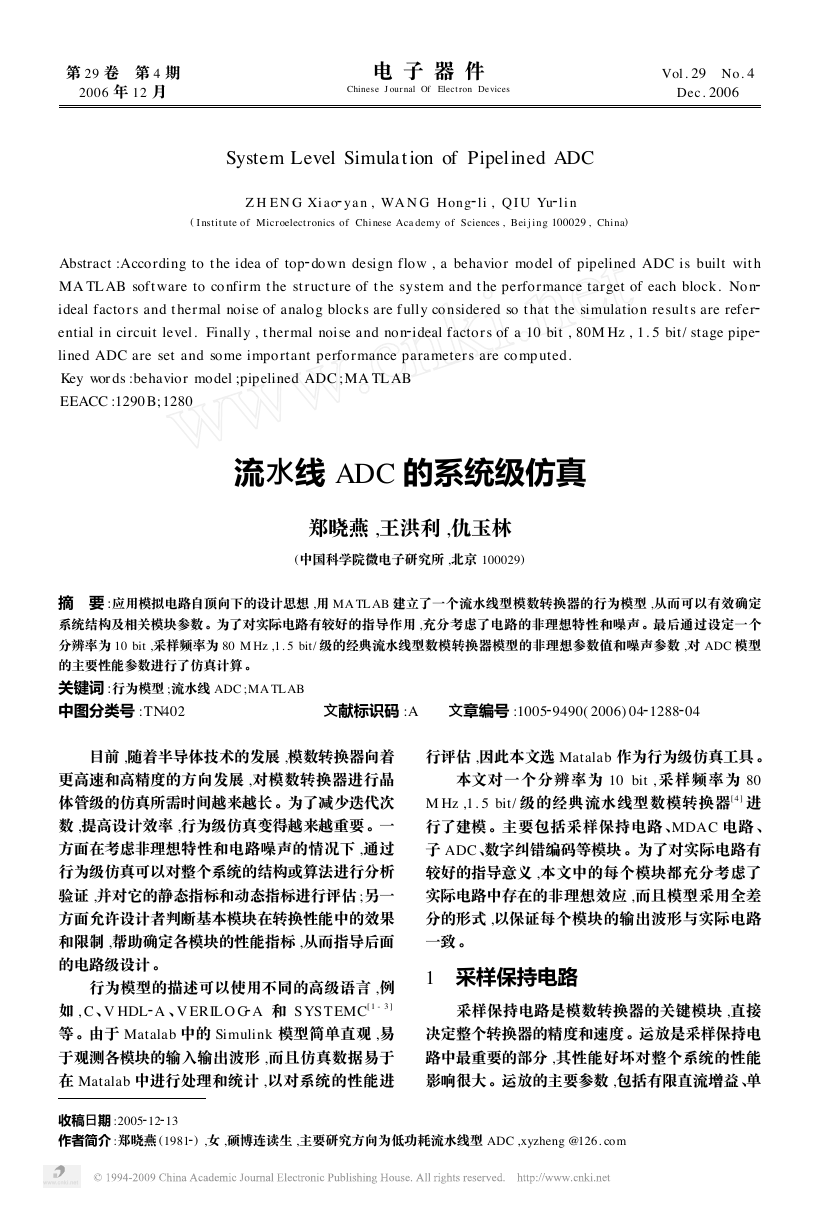

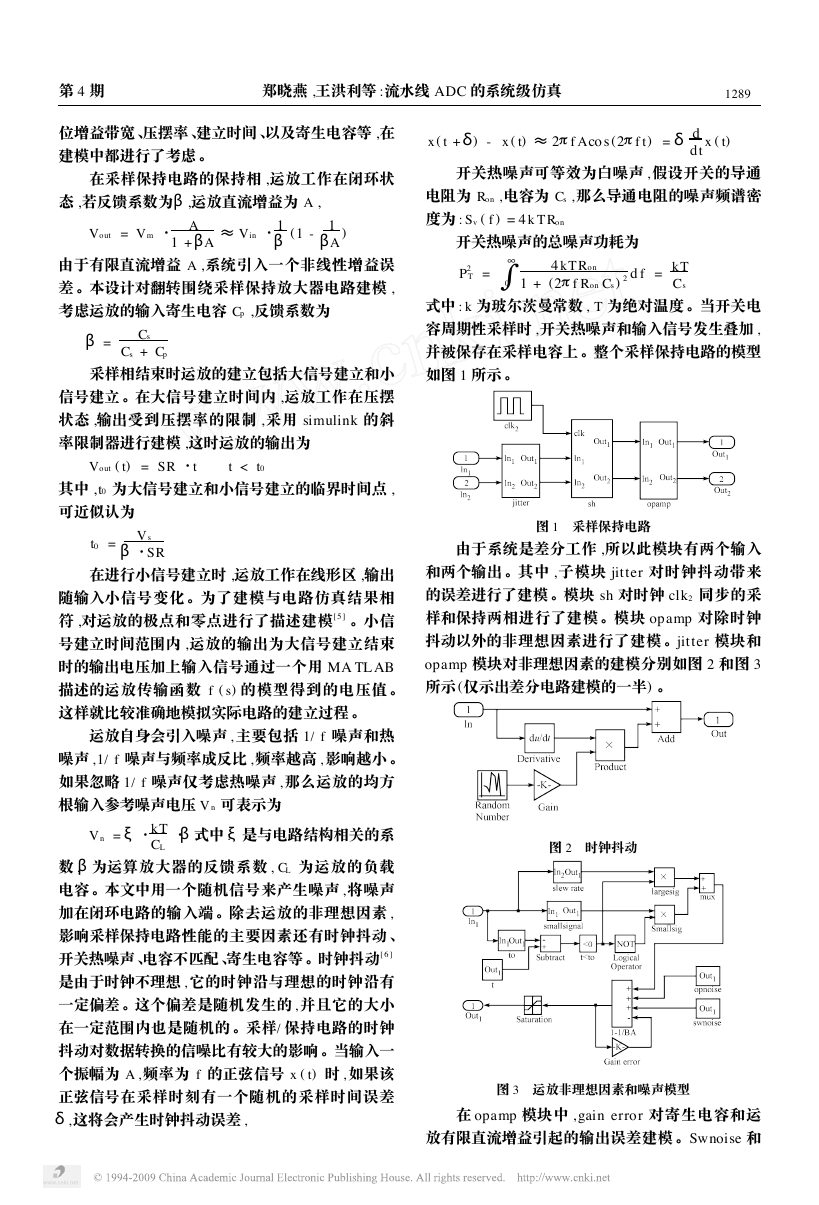

如图 1 所示 。

图 1 采样保持电路

由于系统是差分工作 ,所以此模块有两个输入

和两个输出 。其中 ,子模块 jitter 对时钟抖动带来

的误差进行了建模 。模块 sh 对时钟 clk2 同步的采

样和保持两相进行了建模 。模块 opamp 对除时钟

抖动以外的非理想因素进行了建模 。jitter 模块和

opamp 模块对非理想因素的建模分别如图 2 和图 3

所示 (仅示出差分电路建模的一半) 。

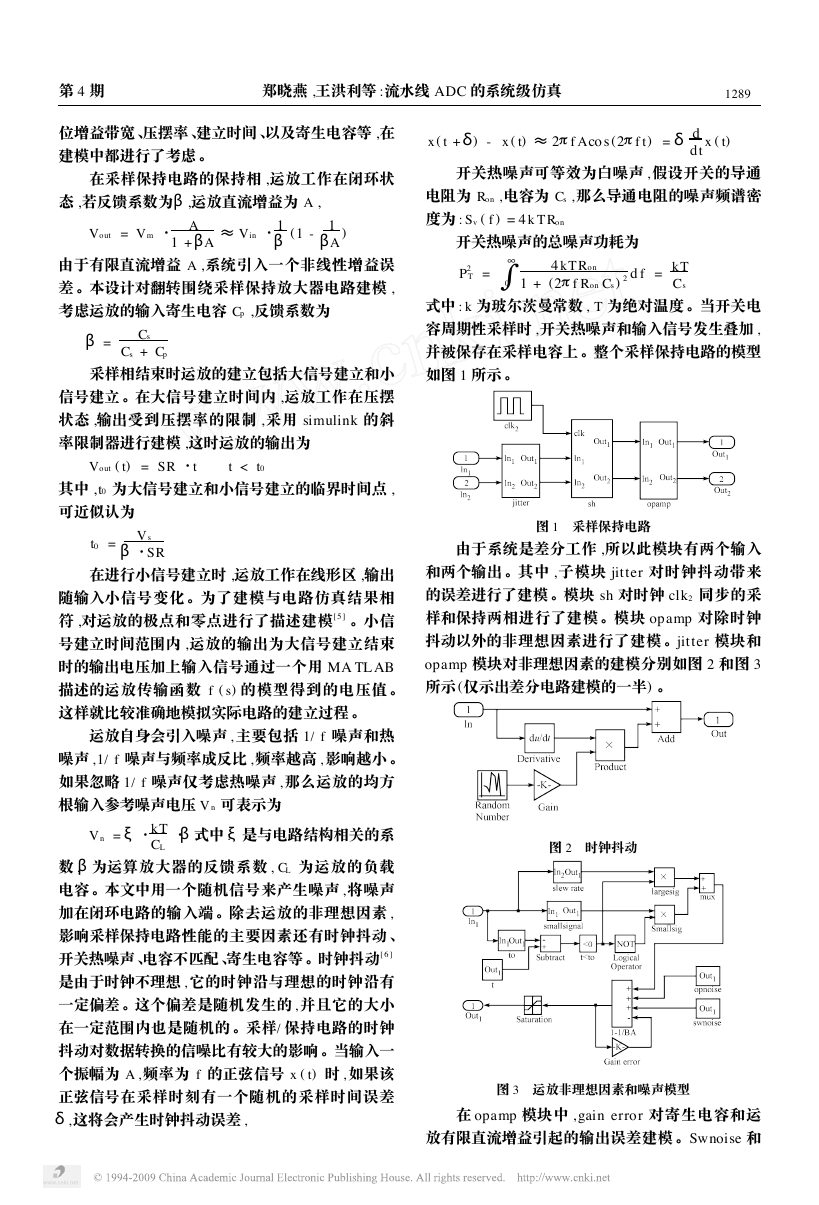

图 2 时钟抖动

图 3 运放非理想因素和噪声模型

在 opamp 模块中 , gain error 对寄生电容和运

放有限直流增益引起的输出误差建模 。Swnoise 和

�

0921

电 子 器 件

第 29 卷

op noise 对开关和运放噪声建模 ,由于热噪声在频谱

上均匀分布 ,开关和运放噪声与时钟抖动误差相似 ,

都用随机信号建模 。两个时间产生模块中 , to 为大

信号行为和小信号行为的交界时间点 , t 为运放工

作周期中工作时间的计时 。模块 t < to 用来判断大

信号建立是否完成 、小信号建立是否要开始 。Slew

rate 和 small signal 对压摆率限制和小信号行为进

行建模 。建模后采样保持电路的输出波形与输入波

形和理想输出波形 (单端输入与输出) 如图 4 ,可以

看到 ,这种建模方法所得到的输出波形与实际电路

很接近 ,这样对于整个系统 ,通过行为级仿真和电路

级仿真的迭代可以有效的指导电路的设计 。

图 5 比较器模型

图 4 采样保持电路输入输出波形

2 MDAC 电路与子 ADC

运放的每一级包含 MDAC 电路和子 ADC。对

于 1. 5 bit/ 级的电路 ,子 ADC 由两个比较器组成 ,

分别与 V ref / 4 和 - V ref / 4 进行比较 。最后一级输出

2 bit 的子 ADC 由三个比较器组成 ,分别与 V ref / 2 、

0 、- V ref / 2 进行比较 。在电路设计中 ,比较器通常

由一个预放大器和一个触发器构成 。用 simulink

建模时 ,比较器模型如图 5 ,图 6 所示 ,包括一个减

法器 ,一个放大器和一个触发器 ,由于输出为数字信

号 ,放大器的非理想因素被忽略 。减法器的输入包

括差分输入信号 、比较参考电压 (比较器阈值电压)

和失调电压 。由于失调电压是比较器中一个重要的

非理想因素 ,因此该比较器模型对失调电压进行了

考虑 。输入信号 、参考电压和失调电压经过求和运

算产生一个和值 ,该和经放大器放大后送触发器产

生比较结果 。

MDAC 电路 ,它可实现数模转换 、减法 、级间放

大等功能 ,在开关电容实现的 MDAC 中 ,误差源主

要有运放的非理想因素 、开关热噪声 、电容不匹配 、

寄生电容等 。与采样保持电路相比 ,没有对时钟抖

动进行建模没 ,因为在 MDAC 中时钟抖动对精度的

影响可忽略 ,MDAC 的输入数据在采样相与余量放

大相交替的时间附近基本为常数 。

图 6 MDAC 电路与子 ADC

MDAC 电路与子 ADC 的模型如图 6 所示 。根

据子 ADC ( subadc) 的 输 出 数 字 码 , 模 数 转 换 器

(subdac) 分别输出到两个减法器 (加法器) 中 。

图 6 中 opamp 模型与图 3 所示的模型对非理

想因素的建模方法相同 ,只是反馈系数不同 ,此处

opamp 模型的增益近似为 2 。MDAC 电路给下一

级的两个输出分别为

V out1 = 2 (V in1 - V subdac )

V out2 = 2 (V in2 - V subdac )

V in1 和 V in2 是一对差分输入信号 ,可以看出输出

给下一级的电压也是一对差分信号 。

3 数字纠错编码

分辨率为 10 bit ,1. 5 bit/ 级的流水线型 ADC

共有 9 级 ,每级输出数字码为 2 bit ,前 8 级每级有 1

位冗余位[ 7 ] 。ADC 输出编码从第 9 级开始 ,第 9 级

对第 8 级进行校正 ,输出 3 bit ,然后再对第 7 级进

行校正 ,依次类推 ,最后输出 10 bit 数字码 。这是数

字部分 ,对整个 ADC 性能影响不大 ,所以没有加非

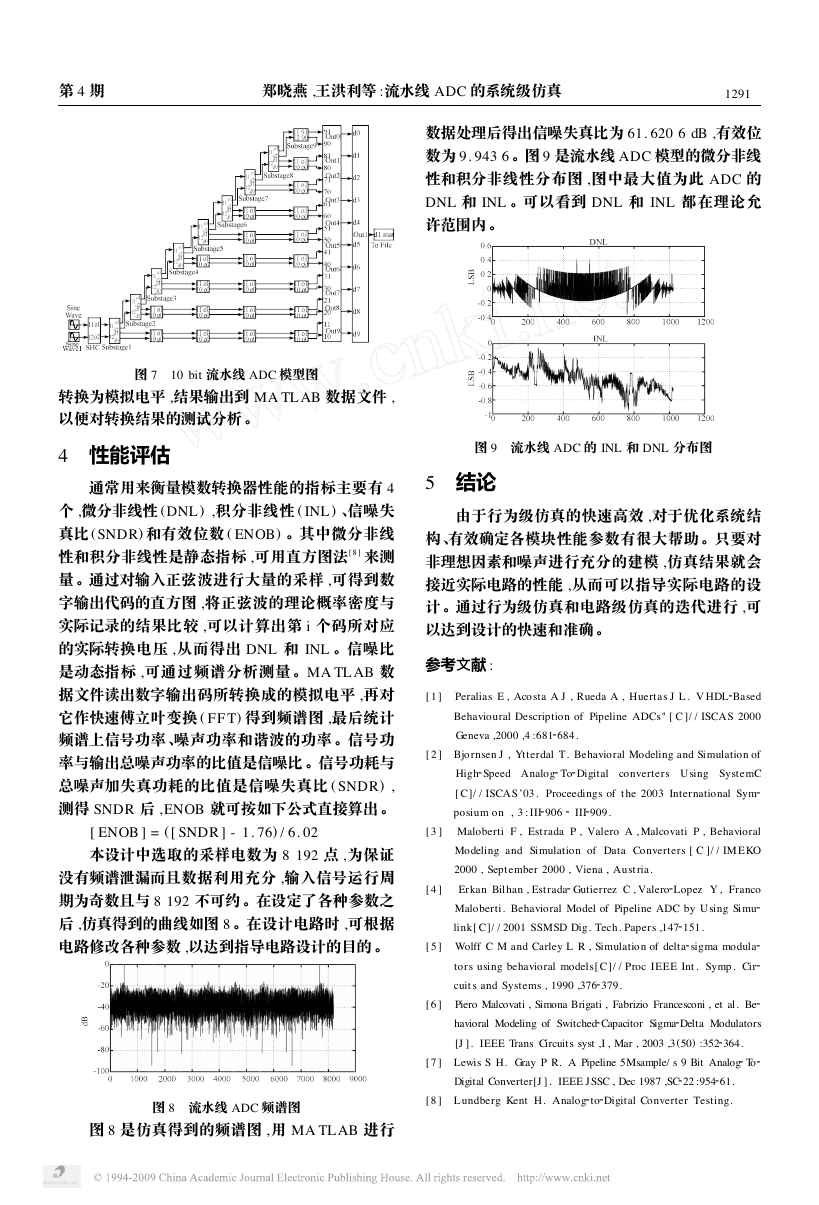

理想因素进行建模 。整个 ADC 模型如图 7 所示 。

substage1~substage8 是前 8 级 ,每级输出两位数

字码经延时模型 ( delay) 输出至数字编码单元 ( sig

nal coding) 进行编码 ,输出两个模拟差分余量电平

至下一级 。Substage9 是最后一级 ,输出两位无冗

余数字码 。由于相璘两个子级时钟相相反 ,即本级

进行采样时下一级进行余量计算 ,相璘的两个奇数

级与偶数级用的延时模块数相同 ,从而输出至编码

模块的所有数字码与同一时钟同步 。out 0 ~out 9 为

流水线 ADC 数字输出码 ,经一个理想 DAC 模型后

�

2

2

2

第 4 期

郑晓燕 ,王洪利等 :流水线 ADC 的系统级仿真

2

2

2

2

2

2

2

2

1921

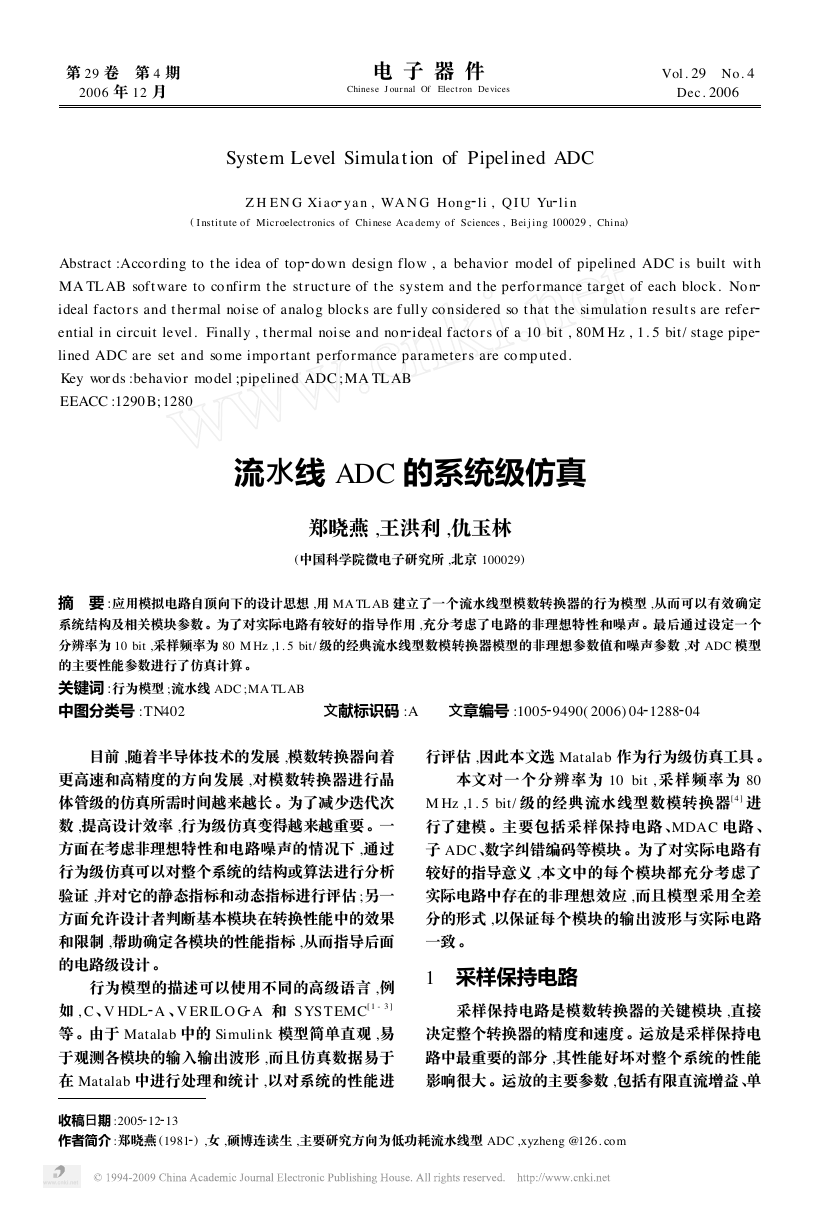

数据处理后得出信噪失真比为 61. 620 6 dB ,有效位

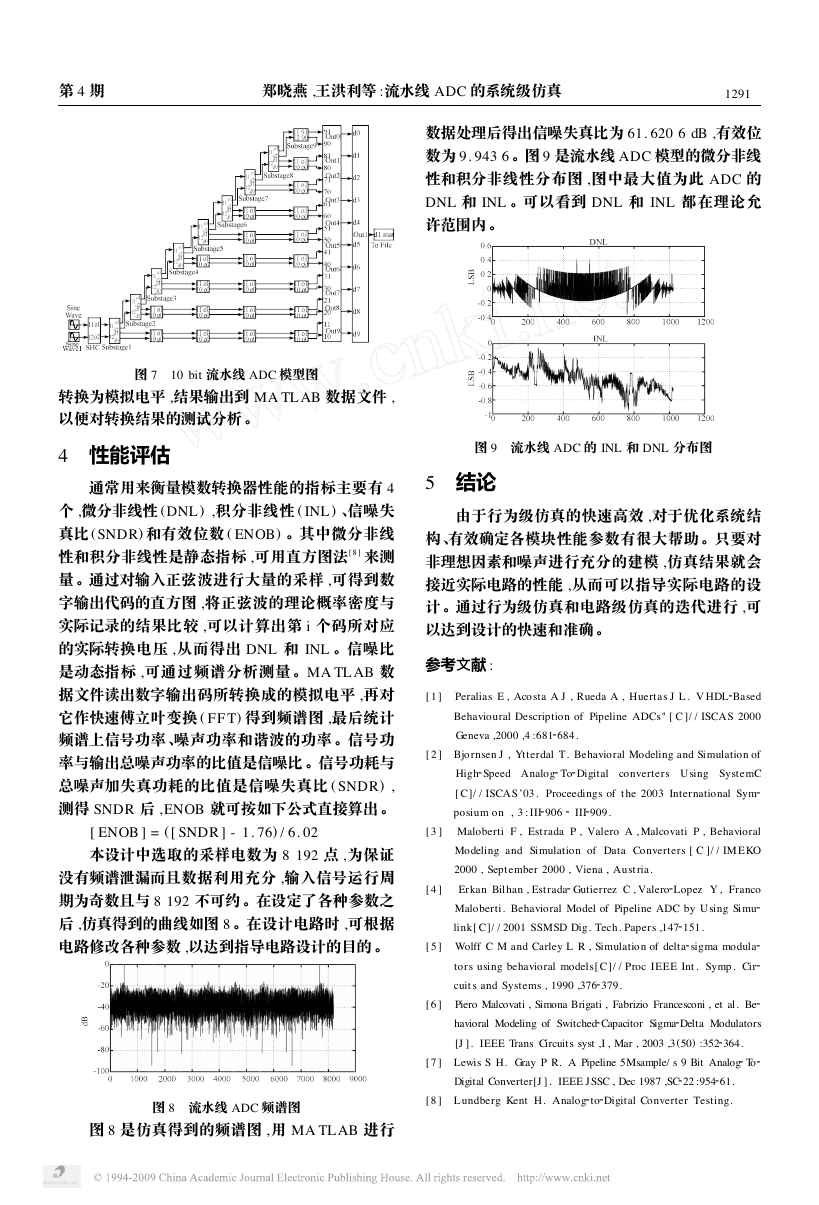

数为 9. 943 6 。图 9 是流水线 ADC 模型的微分非线

性和积分非线性分布图 ,图中最大值为此 ADC 的

DNL 和 INL 。可以看到 DNL 和 INL 都在理论允

许范围内 。

2

2

2

2

2

2

2

2

2

2

2

2

2

2

图 7 10 bit 流水线 ADC 模型图

转换为模拟电平 ,结果输出到 MA TL AB 数据文件 ,

以便对转换结果的测试分析 。

4 性能评估

通常用来衡量模数转换器性能的指标主要有 4

个 ,微分非线性 (DNL ) ,积分非线性 ( INL ) 、信噪失

真比 ( SNDR) 和有效位数 ( ENOB) 。其中微分非线

性和积分非线性是静态指标 ,可用直方图法[ 8 ] 来测

量 。通过对输入正弦波进行大量的采样 ,可得到数

字输出代码的直方图 ,将正弦波的理论概率密度与

实际记录的结果比较 ,可以计算出第 i 个码所对应

的实际转换电压 ,从而得出 DNL 和 INL 。信噪比

是动态指标 ,可通过频谱分析测量 。MA TL AB 数

据文件读出数字输出码所转换成的模拟电平 ,再对

它作快速傅立叶变换 ( FF T) 得到频谱图 ,最后统计

频谱上信号功率 、噪声功率和谐波的功率 。信号功

率与输出总噪声功率的比值是信噪比 。信号功耗与

总噪声加失真功耗的比值是信噪失真比 ( SNDR) ,

测得 SNDR 后 , ENOB 就可按如下公式直接算出 。

[ ENOB ] = ( [ SNDR ] - 1. 76) / 6. 02

本设计中选取的采样电数为 8 192 点 ,为保证

没有频谱泄漏而且数据利用充分 ,输入信号运行周

期为奇数且与 8 192 不可约 。在设定了各种参数之

后 ,仿真得到的曲线如图 8 。在设计电路时 ,可根据

电路修改各种参数 ,以达到指导电路设计的目的 。

图 9 流水线 ADC 的 INL 和 DNL 分布图

5 结论

由于行为级仿真的快速高效 ,对于优化系统结

构 、有效确定各模块性能参数有很大帮助 。只要对

非理想因素和噪声进行充分的建模 ,仿真结果就会

接近实际电路的性能 ,从而可以指导实际电路的设

计 。通过行为级仿真和电路级仿真的迭代进行 ,可

以达到设计的快速和准确 。

参考文献 :

[ 1 ] Peralias E , Acosta A J , Rueda A , Huertas J L . V HDL

Based

Behavioural Description of Pipeline ADCs" [ C ]/ / ISCAS 2000

Geneva ,2000 ,4 :681

684.

[ 2 ] Bjornsen J , Ytterdal T. Behavioral Modeling and Simulation of

converters Using SystemC

Speed Analog

Digital

High

To

[ C]/ / ISCAS’03. Proceedings of t he 2003 International Sym

posium on , 3 : III

906

III

909.

[ 3 ] Maloberti F , Est rada P , Valero A , Malcovati P , Behavioral

Modeling and Simulation of Data Converters [ C ]/ / IME KO

2000 , September 2000 , Viena , Aust ria.

[ 4 ] Erkan Bilhan , Est rada

Gutierrez C , Valero

Lopez Y , Franco

Maloberti. Behavioral Model of Pipeline ADC by U sing Simu

link[ C]/ / 2001 SSMSD Dig. Tech. Papers ,147

[ 5 ] Wolff C M and Carley L R , Simulation of delta

151.

sigma modula

tors using behavioral models[ C]/ / Proc IEEE Int . Symp . Cir

cuit s and Systems , 1990 ,376

379.

[ 6 ] Piero Malcovati , Simona Brigati , Fabrizio Francesconi , et al. Be

Delta Modulators

havioral Modeling of Switched

[J ]. IEEE Trans Circuits syst ,I , Mar , 2003 ,3 (50) :352

364.

[ 7 ] Lewis S H. Gray P R. A Pipeline 5Msample/ s 9 Bit Analog

61.

Digital Converter[J ]. IEEE J SSC , Dec 1987 ,SC

Capacitor Sigma

22 :954

To

图 8 流水线 ADC 频谱图

图 8 是仿真得到的频谱图 ,用 MA TL AB 进行

[ 8 ] L undberg Kent H. Analog

to

Digital Converter Testing.

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc