39899 Balentine Drive, Suite 125

Newark, CA 94560

eDPTM

Phone: 510 651 5122

Fax: 510 651 5127

URL: www.vesa.org

VESA Embedded DisplayPort Standard

Version 1.3

13 January 2011

Purpose

This standard defines requirements and options of a standardized display panel interface for embedded display

applications. It is based on the VESA DisplayPort Standard Version 1.2 and includes implementation options

recommended for consideration by the system integrator.

Summary

DisplayPort 1.2 is a scalable and extendable video data interface developed for use in both embedded (internal)

and external (box-to-box) applications. While DisplayPort™ does reference embedded applications; it is primarily

oriented toward external applications with emphasis on interoperability between system vendors and interconnect

cables. This standard defines a feature set of an embedded version of DisplayPort for applications including, but

not limited to, notebook PCs and all-in-one PCs.

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 1 of 81

Version 1.3

�

Table of Contents

Purpose .................................................................................................................................................. 1

Summary ................................................................................................................................................ 1

Preface ................................................................................................................................................... 6

Acknowledgements ................................................................................................................................ 8

Revision History .................................................................................................................................... 9

1

Overview ........................................................................................................................................ 11

1.1

Background .............................................................................................................................. 11

1.2

Acronyms ................................................................................................................................. 12

1.3

Glossary ................................................................................................................................... 13

1.4

References ................................................................................................................................ 15

2

eDP System Architecture ............................................................................................................... 16

2.1

eDP System Application .......................................................................................................... 16

2.2

eDP Support by Source and Sink Components ....................................................................... 16

3

Embedded DisplayPort Implementation ........................................................................................ 17

3.1

Background .............................................................................................................................. 17

3.2

eDP Feature Requirements and Recommendations ................................................................. 17

3.3

Number of Main Link Lanes vs. Video Mode Support (Informative) .................................... 19

3.4

eDP AUX Link Services .......................................................................................................... 21

3.5

PSR Secondary Data Packet Support ...................................................................................... 37

3.6

Support for Display Authentication and Content Protection ................................................... 39

3.7

Panel Input Power (LCDVCC) ................................................................................................ 46

3.8

Main Stream Attribute Data ..................................................................................................... 46

3.9

Display Backlight Control Using DPCD Registers ................................................................. 47

3.10

LCD Panel Self-Test (Informative) ......................................................................................... 52

4

Panel Self Refresh (PSR) ............................................................................................................... 54

4.1

Architecture Overview ............................................................................................................. 54

4.1.1

Source Responsibilities ................................................................................................................. 55

4.1.2

Sink Responsibilities ..................................................................................................................... 55

4.2

Configuration ........................................................................................................................... 56

4.3

PSR Entry/Exit Protocols ........................................................................................................ 57

4.3.1

PSR States ..................................................................................................................................... 57

4.3.2

PSR Entry ...................................................................................................................................... 60

4.3.3

PSR Exit ........................................................................................................................................ 62

4.3.4

PSR Entry Abort ........................................................................................................................... 65

4.3.5

Single Frame Updates .................................................................................................................. 66

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 2 of 81

Version 1.3

�

4.3.6

Burst Single Frame Updates ......................................................................................................... 67

4.4

Error Management/Recovery ................................................................................................... 67

4.4.1

CRC Verification Performed in Source ........................................................................................ 68

4.4.2

CRC Verification Performed in Sink ............................................................................................ 69

5

Power Sequencing ......................................................................................................................... 71

6

eDP Connector Pin Assignments ................................................................................................... 74

7

Labeling for the eDP Interface ...................................................................................................... 78

8

Appendix A: Main Contribution History ....................................................................................... 79

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 3 of 81

Version 1.3

�

Tables

Table 1: Main Contributors to Version 1.3 ....................................................................................................... 8

Table 1-1: Reference Documents ..................................................................................................................... 15

Table 3-1: eDP Features and Recommended Configurations ........................................................................... 17

Table 3-2: Bit Rate Capacity for Possible eDP Main Link Configurations (Informative) ............................... 19

Table 3-3: Supported Video Mode Examples for Common eDP Configurations (Informative) ..................... 20

Table 3-4: Assignment of DPCD Register 0000Dh Bit 3 within eDP v1.2 ..................................................... 21

Table 3-5: Display Control DPCD Registers Listed as Reserved within DisplayPort v1.2 ............................. 23

Table 3-6: DPCD – Sink PSR Capability Field ................................................................................................ 32

Table 3-7: DPCD – Sink PSR Configuration Field .......................................................................................... 33

Table 3-8: DPCD – Sink PSR Status Field ....................................................................................................... 34

Table 3-9: Video Stream Configuration Packet ................................................................................................ 38

Table 3-10: Video Stream Configuration Packet Header ................................................................................. 38

Table 3-11: Video Stream Configuration Packet DB1 ..................................................................................... 39

Table 3-12: Video Stream Configuration Packet DB2-3 .................................................................................. 39

Table 3-13: Video Stream Configuration Packet DB4-5 .................................................................................. 39

Table 3-14: Video Stream Configuration Packet DB6-7 .................................................................................. 39

Table 3-15: Optional eDP Display Authentication and Content Protection Methods ...................................... 40

Table 3-16: Expanded Description of Figure 3-6 ............................................................................................. 46

Table 3-17: Set of MSA Timing Parameters That May Be Ignored ................................................................. 46

Table 3-18: DPCD Register Bits That Determines Use of Parameters in Table 3-17 ...................................... 47

Table 3-19: Summary of Backlight Control Modes Using DPCD Registers in Table 3-5 ................................ 50

Table 3-20: LCD Self-Test Color Square Definition ....................................................................................... 53

Table 4-1: Sink Action for Single Frame Update .............................................................................................. 66

Table 5-1: eDP Panel Power Sequence Timing Parameters ............................................................................. 72

Table 6-1: 20-Pin eDP Pin Assignment for CCFL Backlight (1 or 2 Lane eDP) ............................................. 74

Table 6-2: 30-Pin eDP Pin Assignment for LED Backlight w/o LED Driver on PCB (1 or 2 Lane eDP) ...... 75

Table 6-3: 30-Pin eDP Pin Assignment for LED Backlight with LED Driver on PCB (1 or 2 Lane eDP) ..... 76

Table 6-4: 40-Pin eDP Pin Assignment for LED Backlight with LED Driver on PCB (up to 4 Lane eDP) ... 77

Table 8-1: Main Contributors to Version 1 ...................................................................................................... 79

Table 8-2: Main Contributors to Version 1.1a .................................................................................................. 80

Table 8-3: Main Contributors to Version 1.2 ................................................................................................... 81

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 4 of 81

Version 1.3

�

Figures

Figure 2-1: Typical System Implementation of eDP ........................................................................................ 16

Figure 3-1: Recommended eDP AUX Channel Topology ............................................................................... 18

Figure 3-2: Example of a Single eDP Panel Supporting Multiple Source Display Authentication Methods .. 41

Figure 3-3: eDP Panel Factory Production Process Operational Example ....................................................... 42

Figure 3-4: eDP Panel Embedded in Notebook PC Operational Example ....................................................... 43

Figure 3-5: eDP Panel Field Service Process Operational Example ................................................................ 44

Figure 3-6: Method 3a or 3b Identification and Control During Link Training Process ................................. 45

Figure 3-7: Control of Backlight via Timing Controller .................................................................................. 48

Figure 3-8: Control of Backlight via eDP Connector Interface ........................................................................ 49

Figure 3-9: TCON Circuit Blocks the Determine Panel Backlight Frequency ................................................ 51

Figure 3-10: LCD Panel Self-Test Patterns ...................................................................................................... 53

Figure 4-1: Panel Self Refresh System-level Diagram ...................................................................................... 54

Figure 4-3: PSR Configuration .......................................................................................................................... 56

Figure 4-4: Source PSR States ........................................................................................................................... 58

Figure 4-5: Sink PSR States .............................................................................................................................. 59

Figure 4-6: PSR Entry for Source TX Off Case ................................................................................................ 60

Figure 4-7: PSR Entry when Source can’t Send PSR Active SDP before Setup Time ..................................... 61

Figure 4-8: PSR Exit Link Management With No Link Training ..................................................................... 63

Figure 4-9: PSR Exit Link Management ........................................................................................................... 64

Figure 4-10: PSR Entry Abort for Source TX Off Case .................................................................................... 65

Figure 4-11: Single Frame Update Timing Shown with Optional SDP for PSR Exit ....................................... 67

Figure 4-12: Burst Single Frame Update SDP Timing ...................................................................................... 67

Figure 4-13: CRC SDP Timing with Frame Capture Indication = 0 and for Single Frame Update ................. 70

Figure 4-14: CRC SDP Timing with Frame Capture Indication = 1 ................................................................. 70

Figure 5-1: eDP Interface Power Up/Down Sequence, Normal System Operation ......................................... 71

Figure 5-2: eDP Interface Power Up/Down Sequence, AUX Channel Transaction Only ............................... 71

Figure 7-1: Example of VESA DisplayPort Panel Showing Warning Label Affixed Near Connector ........... 78

Figure 7-2: Example of a DisplayPort Panel Warning Label ........................................................................... 78

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 5 of 81

Version 1.3

�

Preface

Intellectual Property

Copyright © 2008-2011 Video Electronics Standards Association. All rights reserved.

While every precaution has been taken in the preparation of this standard, the Video Electronics Standards

Association and its contributors assume no responsibility for errors or omissions, and make no warranties,

expressed or implied, of functionality or suitability for any purpose.

Trademarks

All trademarks used within this document are the property of their respective owners. CVT, DP, DisplayPort,

DisplayID, DDC, E-EDID, eDP, Embedded DisplayPort, MCCS and VESA are registered trademarks of the Video

Electronics Standards Association.

I2C is a trademark of Philips.

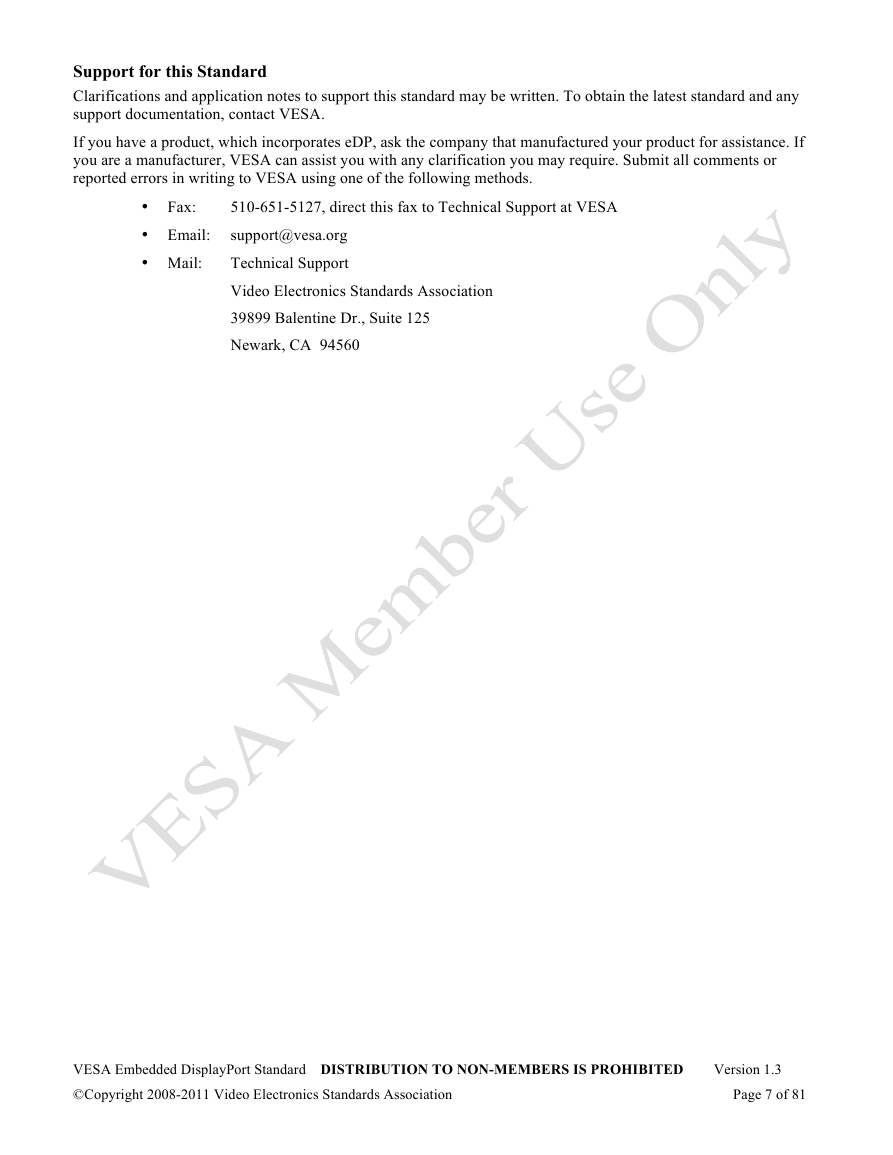

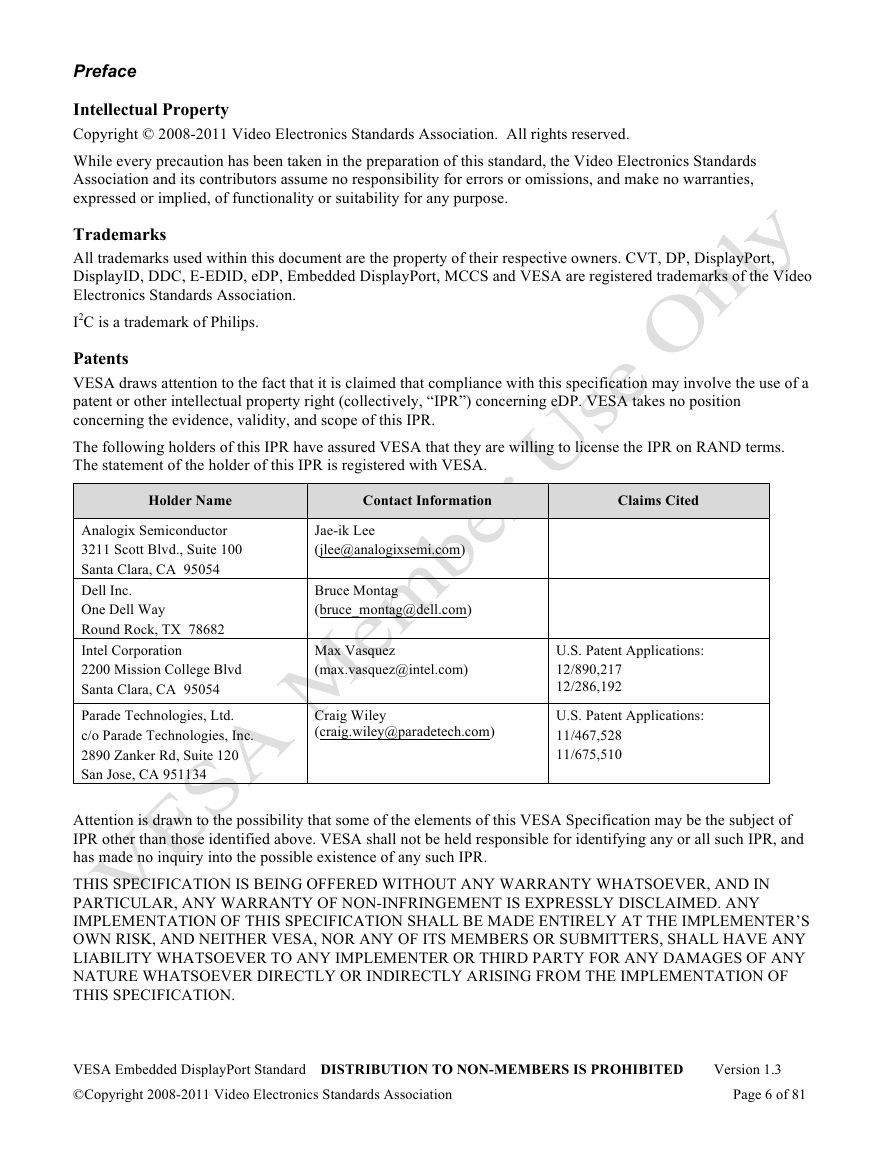

Patents

VESA draws attention to the fact that it is claimed that compliance with this specification may involve the use of a

patent or other intellectual property right (collectively, “IPR”) concerning eDP. VESA takes no position

concerning the evidence, validity, and scope of this IPR.

The following holders of this IPR have assured VESA that they are willing to license the IPR on RAND terms.

The statement of the holder of this IPR is registered with VESA.

Holder Name

Contact Information

Claims Cited

Analogix Semiconductor

3211 Scott Blvd., Suite 100

Santa Clara, CA 95054

Dell Inc.

One Dell Way

Round Rock, TX 78682

Intel Corporation

2200 Mission College Blvd

Santa Clara, CA 95054

Parade Technologies, Ltd.

c/o Parade Technologies, Inc.

2890 Zanker Rd, Suite 120

San Jose, CA 951134

Jae-ik Lee

(jlee@analogixsemi.com)

Bruce Montag

(bruce_montag@dell.com)

Max Vasquez

(max.vasquez@intel.com)

Craig Wiley

(craig.wiley@paradetech.com)

U.S. Patent Applications:

12/890,217

12/286,192

U.S. Patent Applications:

11/467,528

11/675,510

Attention is drawn to the possibility that some of the elements of this VESA Specification may be the subject of

IPR other than those identified above. VESA shall not be held responsible for identifying any or all such IPR, and

has made no inquiry into the possible existence of any such IPR.

THIS SPECIFICATION IS BEING OFFERED WITHOUT ANY WARRANTY WHATSOEVER, AND IN

PARTICULAR, ANY WARRANTY OF NON-INFRINGEMENT IS EXPRESSLY DISCLAIMED. ANY

IMPLEMENTATION OF THIS SPECIFICATION SHALL BE MADE ENTIRELY AT THE IMPLEMENTER’S

OWN RISK, AND NEITHER VESA, NOR ANY OF ITS MEMBERS OR SUBMITTERS, SHALL HAVE ANY

LIABILITY WHATSOEVER TO ANY IMPLEMENTER OR THIRD PARTY FOR ANY DAMAGES OF ANY

NATURE WHATSOEVER DIRECTLY OR INDIRECTLY ARISING FROM THE IMPLEMENTATION OF

THIS SPECIFICATION.

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 6 of 81

Version 1.3

�

Support for this Standard

Clarifications and application notes to support this standard may be written. To obtain the latest standard and any

support documentation, contact VESA.

If you have a product, which incorporates eDP, ask the company that manufactured your product for assistance. If

you are a manufacturer, VESA can assist you with any clarification you may require. Submit all comments or

reported errors in writing to VESA using one of the following methods.

• Fax:

• Email:

• Mail:

510-651-5127, direct this fax to Technical Support at VESA

support@vesa.org

Technical Support

Video Electronics Standards Association

39899 Balentine Dr., Suite 125

Newark, CA 94560

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 7 of 81

Version 1.3

�

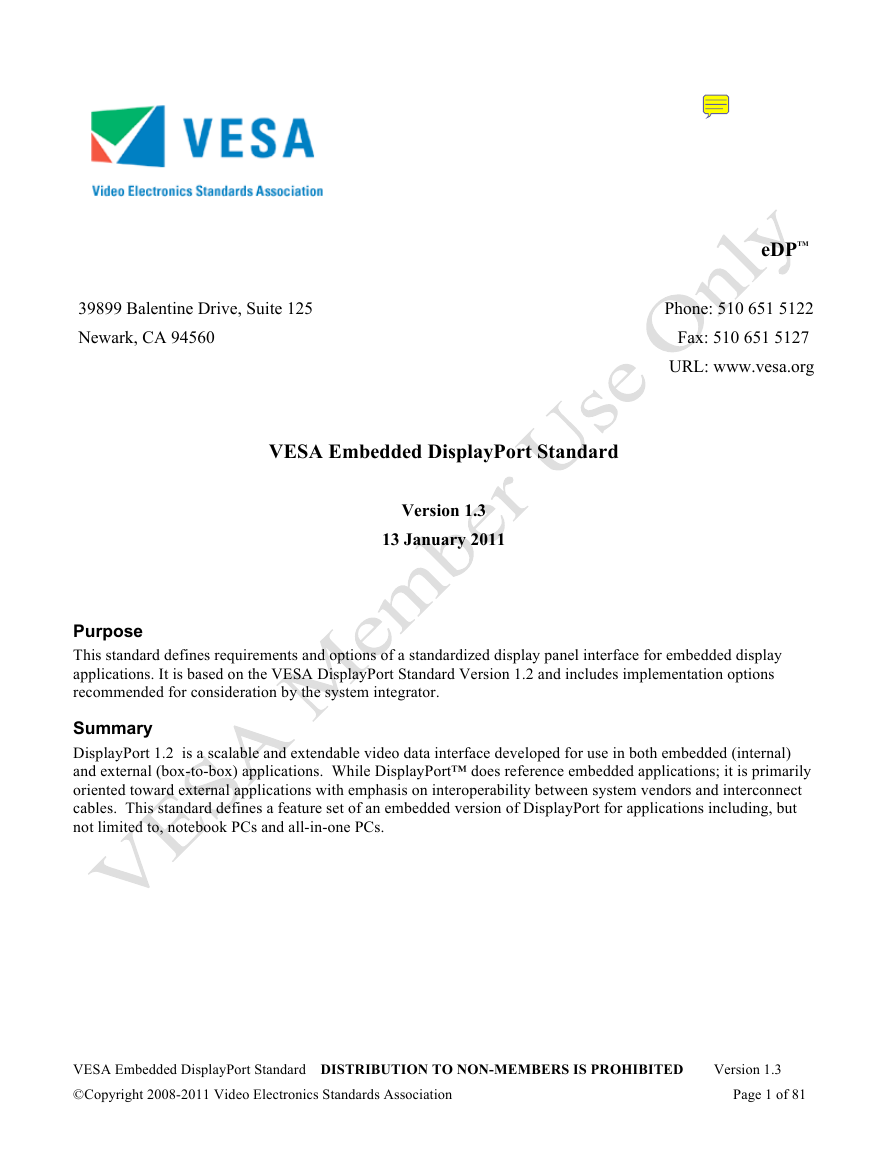

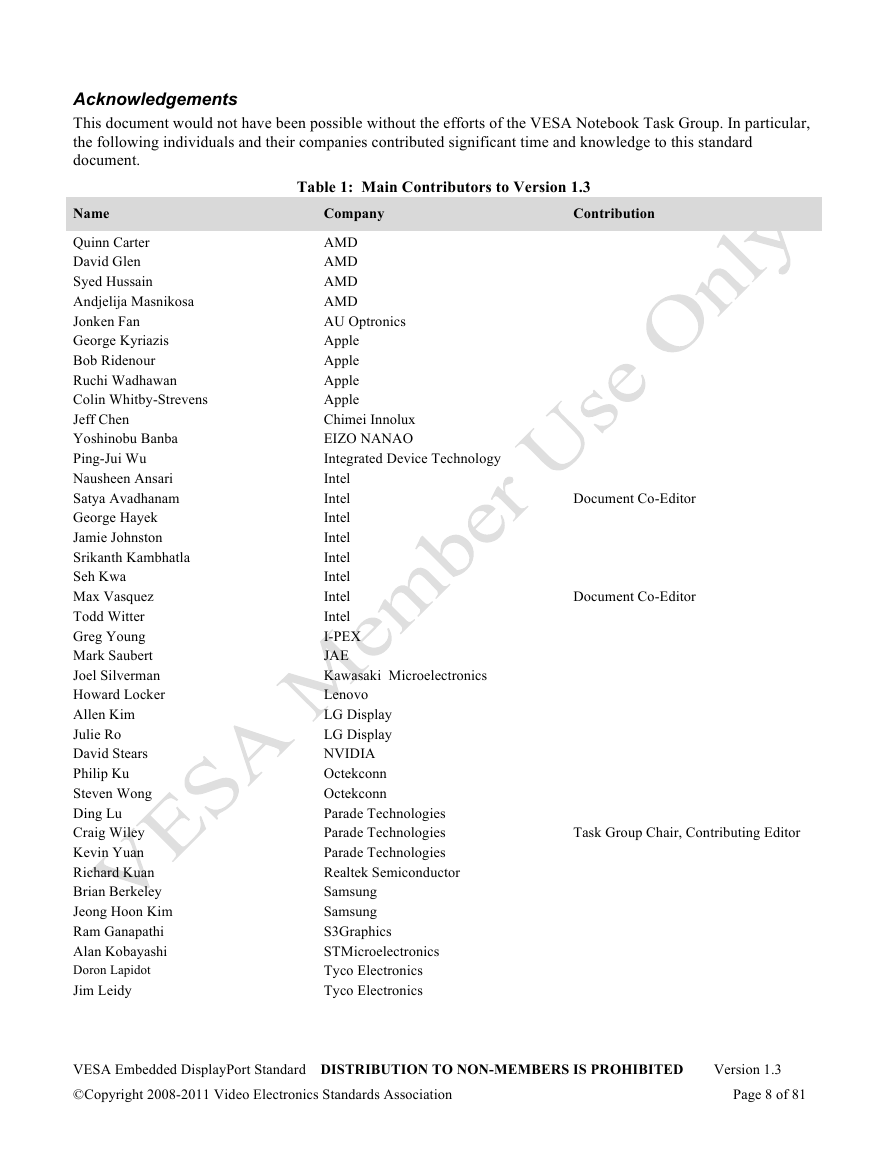

Acknowledgements

This document would not have been possible without the efforts of the VESA Notebook Task Group. In particular,

the following individuals and their companies contributed significant time and knowledge to this standard

document.

Name

Quinn Carter

David Glen

Syed Hussain

Andjelija Masnikosa

Jonken Fan

George Kyriazis

Bob Ridenour

Ruchi Wadhawan

Colin Whitby-Strevens

Jeff Chen

Yoshinobu Banba

Ping-Jui Wu

Nausheen Ansari

Satya Avadhanam

George Hayek

Jamie Johnston

Srikanth Kambhatla

Seh Kwa

Max Vasquez

Todd Witter

Greg Young

Mark Saubert

Joel Silverman

Howard Locker

Allen Kim

Julie Ro

David Stears

Philip Ku

Steven Wong

Ding Lu

Craig Wiley

Kevin Yuan

Richard Kuan

Brian Berkeley

Jeong Hoon Kim

Ram Ganapathi

Alan Kobayashi

Doron Lapidot

Jim Leidy

Table 1: Main Contributors to Version 1.3

Company

Contribution

AMD

AMD

AMD

AMD

AU Optronics

Apple

Apple

Apple

Apple

Chimei Innolux

EIZO NANAO

Integrated Device Technology

Intel

Intel

Intel

Intel

Intel

Intel

Intel

Intel

I-PEX

JAE

Kawasaki Microelectronics

Lenovo

LG Display

LG Display

NVIDIA

Octekconn

Octekconn

Parade Technologies

Parade Technologies

Parade Technologies

Realtek Semiconductor

Samsung

Samsung

S3Graphics

STMicroelectronics

Tyco Electronics

Tyco Electronics

Document Co-Editor

Document Co-Editor

Task Group Chair, Contributing Editor

VESA Embedded DisplayPort Standard DISTRIBUTION TO NON-MEMBERS IS PROHIBITED

©Copyright 2008-2011 Video Electronics Standards Association Page 8 of 81

Version 1.3

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc