作 业

第一讲:计算机系统基础

1. 在三台不同指令系统的计算机上运行同一程序 P 时,A 机需要执行 1.0*108 条指令,B 机

需要执行 2.0*108 条指令,C 机需要执行 4.0*108 条指令,但实际执行时间都是 10 秒,请分

别计算这三台机器在实行程序 P 时的实际运行速度,以 MIPS 为单位。这三台计算机在运行

程序 P 时,哪台性能最高?为什么?

2. 如果要给标量处理器增加向量运算部件,并且假定向量模式的运算速度是标量模式的 8

倍,这里把向量模式所占的百分比时间称作向量化百分比。

a) 画出一张图来表示加速比和向量化百分比的关系,X 轴为向量化百分比,Y 轴为加速比。

b) 向量化百分比为多少时,加速比能达到 2?当加速比达到 2 时,向量模式占了运算运行

时间的百分之多少?向量化百分比为多少时,加速比能达到最大加速比的一半?

c) 假设程序的向量化百分比为 70%。如果需要继续提升处理器的性能,一种方法是增加硬

件成本将向量部件的速度提高一倍,另外一种方法是通过改进编译器来提高向量模式的

应用范围,那么需要提升多少向量化百分比才能得到与向量部件运算速度提高一倍得到

相同的性能?你推荐哪一种设计方案?

3. 假设有一个代表典型应用的基准测试程序。一款不包含浮点部件的处理器(可以通过整

数指令的模拟来执行浮点指令)运行该基准程序的运行速度是 120MIPS,在该处理器上增加

浮点协处理器后运行该基准程序的运行速度是 80MIPS。下面给出了一些参数:I-基准测试

中整数指令的数目,F-基准测试中浮点指令的数目,Y-模拟一条浮点指令需要的整数指令

的数目,W-无浮点协处理器时基准程序的运行时间,B-有浮点协处理器时基准程序的运行

时间。

a) 用上面的参数符号表示出两种配置处理器的 MIPS 值。

b) 在没有协处理器的配置下,假定 F=8*106,Y=50,W=4 秒,求 I 的值。

c) 在上题的条件下,求 B 的值。

d) 在包含协处理器的配置下,系统的 MFLOPS 是多少?

e) 你的同事想要购买这种协处理器来提高性能,而该配置下 MIPS 降低了,请问他的决策

正确吗?解释你的观点。

4. 假设晶片成品率的经验公式如下:晶片成品率 = (1+b*晶片面积/a)-a,其中 a = 4 是衡

量工艺复杂度的参数。

a) 假设每 cm2 晶圆的成本为 c,缺陷密度为 b = 0.6/cm2,利用电子表格,计算当晶片面积

1

�

从 0.5cm2 变化到 4cm2 时晶片的成本。然后,适用数学分析工具拟合出晶片成本和面积关

系的多项式曲线,使其与电子表格中计算出来的数据相吻合。

b) 假设缺陷密度更高,b = 2.0/cm2,求最接近的最低次数的多项式。

5. 对某处理器进行功耗测试,得到如下数据:时钟不翻转,电压 1.2V 时,电流为 500mA;

时钟频率为 1GHz,电压 1.2V 时,电流为 2500mA。请计算此处理器的静态功耗以及 500MHz

下的总功耗。

6. 证明以下结论:

a) N 个正数的几何平均小于算术平均;

b) 用归一化的 SPEC CPU2000 程序分值进行 A、B 两台机器的性能比较与所使用的参考机无

关;

7. 试讨论冯·诺伊曼结构的主要特点。

a) 查阅资料,分别给出一款 Intel、AMD、IBM 商业处理器的峰值性能和访存带宽。

b) 分析这 3 种处理器的访存带宽和存储层次参数(一级 cache 大小和延迟、二级 cache 大

小和延迟等)之间的关系。

8. 在一台个人计算机上(如 Pentium-4、Core、Opteron 的 CPU)

a) 查阅相关资料,给出该机器的浮点运算峰值。

2

�

第二讲:二进制与逻辑电路

9. 定点数的表示

a) 分别给出 64 位定点原码和补码表示的数的范围。

解:[-263, 263-1]

b) 在 32 位定点补码表示中,0x80000000 表示什么数?

解:-231

10. 浮点数的表示

a) 把单精度数转化为十进制数:0x7ff0000, 0xbe400000, 0xff800000

解 : 0x7ff0000=0,0000 1111,111 1111 0000 0000 0000 0000=(1.1111111)2*2(15-127)=

3.8368135610839464260099560574934e-34

0xbe400000=1,0111 1100,100 0000 0000 0000 0000=-(1.1)2*2(124-127)=-0.1875

0xff800000=1,1111 1111,000 0000 0000 0000 0000=-∞

b) 把双精度数转化为十进制数:0x4035000000000000, 0x8008000000000000

解 : 0x4035000000000000=0,10000000011,0101000000000000000000000000000000000000

000000000000=(1.0101)2*2(1027-1023)=21

0x8008000000000000

=

1,00000000000,1000000000000000000000000000000000000000

000000000000=-(0.1)2*2-1022=-2-1023

c) 把十进制数转化为单精度数:-100.0, 0.25

解:-100.0=-(1.100100)2*26=0b1 10000101 10010000000000000000000=0xc2c80000

0.25=(1.0)*2-2=0b0 01111101 00000000000000000000000=0x3e800000;

d) 把十进制数转化为双精度数:1024.0,0.25

解:1024.0=(1.0)*210=0x4090000000000000

0.25=(1.0)*2-2=0x3fd0000000000000

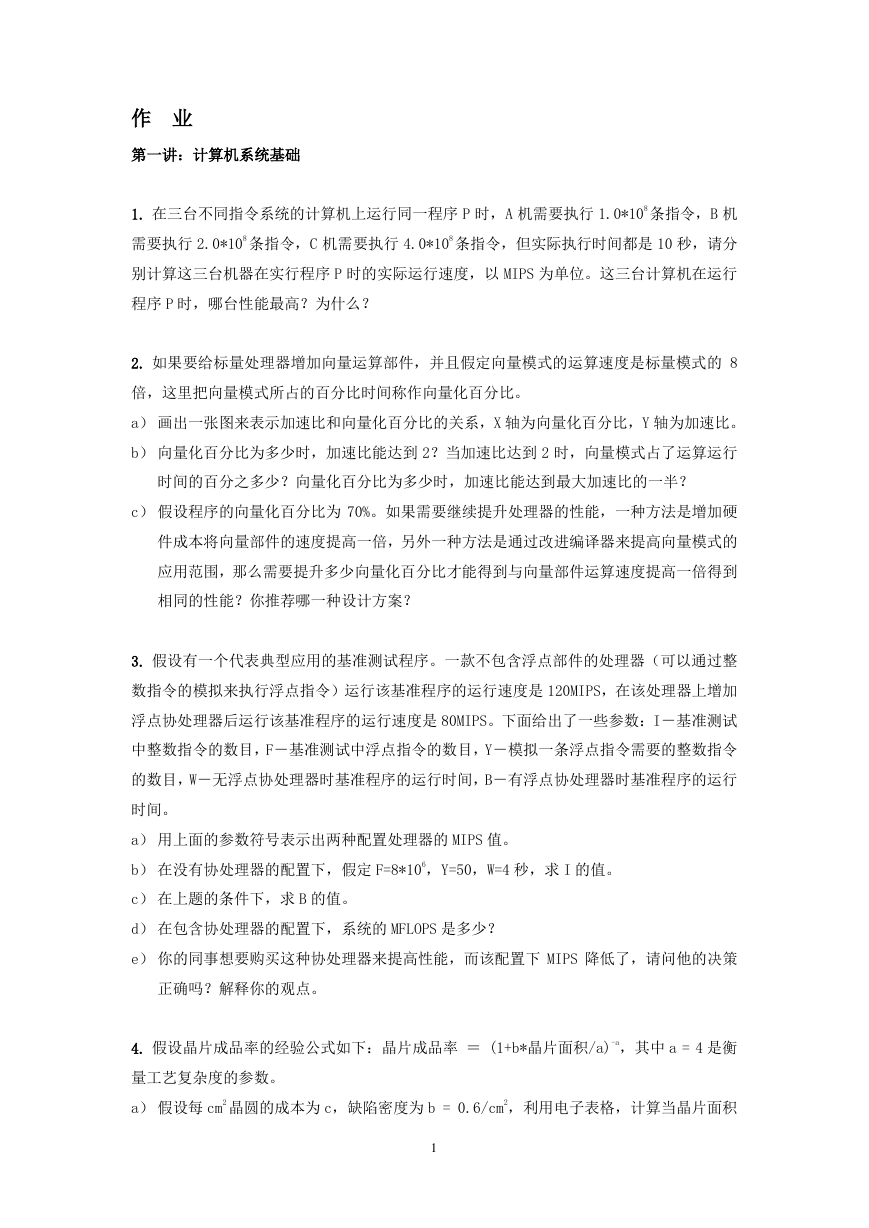

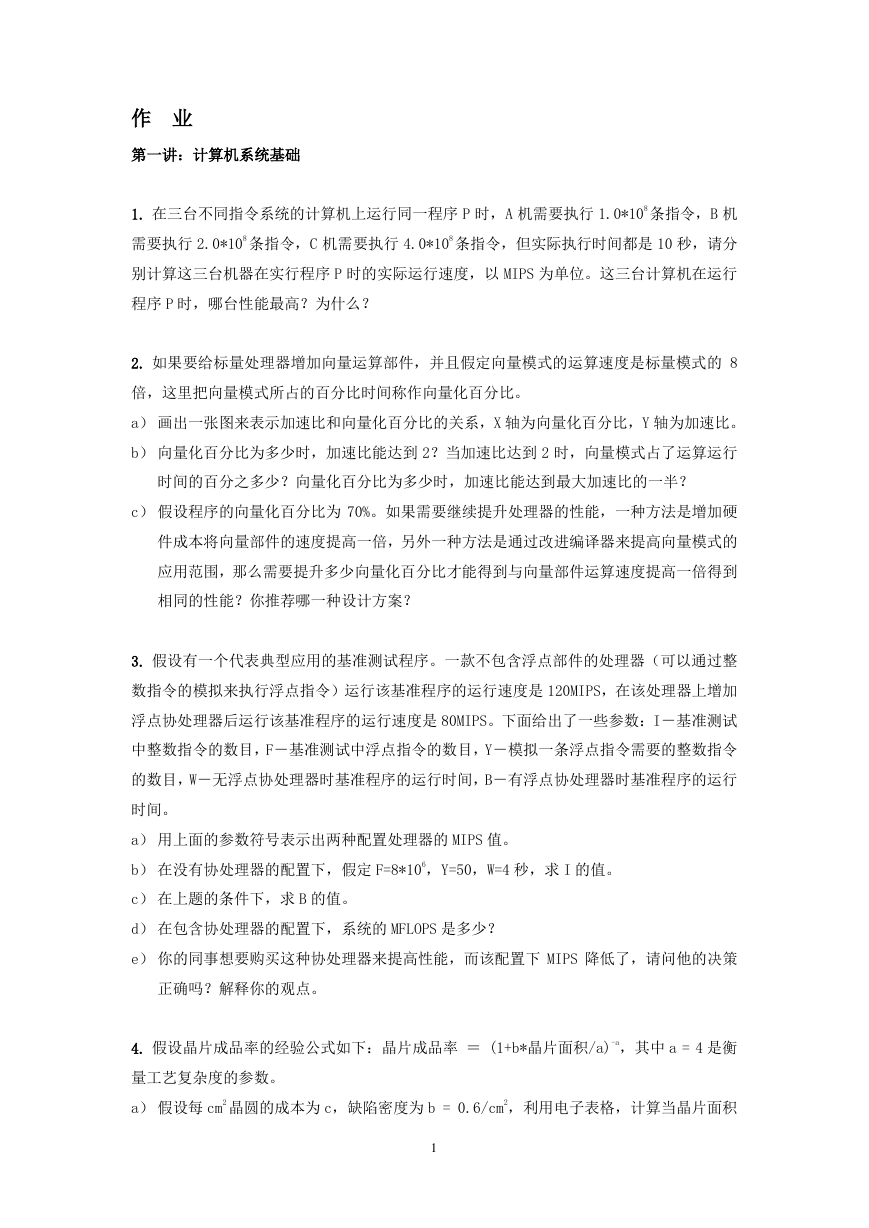

11. 画出 e=a*b+c*d 的晶体管级电路图。

解:

3

�

12. 计算一个 FO4 的延迟,假设反向器的输入电容为 0.0036pf,平均每个负载连线电容为

0.0044pf,翻转延迟为 0.023ns,每 pf 延迟为 4.5ns。

解:

FO4 指的是某类型的电路单元驱动四个相同类型的电路单元。

FO4 延迟=本征延迟+负载延迟=0.023+4.5*((0.0036+0.0044)*4)=0.167ns

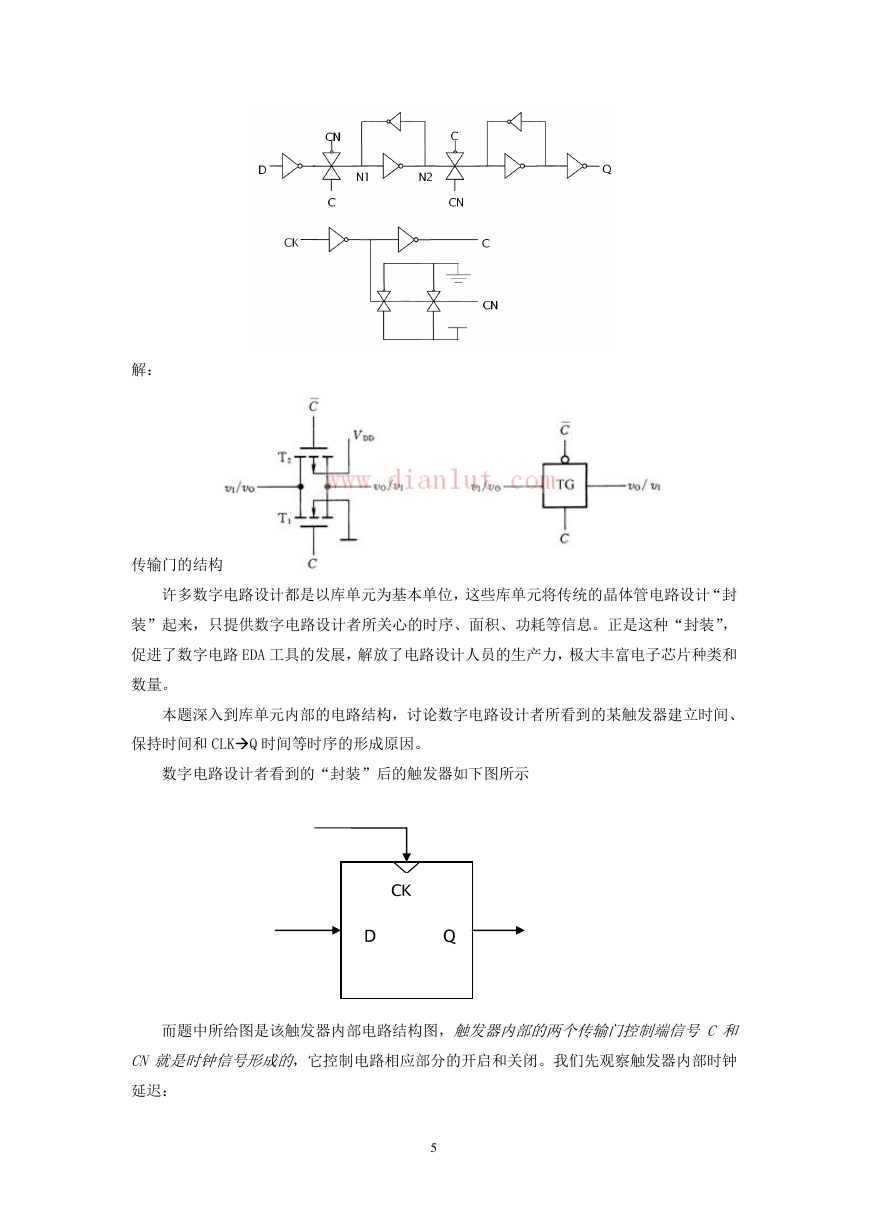

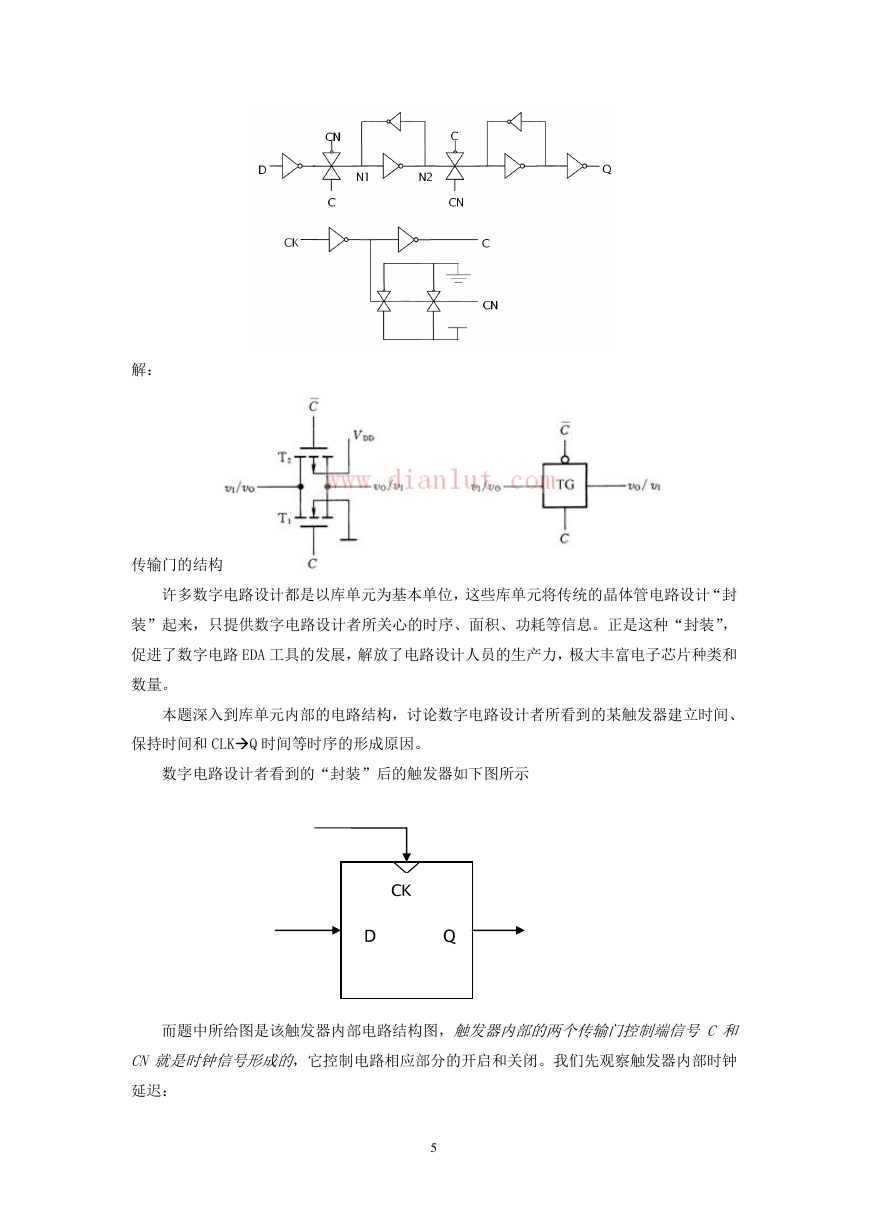

13. 分析 CMOS EDFF 触发器的建立时间、保持时间、和 CLK->Q 的构成。对于下图的电路,

假设反相器的延迟为 1ns,传输门从源到漏(或从漏到源)的延迟为 0.5ns,传输门从栅到漏

(或源)的延迟为 0.75ns,不考虑由于 latch 的 fight 对反相器延迟的影响。请从概念上

分析此电路的 setup 时间和 hold 时间为多少,给出分析过程。

4

VDDGNDababVDDGNDcdcdVDDGNDe�

解:

传输门的结构

许多数字电路设计都是以库单元为基本单位,这些库单元将传统的晶体管电路设计“封

装”起来,只提供数字电路设计者所关心的时序、面积、功耗等信息。正是这种“封装”,

促进了数字电路 EDA 工具的发展,解放了电路设计人员的生产力,极大丰富电子芯片种类和

数量。

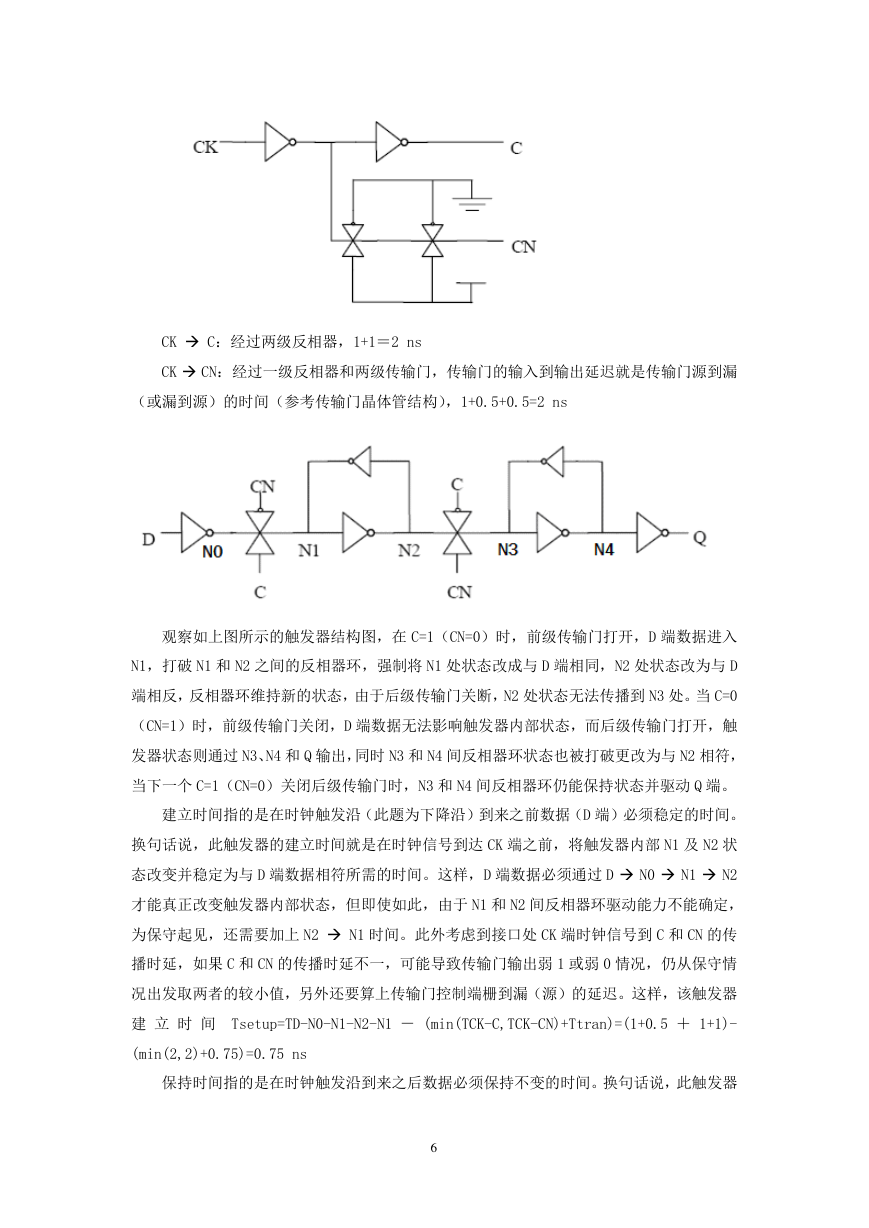

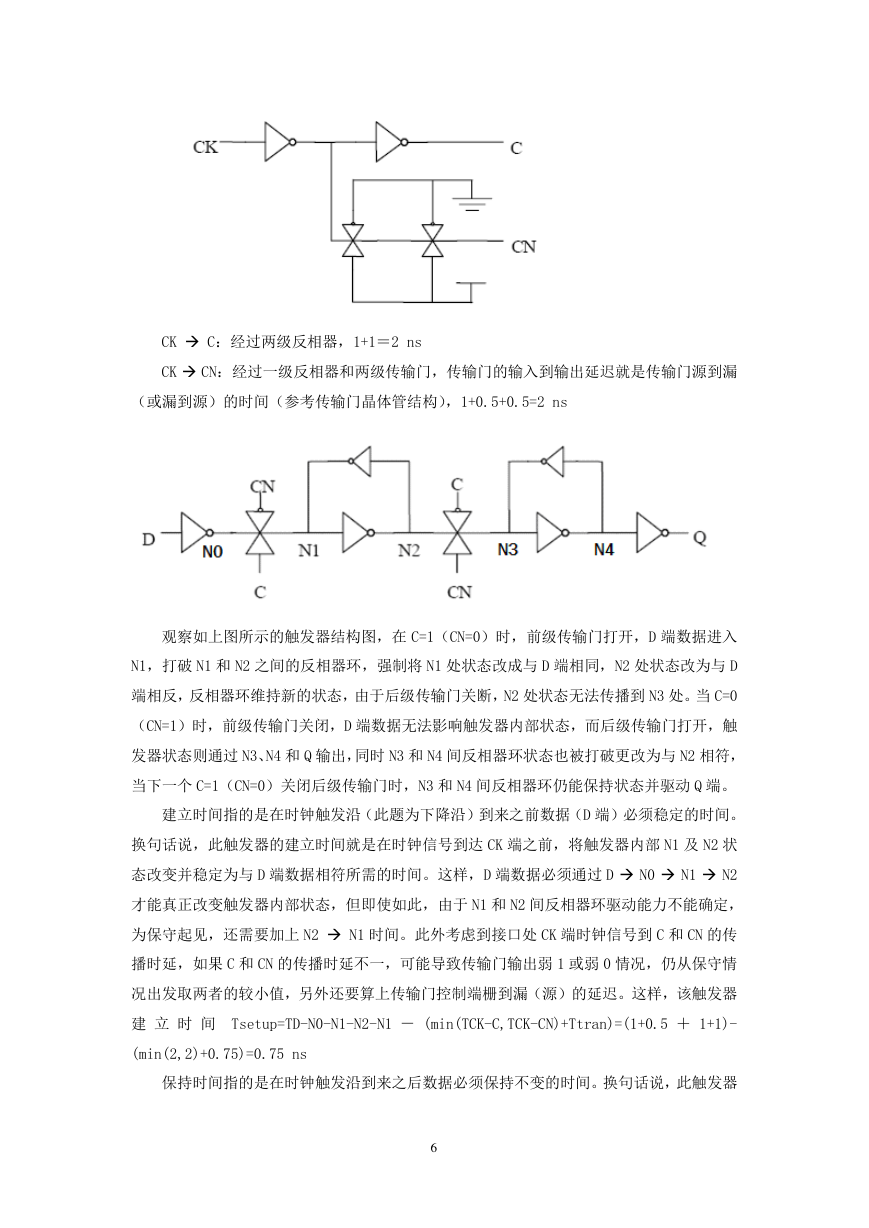

本题深入到库单元内部的电路结构,讨论数字电路设计者所看到的某触发器建立时间、

保持时间和 CLKQ 时间等时序的形成原因。

数字电路设计者看到的“封装”后的触发器如下图所示

而题中所给图是该触发器内部电路结构图,触发器内部的两个传输门控制端信号 C 和

CN 就是时钟信号形成的,它控制电路相应部分的开启和关闭。我们先观察触发器内部时钟

延迟:

5

�

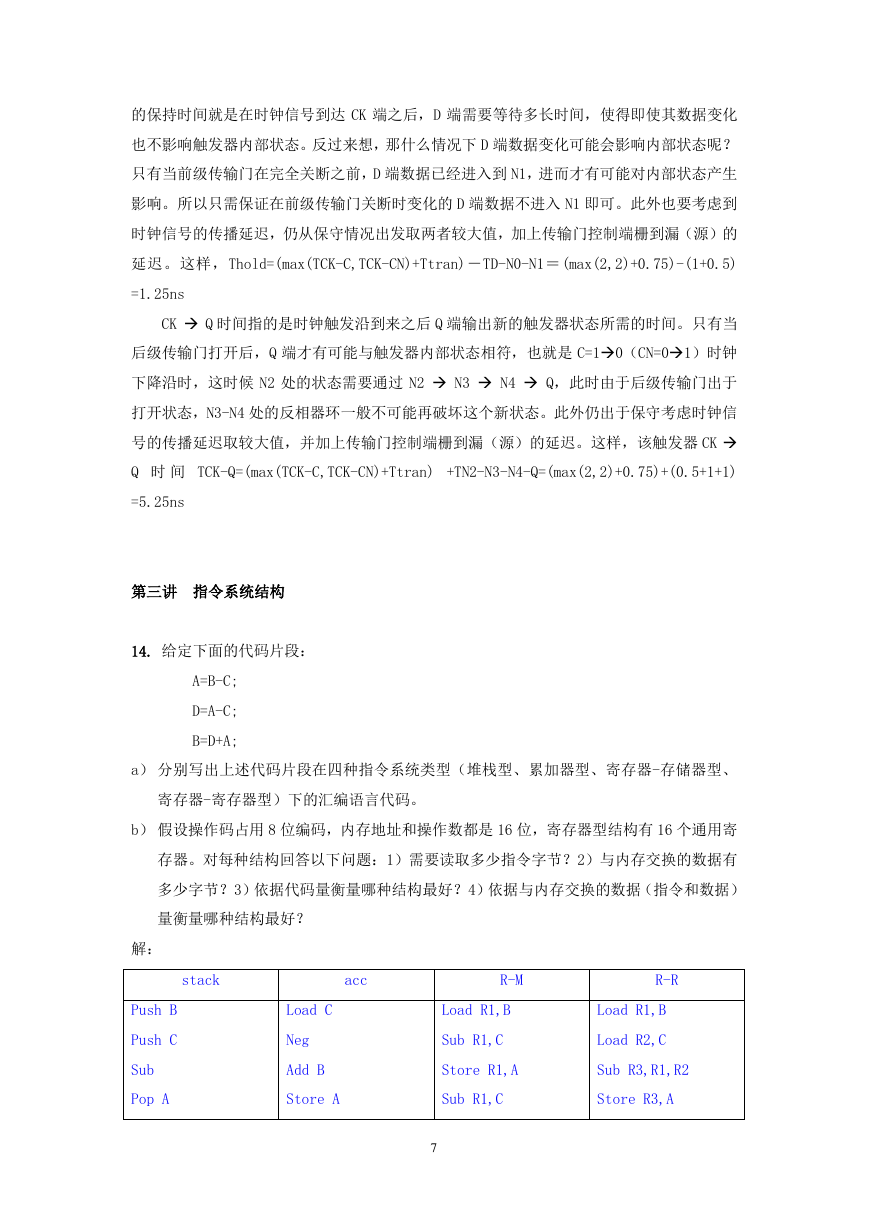

CK C:经过两级反相器,1+1=2 ns

CK CN:经过一级反相器和两级传输门,传输门的输入到输出延迟就是传输门源到漏

(或漏到源)的时间(参考传输门晶体管结构),1+0.5+0.5=2 ns

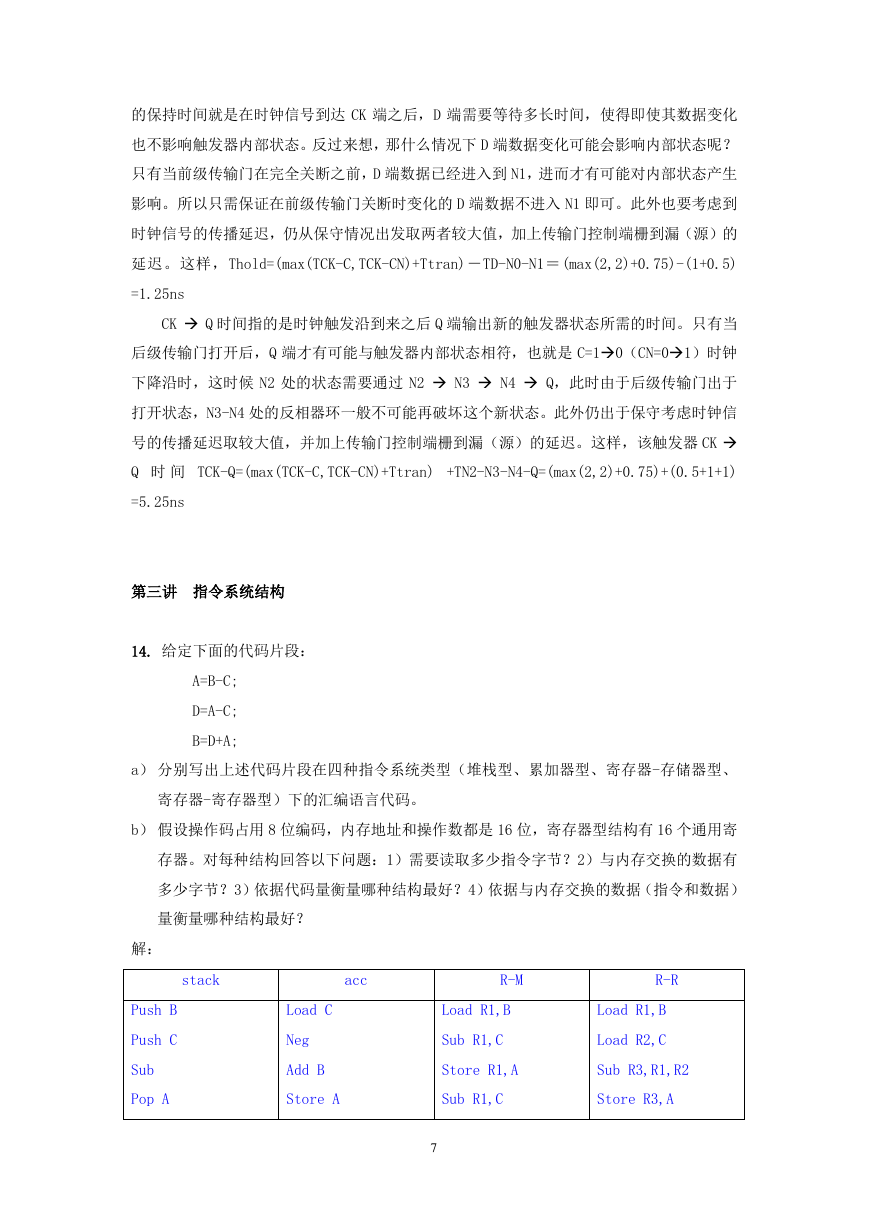

观察如上图所示的触发器结构图,在 C=1(CN=0)时,前级传输门打开,D 端数据进入

N1,打破 N1 和 N2 之间的反相器环,强制将 N1 处状态改成与 D 端相同,N2 处状态改为与 D

端相反,反相器环维持新的状态,由于后级传输门关断,N2 处状态无法传播到 N3 处。当 C=0

(CN=1)时,前级传输门关闭,D 端数据无法影响触发器内部状态,而后级传输门打开,触

发器状态则通过 N3、N4 和 Q 输出,同时 N3 和 N4 间反相器环状态也被打破更改为与 N2 相符,

当下一个 C=1(CN=0)关闭后级传输门时,N3 和 N4 间反相器环仍能保持状态并驱动 Q 端。

建立时间指的是在时钟触发沿(此题为下降沿)到来之前数据(D 端)必须稳定的时间。

换句话说,此触发器的建立时间就是在时钟信号到达 CK 端之前,将触发器内部 N1 及 N2 状

态改变并稳定为与 D 端数据相符所需的时间。这样,D 端数据必须通过 D N0 N1 N2

才能真正改变触发器内部状态,但即使如此,由于 N1 和 N2 间反相器环驱动能力不能确定,

为保守起见,还需要加上 N2 N1 时间。此外考虑到接口处 CK 端时钟信号到 C 和 CN 的传

播时延,如果 C 和 CN 的传播时延不一,可能导致传输门输出弱 1 或弱 0 情况,仍从保守情

况出发取两者的较小值,另外还要算上传输门控制端栅到漏(源)的延迟。这样,该触发器

建 立 时 间 Tsetup=TD-N0-N1-N2-N1 - (min(TCK-C,TCK-CN)+Ttran)=(1+0.5 + 1+1)-

(min(2,2)+0.75)=0.75 ns

保持时间指的是在时钟触发沿到来之后数据必须保持不变的时间。换句话说,此触发器

6

�

的保持时间就是在时钟信号到达 CK 端之后,D 端需要等待多长时间,使得即使其数据变化

也不影响触发器内部状态。反过来想,那什么情况下 D 端数据变化可能会影响内部状态呢?

只有当前级传输门在完全关断之前,D 端数据已经进入到 N1,进而才有可能对内部状态产生

影响。所以只需保证在前级传输门关断时变化的 D 端数据不进入 N1 即可。此外也要考虑到

时钟信号的传播延迟,仍从保守情况出发取两者较大值,加上传输门控制端栅到漏(源)的

延迟。这样,Thold=(max(TCK-C,TCK-CN)+Ttran)-TD-N0-N1=(max(2,2)+0.75)-(1+0.5)

=1.25ns

CK Q 时间指的是时钟触发沿到来之后 Q 端输出新的触发器状态所需的时间。只有当

后级传输门打开后,Q 端才有可能与触发器内部状态相符,也就是 C=10(CN=01)时钟

下降沿时,这时候 N2 处的状态需要通过 N2 N3 N4 Q,此时由于后级传输门出于

打开状态,N3-N4 处的反相器环一般不可能再破坏这个新状态。此外仍出于保守考虑时钟信

号的传播延迟取较大值,并加上传输门控制端栅到漏(源)的延迟。这样,该触发器 CK

Q 时 间 TCK-Q=(max(TCK-C,TCK-CN)+Ttran) +TN2-N3-N4-Q=(max(2,2)+0.75)+(0.5+1+1)

=5.25ns

第三讲 指令系统结构

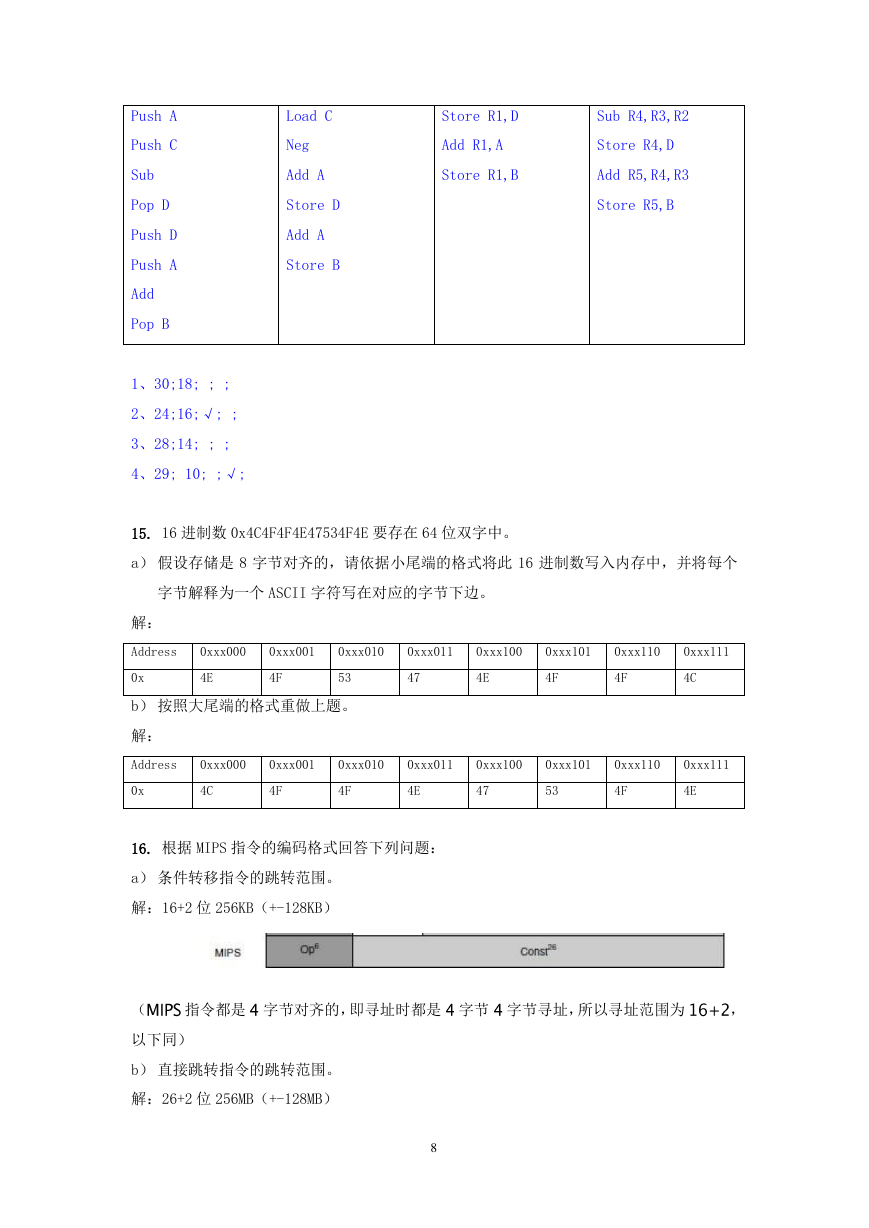

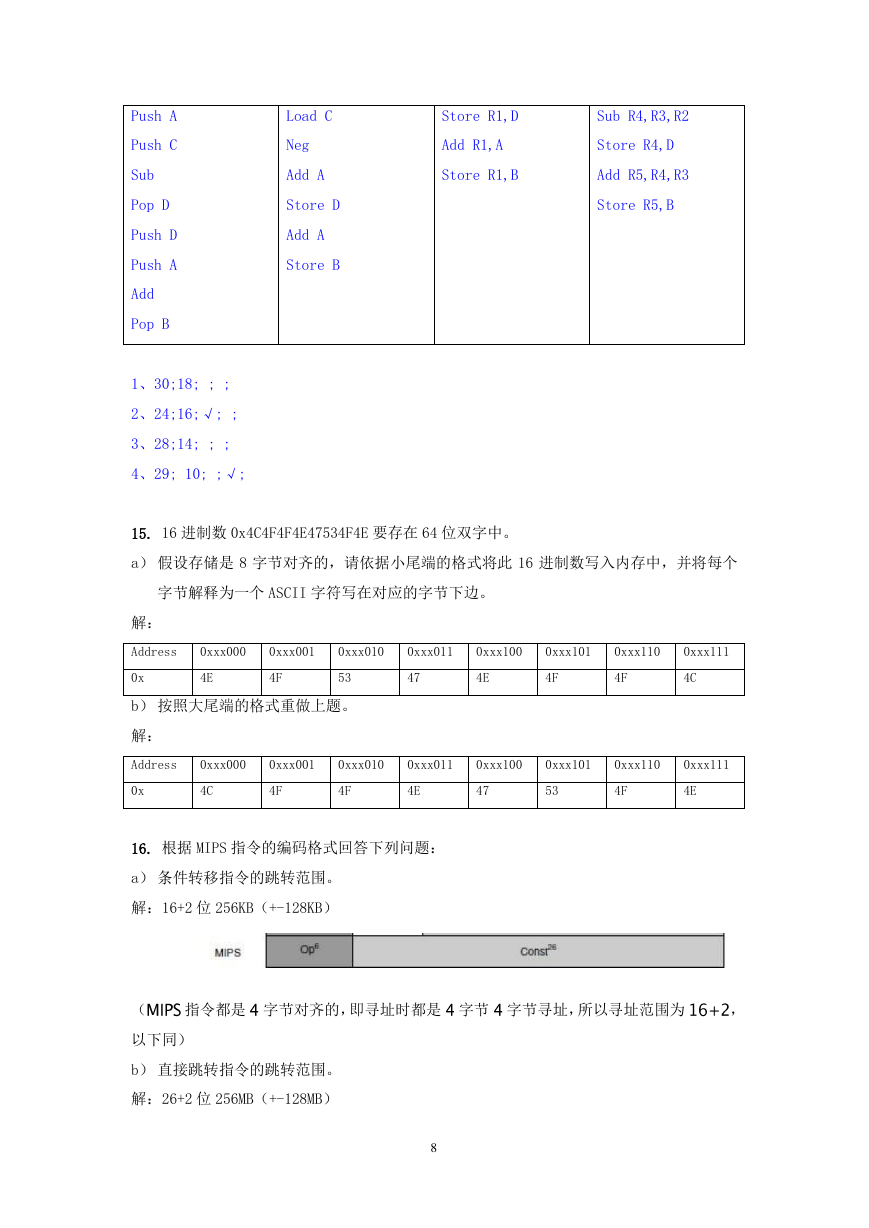

14. 给定下面的代码片段:

A=B-C;

D=A-C;

B=D+A;

a) 分别写出上述代码片段在四种指令系统类型(堆栈型、累加器型、寄存器-存储器型、

寄存器-寄存器型)下的汇编语言代码。

b) 假设操作码占用 8 位编码,内存地址和操作数都是 16 位,寄存器型结构有 16 个通用寄

存器。对每种结构回答以下问题:1)需要读取多少指令字节?2)与内存交换的数据有

多少字节?3)依据代码量衡量哪种结构最好?4)依据与内存交换的数据(指令和数据)

量衡量哪种结构最好?

解:

stack

acc

R-M

R-R

Push B

Push C

Sub

Pop A

Load C

Neg

Add B

Store A

Load R1,B

Sub R1,C

Load R1,B

Load R2,C

Store R1,A

Sub R3,R1,R2

Sub R1,C

Store R3,A

7

�

Store R1,D

Sub R4,R3,R2

Add R1,A

Store R4,D

Store R1,B

Add R5,R4,R3

Store R5,B

Load C

Neg

Add A

Store D

Add A

Store B

Push A

Push C

Sub

Pop D

Push D

Push A

Add

Pop B

1、30;18; ; ;

2、24;16;√; ;

3、28;14; ; ;

4、29; 10; ;√;

15. 16 进制数 0x4C4F4F4E47534F4E 要存在 64 位双字中。

a) 假设存储是 8 字节对齐的,请依据小尾端的格式将此 16 进制数写入内存中,并将每个

字节解释为一个 ASCII 字符写在对应的字节下边。

解:

Address

0xxx000

0xxx001

0xxx010

0xxx011

0xxx100

0xxx101

0xxx110

0xxx111

0x

4E

4F

53

47

4E

4F

4F

4C

b) 按照大尾端的格式重做上题。

解:

Address

0xxx000

0xxx001

0xxx010

0xxx011

0xxx100

0xxx101

0xxx110

0xxx111

4C

4F

4F

4E

47

53

4F

4E

0x

16. 根据 MIPS 指令的编码格式回答下列问题:

a) 条件转移指令的跳转范围。

解:16+2 位 256KB(+-128KB)

(

指令都是 字节对齐的,即寻址时都是 字节 字节寻址,所以寻址范围为

,

以下同)

b) 直接跳转指令的跳转范围。

解:26+2 位 256MB(+-128MB)

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc