MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

MEDIATEK CONFIDENTIAL

MT7620

DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

Page 1 of 56

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

Applications:

Routers

NAS devices

iNICs

Dual band

concurrent routers

Intelligent Clock Scaling (exclusive)

DDRII: ODT off, Self-refresh mode

SDRAM: Pre-charge power down

I2C, I2S, SPI, PCM, UART, JTAG, MDC, MDIO, GPIO

Hardware NAT with IPv6 and 2 Gbps wired speed

16 Multiple BSSID

WEP64/128, TKIP, AES, WPA, WPA2, WAPI

QoS: WMM, WMM-PS

WPS: PBC, PIN

Voice Enterprise: 802.11k+r

AP Firmware: Linux 2.6 SDK, eCOS with IPv6

RGMII iNIC Driver: Linux 2.4/2.6

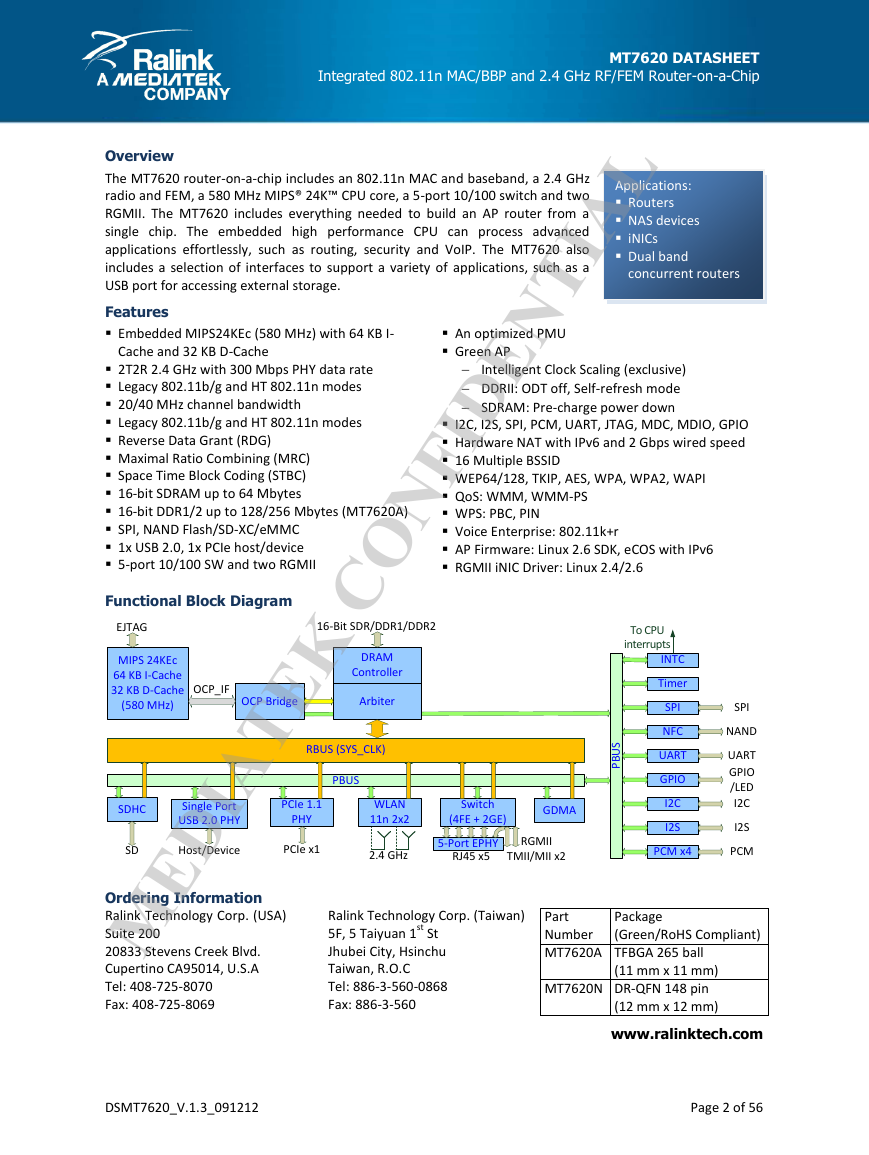

Overview

Cache and 32 KB D-Cache

An optimized PMU

Green AP

Features

Embedded MIPS24KEc (580 MHz) with 64 KB I-

The MT7620 router-on-a-chip includes an 802.11n MAC and baseband, a 2.4 GHz

radio and FEM, a 580 MHz MIPS® 24K™ CPU core, a 5-port 10/100 switch and two

RGMII. The MT7620 includes everything needed to build an AP router from a

single chip. The embedded high performance CPU can process advanced

applications effortlessly, such as routing, security and VoIP. The MT7620 also

includes a selection of interfaces to support a variety of applications, such as a

USB port for accessing external storage.

2T2R 2.4 GHz with 300 Mbps PHY data rate

Legacy 802.11b/g and HT 802.11n modes

20/40 MHz channel bandwidth

Legacy 802.11b/g and HT 802.11n modes

Reverse Data Grant (RDG)

Maximal Ratio Combining (MRC)

Space Time Block Coding (STBC)

16-bit SDRAM up to 64 Mbytes

16-bit DDR1/2 up to 128/256 Mbytes (MT7620A)

SPI, NAND Flash/SD-XC/eMMC

1x USB 2.0, 1x PCIe host/device

5-port 10/100 SW and two RGMII

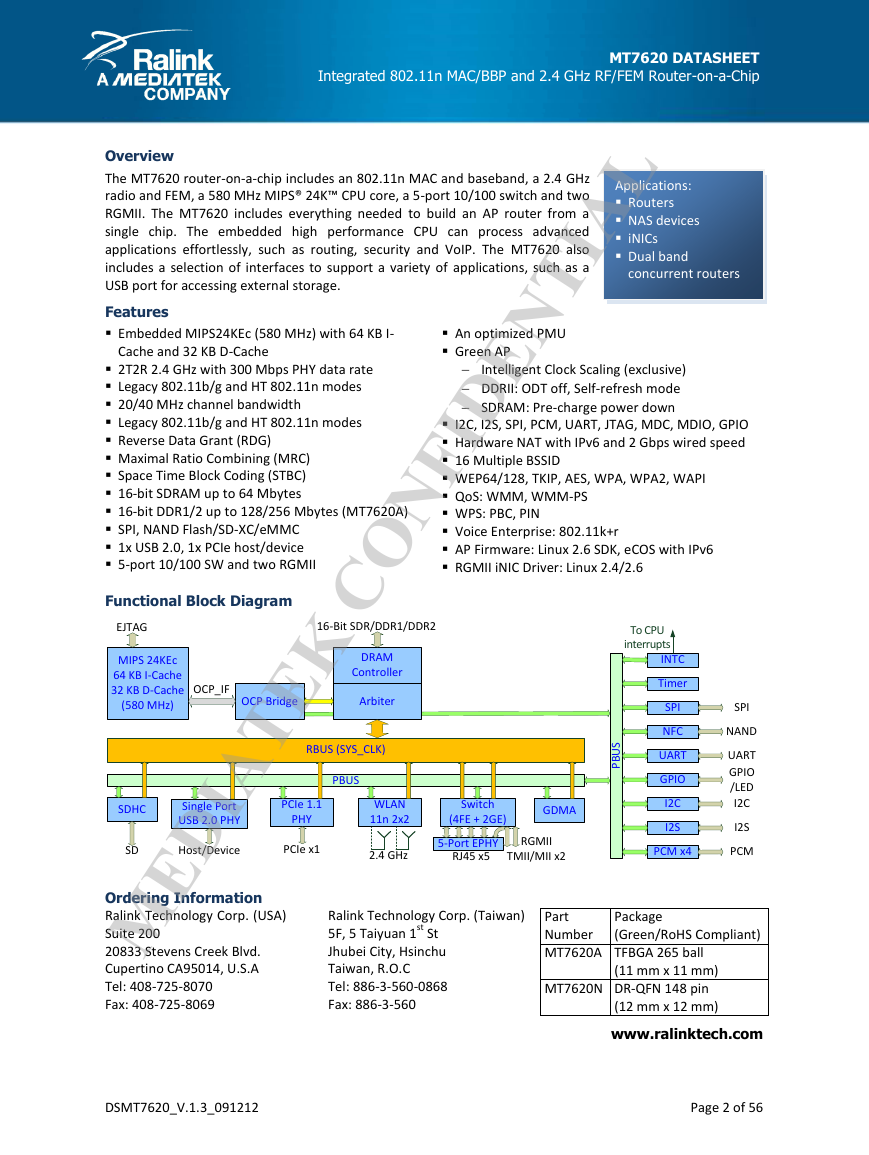

Functional Block Diagram

MEDIATEK CONFIDENTIAL

MIPS 24KEc

64 KB I-Cache

32 KB D-Cache

Single Port

USB 2.0 PHY

Switch

(4FE + 2GE)

16-Bit SDR/DDR1/DDR2

5-Port EPHY

RGMII

RJ45 x5

TMII/MII x2

SD

Host/Device

PCIe x1

OCP Bridge

Arbiter

WLAN

11n 2x2

2.4 GHz

OCP_IF

(580 MHz)

RBUS (SYS_CLK)

PBUS

DRAM

Controller

PCIe 1.1

PHY

EJTAG

S

U

B

P

GDMA

Ralink Technology Corp. (Taiwan)

5F, 5 Taiyuan 1st St

Jhubei City, Hsinchu

Taiwan, R.O.C

Tel: 886-3-560-0868

Fax: 886-3-560

SDHC

Ordering Information

Ralink Technology Corp. (USA)

Suite 200

20833 Stevens Creek Blvd.

Cupertino CA95014, U.S.A

Tel: 408-725-8070

Fax: 408-725-8069

To CPU

interrupts

INTC

Timer

SPI

NFC

UART

GPIO

I2C

I2S

PCM x4

SPI

NAND

UART

GPIO

/LED

I2C

I2S

PCM

Part

Number

MT7620A TFBGA 265 ball

Package

(Green/RoHS Compliant)

(11 mm x 11 mm)

MT7620N DR-QFN 148 pin

(12 mm x 12 mm)

www.ralinktech.com

Page 2 of 56

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

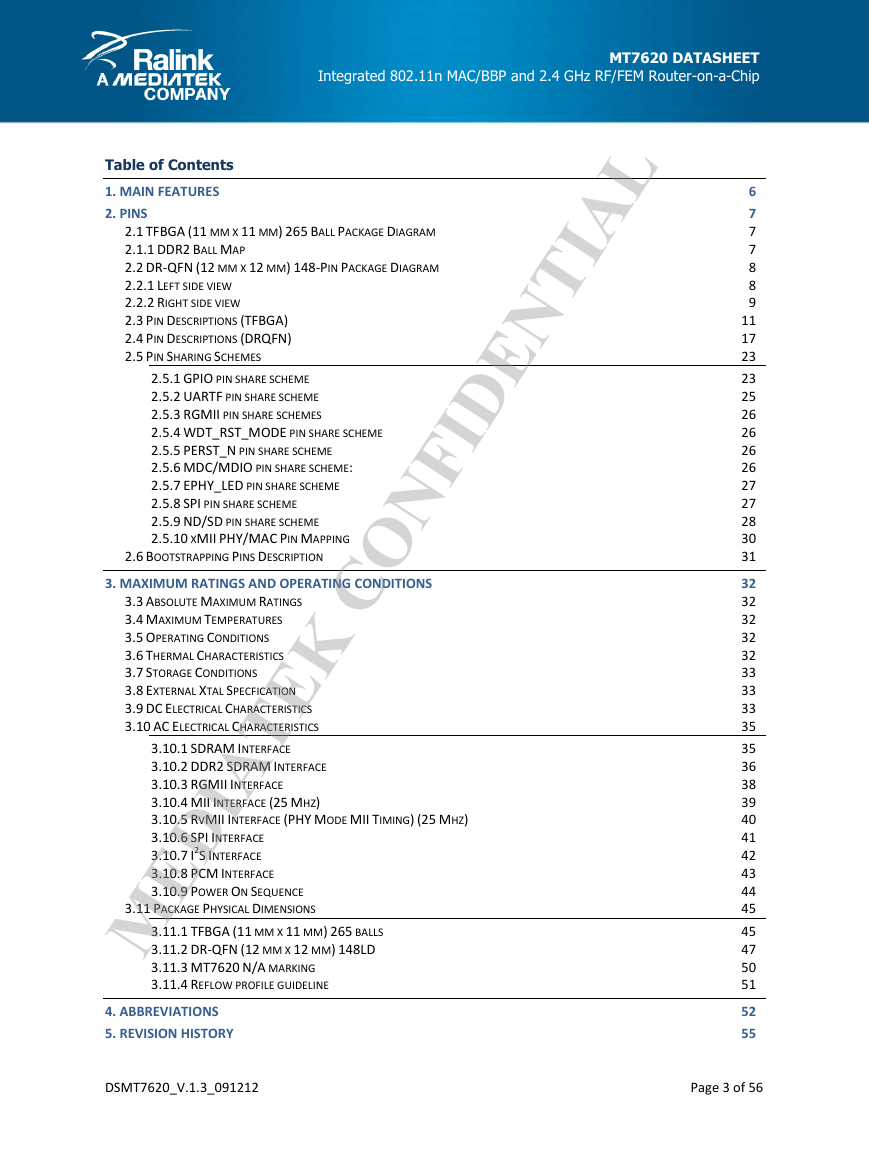

Table of Contents

1. MAIN FEATURES

2. PINS

6

7

7

7

8

8

9

11

17

23

23

25

26

26

26

26

27

27

28

30

31

32

32

32

32

32

33

33

33

35

35

36

38

39

40

41

42

43

44

45

45

47

50

51

52

55

Page 3 of 56

2.5.1 GPIO PIN SHARE SCHEME

2.5.2 UARTF PIN SHARE SCHEME

2.5.3 RGMII PIN SHARE SCHEMES

2.5.4 WDT_RST_MODE PIN SHARE SCHEME

2.5.5 PERST_N PIN SHARE SCHEME

2.5.6 MDC/MDIO PIN SHARE SCHEME:

2.5.7 EPHY_LED PIN SHARE SCHEME

2.5.8 SPI PIN SHARE SCHEME

2.5.9 ND/SD PIN SHARE SCHEME

2.5.10 XMII PHY/MAC PIN MAPPING

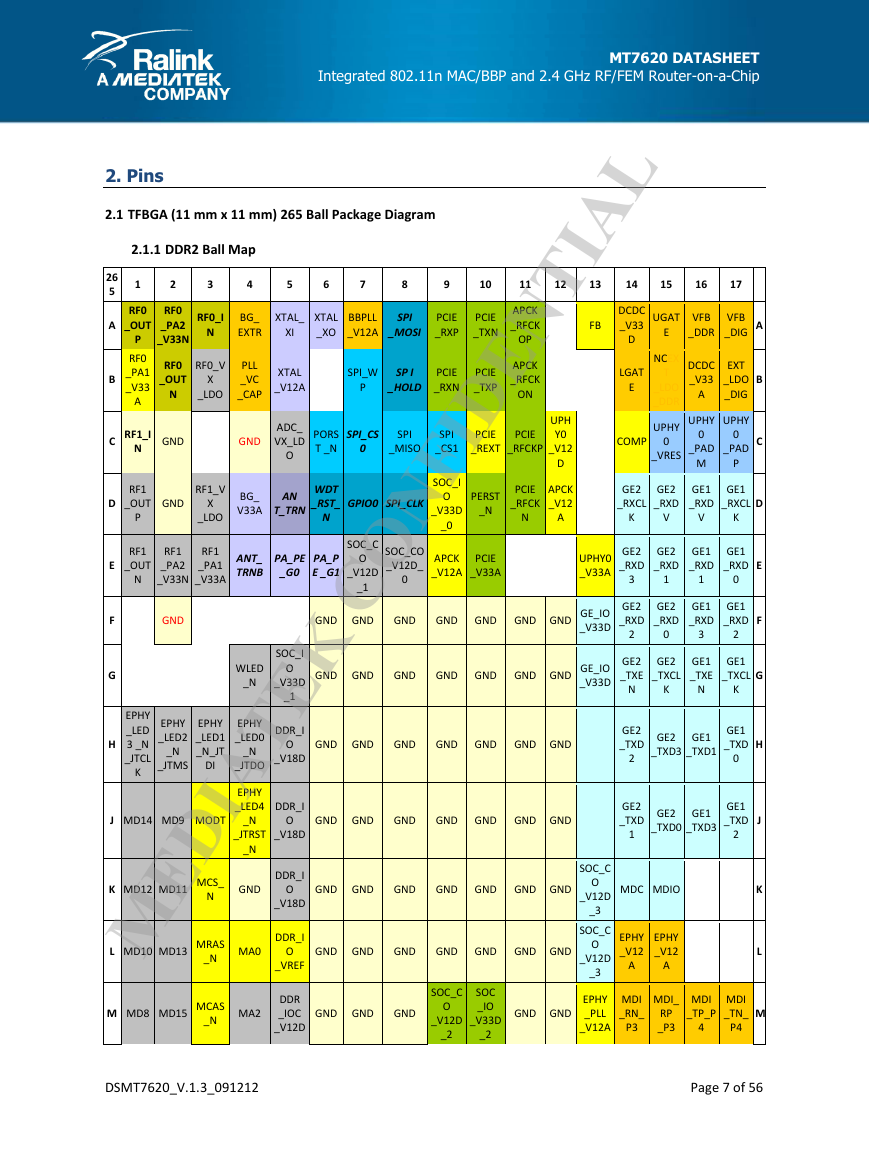

2.1 TFBGA (11 MM X 11 MM) 265 BALL PACKAGE DIAGRAM

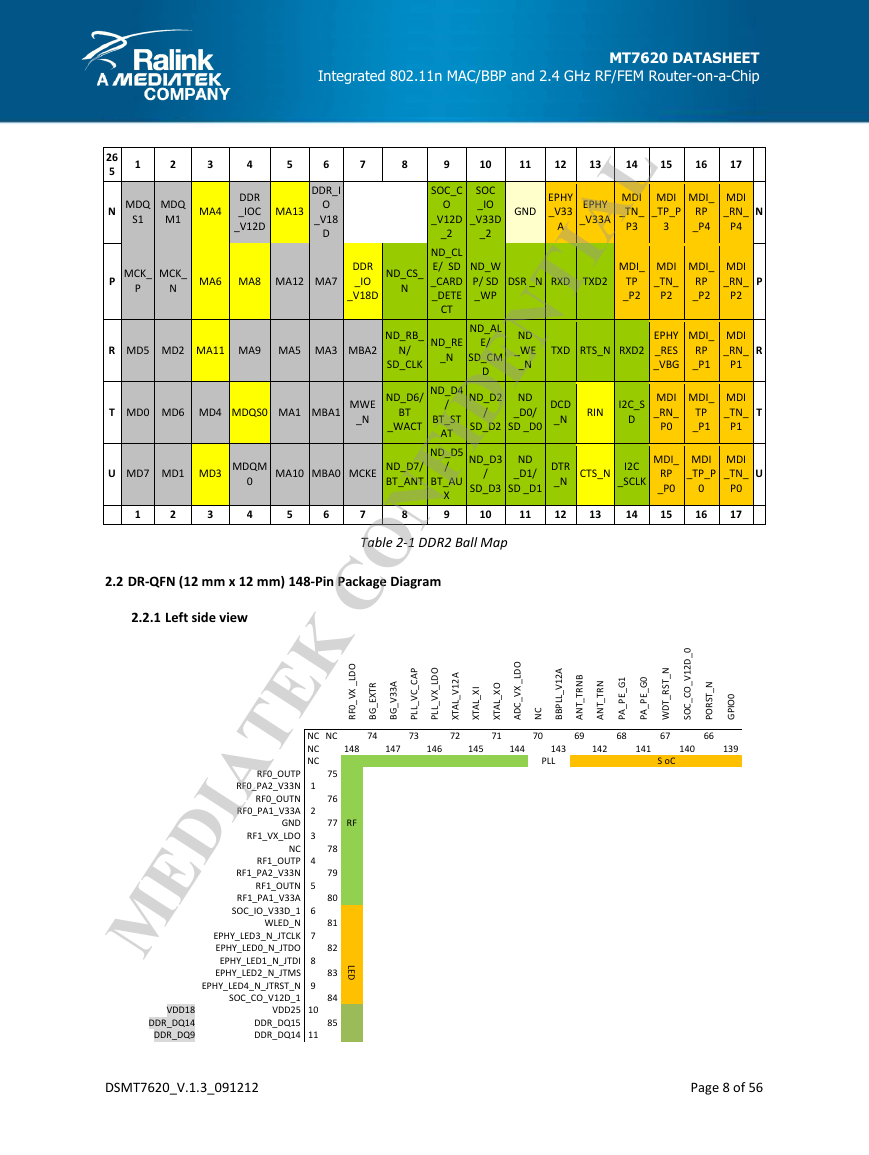

2.1.1 DDR2 BALL MAP

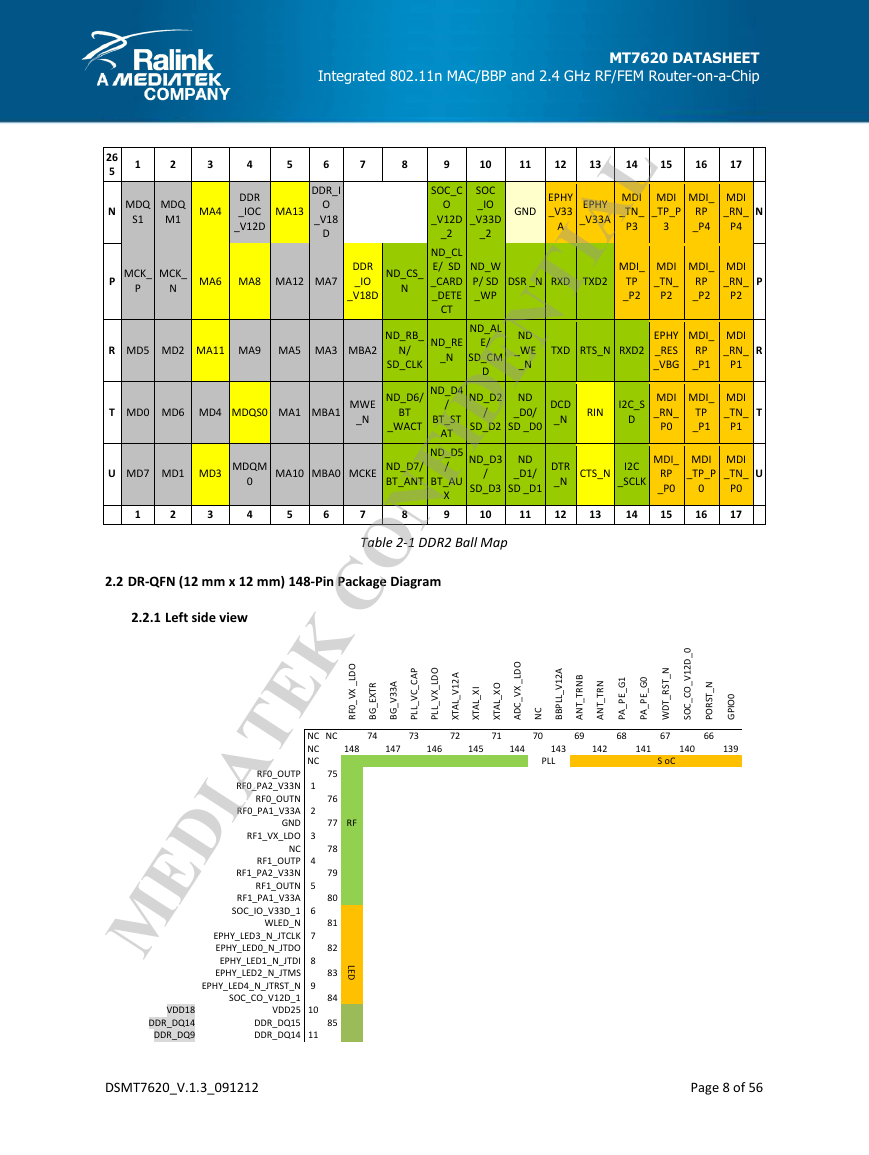

2.2 DR-QFN (12 MM X 12 MM) 148-PIN PACKAGE DIAGRAM

2.2.1 LEFT SIDE VIEW

2.2.2 RIGHT SIDE VIEW

2.3 PIN DESCRIPTIONS (TFBGA)

2.4 PIN DESCRIPTIONS (DRQFN)

2.5 PIN SHARING SCHEMES

MEDIATEK CONFIDENTIAL

3.10.1 SDRAM INTERFACE

3.10.2 DDR2 SDRAM INTERFACE

3.10.3 RGMII INTERFACE

3.10.4 MII INTERFACE (25 MHZ)

3.10.5 RVMII INTERFACE (PHY MODE MII TIMING) (25 MHZ)

3.10.6 SPI INTERFACE

3.10.7 I2S INTERFACE

3.10.8 PCM INTERFACE

3.10.9 POWER ON SEQUENCE

3.3 ABSOLUTE MAXIMUM RATINGS

3.4 MAXIMUM TEMPERATURES

3.5 OPERATING CONDITIONS

3.6 THERMAL CHARACTERISTICS

3.7 STORAGE CONDITIONS

3.8 EXTERNAL XTAL SPECFICATION

3.9 DC ELECTRICAL CHARACTERISTICS

3.10 AC ELECTRICAL CHARACTERISTICS

3.11 PACKAGE PHYSICAL DIMENSIONS

3.11.1 TFBGA (11 MM X 11 MM) 265 BALLS

3.11.2 DR-QFN (12 MM X 12 MM) 148LD

3.11.3 MT7620 N/A MARKING

3.11.4 REFLOW PROFILE GUIDELINE

2.6 BOOTSTRAPPING PINS DESCRIPTION

3. MAXIMUM RATINGS AND OPERATING CONDITIONS

4. ABBREVIATIONS

5. REVISION HISTORY

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

Table of Figures

FIGURE 2-1 DR-QFN PIN DIAGRAM (LEFT VIEW) .............................................................................................................. 9

FIGURE 2-2 DR-QFN PIN DIAGRAM (RIGHT SIDE VIEW) ................................................................................................... 10

FIGURE 2-3 MII MII PHY ..................................................................................................................................... 30

FIGURE 2-4 RVMII MII MAC ................................................................................................................................ 30

FIGURE 2-5 RGMII RGMII PHY ............................................................................................................................. 30

FIGURE 2-6 RGMII RGMII MAC ........................................................................................................................... 30

FIGURE 3-1 SDRAM INTERFACE .................................................................................................................................. 35

FIGURE 3-2 DDR2 SDRAM COMMAND ....................................................................................................................... 36

FIGURE 3-3 DDR2 SDRAM WRITE DATA ...................................................................................................................... 36

FIGURE 3-4 DDR2 SDRAM READ DATA ....................................................................................................................... 36

FIGURE 3-5 RGMII INTERFACE .................................................................................................................................... 38

FIGURE 3-6 MII INTERFACE ......................................................................................................................................... 39

FIGURE 3-7 RVMII INTERFACE ..................................................................................................................................... 40

FIGURE 3-8 SPI INTERFACE ......................................................................................................................................... 41

FIGURE 3-9 I2S INTERFACE ......................................................................................................................................... 42

FIGURE 3-10 PCM INTERFACE ..................................................................................................................................... 43

FIGURE 3-11 POWER ON SEQUENCE ............................................................................................................................ 44

FIGURE 3-12 TFBGA TOP VIEW .................................................................................................................................. 45

FIGURE 3-13 TFBGA SIDE VIEW .................................................................................................................................. 45

FIGURE 3-14 TFBGA “A” EXPANDED ........................................................................................................................... 45

FIGURE 3-15 TFBGA BOTTOM VIEW ............................................................................................................................ 46

FIGURE 3-16 TFBGA “B” EXPANDED ........................................................................................................................... 46

FIGURE 3-17 DR-QFN TOP VIEW ................................................................................................................................ 47

FIGURE 3-18 DR-QFN SIDE VIEW ............................................................................................................................... 47

FIGURE 3-19 DR-QFN “B” EXPANDED ......................................................................................................................... 47

FIGURE 3-20 DR-QFN BOTTOM VIEW ......................................................................................................................... 48

FIGURE 3-21 DR-QFN “A” EXPANDED ......................................................................................................................... 48

FIGURE 3-22 MT7620N TOP MARKING ........................................................................................................................ 50

FIGURE 3-23 MT7620A TOP MARKING ........................................................................................................................ 50

FIGURE 3-24 REFLOW PROFILE FOR MT7620 ................................................................................................................ 51

MEDIATEK CONFIDENTIAL

List of Tables

TABLE 1-1 MAIN FEATURES ........................................................................................................................................... 6

TABLE 2-1 DDR2 BALL MAP ......................................................................................................................................... 8

TABLE 3-1 ABSOLUTE MAXIMUM RATINGS .................................................................................................................... 32

TABLE 3-2 MAXIMUM TEMPERATURES .......................................................................................................................... 32

TABLE 3-3 OPERATING CONDITIONS ............................................................................................................................. 32

TABLE 3-4 THERMAL CHARACTERISTICS ......................................................................................................................... 32

TABLE 3-5 EXTERNAL XTAL SPECIFICATIONS .................................................................................................................... 33

TABLE 3-6 DC ELECTRICAL CHARACTERISTICS .................................................................................................................. 33

TABLE 3-7 VDD 2.5V ELECTRICAL CHARACTERISTICS ........................................................................................................ 34

TABLE 3-8 VDD 3.3V ELECTRICAL CHARACTERISTICS ........................................................................................................ 34

TABLE 3-9 SDRAM INTERFACE DIAGRAM KEY ................................................................................................................ 35

TABLE 3-10 DDR2 SDRAM INTERFACE DIAGRAM KEY .................................................................................................... 37

TABLE 3-11 RGMII INTERFACE DIAGRAM KEY ................................................................................................................ 38

TABLE 3-12 MII INTERFACE DIAGRAM KEY .................................................................................................................... 39

TABLE 3-13 RVMII INTERFACE DIAGRAM KEY ................................................................................................................ 40

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

Page 4 of 56

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

TABLE 3-14 SPI INTERFACE DIAGRAM KEY ..................................................................................................................... 41

TABLE 3-15 I2S INTERFACE DIAGRAM KEY ..................................................................................................................... 42

TABLE 3-16 PCM INTERFACE DIAGRAM KEY .................................................................................................................. 43

TABLE 3-17 POWER ON SEQUENCE DIAGRAM KEY .......................................................................................................... 44

MEDIATEK CONFIDENTIAL

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

Page 5 of 56

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

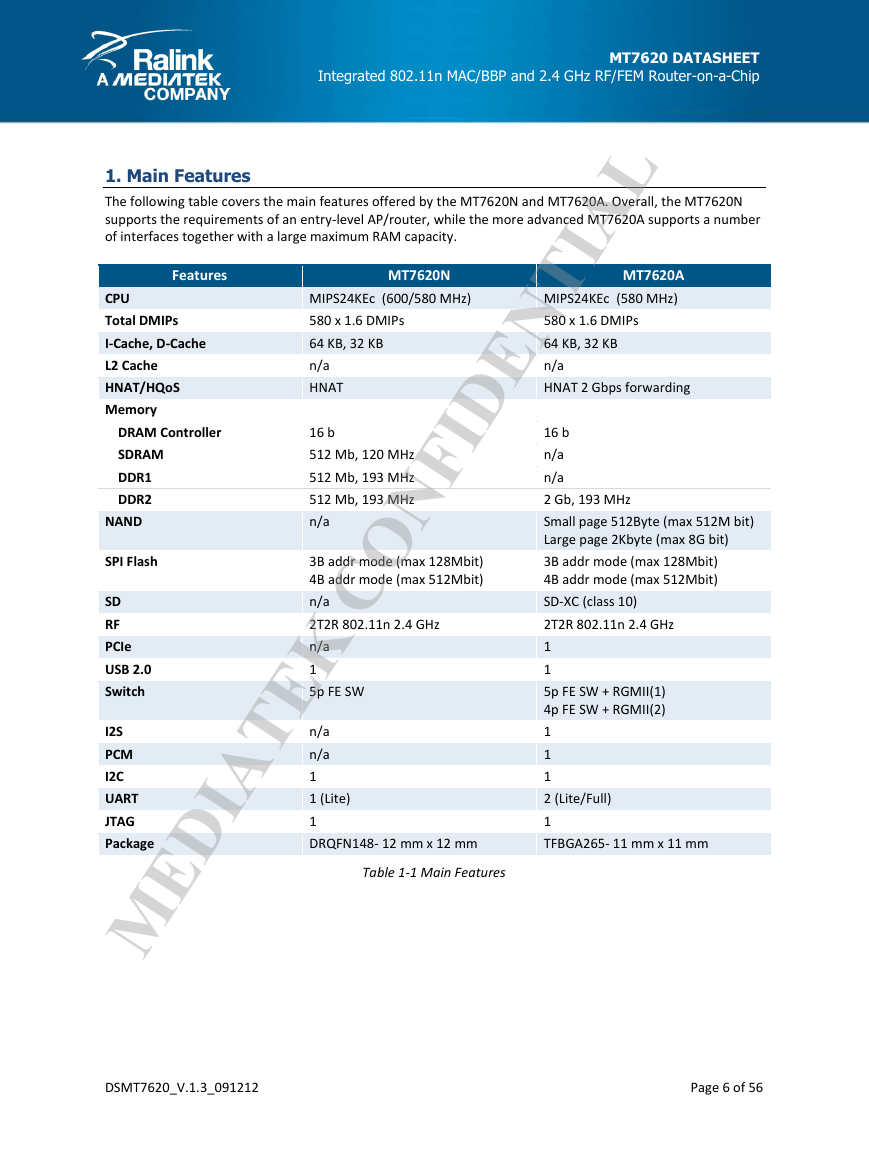

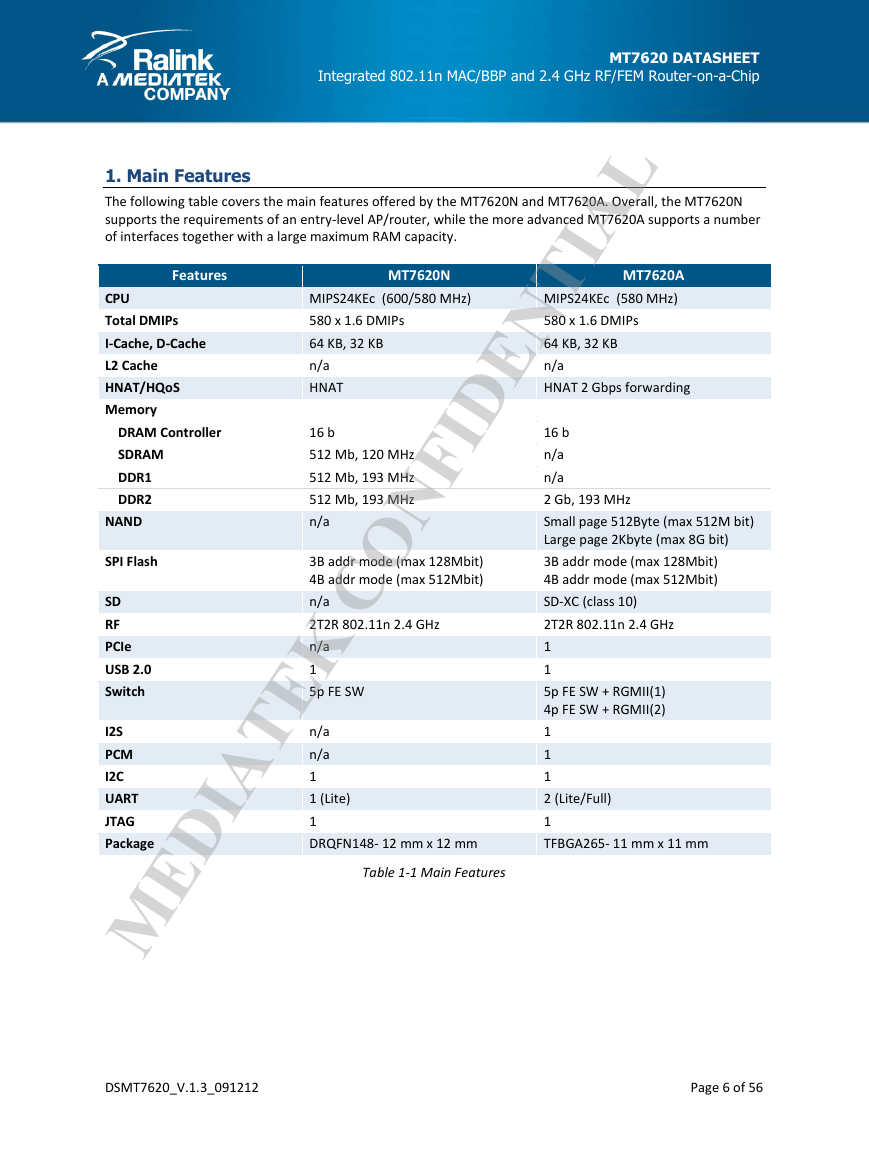

The following table covers the main features offered by the MT7620N and MT7620A. Overall, the MT7620N

supports the requirements of an entry-level AP/router, while the more advanced MT7620A supports a number

of interfaces together with a large maximum RAM capacity.

64 KB, 32 KB

Features

MT7620N

NAND

SPI Flash

n/a

DRAM Controller

SDRAM

DDR1

DDR2

n/a

HNAT

16 b

512 Mb, 193 MHz

512 Mb, 193 MHz

16 b

n/a

n/a

512 Mb, 120 MHz

1. Main Features

MIPS24KEc (600/580 MHz)

580 x 1.6 DMIPs

CPU

Total DMIPs

I-Cache, D-Cache

L2 Cache

HNAT/HQoS

Memory

MEDIATEK CONFIDENTIAL

I2S

PCM

I2C

UART

JTAG

Package

3B addr mode (max 128Mbit)

4B addr mode (max 512Mbit)

SD

RF

PCIe

USB 2.0

Switch

DRQFN148- 12 mm x 12 mm

Table 1-1 Main Features

2T2R 802.11n 2.4 GHz

1

1

1

1

1

1

n/a

n/a

1

n/a

n/a

1

1

2 Gb, 193 MHz

1 (Lite)

2 (Lite/Full)

5p FE SW

n/a

MT7620A

MIPS24KEc (580 MHz)

580 x 1.6 DMIPs

64 KB, 32 KB

HNAT 2 Gbps forwarding

Small page 512Byte (max 512M bit)

Large page 2Kbyte (max 8G bit)

3B addr mode (max 128Mbit)

4B addr mode (max 512Mbit)

SD-XC (class 10)

2T2R 802.11n 2.4 GHz

5p FE SW + RGMII(1)

4p FE SW + RGMII(2)

TFBGA265- 11 mm x 11 mm

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

Page 6 of 56

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

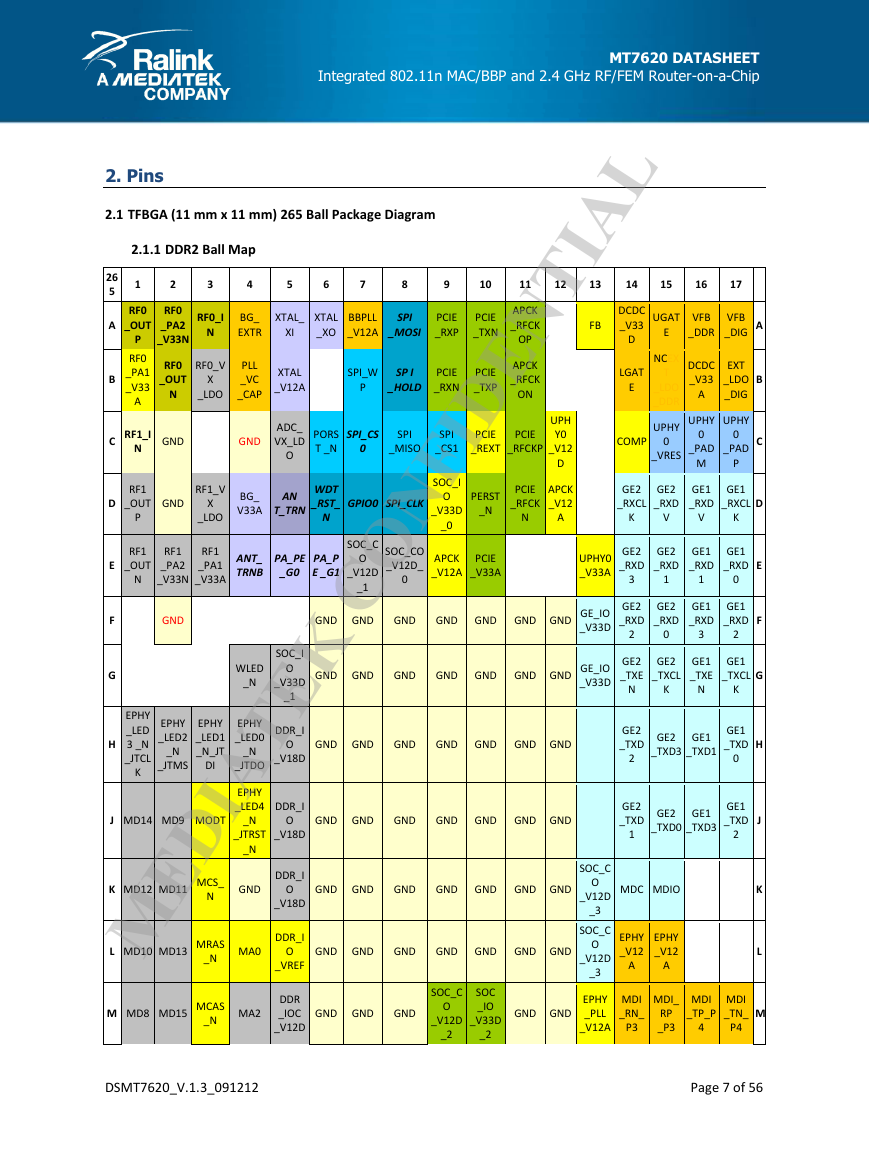

2. Pins

A

C

RF1_I

N

O

2.1 TFBGA (11 mm x 11 mm) 265 Ball Package Diagram

26

5

A

B

D

E

F

G

H

N

D

SOC_I

14

D

GND

GND

RF1_V

_LDO

GND

X

LGAT

E

8

9

10

N

_LDO

1

2

3

4

SPI

_CS1

5

6

7

RF0_V

X

PCIE

_TXP

PORS

T _N

RF0_I

N

RF0

_OUT

BG_

V33A

AN

T_TRN

BG_

EXTR

XTAL_

XI

PCIE

_RXN

0

_MISO

RF0

_OUT

P

RF1

_OUT

P

PCIE

_RFCKP

PCIE

_RXP

PCIE

_TXN

P

_HOLD

SPI

_MOSI

WDT

_RST_

DCDC

_V33

SPI_CS

SPI

ADC_

VX_LD

11

12

13

SPI_W

SP I

PCIE

_REXT

XTAL

_V12A

GPIO0 SPI_CLK

XTAL

_XO

BBPLL

_V12A

UPH

Y0

_V12

RF0

_PA1

_V33

PLL

_VC

_CAP

APCK

_RFCK

OP

APCK

_RFCK

ON

RF0

_PA2

_V33N

2.1.1 DDR2 Ball Map

MEDIATEK CONFIDENTIAL

EPHY

_LED

3 _N

_JTCL

RF1

_PA2

_V33N

RF1

_PA1

_V33A

EPHY

_LED1

_N_JT

APCK

_V12A

PCIE

_V33A

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

GND GND

SOC_CO

_V12D_

GE2

_TXE

N

_JTMS

DI

_JTDO

PCIE

_RFCK

APCK

_V12

GND GND

GND

GND GND

GND

GND GND

GND

GND GND

GND

GND GND

GND

GND GND

GND

UPHY0

_V33A

GE_IO

_V33D

GE_IO

_V33D

_JTRST

_V18D

ANT_

TRNB

PA_PE

_G0

PA_P

E _G1

EPHY

_LED4

EPHY

_LED2

EPHY

_LED0

GE2

_TXD

1

GE2

_TXD

2

GE2

_RXD

3

RF1

_OUT

N

GE2

_RXD

2

GE2

_RXCL

_V33D

_N

_V12D

_3

SOC_C

MRAS

_N

_V12D

_1

_N

_V33D

MCS_

N

WLED

O

DDR_I

O

O

PERST

DDR_I

O

_V18D

SOC_C

O

MA0

O

SOC_C

O

GND

O

N

A

_V18D

DDR_I

_N

_N

SOC_I

_1

K

GND

_N

COMP

K

_0

0

K MD12 MD11

L MD10 MD13

J MD14 MD9 MODT

_N

FB

15

16

17

UGAT

E

VFB

_DDR

VFB

_DIG

A

NCEX

T

_LDO

_DDR

UPHY

0

_VRES

DCDC

_V33

A

EXT

_LDO

_DIG

B

UPHY

UPHY

0

0

_PAD

M

_PAD

P

C

GE2

_RXD

GE1

_RXD

GE1

_RXCL

D

V

V

K

GE2

_RXD

GE1

_RXD

GE1

_RXD

E

1

1

0

GE2

_RXD

GE1

_RXD

GE1

_RXD

F

0

3

2

GE2

_TXCL

K

GE1

_TXE

N

GE1

_TXCL

G

K

GE2

_TXD3

GE1

_TXD1

GE1

_TXD

0

H

GE2

_TXD0

GE1

_TXD3

GE1

_TXD

2

J

DDR_I

_VREF

MDC MDIO

EPHY

_V12

A

EPHY

_V12

A

_V12D

O

_3

K

L

M MD8 MD15

MCAS

_N

MA2

DDR

_IOC

_V12D

GND GND

GND

SOC_C

O

_V12D

_2

SOC

_IO

_V33D

_2

GND GND

EPHY

_PLL

_V12A

MDI

_RN_

P3

MDI_

RP

_P3

MDI

_TP_P

4

MDI

_TN_

P4

M

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

Page 7 of 56

�

MT7620 DATASHEET

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

15

16

17

MDI

_TP_P

3

MDI_

RP

_P4

MDI

_RN_

P4

N

MDI

_TN_

P2

MDI_

RP

_P2

MDI

_RN_

P2

EPHY

_RES

_VBG

MDI_

RP

_P1

MDI

_RN_

P1

MDI

_RN_

P0

MDI_

TP

_P1

MDI

_TN_

P1

P

R

T

MDI_

RP

_P0

MDI

_TP_P

0

MDI

_TN_

P0

U

15

16

17

0

G

_

E

P

_

A

P

141

0

_

D

2

1

V

_

O

C

_

C

O

S

N

_

T

S

R

_

T

D

W

N

_

T

S

R

O

P

0

O

P

G

I

67

66

140

S oC

139

Page 8 of 56

D

U MD7 MD1 MD3

26

5

N

P

R MD5 MD2 MA11 MA9 MA5 MA3 MBA2

N/

T MD0 MD6 MD4 MDQS0 MA1 MBA1

RIN

14

0

4

3

CT

ND_AL

DDR_I

SOC_C

GND

A

8

10

MDQM

_V18D

N

ND_D2

SD_D2

MA4

MA13

CTS_N

I2C

_SCLK

ND_D5

BT_AU

ND_D3

/

SD_D3

ND_D4

/

7

8

3

4

BT

_WACT

5

6

7

ND_CS_

5

6

9

O

D

/

1

2

1

2

P

N

10

11

_2

_2

SD_CLK

I2C_S

D

ND_RB_

12

13

MWE

_N

ND_D6/

ND_RE

E/

/

X

9

_N

SD_CM

DTR

_N

SOC

_IO

DDR

_IO

DCD

_N

MCK_

MCK_

O

_V18

_V12D

_V33D

MDQ

M1

MDQ

S1

EPHY

_V33

BT_ST

AT

EPHY

_V33A

ND

_WE

_N

MDI

_TN_

P3

MDI_

TP

_P2

ND_D7/

BT_ANT

TXD RTS_N RXD2

DSR _N RXD TXD2

MA10 MBA0 MCKE

ND_W

P/ SD

_WP

DDR

_IOC

_V12D

ND

_D0/

SD _D0

ND

_D1/

SD _D1

MA6 MA8 MA12 MA7

ND_CL

E/ SD

_CARD

_DETE

MEDIATEK CONFIDENTIAL

NC NC

NC 148

NC

75

RF0_PA2_V33N 1

76

RF0_PA1_V33A 2

RF1_VX_LDO 3

RF1_OUTP 4

RF1_OUTN 5

RF1_PA1_V33A

SOC_IO_V33D_1 6

EPHY_LED3_N_JTCLK 7

EPHY_LED0_N_JTDO

EPHY_LED1_N_JTDI 8

EPHY_LED2_N_JTMS

EPHY_LED4_N_JTRST_N 9

VDD25 10

VDD18

DDR_DQ15

DDR_DQ14

DDR_DQ9

DDR_DQ14 11

Table 2-1 DDR2 Ball Map

2.2.1 Left side view

80

78

79

L

83

E

D

81

82

84

85

SOC_CO_V12D_1

RF1_PA2_V33N

O

D

L

_

X

V

_

C

D

A

O

D

L

_

X

V

_

0

F

R

O

D

L

_

X

V

_

L

L

P

A

2

1

V

_

L

L

P

B

B

145

147

142

146

P

A

C

_

C

V

_

L

L

P

71

70

77 RF

A

2

1

V

_

L

A

T

X

74

73

72

69

68

RF0_OUTN

B

N

R

T

_

T

N

A

RF0_OUTP

1

G

_

E

P

_

A

P

11

12

13

14

143

PLL

GND

NC

N

R

T

_

T

N

A

A

3

3

V

_

G

B

144

I

X

_

L

A

T

X

O

X

_

L

A

T

X

R

T

X

E

_

G

B

C

N

WLED_N

2.2 DR-QFN (12 mm x 12 mm) 148-Pin Package Diagram

DSMT7620_V.1.3_091212

loginid=guanyu.liu@feixun.com.cn,time=2014-06-14 15:41:12,ip=222.65.124.250,doctitle=MT7620_Datasheet_20131216.pdf,company=Shanghai Feixun Communication Co.Ltd上海斐訊數據通信技術有限公司_RLT

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc