卷

第 19 期

.34 No.19

第 34

Vol

·工程应用技术与实现·

计 算 机 工 程

Computer Engineering

2008 年 10 月

October 2008

文章编号:1000—3428(2008)19—0244—04

文献标识码:A

中图分类号:TP391

一种 AHB2AHB 桥的设计与实现

李 根,唐志敏,章 军

(中国科学院计算技术研究所,北京 100083)

摘 要:介绍一种跨时钟域的 32 位 AHB 总线桥的设计与实现。通过采用状态机设计以及使用预防死锁与解除死锁相结合的方法解决死锁,

使得该桥支持读写 burst、读预取、总线抢占式仲裁等多种操作并且简化了设计。性能测试表明,该桥能极大提高复杂 SoC 系统的系统带

宽和时序性能。

关键词:AHB 总线;桥;跨时钟域

Design and Implementation of AHB2AHB Bridge

LI Gen, TANG Zhi-min, ZHANG Jun

(Institute of Computing Technology, Chinese Academy of Sciences, Beijing 100083)

【Abstract】This paper introduces the design and implementation of an AHB bus bridge of crossing clock domains. By adopting the state machine

design method and using the merging of prevent-deadlock and break-deadlock to deal with deadlock, the bridge can support read/write burst,

pre-fetch operation for reading, deprived bus arbiter etc operations and simplify the implementation. Performance test indicates that it can improve

the system bandwidth and timing performance greatly.

【Key words】AHB bus; bridge; crossing clock domains

1 概述

在采用 AMBA 总线体系结构的 SoC 系统中,随着集成

的 IP 数量不断增多、总线带宽需求的不断加大以及总线时序

性能不断恶化,一条 AHB 内部总线难以同时支持种类繁多的

各种功能。因此,需要引入多级总线结构。

ARM公司提出了多层AHB总线和互连矩阵结构,每层

AHB总线上主设备可以同时访问不同的从设备,大大提高了

系统带宽,但是,随着系统总线主设备的增多,其总线互连

矩阵结构将变得非常复杂[1-2]。利用一个AHB2APB桥将一条

AHB总线和一条APB总线连接起来组成的典型AMBA总线架

构[3],虽然能满足很多不同场合下的需要,但是对于高带宽

IP集成数量越来越多的系统,如拥有以太网、PCIe、USB、

Wi-Fi、DMA设备等,总线带宽将成为瓶颈。因此,便出现

了双高速AHB总线结构,2 条AHB总线上可分别有多个主设

备和从设备,总线之间以AHB2AHB桥相连接,如NXP半导

体推出的LPC2300 系列ARM7 微控制器,便采用了该 结构。

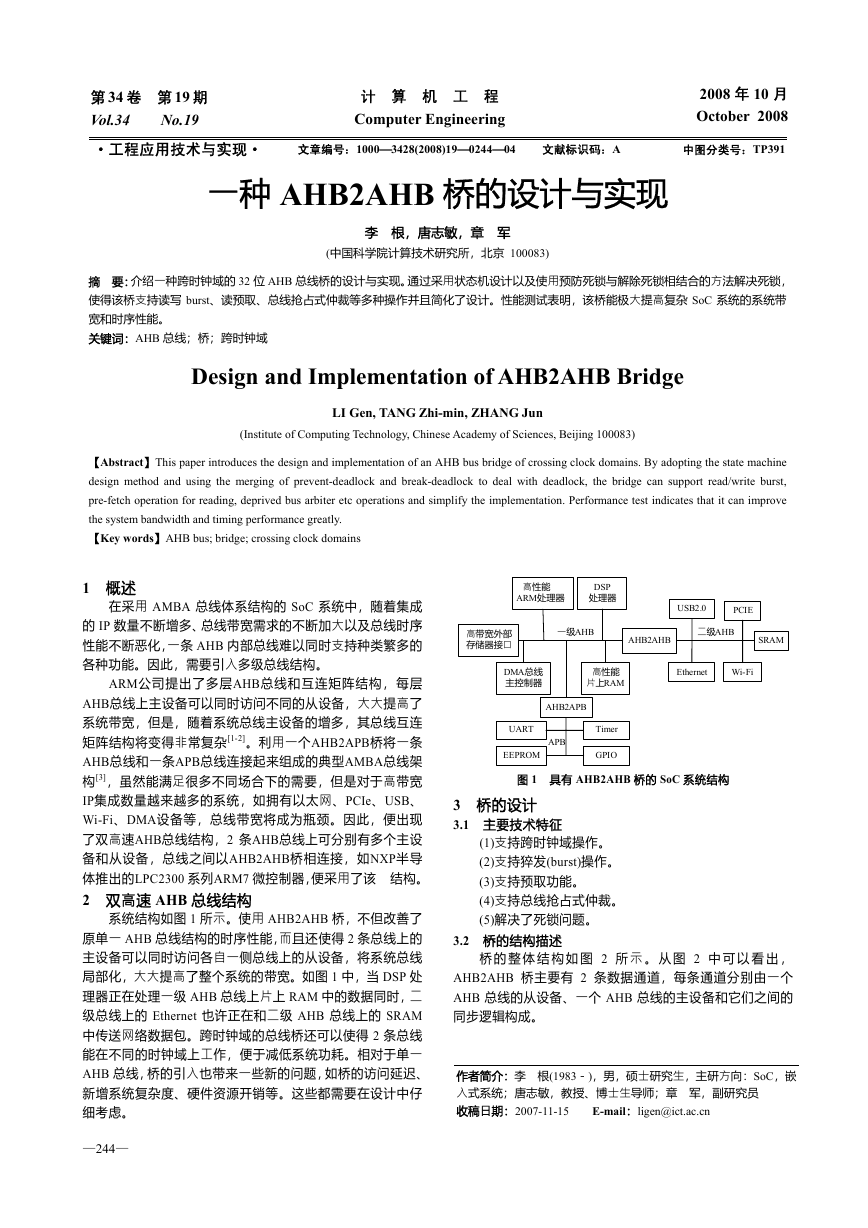

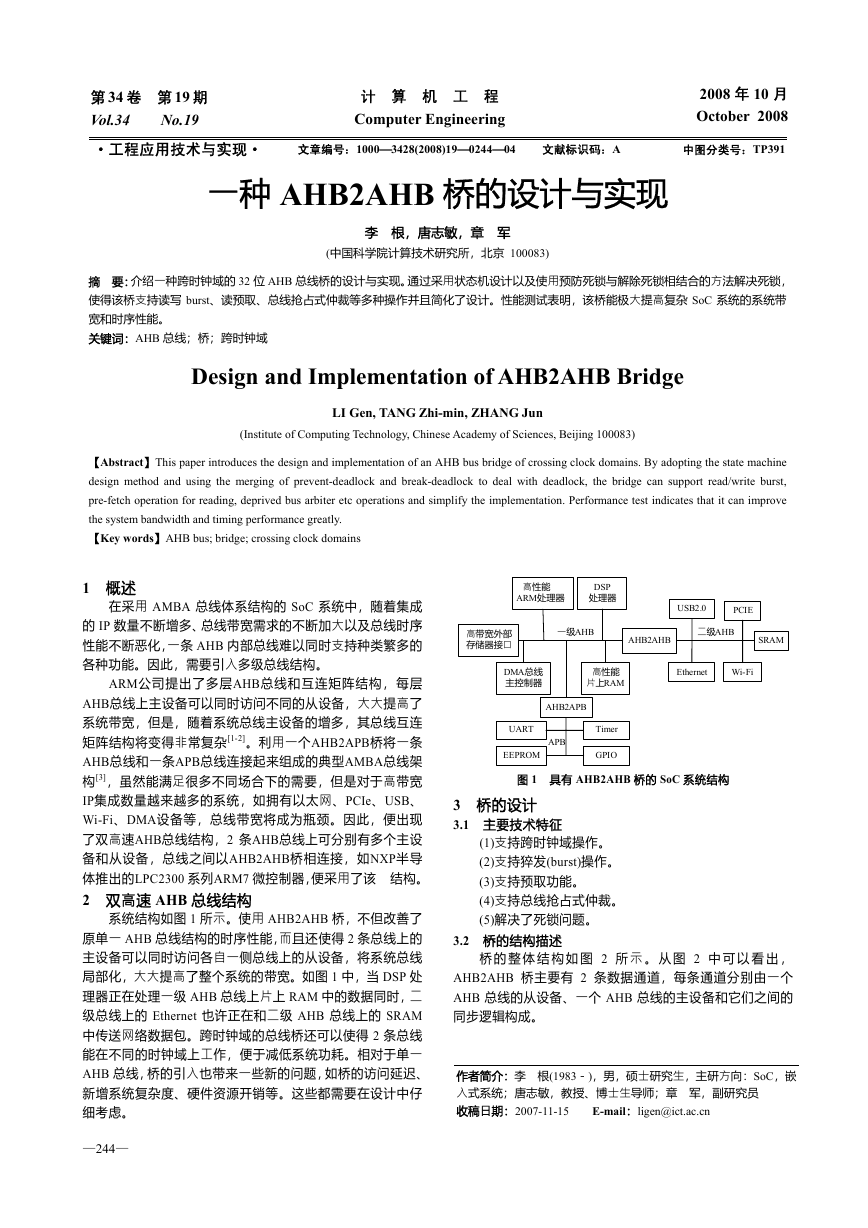

2 双高速 AHB 总线结构

系统结构如图 1 所示。使用 AHB2AHB 桥,不但改善了

原单一 AHB 总线结构的时序性能,而且还使得 2 条总线上的

主设备可以同时访问各自一侧总线上的从设备,将系统总线

局部化,大大提高了整个系统的带宽。如图 1 中,当 DSP 处

理器正在处理一级 AHB 总线上片上 RAM 中的数据同时,二

级总线上的 Ethernet 也许正在和二级 AHB 总线上的 SRAM

中传送网络数据包。跨时钟域的总线桥还可以使得 2 条总线

能在不同的时钟域上工作,便于减低系统功耗。相对于单一

AHB 总线,桥的引入也带来一些新的问题,如桥的访问延迟、

新增系统复杂度、硬件资源开销等。这些都需要在设计中仔

细考虑。

—244—

高性能

ARM处理器

DSP

处理器

USB2.0

PCIE

高带宽外部

存储器接口

一级AHB

AHB2AHB

二级AHB

SRAM

DMA总线

主控制器

高性能

片上RAM

AHB2APB

UART

EEPROM

APB

Timer

GPIO

Ethernet

Wi-Fi

图 1 具有 AHB2AHB 桥的 SoC 系统结构

3 桥的设计

3.1 主要技术特征

(1)支持跨时钟域操作。

(2)支持猝发(burst)操作。

(3)支持预取功能。

(4)支持总线抢占式仲裁。

(5)解决了死锁问题。

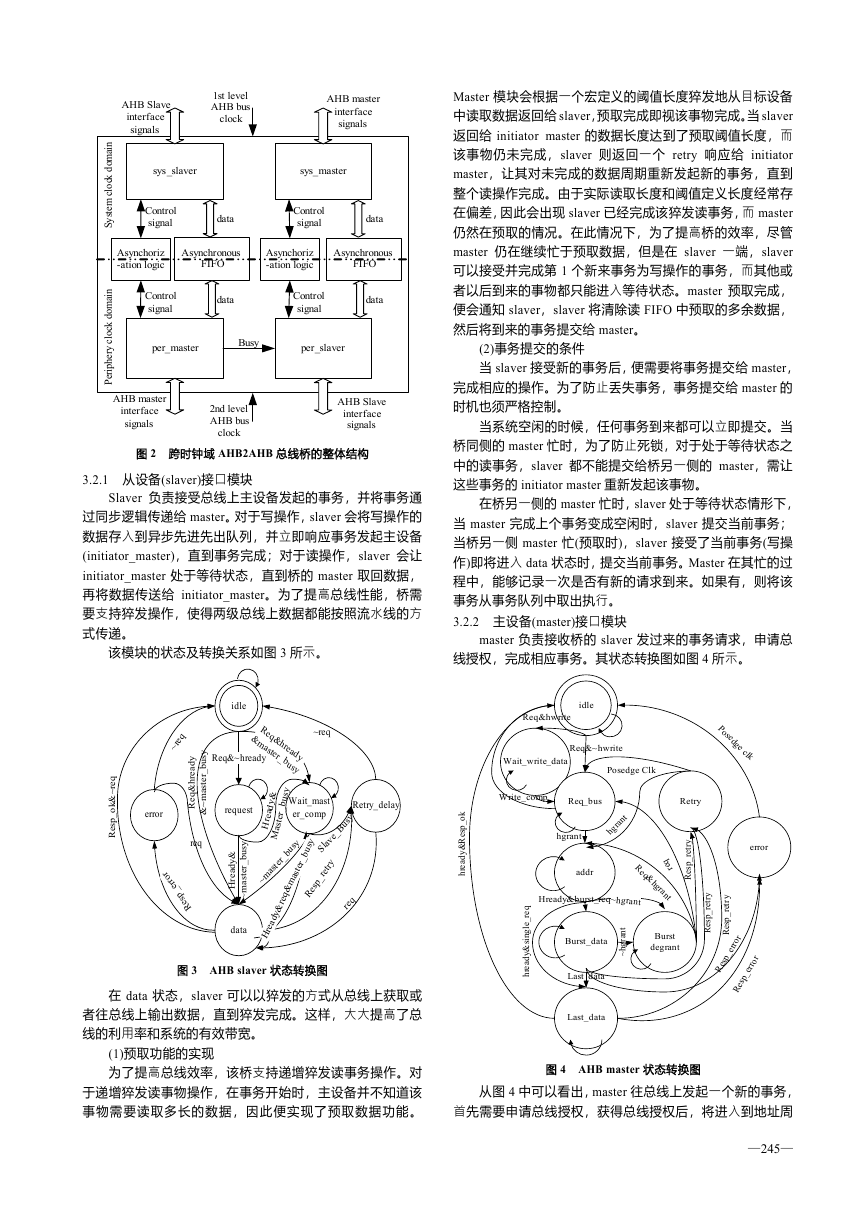

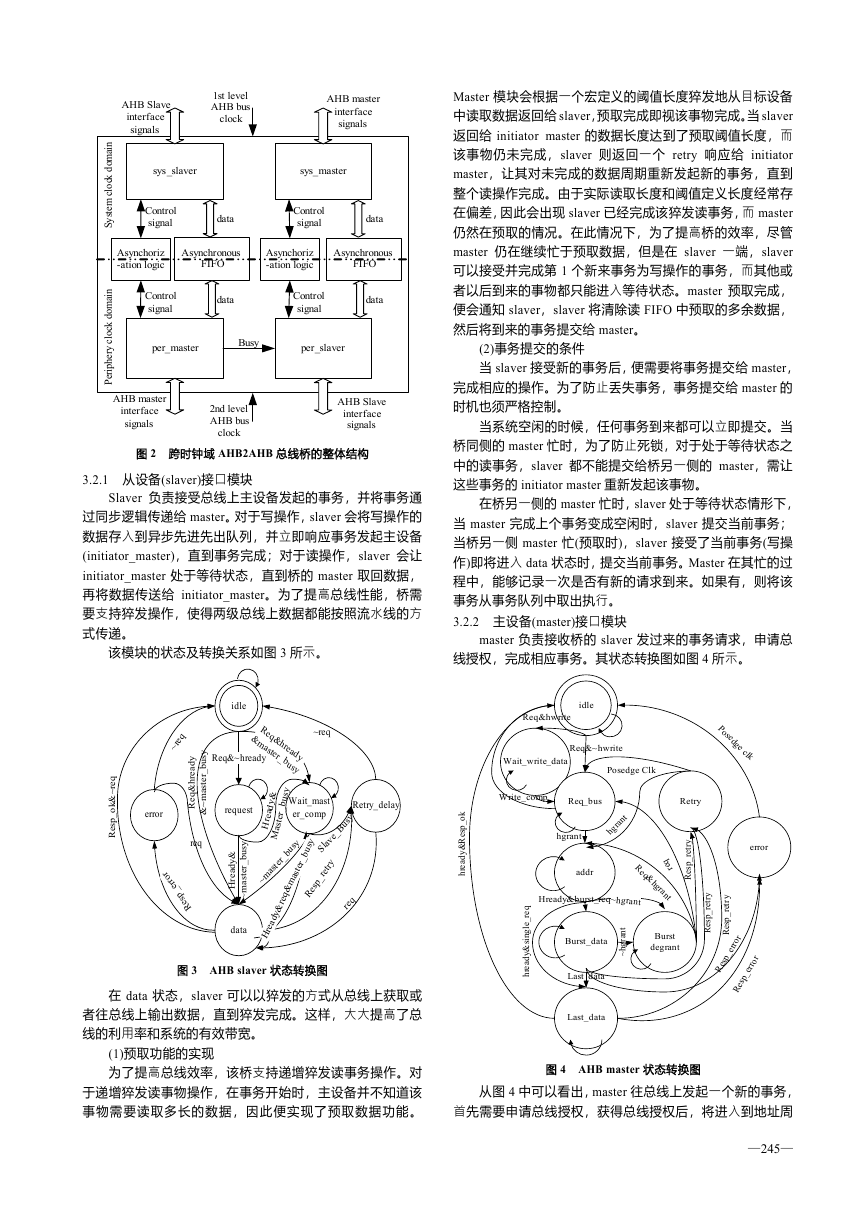

3.2 桥的结构描述

桥 的 整 体 结 构 如 图 2 所 示 。 从 图 2 中 可 以 看 出 ,

AHB2AHB 桥主要有 2 条数据通道,每条通道分别由一个

AHB 总线的从设备、一个 AHB 总线的主设备和它们之间的

同步逻辑构成。

作者简介:李 根(1983-),男,硕士研究生,主研方向:SoC,嵌

入式系统;唐志敏,教授、博士生导师;章 军,副研究员

收稿日期:2007-11-15 E-mail:ligen@ict.ac.cn

�

AHB Slave

interface

signals

1st level

AHB bus

clock

AHB master

interface

signals

sys_slaver

sys_master

Control

signal

data

Control

signal

data

Asynchoriz

-ation logic

Asynchronous

FIFO

Asynchoriz

-ation logic

Asynchronous

FIFO

Control

signal

data

Control

signal

data

per_master

Busy

per_slaver

n

i

a

m

o

d

k

c

o

l

c

m

e

t

s

y

S

n

i

a

m

o

d

k

c

o

l

c

y

r

e

h

p

i

r

e

P

AHB master

interface

signals

2nd level

AHB bus

clock

AHB Slave

interface

signals

图 2 跨时钟域 AHB2AHB 总线桥的整体结构

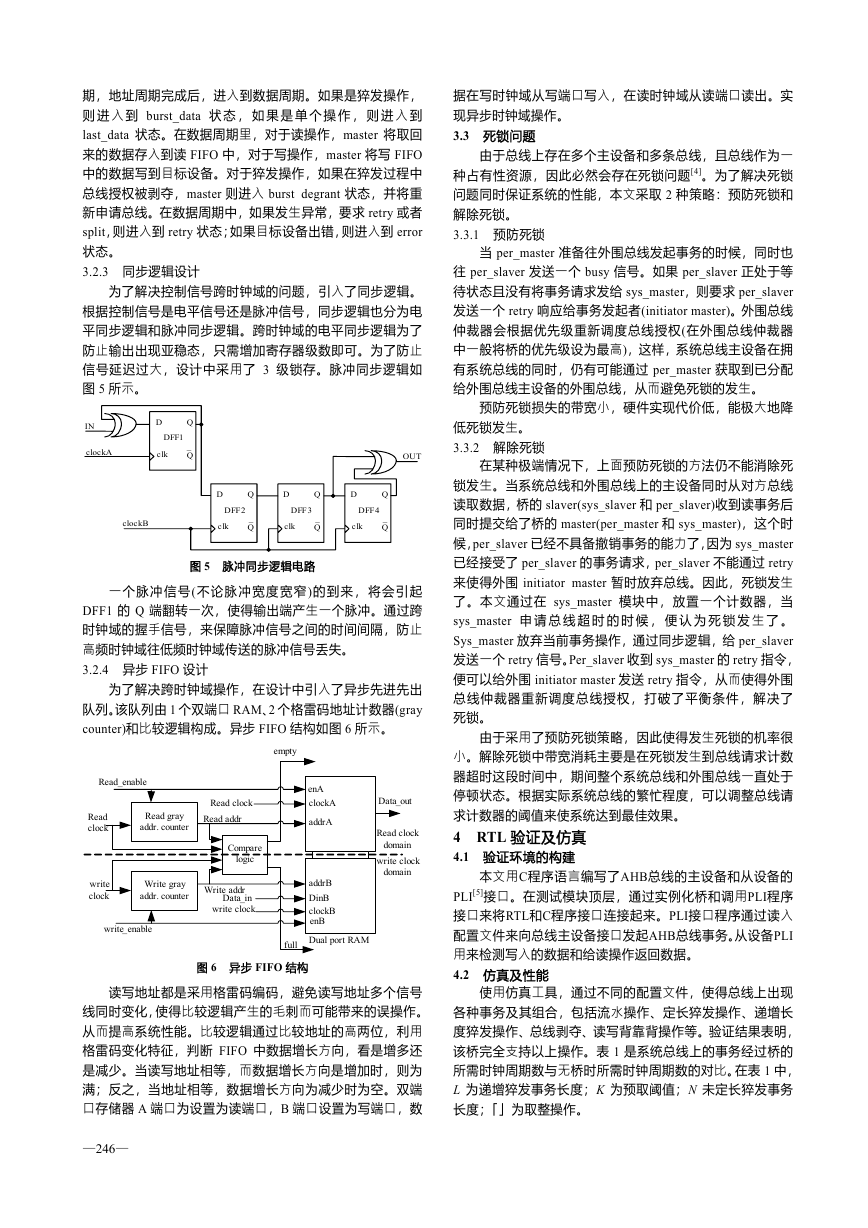

3.2.1 从设备(slaver)接口模块

Slaver 负责接受总线上主设备发起的事务,并将事务通

过同步逻辑传递给 master。对于写操作,slaver 会将写操作的

数据存入到异步先进先出队列,并立即响应事务发起主设备

(initiator_master),直到事务完成;对于读操作,slaver 会让

initiator_master 处于等待状态,直到桥的 master 取回数据,

再将数据传送给 initiator_master。为了提高总线性能,桥需

要支持猝发操作,使得两级总线上数据都能按照流水线的方

式传递。

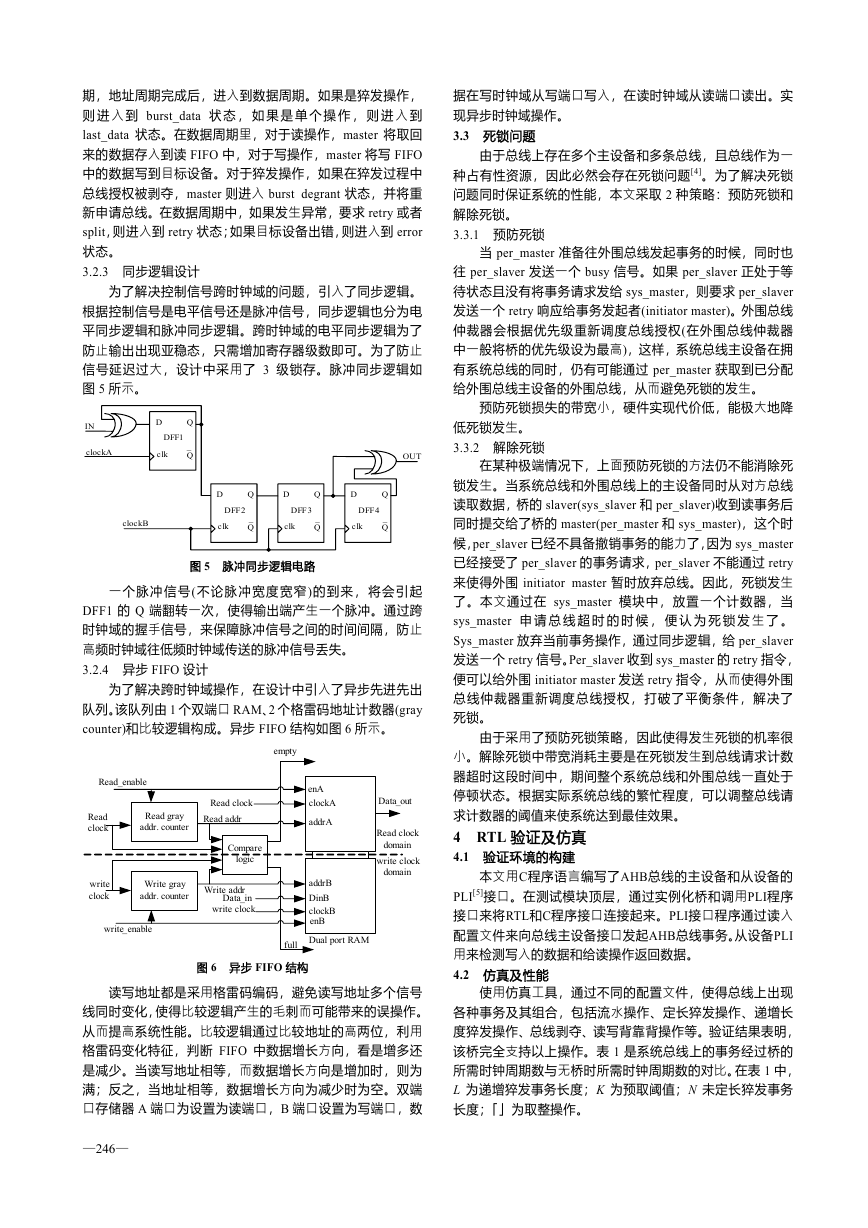

该模块的状态及转换关系如图 3 所示。

Master 模块会根据一个宏定义的阈值长度猝发地从目标设备

中读取数据返回给 slaver,预取完成即视该事物完成。当 slaver

返回给 initiator master 的数据长度达到了预取阈值长度,而

该事物仍未完成,slaver 则返回一个 retry 响应给 initiator

master,让其对未完成的数据周期重新发起新的事务,直到

整个读操作完成。由于实际读取长度和阈值定义长度经常存

在偏差,因此会出现 slaver 已经完成该猝发读事务,而 master

仍然在预取的情况。在此情况下,为了提高桥的效率,尽管

master 仍在继续忙于预取数据,但是在 slaver 一端,slaver

可以接受并完成第 1 个新来事务为写操作的事务,而其他或

者以后到来的事物都只能进入等待状态。master 预取完成,

便会通知 slaver,slaver 将清除读 FIFO 中预取的多余数据,

然后将到来的事务提交给 master。

(2)事务提交的条件

当 slaver 接受新的事务后,便需要将事务提交给 master,

完成相应的操作。为了防止丢失事务,事务提交给 master 的

时机也须严格控制。

当系统空闲的时候,任何事务到来都可以立即提交。当

桥同侧的 master 忙时,为了防止死锁,对于处于等待状态之

中的读事务,slaver 都不能提交给桥另一侧的 master,需让

这些事务的 initiator master 重新发起该事物。

在桥另一侧的 master 忙时,slaver 处于等待状态情形下,

当 master 完成上个事务变成空闲时,slaver 提交当前事务;

当桥另一侧 master 忙(预取时),slaver 接受了当前事务(写操

作)即将进入 data 状态时,提交当前事务。Master 在其忙的过

程中,能够记录一次是否有新的请求到来。如果有,则将该

事务从事务队列中取出执行。

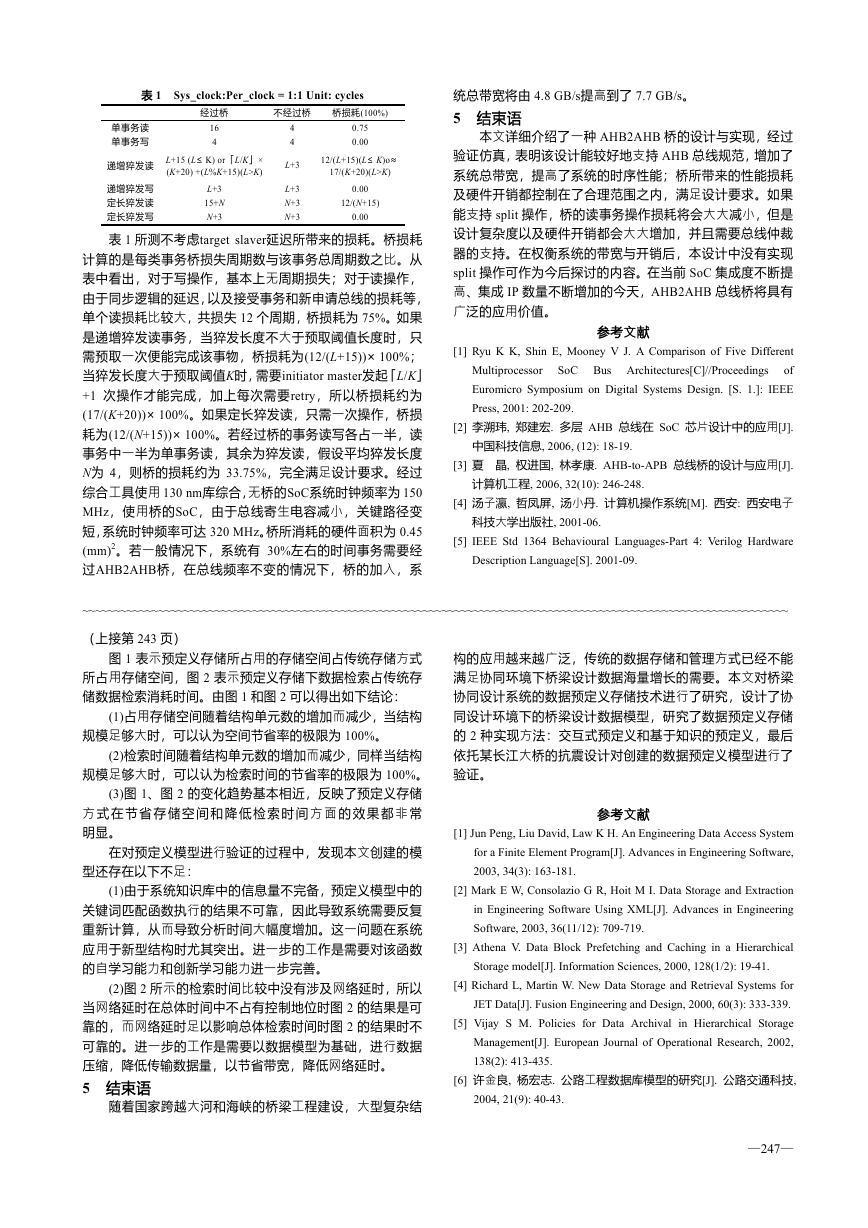

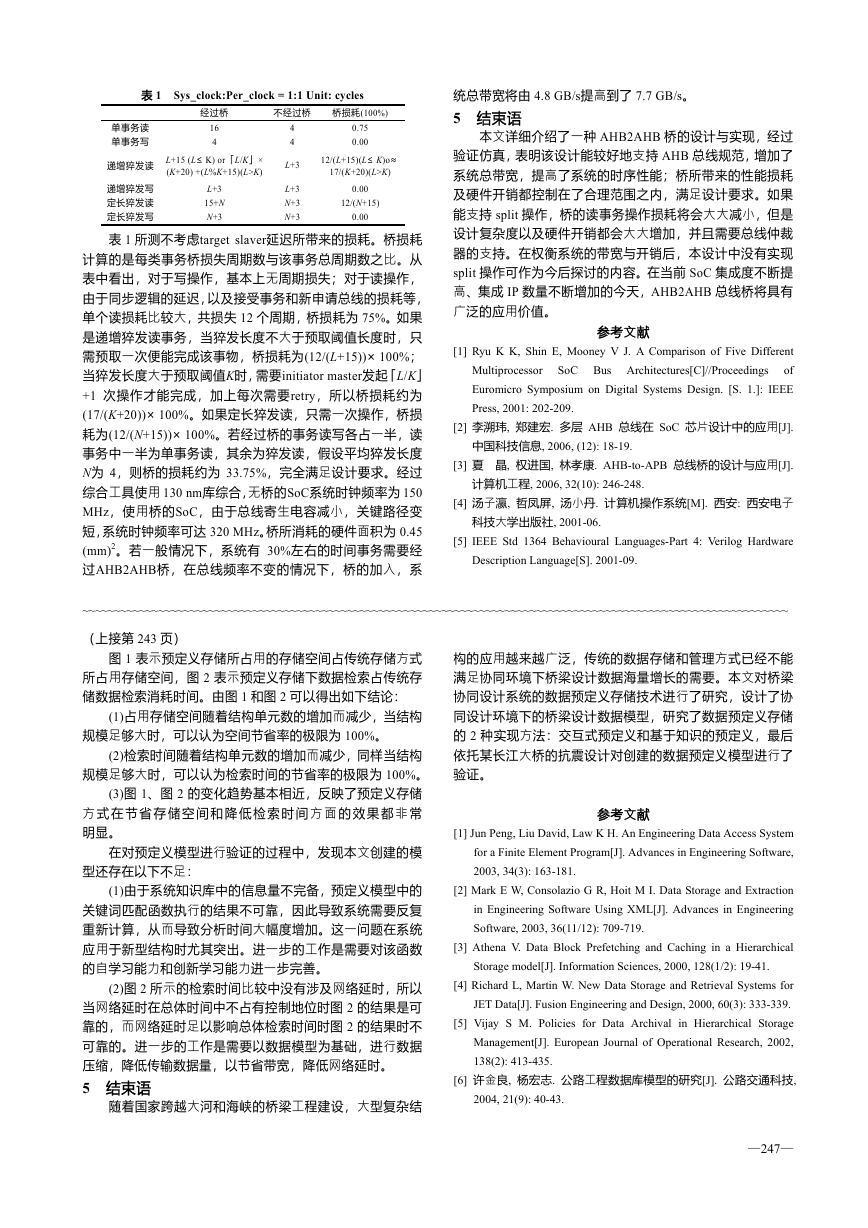

3.2.2 主设备(master)接口模块

master 负责接收桥的 slaver 发过来的事务请求,申请总

线授权,完成相应事务。其状态转换图如图 4 所示。

idle

&

Req&hready

master_busy

Req&~hready

~req

idle

Req&hwrite

Wait_write_data

Req&~hwrite

Posedge Clk

Retry_delay

Write_comp

Req_bus

k

o

_

p

s

e

R

&

y

d

a

e

r

h

hgrant

hgrant

addr

q

e

r

R

e

q

&

Wait_mast

er_comp

Slave_Busy

master_busy

~master_busy

Resp_retry

Hready&req&

req

q

e

r

_

e

l

g

n

i

s

&

y

d

a

e

r

h

Hready&burst_req

~hgrant

h

gra

nt

Burst_data

t

n

a

r

g

h

~

Burst

degrant

Last_data

Last_data

~req

y

d

a

e

r

h

&

q

e

R

y

s

u

b

_

r

e

t

s

a

m

~

&

req

q

e

r

~

&

k

o

_

p

s

e

R

error

r

o

rr

e

_

p

s

e

R

&

y

ad

re

H

y

us

b

_

ster

a

M

request

&

y

d

a

e

r

H

y

s

u

b

_

r

e

t

s

a

m

~

data

图 3 AHB slaver 状态转换图

在 data 状态,slaver 可以以猝发的方式从总线上获取或

者往总线上输出数据,直到猝发完成。这样,大大提高了总

线的利用率和系统的有效带宽。

(1)预取功能的实现

为了提高总线效率,该桥支持递增猝发读事务操作。对

于递增猝发读事物操作,在事务开始时,主设备并不知道该

事物需要读取多长的数据,因此便实现了预取数据功能。

P

o

se

d

g

e clk

Retry

y

r

t

e

r

_

p

s

e

R

error

y

r

t

e

r

_

p

s

e

R

y

r

t

e

r

_

p

s

e

R

Resp_error

Resp_error

图 4 AHB master 状态转换图

从图 4 中可以看出,master 往总线上发起一个新的事务,

首先需要申请总线授权,获得总线授权后,将进入到地址周

—245—

�

期,地址周期完成后,进入到数据周期。如果是猝发操作,

则 进 入 到 burst_data 状 态 , 如 果 是 单 个 操 作 , 则 进 入 到

last_data 状态。在数据周期里,对于读操作,master 将取回

来的数据存入到读 FIFO 中,对于写操作,master 将写 FIFO

中的数据写到目标设备。对于猝发操作,如果在猝发过程中

总线授权被剥夺,master 则进入 burst degrant 状态,并将重

新申请总线。在数据周期中,如果发生异常,要求 retry 或者

split,则进入到 retry 状态;如果目标设备出错,则进入到 error

状态。

3.2.3 同步逻辑设计

为了解决控制信号跨时钟域的问题,引入了同步逻辑。

根据控制信号是电平信号还是脉冲信号,同步逻辑也分为电

平同步逻辑和脉冲同步逻辑。跨时钟域的电平同步逻辑为了

防止输出出现亚稳态,只需增加寄存器级数即可。为了防止

信号延迟过大,设计中采用了 3 级锁存。脉冲同步逻辑如

图 5 所示。

IN

clockA

D

DFF1

clk

Q

_

Q

clockB

D

DFF2

clk

Q

_

Q

D

DFF3

clk

Q

_

Q

D

DFF4

clk

Q

_

Q

OUT

图 5 脉冲同步逻辑电路

一个脉冲信号(不论脉冲宽度宽窄)的到来,将会引起

DFF1 的 Q 端翻转一次,使得输出端产生一个脉冲。通过跨

时钟域的握手信号,来保障脉冲信号之间的时间间隔,防止

高频时钟域往低频时钟域传送的脉冲信号丢失。

3.2.4 异步 FIFO 设计

为了解决跨时钟域操作,在设计中引入了异步先进先出

队列。该队列由 1 个双端口 RAM、2 个格雷码地址计数器(gray

counter)和比较逻辑构成。异步 FIFO 结构如图 6 所示。

empty

Read_enable

Read

clock

Read gray

addr. counter

write

clock

Write gray

addr. counter

write_enable

Read clock

Read addr

Compare

logic

Write addr

Data_in

write clock

enA

clockA

addrA

addrB

DinB

clockB

enB

Data_out

Read clock

domain

write clock

domain

Dual port RAM

full

图 6 异步 FIFO 结构

读写地址都是采用格雷码编码,避免读写地址多个信号

线同时变化,使得比较逻辑产生的毛刺而可能带来的误操作。

从而提高系统性能。比较逻辑通过比较地址的高两位,利用

格雷码变化特征,判断 FIFO 中数据增长方向,看是增多还

是减少。当读写地址相等,而数据增长方向是增加时,则为

满;反之,当地址相等,数据增长方向为减少时为空。双端

口存储器 A 端口为设置为读端口,B 端口设置为写端口,数

—246—

据在写时钟域从写端口写入,在读时钟域从读端口读出。实

现异步时钟域操作。

3.3 死锁问题

由于总线上存在多个主设备和多条总线,且总线作为一

种占有性资源,因此必然会存在死锁问题[4]。为了解决死锁

问题同时保证系统的性能,本文采取 2 种策略:预防死锁和

解除死锁。

3.3.1 预防死锁

当 per_master 准备往外围总线发起事务的时候,同时也

往 per_slaver 发送一个 busy 信号。如果 per_slaver 正处于等

待状态且没有将事务请求发给 sys_master,则要求 per_slaver

发送一个 retry 响应给事务发起者(initiator master)。外围总线

仲裁器会根据优先级重新调度总线授权(在外围总线仲裁器

中一般将桥的优先级设为最高),这样,系统总线主设备在拥

有系统总线的同时,仍有可能通过 per_master 获取到已分配

给外围总线主设备的外围总线,从而避免死锁的发生。

预防死锁损失的带宽小,硬件实现代价低,能极大地降

低死锁发生。

3.3.2 解除死锁

在某种极端情况下,上面预防死锁的方法仍不能消除死

锁发生。当系统总线和外围总线上的主设备同时从对方总线

读取数据,桥的 slaver(sys_slaver 和 per_slaver)收到读事务后

同时提交给了桥的 master(per_master 和 sys_master),这个时

候,per_slaver 已经不具备撤销事务的能力了,因为 sys_master

已经接受了 per_slaver 的事务请求,per_slaver 不能通过 retry

来使得外围 initiator master 暂时放弃总线。因此,死锁发生

了。本文通过在 sys_master 模块中,放置一个计数器,当

sys_master 申 请 总 线 超 时 的 时 候 , 便 认 为 死 锁 发 生 了 。

Sys_master 放弃当前事务操作,通过同步逻辑,给 per_slaver

发送一个 retry 信号。Per_slaver 收到 sys_master 的 retry 指令,

便可以给外围 initiator master 发送 retry 指令,从而使得外围

总线仲裁器重新调度总线授权,打破了平衡条件,解决了

死锁。

由于采用了预防死锁策略,因此使得发生死锁的机率很

小。解除死锁中带宽消耗主要是在死锁发生到总线请求计数

器超时这段时间中,期间整个系统总线和外围总线一直处于

停顿状态。根据实际系统总线的繁忙程度,可以调整总线请

求计数器的阈值来使系统达到最佳效果。

4 RTL 验证及仿真

4.1 验证环境的构建

本文用C程序语言编写了AHB总线的主设备和从设备的

PLI[5]接口。在测试模块顶层,通过实例化桥和调用PLI程序

接口来将RTL和C程序接口连接起来。PLI接口程序通过读入

配置文件来向总线主设备接口发起AHB总线事务。从设备PLI

用来检测写入的数据和给读操作返回数据。

4.2 仿真及性能

使用仿真工具,通过不同的配置文件,使得总线上出现

各种事务及其组合,包括流水操作、定长猝发操作、递增长

度猝发操作、总线剥夺、读写背靠背操作等。验证结果表明,

该桥完全支持以上操作。表 1 是系统总线上的事务经过桥的

所需时钟周期数与无桥时所需时钟周期数的对比。在表 1 中,

L 为递增猝发事务长度;K 为预取阈值;N 未定长猝发事务

长度;「」为取整操作。

�

表 1 Sys_clock:Per_clock = 1:1 Unit: cycles

经过桥

不经过桥

桥损耗(100%)

单事务读

单事务写

递增猝发读 L+15 (L≤K) or「L/K」×

(K+20) +(L%K+15)(L>K)

16

4

4

4

L+3

0.75

0.00

12/(L+15)(L≤K)o≈

17/(K+20)(L>K)

统总带宽将由 4.8 GB/s提高到了 7.7 GB/s。

5 结束语

L+3

15+N

N+3

L+3

N+3

N+3

12/(N+15)

0.00

0.00

本文详细介绍了一种 AHB2AHB 桥的设计与实现,经过

验证仿真,表明该设计能较好地支持 AHB 总线规范,增加了

系统总带宽,提高了系统的时序性能;桥所带来的性能损耗

及硬件开销都控制在了合理范围之内,满足设计要求。如果

能支持 split 操作,桥的读事务操作损耗将会大大减小,但是

设计复杂度以及硬件开销都会大大增加,并且需要总线仲裁

器的支持。在权衡系统的带宽与开销后,本设计中没有实现

split 操作可作为今后探讨的内容。在当前 SoC 集成度不断提

高、集成 IP 数量不断增加的今天,AHB2AHB 总线桥将具有

广泛的应用价值。

递增猝发写

定长猝发读

定长猝发写

表 1 所测不考虑target slaver延迟所带来的损耗。桥损耗

计算的是每类事务桥损失周期数与该事务总周期数之比。从

表中看出,对于写操作,基本上无周期损失;对于读操作,

由于同步逻辑的延迟,以及接受事务和新申请总线的损耗等,

单个读损耗比较大,共损失 12 个周期,桥损耗为 75%。如果

是递增猝发读事务,当猝发长度不大于预取阈值长度时,只

需预取一次便能完成该事物,桥损耗为(12/(L+15))×100%;

当猝发长度大于预取阈值K时,需要initiator master发起「L/K」

+1 次操作才能完成,加上每次需要retry,所以桥损耗约为

(17/(K+20))×100%。如果定长猝发读,只需一次操作,桥损

耗为(12/(N+15))×100%。若经过桥的事务读写各占一半,读

事务中一半为单事务读,其余为猝发读,假设平均猝发长度

N为 4,则桥的损耗约为 33.75%,完全满足设计要求。经过

综合工具使用 130 nm库综合,无桥的SoC系统时钟频率为 150

MHz,使用桥的SoC,由于总线寄生电容减小,关键路径变

短,系统时钟频率可达 320 MHz。桥所消耗的硬件面积为 0.45

(mm)2。若一般情况下,系统有 30%左右的时间事务需要经

过AHB2AHB桥,在总线频率不变的情况下,桥的加入,系

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

[1] Ryu K K, Shin E, Mooney V J. A Comparison of Five Different

Multiprocessor SoC Bus Architectures[C]//Proceedings

of

Euromicro Symposium on Digital Systems Design. [S. 1.]: IEEE

Press, 2001: 202-209.

[2] 李溯玮, 郑建宏. 多层 AHB 总线在 SoC 芯片设计中的应用[J].

[3] 夏 晶, 权进国, 林孝康. AHB-to-APB 总线桥的设计与应用[J].

[4] 汤子瀛, 哲凤屏, 汤小丹. 计算机操作系统[M]. 西安: 西安电子

[5] IEEE Std 1364 Behavioural Languages-Part 4: Verilog Hardware

Description Language[S]. 2001-09.

参考文献

中国科技信息, 2006, (12): 18-19.

计算机工程, 2006, 32(10): 246-248.

科技大学出版社, 2001-06.

(上接第 243 页)

图 1 表示预定义存储所占用的存储空间占传统存储方式

所占用存储空间,图 2 表示预定义存储下数据检索占传统存

储数据检索消耗时间。由图 1 和图 2 可以得出如下结论:

(1)占用存储空间随着结构单元数的增加而减少,当结构

规模足够大时,可以认为空间节省率的极限为 100%。

(2)检索时间随着结构单元数的增加而减少,同样当结构

规模足够大时,可以认为检索时间的节省率的极限为 100%。

(3)图 1、图 2 的变化趋势基本相近,反映了预定义存储

方式在 节省 存 储空间 和降 低 检索时 间方 面 的效果 都非常

明显。

在对预定义模型进行验证的过程中,发现本文创建的模

型还存在以下不足:

(1)由于系统知识库中的信息量不完备,预定义模型中的

关键词匹配函数执行的结果不可靠,因此导致系统需要反复

重新计算,从而导致分析时间大幅度增加。这一问题在系统

应用于新型结构时尤其突出。进一步的工作是需要对该函数

的自学习能力和创新学习能力进一步完善。

(2)图 2 所示的检索时间比较中没有涉及网络延时,所以

当网络延时在总体时间中不占有控制地位时图 2 的结果是可

靠的,而网络延时足以影响总体检索时间时图 2 的结果时不

可靠的。进一步的工作是需要以数据模型为基础,进行数据

压缩,降低传输数据量,以节省带宽,降低网络延时。

5 结束语

随着国家跨越大河和海峡的桥梁工程建设,大型复杂结

构的应用越来越广泛,传统的数据存储和管理方式已经不能

满足协同环境下桥梁设计数据海量增长的需要。本文对桥梁

协同设计系统的数据预定义存储技术进行了研究,设计了协

同设计环境下的桥梁设计数据模型,研究了数据预定义存储

的 2 种实现方法:交互式预定义和基于知识的预定义,最后

依托某长江大桥的抗震设计对创建的数据预定义模型进行了

验证。

参考文献

[1] Jun Peng, Liu David, Law K H. An Engineering Data Access System

for a Finite Element Program[J]. Advances in Engineering Software,

2003, 34(3): 163-181.

[2] Mark E W, Consolazio G R, Hoit M I. Data Storage and Extraction

in Engineering Software Using XML[J]. Advances in Engineering

Software, 2003, 36(11/12): 709-719.

[3] Athena V. Data Block Prefetching and Caching in a Hierarchical

Storage model[J]. Information Sciences, 2000, 128(1/2): 19-41.

[4] Richard L, Martin W. New Data Storage and Retrieval Systems for

JET Data[J]. Fusion Engineering and Design, 2000, 60(3): 333-339.

[5] Vijay S M. Policies for Data Archival in Hierarchical Storage

Management[J]. European Journal of Operational Research, 2002,

138(2): 413-435.

[6] 许金良, 杨宏志. 公路工程数据库模型的研究[J]. 公路交通科技,

2004, 21(9): 40-43.

—247—

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc