http://www.paper.edu.cn

AES 算法实现分析及其应用

罗兰,寿国础,胡怡红

北京邮电大学通信测试技术研究中心,北京(100876)

E-mail:luolanzone@gmail.com

摘 要:在介绍 AES 加密算法的基本原理基础上,分析了目前主要的三种 AES 硬件结构实现,

并对其进行分析比较,给出结构的优化实现方法。然后介绍了 AES 在 EPON 中的加密实现。

关键词:AES,加密,硬件结构,EOPN

中图分类号:TN929.11

1. 引言

随着计算机数据通信业务的快速发展,用户对网络的安全性能要求越来越高,自 20 世纪

70 年代以来一直广泛使用的“数据加密标准”(DES)已无法满足需求,AES(Advanced Encryption

Standard)是美国国家标准与技术研究所(NIST)筹划的,旨在取代 DES,以保护 21 世纪敏感政府

信息的新型加密标准。1997 年 4 月 NIST 开始公开征集,经过 3 年的评比、审定,2000 年 10

月 2 日,NIST 宣布 Rijndael 算法当选 AES。Rijndael 是一种迭代分组密码算法,Rijndael 算法

本身支持可变的分组长度和密钥长度,而 AES 只采用了 128 位分组长度和 128、192 或 256 位

的密钥长度。该算法的主要优点是:设计简单,密钥安装快,需要的内存空间少,在所有平台

上运行良好,支持并行处理,可抵御目前所有已知攻击[1]。

2. AES 算法介绍

AES 采用 128 比特分组长度,根据密钥长度不同,128、192 或 256 位长度的密钥需加密的

轮次(用 Nr 表示)分别为 10 轮、12 轮和 l4 轮。经过验证[2],选用 l28 位的明文和密钥是几种

组合中加解密速度最快的。

AES 加密过程包括一个初始密钥加法,记作 AddRoundKey,接着进行 Nr-1 次轮变换 Round,

最后使用一个轮变换 FinalRound。在最后一个轮变换 FinalRound 是将轮变换中的轮密钥加过程

略去。轮变换 Round 由四个变换组成:

(1)字节替代(SubBytes),由一个 S 盒来完成加密过程中的字节替代,它是轮变换中唯

一的非线性变换,S 盒在整个硬件设计中占了很大的比重。S 盒性能的提高对于整个设计性能会

有很大的改善,因此 S 盒是整个设计优化的重点。

(2)行移位(ShiftRows),一个字节换位操作,即输入分组的状态矩阵的第 1 行保持不变,

第 2 行循环左(右)移 1 个字节,第 3 行循环左(右)移 2 个字节,第 4 行循环左(右)移 3 个字节。

+ ,

'02'

(3)列混淆(MixColumns),将状态的每列均乘以一个固定多项式 ( )

C x

'03'

'01'

x

=

+

'01'

x

x

+

由于所乘为固定多项式,Mixcolumn 运算可以由查找表操作代替。

(4)轮密钥加(AddRoundKey),状态通过前三步变换的结果与一个轮密钥(由初始密钥

扩展得到)进行异或得到。

3. AES 硬件实现方法

AES 算法的硬件实现就是主要针对轮函数的四种运算利用合适的硬件资源和结构进行设

- 1 -

�

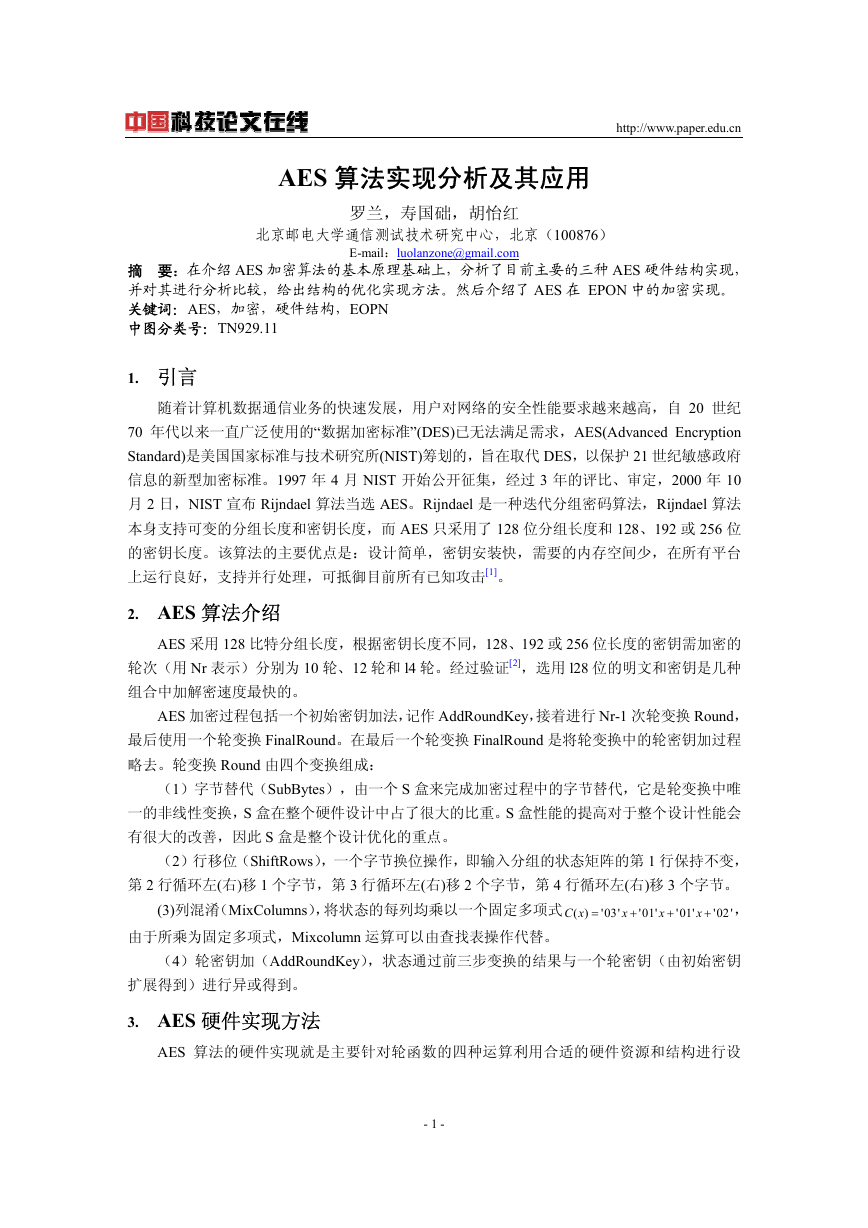

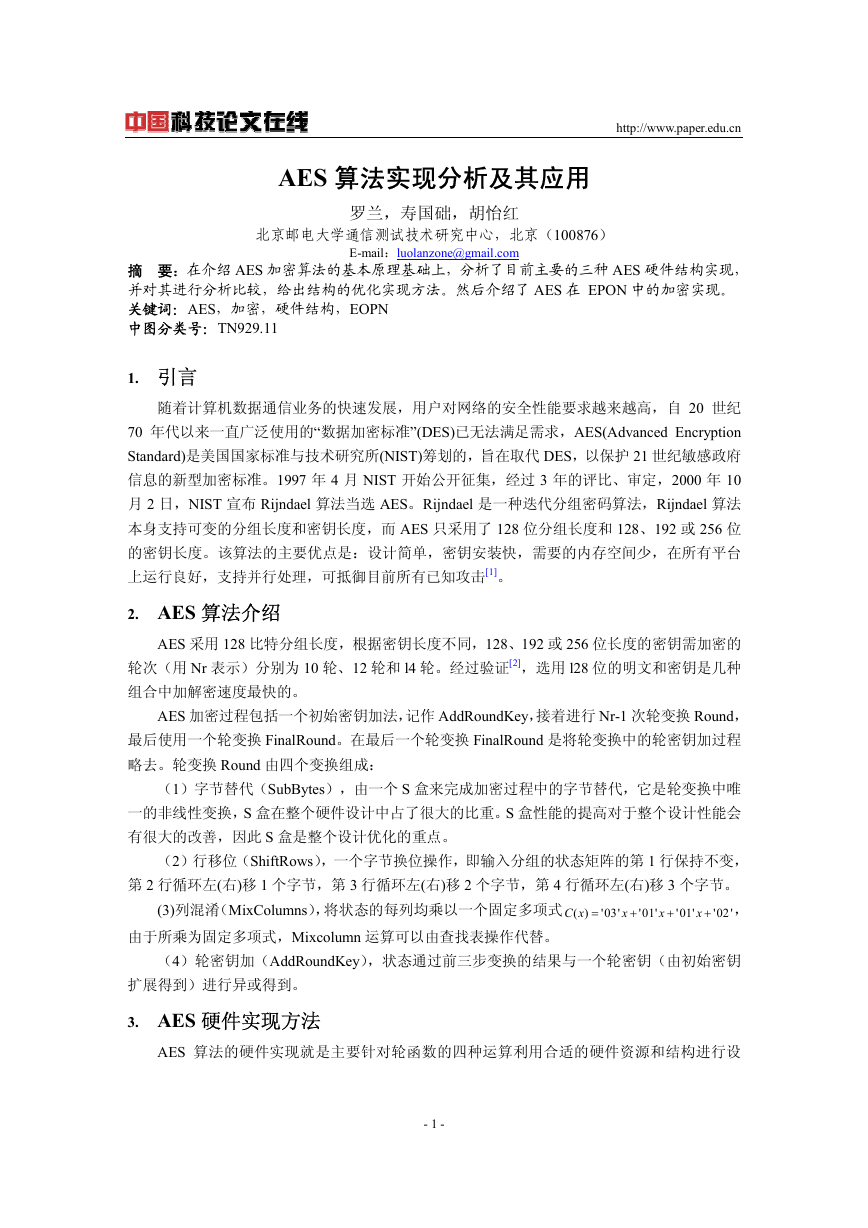

计。本文研究了三种 AES 算法硬件实现结构:完全流水线结构,循环式结构,流水线循环结构。

图 1(a)~(c)给出了三种结构的示意图。这三种结构均支持 128/192/256 比特的密钥大小。

http://www.paper.edu.cn

图 1 硬件实现结构

(1)完全流水线结构

图(a)中将输入的明文(或密文)分成 16 个字节,在第一个轮密钥加(Add Round Keys)变换

后进入 Nr 轮迭代。前 Nr-1 轮完全相同,依次经过字节代替、行移位、列混合、轮密钥加,最

后一轮则跳过了列混合。在这种结构中,每个流水线级都是一个轮单元,轮函数用组合逻辑实

现,Nr 轮迭代过程直接相连,前一轮结果直接作为下一轮的输入,1 个时钟周期内完成一个分

组运算,吞吐量可以达到最佳状态。当流水线的轮数 K=Nr 时称为完全流水线结构。流水线结

构的面积与 k 成正比。建立流水线是提高速度的常用方法,但是硬件资源消耗大(面积换取速

度)。在 AES 算法的硬件实现中,流水线结构是应用较为广泛的实现方式。

(2)循环式结构

- 2 -

�

http://www.paper.edu.cn

图(b)循环式结构中所有迭代只使用一个轮函数单元,根据密钥的大小不同,在 10~14 个

周期内完成一个 128 比特明文分组的加密运算。循环式结构资源占用较少。但每个分组运算时

间比较长,吞吐量相对较低。

(3)流水线循环结构

流水线循环结构是针对流水线结构和循环式结构的不足提出的,能够得到最佳的速度面积

比率。图(c)中给出了 4 级流水线结构,每级流水线内实现了 4 轮模块循环。根据密钥的大小

不同,每个块对 128 比特数据分组加密需要 1~4 个时钟,然后将处理完的数据传输到下一个处

理模块。4 级流水线循环式结构的吞吐量在不同密钥下都是每四个时钟周期 128 比特数据[3].

4. AES 算法实现优化分析

衡量分组密码硬件实现性能的重要参数有两个:1)吞吐量(throughput)。单位时间内加/解密

的数据量(b/s) 。2)电路面积(area),针对 FPGA,指的是所消耗的可配置逻辑块(CLB)。数据

的加密速度和加密的吞吐量密切相关,可用式(1)进行简单计算:

吞吐量=处理的比特平均数/秒. (1)

在 AES 算法模式下,也可表示成:

吞吐量=l28/(处理一个块的时钟周期的平均值+时钟周期值).(2)

在非反馈模式下使用不同的结构,可以实现不同的优化要求。流水线结构能实现速度最大

优化,最小面积需求的应用中,则可使用循环结构。要实现最佳速度面积比率, 流水线循环结

构是最佳选择。结构改进可以实现一定的性能优化

为了提高 AES 加密硬件实现结构的吞吐量,可针对 AES 算法轮函数中的四个关键步骤进

行优化设计和实现。(1)对列混淆的有限域运算进行优化。列混淆是基于 GF(28)代数运算的数

据代换过程,可以通过对运算的分解做出优化。在文献[4]中给出了详细过程。对有限域运算进

行优化有效节约了设计资源。(2)利用 FPGA 中的存储器资源,用查表方法取代乘法操作。将

S 盒用一个 8 入 8 出的查找表实现。这样提高了资源利用率。文献[5]通过对 S 盒的优化,使用

0.137m CMOS 技术在 780MHz 标准库下实现了 10Gbps 的加密速度。

5. AES 加密算法的应用

从 AES 算法提出至今,由于其显著优势已逐步取代 DES 成为新一代加密标准。它的主要

特点有:成功运用了二元域上多项式的结构,硬件实现很方便。软件实现也方便,可以在智能

卡中实现,且速度较高,算法的代码行少.效率较高,AES 的均衡对称结构使其对差分分析攻

击明显强于 DES。AES 在保障数据安全方面已经得到了广泛应用。在本文中,仅介绍 AES 加密

算法在 EPON 中对下行流量的加密。

5.1 AES 在 EPON 中的加密实现

EPON 是基于以太网的光纤接入方式,由光线路终端(OLT)、光合/分路器和光网络单元(ONU)

组成。EPON 是点到多点的无源光网络,通常采用总线型(Bus PON)、树型 Tree PON)或环型(Ring

PON)拓扑结构,在 EPON 中表现为 0LT(光线路终端)以由以太帧组成的下行帧的形式向 ONU (光

网络单元)发送信息,每个 ONU 收到全部的数据流,然后根据 ONU 的媒质访问控制(MAC)地址

提取出特定的数据包。正是由于这种下行方式,使网络存在窃听、假冒、业务拒绝等安全威胁。

- 3 -

�

http://www.paper.edu.cn

故需对 EPON 下行流量进行加密以保证其安全性。在 EPON 设备中,传输速率达到 1G/s,完全

采用 AES 加密。

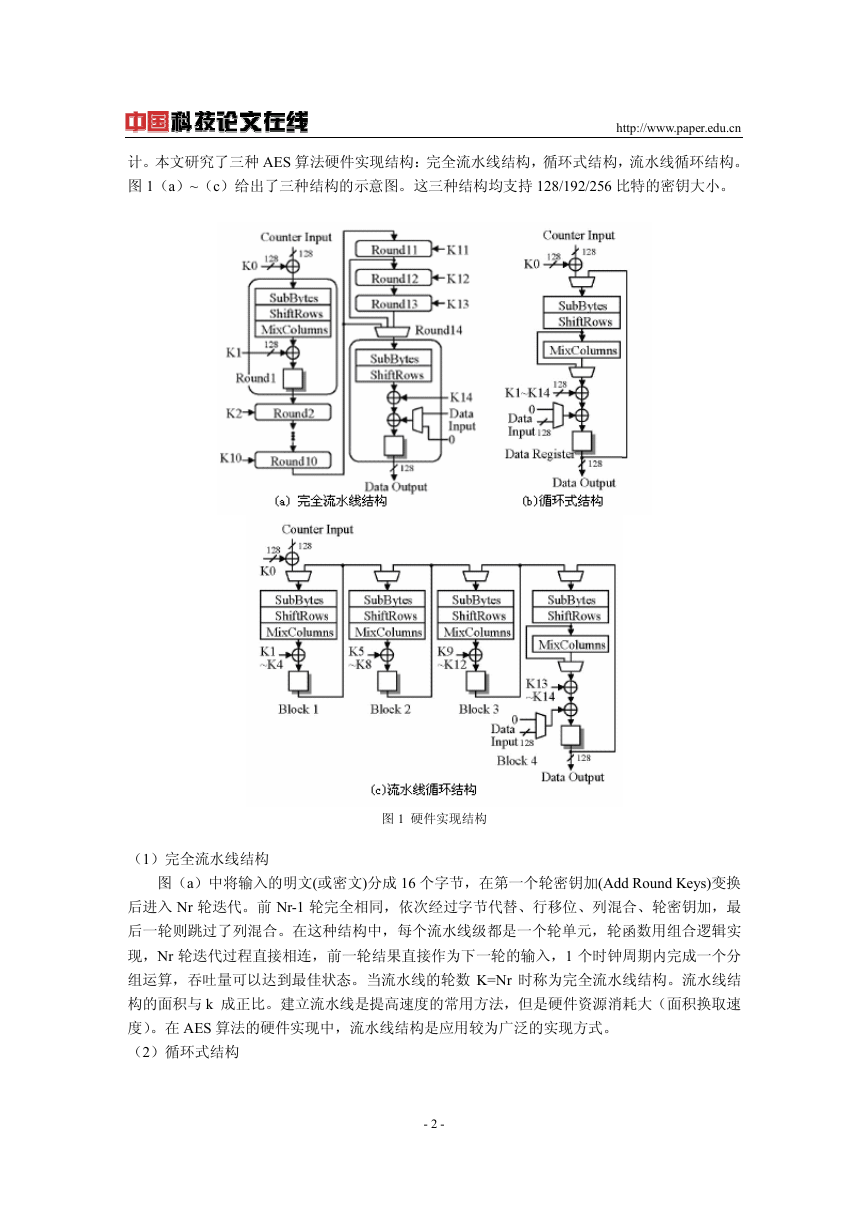

EPON 实现了一个 P2P 仿真(Emulation)子层,该子层使得 P2MP 网络拓扑对于高层来说就

是多个点对点链路的集合,该子层是通过在每个数据帧的前面加上一个 LLID(Logical Link

Identification)逻辑链路标识来实现的,该 LLID 将替换前导码中的两个字节。加密可以在仿真子

层来实现,图 2 给出加密子层在分层协议中的位置。经过加密,数据帧需要添加相应的加密信

息标识字段。为了不改变帧长,其位置可以是帧中间数据段的前部,然而这样会打断加密段的

连续性,增加解密的复杂度;或者位于前导码,在 8 个字节的前导码中已经使用了六个,包括

帧起始标记 SOP(1byte),OAM(1byte),消息 Msg(1byte),CRC(1byte)以及 LLID(2bytes),还有

两个未使用,这样可以利用其中一个字节用于标识加密信息。字段具体内容至少应该包括:加

密是否标记,需要一个比特,标记帧是否被加密;密钥索引,一个比特,其作用指示在解密过

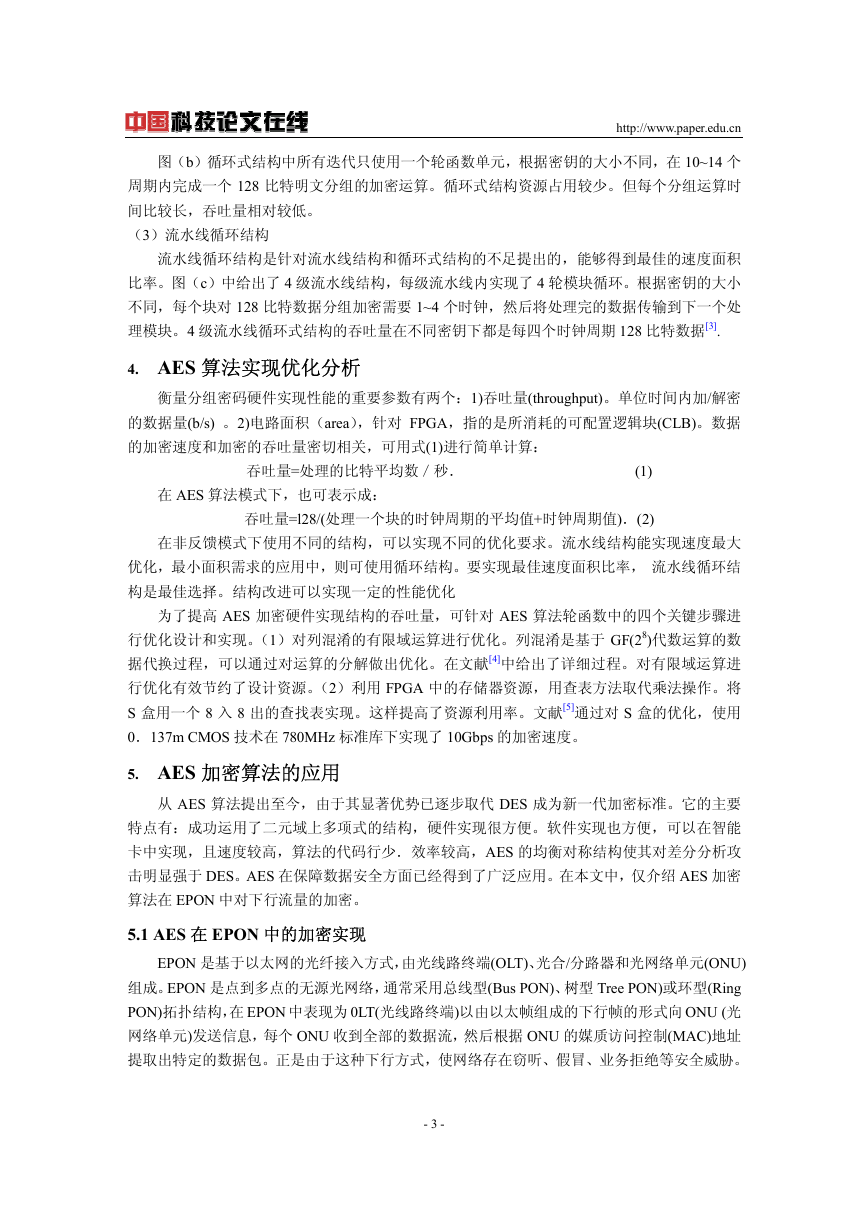

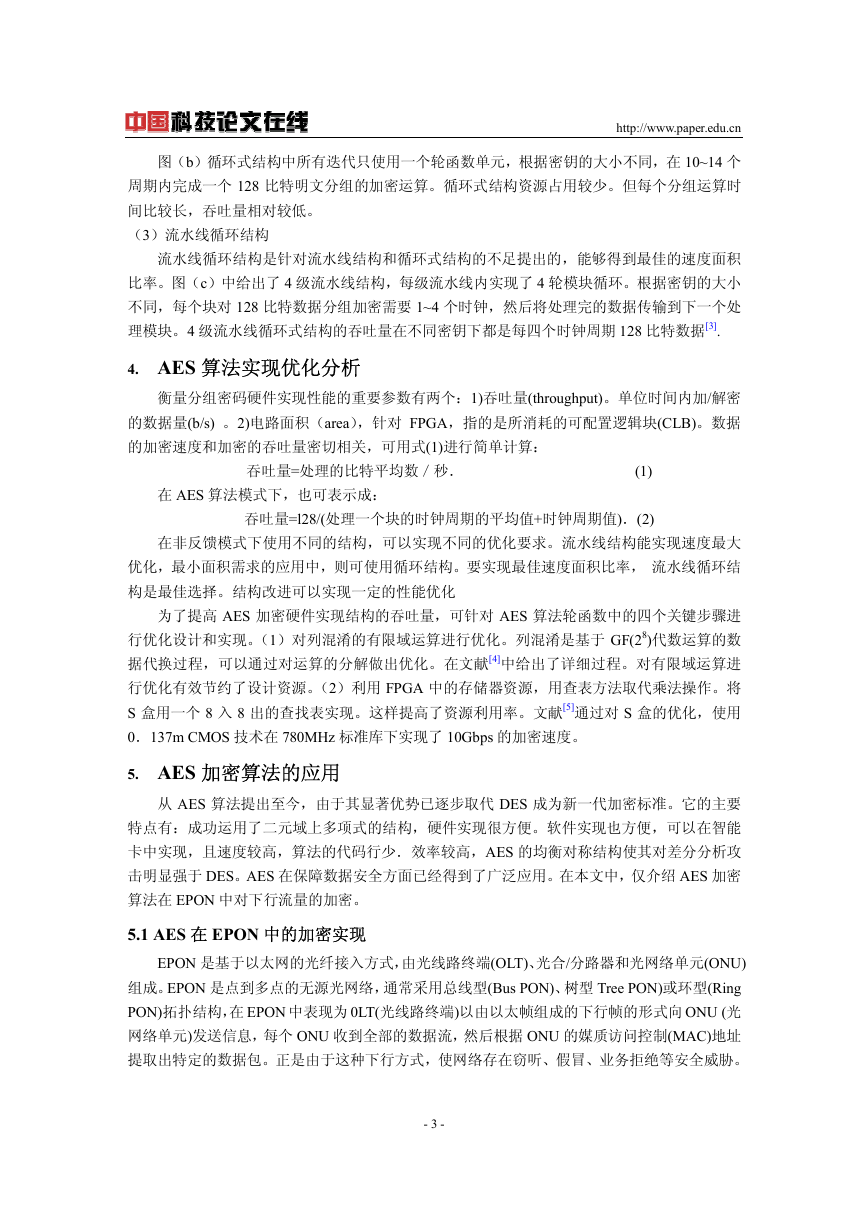

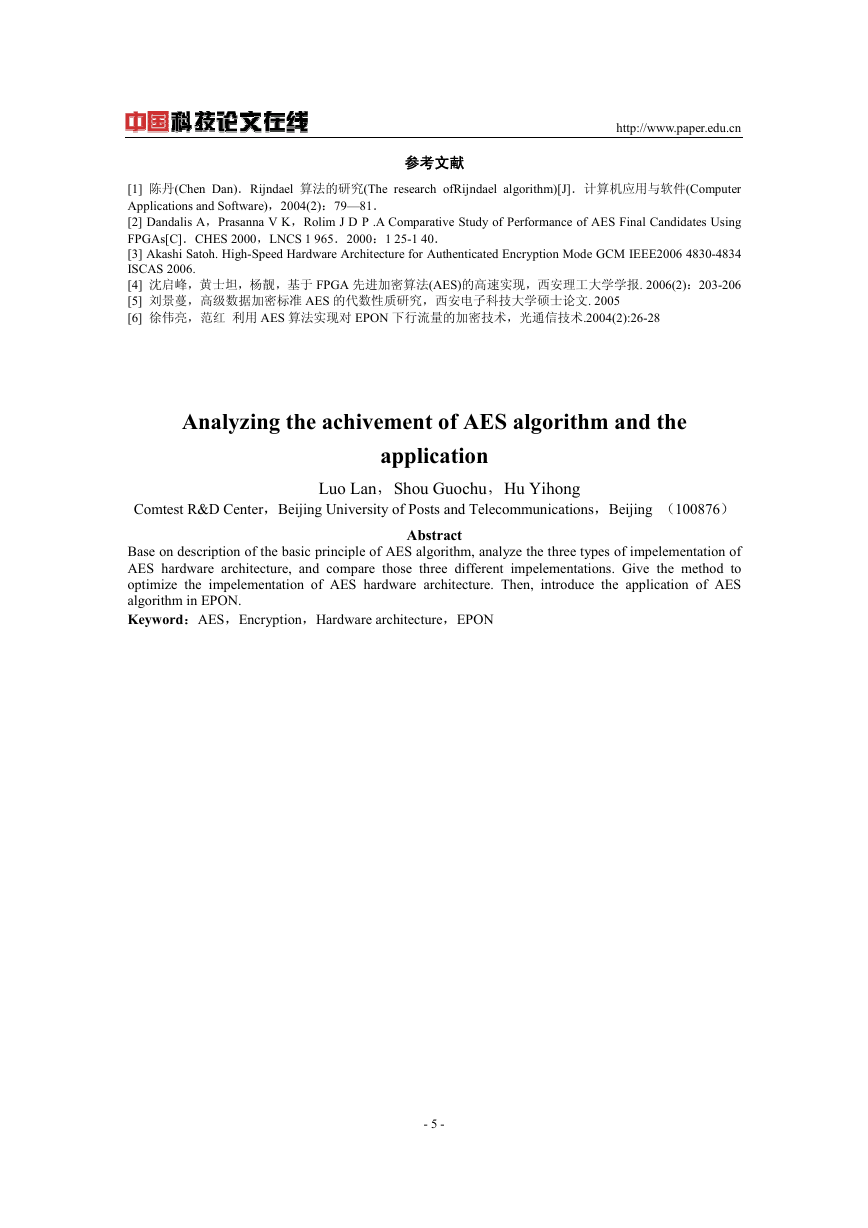

程中要采用哪个密钥,这对于密钥平滑更新是必须的。因此一个经过加密的完整的帧结构如图

3 所示,包含了前导码(Preamble)、加密信息标识(Enc)、LLID、目的地址(DA)、源地址(SA)、

类型/长度字段(L/Type)、Data 和帧校验序列 (FCS)。加密的数据帧范围应从 DA 到 FCS。

图 2 分层结构图

图 3 加密后帧结构图

加密过程具体为:AES 算法的数据块长度为 128bits,首先将明文以每 16 个字节为一组,

得到若干组分组明文,记为 Pi,剩余不足 16 个字节的,填充相应个数 0 字节;在对第一组进行

加密前,需要先产生一个 16 个字节的初始化向量(IV)并保存,标记为 Co;然后先将 PI 和 C0 进

行异或,紧接着采用 AES 算法对异或结果进行加密,得到分组密文 Ci;以后的每一分组明文在

加密前先与前一个分组密文进行异或,如此下去,直至最后一个分组。

在加密过程中可以看到,为了适应 AES 算法的 128bits 的数据块长度,在最后一个分组不

得不填充了若干个无用的字节,称之为完全填充,这样就降低了 EPON 的效率。文献[6]提出了

部分填充和不填充两种解决方式,对其进行了仿真,从效率的角度出发,指出采用不填充是最

佳方法。

6. 结束语

AES 加密算法因加密效率高,安全性强,将逐步替代 DES。为了更好的提高系统性能。需

要进一步研究结构优化和算法优化的结合。随着 AES 算法实现的不断优化设计,必将为保证接

入网数据安全而得到广泛应用。

- 4 -

�

参考文献

http://www.paper.edu.cn

[1] 陈丹(Chen Dan).Rijndael 算法的研究(The research ofRijndael algorithm)[J].计算机应用与软件(Computer

Applications and Software),2004(2):79—81.

[2] Dandalis A,Prasanna V K,Rolim J D P .A Comparative Study of Performance of AES Final Candidates Using

FPGAs[C].CHES 2000,LNCS 1 965.2000:1 25-1 40.

[3] Akashi Satoh. High-Speed Hardware Architecture for Authenticated Encryption Mode GCM IEEE2006 4830-4834

ISCAS 2006.

[4] 沈启峰,黄士坦,杨靓,基于 FPGA 先进加密算法(AES)的高速实现,西安理工大学学报. 2006(2):203-206

[5] 刘景蔓,高级数据加密标准 AES 的代数性质研究,西安电子科技大学硕士论文. 2005

[6] 徐伟亮,范红 利用 AES 算法实现对 EPON 下行流量的加密技术,光通信技术.2004(2):26-28

Analyzing the achivement of AES algorithm and the

application

Comtest R&D Center,Beijing University of Posts and Telecommunications,Beijing (100876)

Luo Lan,Shou Guochu,Hu Yihong

Abstract

Base on description of the basic principle of AES algorithm, analyze the three types of impelementation of

AES hardware architecture, and compare those three different impelementations. Give the method to

optimize the impelementation of AES hardware architecture. Then, introduce the application of AES

algorithm in EPON.

Keyword:AES,Encryption,Hardware architecture,EPON

- 5 -

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc