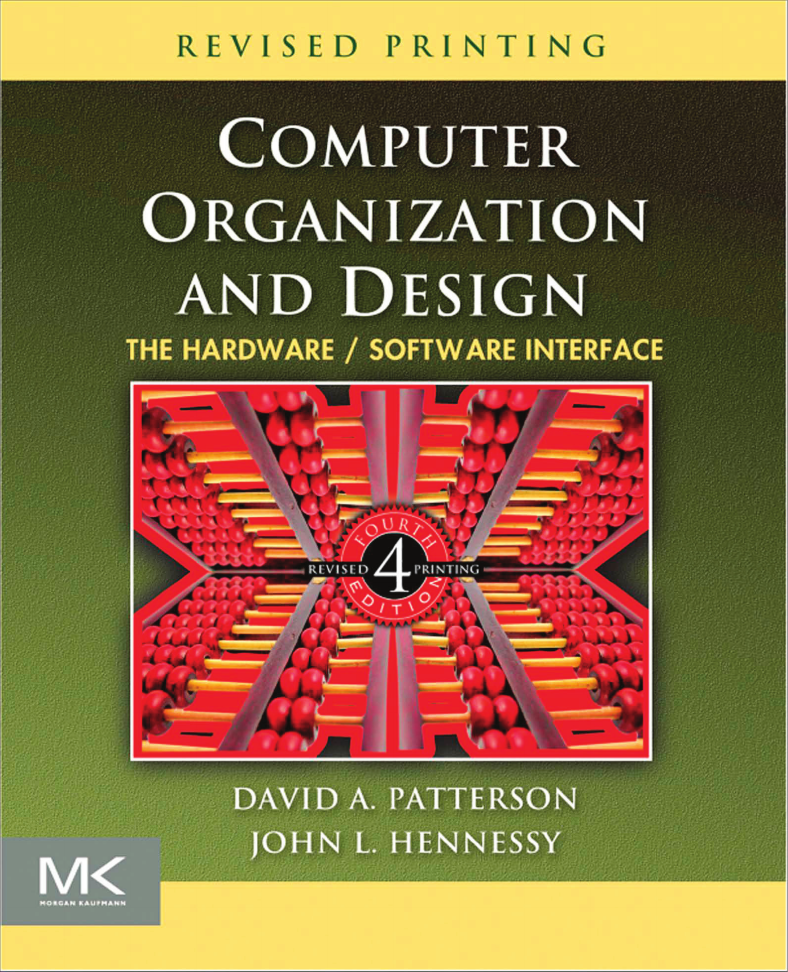

Front Cover

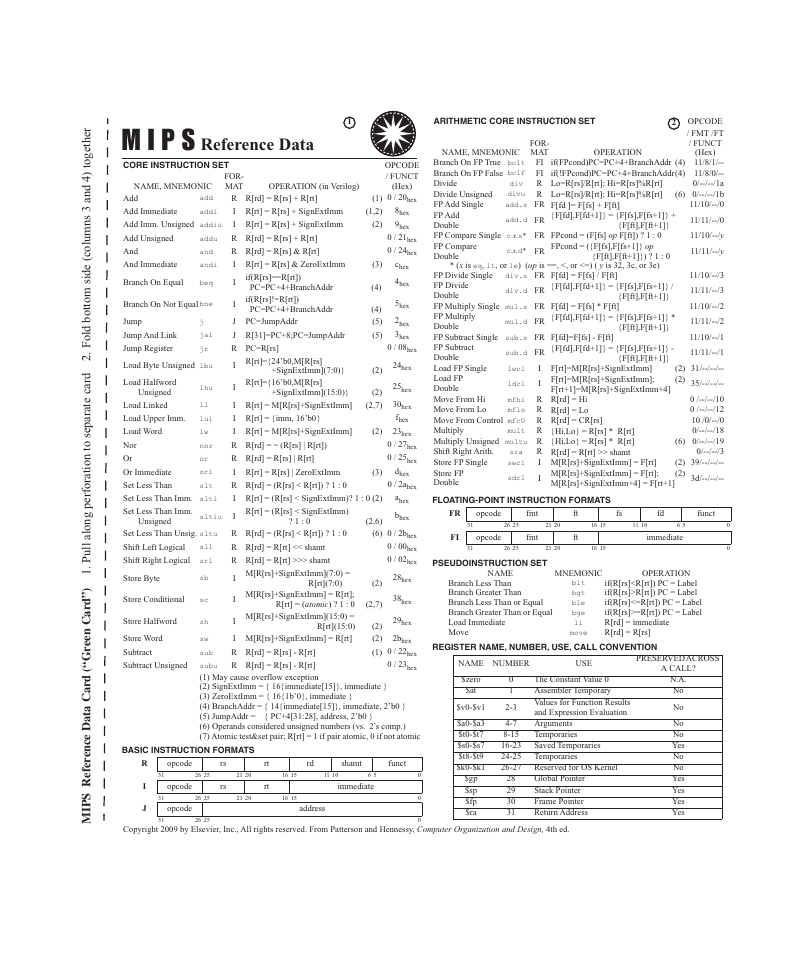

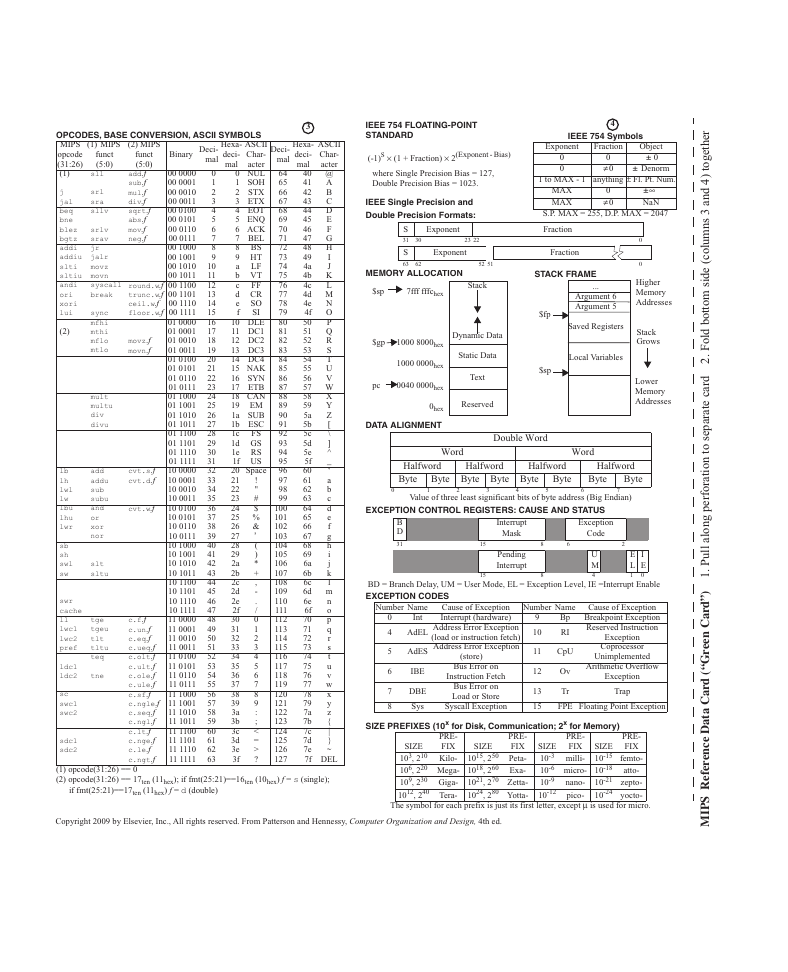

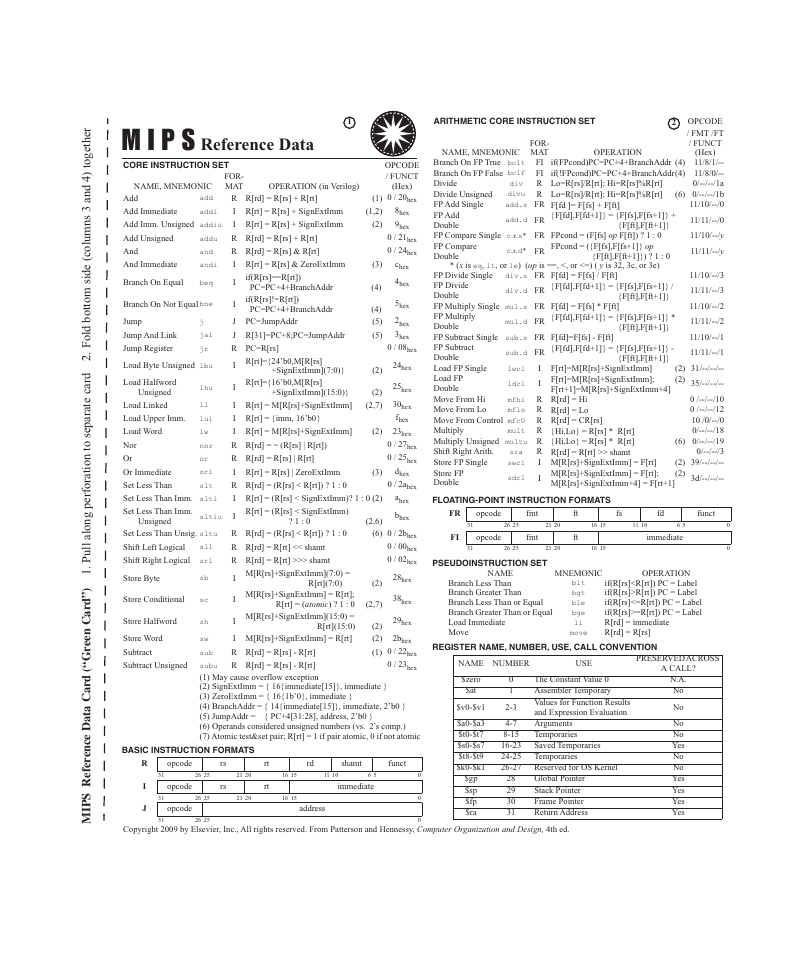

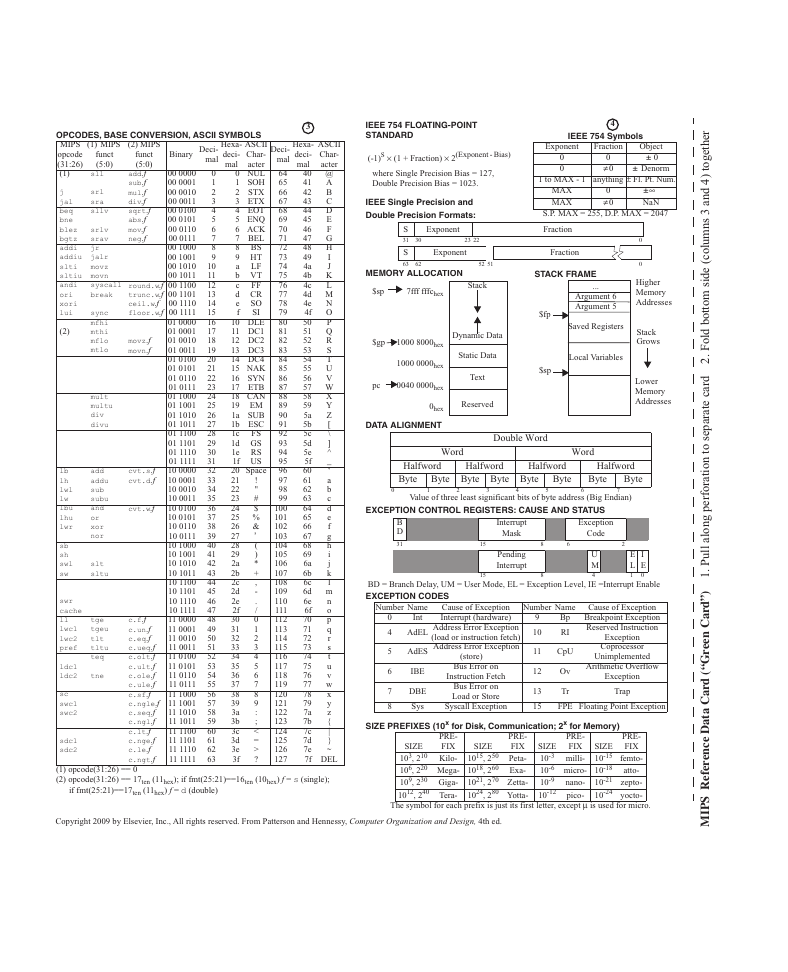

MIPS Reference Data

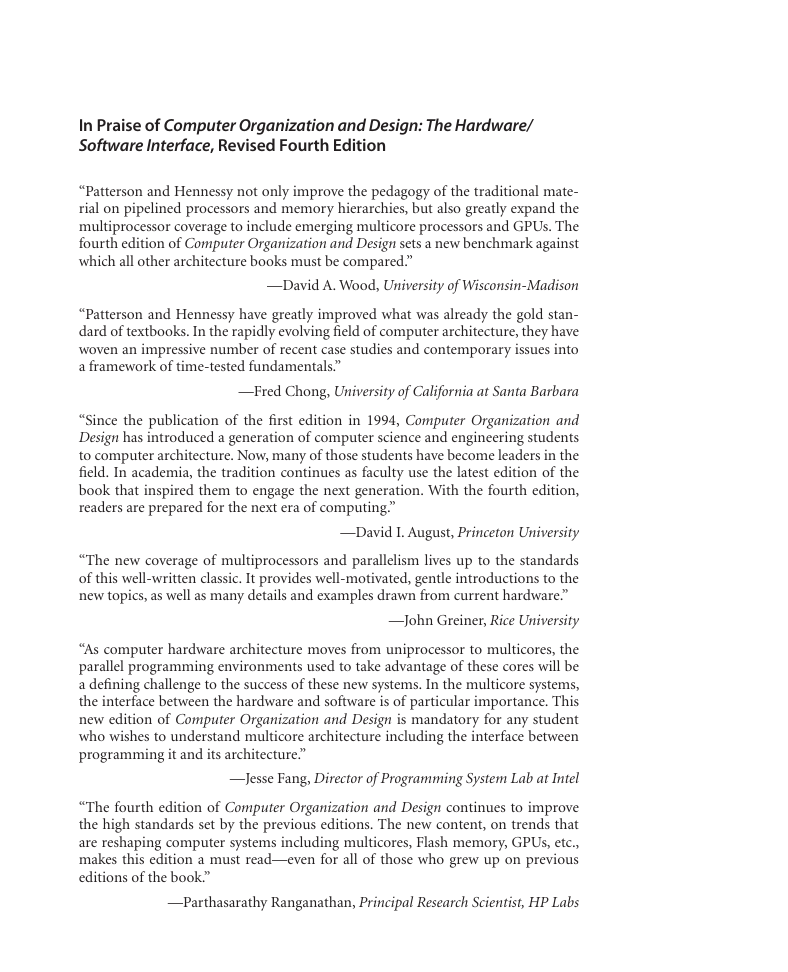

In Praise of Computer Organization and Design: The Hardware/Software Interface, Revised Fourth Edition

Acknowledgments

Computer Organization and Design: The Hardware/Software Interface

Copyright Page

Dedication Page

Contents

Preface

About This Book

About the Other Book

Changes for the Fourth Edition

Instructor Support

Concluding Remarks

Acknowledgments for the Fourth Edition

1 Computer Abstractions and Technology

1.1 Introduction

Classes of Computing Applications and Their Characteristics

What You Can Learn in This Book

1.2 Below Your Program

From a High-Level Language to the Language of Hardware

1.3 Under the Covers

Anatomy of a Mouse

Through the Looking Glass

Opening the Box

A Safe Place for Data

Communicating with Other Computers

Technologies for Building Processors and Memory

1.4 Performance

Defining Performance

Measuring Performance

CPU Performance and Its Factors

Instruction Performance

The Classic CPU Performance Equation

1.5 The Power Wall

1.6 The Sea Change: The Switch from Uniprocessors to Multiprocessors

1.7 Real Stuff: Manufacturing and Benchmarking the AMD Opteron X4

SPEC CPU Benchmark

SPEC Power Benchmark

1.8 Fallacies and Pitfalls

1.9 Concluding Remarks

Road Map for This Book

1.10 Historical Perspective and Further Reading

1.11 Exercises

Exercise 1.1

Exercise 1.2

Exercise 1.3

Exercise 1.4

Exercise 1.5

Exercise 1.6

Exercise 1.7

Exercise 1.8

Exercise 1.9

Exercise 1.10

Exercise 1.11

Exercise 1.12

Exercise 1.13

Exercise 1.14

Exercise 1.15

Exercise 1.16

2 Instructions: Language of the Computer

2.1 Introduction

2.2 Operations of the Computer Hardware

2.3 Operands of the Computer Hardware

Memory Operands

Constant or Immediate Operands

2.4 Signed and Unsigned Numbers

Summary

2.5 Representing Instructions in the Computer

MIPS Fields

2.6 Logical Operations

2.7 Instructions for Making Decisions

Loops

Case/Switch Statement

2.8 Supporting Procedures in Computer Hardware

Using More Registers

Nested Procedures

Allocating Space for New Data on the Stack

Allocating Space for New Data on the Heap

2.9 Communicating with People

Characters and Strings in Java

2.10 MIPS Addressing for 32-Bit Immediates and Addresses

32-Bit Immediate Operands

Addressing in Branches and Jumps

MIPS Addressing Mode Summary

Decoding Machine Language

2.11 Parallelism and Instructions: Synchronization

2.12 Translating and Starting a Program

Compiler

Assembler

Linker

Loader

Dynamically Linked Libraries

Starting a Java Program

2.13 A C Sort Example to Put It All Together

The Procedure swap

Register Allocation for swap

Code for the Body of the Procedure swap

The Full swap Procedure

The Procedure sort

Register Allocation for sort

Code for the Body of the Procedure sort

The Procedure Call in sort

Passing Parameters in sort

Preserving Registers in sort

The Full Procedure sort

2.14 Arrays versus Pointers

Array Version of Clear

Pointer Version of Clear

Comparing the Two Versions of Clear

2.15 Advanced Material: Compiling C and Interpreting Java

2.16 Real Stuff: ARM Instructions

Addressing Modes

Compare and Conditional Branch

Unique Features of ARM

2.17 Real Stuff: x86 Instructions

Evolution of the Intel x86

x86 Registers and Data Addressing Modes

x86 Integer Operations

x86 Instruction Encoding

x86 Conclusion

2.18 Fallacies and Pitfalls

2.19 Concluding Remarks

2.20 Historical Perspective and Further Reading

2.21 Exercises

Exercise 2.1

Exercise 2.2

Exercise 2.3

Exercise 2.4

Exercise 2.5

Exercise 2.6

Exercise 2.7

Exercise 2.8

Exercise 2.9

Exercise 2.10

Exercise 2.11

Exercise 2.12

Exercise 2.13

Exercise 2.14

Exercise 2.15

Exercise 2.16

Exercise 2.17

Exercise 2.18

Exercise 2.19

Exercise 2.20

Exercise 2.21

Exercise 2.22

Exercise 2.23

Exercise 2.24

Exercise 2.25

Exercise 2.26

Exercise 2.27

Exercise 2.28

Exercise 2.29

Exercise 2.30

Exercise 2.31

Exercise 2.32

Exercise 2.33

Exercise 2.34

Exercise 2.35

Exercise 2.36

Exercise 2.37

Exercise 2.38

Exercise 2.39

Exercise 2.40

3 Arithmetic for Computers

3.1 Introduction

3.2 Addition and Subtraction

Arithmetic for Multimedia

Summary

3.3 Multiplication

Sequential Version of the Multiplication Algorithmand Hardware

Signed Multiplication

Faster Multiplication

Multiply in MIPS

Summary

3.4 Division

A Division Algorithm and Hardware

Signed Division

Faster Division

Divide in MIPS

Summary

3.5 Floating Point

Floating-Point Representation

Floating-Point Addition

Floating-Point Multiplication

Floating-Point Instructions in MIPS

Accurate Arithmetic

Summary

3.6 Parallelism and Computer Arithmetic: Associativity

3.7 Real Stuff: Floating Point in the x86

The x86 Floating-Point Architecture

The Intel Streaming SIMD Extension 2 (SSE2)Floating-Point Architecture

3.8 Fallacies and Pitfalls

3.9 Concluding Remarks

3.10 Historical Perspective and Further Reading

3.11 Exercises

Exercise 3.1

Exercise 3.2

Exercise 3.3

Exercise 3.4

Exercise 3.5

Exercise 3.6

Exercise 3.7

Exercise 3.8

Exercise 3.9

Exercise 3.10

Exercise 3.11

Exercise 3.12

Exercise 3.13

Exercise 3.14

Exercise 3.15

4 The Processor

4.1 Introduction

A Basic MIPS Implementation

An Overview of the Implementation

4.2 Logic Design Conventions

Clocking Methodology

4.3 Building a Datapath

Creating a Single Datapath

4.4 A Simple Implementation Scheme

The ALU Control

Designing the Main Control Unit

Operation of the Datapath

Finalizing Control

Why a Single-Cycle Implementation Is Not Used Today

4.5 An Overview of Pipelining

Designing Instruction Sets for Pipelining

Pipeline Hazards

Structural Hazards

Data Hazards

Control Hazards

Pipeline Overview Summary

4.6 Pipelined Datapath and Control

Graphically Representing Pipelines

Pipelined Control

4.7 Data Hazards: Forwarding versus Stalling

Data Hazards and Stalls

4.8 Control Hazards

Assume Branch Not Taken

Reducing the Delay of Branches

Dynamic Branch Prediction

Pipeline Summary

4.9 Exceptions

How Exceptions Are Handled in the MIPS Architecture

Exceptions in a Pipelined Implementation

4.10 Parallelism and Advanced Instruction-Level Parallelism

The Concept of Speculation

Static Multiple Issue

An Example: Static Multiple Issue with the MIPS ISA

Dynamic Multiple-Issue Processors

Dynamic Pipeline Scheduling

Power Efficiency and Advanced Pipelining

4.11 Real Stuff: the AMD Opteron X4 (Barcelona) Pipeline

4.12 Advanced Topic: an Introduction to Digital Design Using a Hardware Design Language to Describe and Model a Pipeline and More Pipelining Illustrations

4.13 Fallacies and Pitfalls

4.14 Concluding Remarks

4.15 Historical Perspective and Further Reading

4.16 Exercises

Exercise 4.1

Exercise 4.2

Exercise 4.3

Exercise 4.4

Exercise 4.5

Exercise 4.6

Exercise 4.7

Exercise 4.8

Exercise 4.9

Exercise 4.10

Exercise 4.11

Exercise 4.12

Exercise 4.13

Exercise 4.14

Exercise 4.15

Exercise 4.16

Exercise 4.17

Exercise 4.18

Exercise 4.19

Exercise 4.20

Exercise 4.21

Exercise 4.22

Exercise 4.23

Exercise 4.24

Exercise 4.25

Exercise 4.26

Exercise 4.27

Exercise 4.28

Exercise 4.29

Exercise 4.30

Exercise 4.31

Exercise 4.32

Exercise 4.33

Exercise 4.34

Exercise 4.35

Exercise 4.36

Exercise 4.37

Exercise 4.38

Exercise 4.39

5 Large and Fast: Exploiting Memory Hierarchy

5.1 Introduction

5.2 The Basics of Caches

Accessing a Cache

Handling Cache Misses

Handling Writes

An Example Cache: The Intrinsity FastMATH Processor

Designing the Memory System to Support Caches

Summary

5.3 Measuring and Improving Cache Performance

Reducing Cache Misses by More Flexible Placement of Blocks

Locating a Block in the Cache

Choosing Which Block to Replace

Reducing the Miss Penalty Using Multilevel Caches

Summary

5.4 Virtual Memory

Placing a Page and Finding It Again

Page Faults

What about Writes?

Making Address Translation Fast: the TLB

The Intrinsity FastMATH TLB

Integrating Virtual Memory, TLBs, and Caches

Implementing Protection with Virtual Memory

Handling TLB Misses and Page Faults

Summary

5.5 A Common Framework for Memory Hierarchies

Question 1: Where Can a Block Be Placed?

Question 2: How Is a Block Found?

Question 3: Which Block Should Be Replaced on a Cache Miss?

Question 4: What Happens on a Write?

The Three Cs: An Intuitive Model for Understanding the Behavior of Memory Hierarchies

5.6 Virtual Machines

Requirements of a Virtual Machine Monitor

(Lack of) Instruction Set Architecture Support for Virtual Machines

Protection and Instruction Set Architecture

5.7 Using a Finite-State Machine to Control a Simple Cache

A Simple Cache

Finite-State Machines

FSM for a Simple Cache Controller

5.8 Parallelism and Memory Hierarchies: Cache Coherence

Basic Schemes for Enforcing Coherence

Snooping Protocols

5.9 Advanced Material: Implementing Cache Controllers

5.10 Real Stuff: the AMD Opteron X4 (Barcelona) and Intel Nehalem Memory Hierarchies

The Memory Hierarchies of the Nehalem and Opteron

Techniques to Reduce Miss Penalties

5.11 Fallacies and Pitfalls

5.12 Concluding Remarks

5.13 Historical Perspective and Further Reading

5.14 Exercises

Exercise 5.1

Exercise 5.2

Exercise 5.3

Exercise 5.4

Exercise 5.5

Exercise 5.6

Exercise 5.7

Exercise 5.8

Exercise 5.9

Exercise 5.10

Exercise 5.11

Exercise 5.12

Exercise 5.13

Exercise 5.14

Exercise 5.15

Exercise 5.16

Exercise 5.17

Exercise 5.18

6 Storage and Other I/O Topics

6.1 Introduction

6.2 Dependability, Reliability, and Availability

6.3 Disk Storage

6.4 Flash Storage

6.5 Connecting Processors, Memory, and I/O Devices

Connection Basics

The I/O Interconnects of the x86 Processors

6.6 Interfacing I/O Devices to the Processor, Memory, and Operating System

Giving Commands to I/O Devices

Communicating with the Processor

Interrupt Priority Levels

Transferring the Data between a Device and Memory

Direct Memory Access and the Memory System

6.7 I/O Performance Measures: Examples from Disk and File Systems

Transaction Processing I/O Benchmarks

File System and Web I/O Benchmarks

6.8 Designing an I/O System

6.9 Parallelism and I/O: Redundant Arrays of Inexpensive Disks

No Redundancy (RAID 0)

Mirroring (RAID 1)

Error Detecting and Correcting Code (RAID 2)

Bit-Interleaved Parity (RAID 3)

Block-Interleaved Parity (RAID 4)

Distributed Block-Interleaved Parity (RAID 5)

P + Q Redundancy (RAID 6)

RAID Summary

6.10 Real Stuff: Sun Fire x4150 Server

6.11 Advanced Topics: Networks

6.12 Fallacies and Pitfalls

6.13 Concluding Remarks

6.14 Historical Perspective and Further Reading

6.15 Exercises

Exercise 6.1

Exercise 6.2

Exercise 6.3

Exercise 6.4

Exercise 6.5

Exercise 6.6

Exercise 6.7

Exercise 6.8

Exercise 6.9

Exercise 6.10

Exercise 6.11

Exercise 6.12

Exercise 6.13

Exercise 6.14

Exercise 6.15

Exercise 6.16

Exercise 6.17

Exercise 6.18

Exercise 6.19

Exercise 6.20

7 Multicores, Multiprocessors, and Clusters

7.1 Introduction

7.2 The Difficulty of Creating Parallel Processing Programs

7.3 Shared Memory Multiprocessors

7.4 Clusters and Other Message-Passing Multiprocessors

7.5 Hardware Multithreading

7.6 SISD, MIMD, SIMD, SPMD, and Vector

SIMD in x86: Multimedia Extensions

Vector

Vector versus Scalar

Vector versus Multimedia Extensions

7.7 Introduction to Graphics Processing Units

An Introduction to the NVIDIA GPU Architecture

Putting GPUs into Perspective

7.8 Introduction to Multiprocessor Network Topologies

Implementing Network Topologies

7.9 Multiprocessor Benchmarks

7.10 Roofline: A Simple Performance Model

The Roofline Model

Comparing Two Generations of Opterons

7.11 Real Stuff: Benchmarking Four Multicores Using the Roofline Model

Four Multicore Systems

Sparse Matrix

Structured Grid

Productivity

7.12 Fallacies and Pitfalls

7.13 Concluding Remarks

7.14 Historical Perspective and Further Reading

7.15 Exercises

Exercise 7.1

Exercise 7.2

Exercise 7.3

Exercise 7.4

Exercise 7.5

Exercise 7.6

Exercise 7.7

Exercise 7.8

Exercise 7.9

Exercise 7.10

Exercise 7.11

Exercise 7.12

Exercise 7.13

Exercise 7.14

Exercise 7.15

Exercise 7.16

Exercise 7.17

Exercise 7.18

Exercise 7.19

Exercise 7.20

Exercise 7.21

Exercise 7.22

Exercise 7.23

Appendix A. Graphics and Computing GPUs

A.1 Introduction

A Brief History of GPU Evolution

GPU Graphics Trends

Heterogeneous System

GPU Evolves into Scalable Parallel Processor

Why CUDA and GPU Computing?

GPU Unifies Graphics and Computing

GPU Visual Computing Applications

A.2 GPU System Architectures

Heterogeneous CPU–GPU System Architecture

The Historical PC (circa 1990)

Game Consoles

GPU Interfaces and Drivers

Graphics Logical Pipeline

Mapping Graphics Pipeline to Unified GPU Processors

Basic Unified GPU Architecture

Processor Array

A.3 Programming GPUs

Programming Real-Time Graphics

Logical Graphics Pipeline

Graphics Shader Programs

Pixel Shader Example

Programming Parallel Computing Applications

Data Parallel Problem Decomposition

Scalable Parallel Programming with CUDA

The CUDA Paradigm

Restrictions

Implications for Architecture

A.4 Multithreaded Multiprocessor Architecture

Massive Multithreading

Multiprocessor Architecture

Single-Instruction Multiple-Thread (SIMT)

SIMT Warp Execution and Divergence

Managing Threads and Thread Blocks

Thread Instructions

Instruction Set Architecture (ISA)

Memory Access Instructions

Barrier Synchronization for Thread Communication

Streaming Processor (SP)

Special Function Unit (SFU)

Comparing with Other Multiprocessors

Multithreaded Multiprocessor Conclusion

A.5 Parallel Memory System

DRAM Considerations

Caches

MMU

Memory Spaces

Global memory

Shared memory

Local Memory

Constant Memory

Texture Memory

Surfaces

Load/Store Access

ROP

A.6 Floating-point Arithmetic

Supported Formats

Basic Arithmetic

Specialized Arithmetic

Texture Operations

Performance

Double precision

A.7 Real Stuff: The NVIDIA GeForce 8800

Streaming Processor Array (SPA)

Texture/Processor Cluster (TPC)

Streaming Multiprocessor (SM)

Instruction Set

Streaming Processor (SP)

Special Function Unit (SFU)

Rasterization

Raster Operations Processor (ROP) and Memory System

Scalability

Performance

Dense Linear Algebra Performance

FFT Performance

Sorting Performance

A.8 Real Stuff: Mapping Applications to GPUs

Sparse Matrices

Caching in Shared memory

Scan and Reduction

Radix Sort

N-Body Applications on a GPU1

N-Body Mathematics

Optimization for GPU Execution

Using Shared memory

Using Multiple Threads per Body

Performance Comparison

Results

A.9 Fallacies and Pitfalls

A.10 Concluding Remarks

Acknowledgments

A.11 Historical Perspective and Further Reading

Appendix B. Assemblers, Linkers, and the SPIM Simulator

B.1 Introduction

When to Use Assembly Language

Drawbacks of Assembly Language

B.2 Assemblers

Object File Format

Additional Facilities

B.3 Linkers

B.4 Loading

B.5 Memory Usage

B.6 Procedure Call Convention

Procedure Calls

Procedure Call Example

Another Procedure Call Example

B.7 Exceptions and Interrupts

B.8 Input and Output

B.9 SPIM

Simulation of a Virtual Machine

Getting Started with SPIM

Surprising Features

Byte Order

System Calls

B.10 MIPS R2000 Assembly Language

Addressing Modes

Assembler Syntax

Encoding MIPS Instructions

Instruction Format

Addition (with overflow)

Multiply (without overflow)

Arithmetic and Logical Instructions

Absolute value

Addition (with overflow)

Addition (without overflow)

Addition immediate (with overflow)

Addition immediate (without overflow)

AND

AND immediate

Count leading ones

Count leading zeros

Divide (with overflow)

Divide (without overflow)

Divide (with overflow)

Divide (without overflow)

Multiply

Unsigned multiply

Multiply (without overflow)

Multiply (with overflow)

Unsigned multiply (with overflow)

Multiply add

Unsigned multiply add

Multiply subtract

Unsigned multiply subtract

Negate value (with overflow)

Negate value (without overflow)

NOR

NOT

OR

OR immediate

Remainder

Unsigned remainder

Shift left logical

Shift left logical variable

Shift right arithmetic

Shift right arithmetic variable

Shift right logical

Shift right logical variable

Rotate left

Rotate right

Subtract (with overflow)

Subtract (without overflow)

Exclusive OR

XOR immediate

Constant-Manipulating Instructions

Load upper immediate

Load immediate

Comparison Instructions

Set less than

Set less than unsigned

Set less than immediate

Set less than unsigned immediate

Set equal

Set greater than equal

Set greater than equal unsigned

Set greater than

Set greater than unsigned

Set less than equal

Set less than equal unsigned

Set not equal

Branch Instructions

Branch instruction

Branch coprocessor false

Branch coprocessor true

Branch on equal

Branch on greater than equal zero

Branch on greater than equal zero and link

Branch on greater than zero

Branch on less than equal zero

Branch on less than and link

Branch on less than zero

Branch on not equal

Branch on equal zero

Branch on greater than equal

Branch on greater than equal unsigned

Branch on greater than

Branch on greater than unsigned

Branch on less than equal

Branch on less than equal unsigned

Branch on less than

Branch on less than unsigned

Branch on not equal zero

Jump Instructions

Jump

Jump and link

Jump and link register

Jump register

Trap Instructions

Trap if equal

Trap if equal immediate

Trap if not equal

Trap if not equal immediate

Trap if greater equal

Unsigned trap if greater equal

Trap if greater equal immediate

Unsigned trap if greater equal immediate

Trap if less than

Unsigned trap if less than

Trap if less than immediate

Unsigned trap if less than immediate

Load Instructions

Load address

Load byte

Load unsigned byte

Load halfword

Load unsigned halfword

Load word

Load word coprocessor 1

Load word left

Load word right

Load doubleword

Unaligned load halfword

Unaligned load halfword unsigned

Unaligned load word

Load linked

Store Instructions

Store byte

Store halfword

Store word

Store word coprocessor 1

Store double coprocessor 1

Store word left

Store word right

Store doubleword

Unaligned store halfword

Unaligned store word

Store conditional

Data Movement Instructions

Move

Move from hi

Move from lo

Move to hi

Move to lo

Move from coprocessor 0

Move from coprocessor 1

Move double from coprocessor 1

Move to coprocessor 0

Move to coprocessor 1

Move conditional not zero

Move conditional zero

Move conditional on FP false

Floating-Point Instructions

Floating-point absolute value double

Floating-point absolute value single

Floating-point addition double

Floating-point addition single

Floating-point ceiling to word

Compare equal double

Compare equal single

Compare less than equal double

Compare less than equal single

Compare less than double

Compare less than single

Convert single to double

Convert integer to double

Convert double to single

Convert integer to single

Convert double to integer

Convert single to integer

Floating-point divide double

Floating-point divide single

Floating-point floor to word

Load floating-point double

Load floating-point single

Move floating-point double

Move floating-point single

Move conditional floating-point double false

Move conditional floating-point single false

Move conditional floating-point double true

Move conditional floating-point single true

Move conditional floating-point double not zero

Move conditional floating-point single not zero

Move conditional floating-point double zero

Move conditional floating-point single zero

Floating-point multiply double

Floating-point multiply single

Negate double

Negate single

Floating-point round to word

Square root double

Square root single

Store floating-point double

Store floating-point single

Floating-point subtract double

Floating-point subtract single

Floating-point truncate to word

Exception and Interrupt Instructions

Exception return

System call

Break

No operation

B.11 Concluding Remarks

Further Reading

B.12 Exercises

Index

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

X

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc